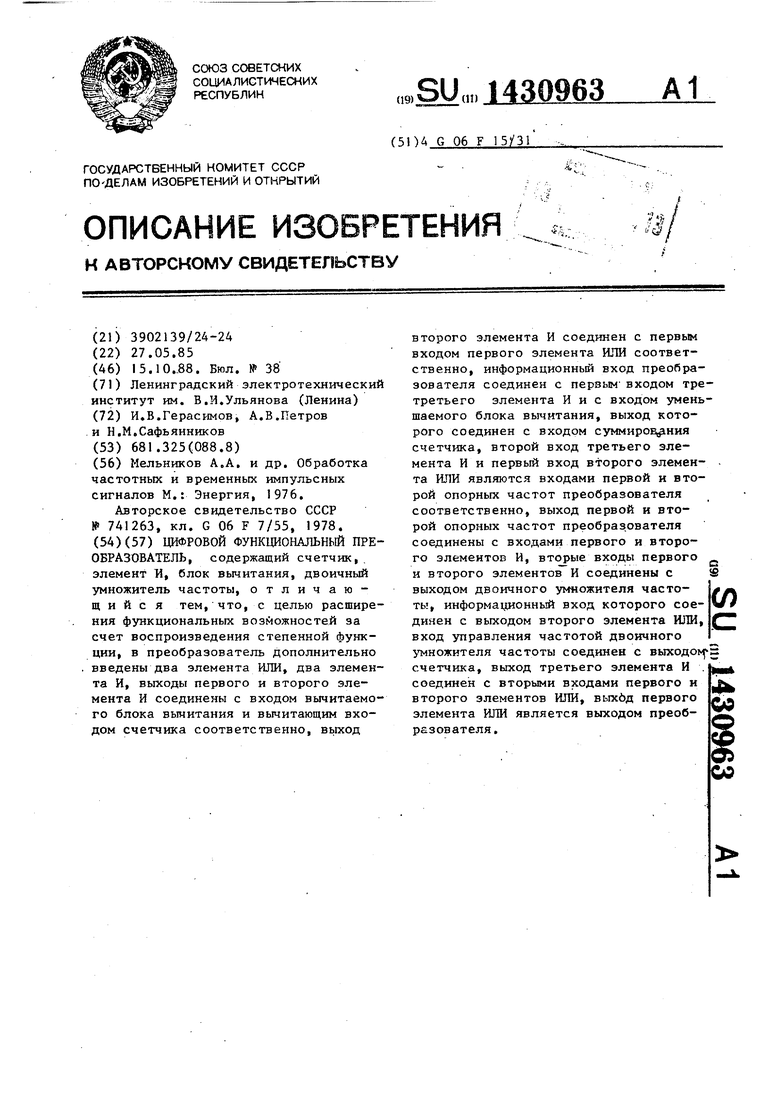

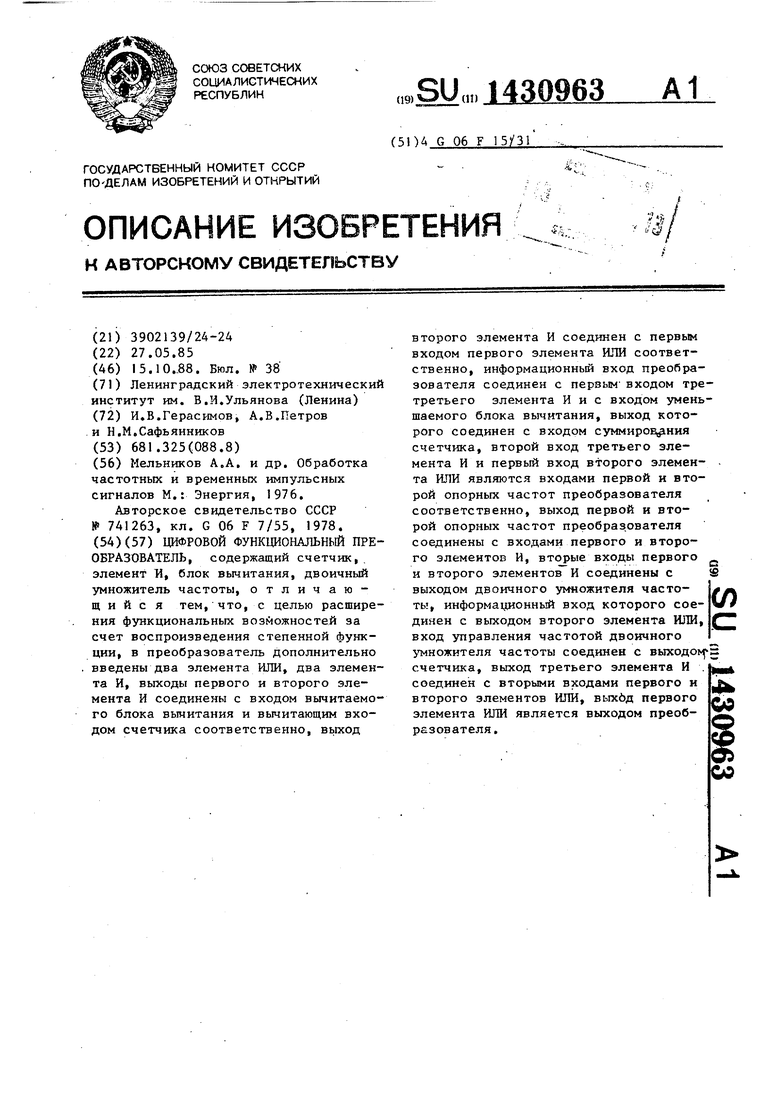

Изобретение относится к автоматике и вычислительной технике и может найти применение в устройствах обработки информации, представленной в виде числа импульсов или интервалов времени.

Цель изобретения - расширение функциональных возможностей преобразователя при одновременном повышении помехоустойчивости.

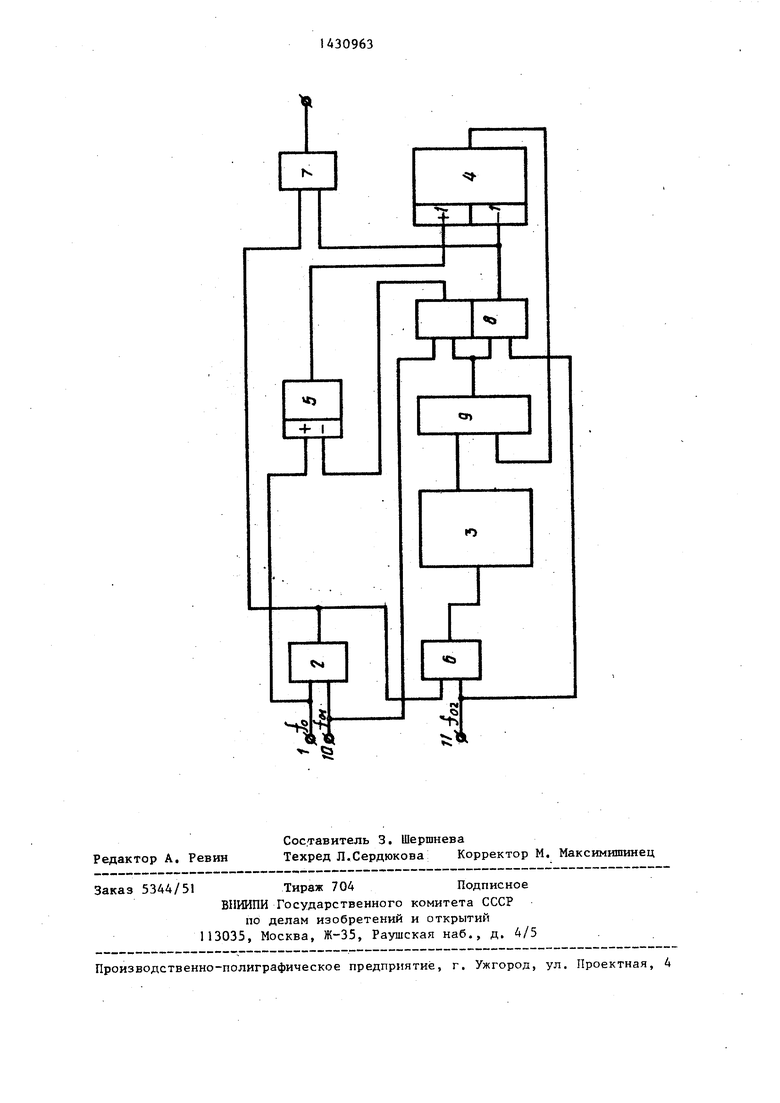

На чертеже изображен предлагаемый преобразователь.

Сущность изобретения состоит в создании помехоустойчивого цифрового функционального преобразователя для. вычитания натурального логарифма и степенной функции вида X , периодически преобразующего число-импульсные сигналы с использованием итерационного метода реализации оператора усреднения путем функционального обобщения двоичного умножителя частоты за счет совмещения фазирования и модуляции импульсных последо- вательностей и создания благодаря этому возможностей аппроксимирующего вычисления функций натурального логарифма и функции ввда .

Преобразователь.содержит информа- ционный вход 1, элемент И 2, счетчик 3, двоичный умножитель 4 частоты, блок 5 вычитания, элементы ИЛИ 6 и 7 и элементы И 8 и 9.

Преобразователь работает следующим образом.

Пусть в начальный момент времени разряды счетчика 3 обнулены. На информационный вход 1 поступает периодически повторяющийся с периодом Т число-импульсный код с опорной частотой f, , На входы 10 и 11 поступают последовательности импульсов со средними опорными частотами foi и fell меньшими fо, первая из которых синхронизирована импульсами чис- .ло-импульсного кода, поступающими по фазе 1, а вторая синхронизирована импульсами фазы 2. При,этом импульсы, поступающие с входа 1 запаздьшают относительно импульсов, поступающих с входа 10 на время задержки логического элемента. Таким образом, импульсы, поступающие с входа JО с опорной частотой ,, , пройдут на выход элемента И в течение промежутка времени t каждого периода поступления число-импульсного кода Т где N - коэффициент пересчета счет

чиков устройства. Средняя частота периодически повторяющейся последовательности импульсов-, формируемой на выходе элемента И 2, определяется следующим образом:

F, - f,

kt

01 N.

(1)

Q

5 0 5

Q

5

5

0

5

0

Учитьшая, что за время t каждого периода повторения число-импульсного кода по входу 1 поступает fot импульсов аргз мента, выражение представляет собой нормированное значение аргумента Njj. Следовательно

F foiNx

На суммирующий вход блока 5 вычитания с входа 1 в среднем за период поступления кода аргумента поступает частота fpNJ . Благодаря фазированию опорных последовательностей, поступающих с входом 10 и П , на вь|ходе элемента ИЛИ 6 будет сформирована импульсная последовательность со средней частотой foiNj i+ fo поступающая на вход двоичного умножителя частоты.

На суммирующий вход счетчика 3 поступают импульсы аргумента с выхода блока 5 вычитания, на вычитающем входе которого импульсы отсутствуют в момент начальной установки. Под воздействием растущего управляющего кода счетчика 3 на входы элементов И 8 и 9 начнут поступать импульсы со средней частотой

f 01 N X - К.

.N, .

где число, соответствующее коду

счетчика 3.

На выходе элементов И 8 и 9 будут сформированы из входной последовательности импульсов двоичного умножителя частоты две последовательности импульсов, поступающие на вьиита- ющий вход блока 5 вычитания и вычитающий вход счетчика 3 синхронно с импульсами, проходящими на первый и второй входы элемента ИЛИ 6 по фазе 1 и 2 со средними частотами

f °LNl.N „ blN N«, - N «

В основу работы преобразователя положен принцип автоматической компенсации импульсных последовательностей с использованием частотно-импуль

314

сной следящей системы при наличии импульсного потока, объединяемого и разделяемого в процессе формирования сигналов прямой и обратной связи, в результате чего воспроизводится дроб- но-рациональное выражение с частотным представлением выходной информации, причем перестройка вычисляемой элементарной функции осуществляется путем изменения значений частот опорной и импульсных последовательностей В качестве схемы сравнения, выраба- тьтающей сигнал рассогласования, используется реверсивный счетчик 3. Ус- ловием динамического равновесия преобразователя является равенство приращений кодов суммирующих и вычитающий цепей в реверсивном счетчике 3 в течение периода повторения число-импульсного кода, поступающего с входа 1,-т.е. равенство средних частот импульсных последовательностей, поступающих на суммирующий и вычитающий входы реверсивного счетчика 3. С учетом функционирования элементов 2-9 условием динамического равенства будет

f м - м N

откуда

N MO.NX .

foi.Ny + fo

(2)

Отсюда определяется выражение / средней частоты импульсной последовательности, поступающей на вычитающий вход счетчика 3,

К f

fo, N..

+ f

01

Сумма частот последовательностей импульсов, поступающих по фазе 1 и 2 на входы элемента ИЛИ 7 и формируемая на выходе этого элемента, определяет результат функционального преобразования:

2

F,+

F, f,iN,,-b

.

(fo, + fci)N x

f..Nv/+ f

fo,N,, +

oa (3)

-oi

Обозначив X N X из (3) получим

i S s l fkifki-ul571 .f 01 5 f pl

где f o fc/F7,

f 01 foi /FlMMkcJ

-at

fo, /F,

-7 M«ifC

07 / «акс

максимальное значение частоты выходной импульсной последовательности. При вьшолиении следующих условий:

fi

0,82505j

OJ7372;

0,29624, получим рациональную функцию FZ„/..S .372x4 j 7gi 5x

f;,

ol

-- Р(х)

2

X + 1 ,7053

которая аппроксимирует функцию Pn(ltx), 12с относительной погрешностью, не превосходящей 0,014% При задании величины

f: f; f;.

0,25928-10 ;

0,71009,

0,91857-10,

15

25 получим рациональную дробь

FI р , OiZ10225ii Qi.2729x

г.Х п Гопт

-гл.«.сX + 0,12937

л

аппроксимируюп1;ую функцию x , 1 с относительной приведенной погрешно-, стью, не превосходящей 0,%.

Таким образом, предлагаемый функциональный преобразователь имеет расширенные функциональные возможности в сравнении с прототипом. Кроме того предлагаемый преобразователь является более помехоустойчивым, так как появление единичных сбоев не приводит из-за реализации оператора усреднения к окончательному искажению результата. К числу достоинств предлагаемого преобразователя можно отнести его относительную простоту, позволяющую отказаться от использования узла сложения и блока управления прототипа, реализация которых, очевидно, сложнее вводимых четырех логических элементов, а также возможность построения двоичного умножителя частоты в интегральном исполнении на базе микросхем К 155 ИЕ8, вьтускаемых промышленностью.

Таким образом, предлагаемый преобразователь является к тому же более технологичным и надежным, а при со- поставимой конструкторско-технологи- ческой среде проектирования имеет меньшие габариты и вес.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления тангенса | 1990 |

|

SU1734091A1 |

| Множительно-делительное устройство | 1987 |

|

SU1451732A2 |

| Функциональный преобразователь широтно-импульсных сигналов | 1984 |

|

SU1226483A1 |

| УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНОГО ПРЕОБРАЗОВАНИЯ ШИРОТНО-ИМПУЛЬСНЫХ СИГНАЛОВ | 1992 |

|

RU2041499C1 |

| Устройство для функционального кодирования широтно-импульсных сигналов | 1985 |

|

SU1254583A1 |

| Устройство для функционального преобразования ШИМ-сигналов | 1984 |

|

SU1211749A1 |

| Устройство для вычисления элементарных функций | 1985 |

|

SU1275433A1 |

| ВРЕМЯ-ИМПУЛЬСНЫЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU363990A1 |

| ДВОИЧНЫЙ УМНОЖИТЕЛЬ | 1992 |

|

RU2006918C1 |

| ТЕПЛОСЧЕТЧИК | 1992 |

|

RU2041450C1 |

т1

s

| Мельников А.А | |||

| и др | |||

| Обработка частотных и временных импульсных сигналов М.: Энергия, 1976 | |||

| Устройство для вычисления логарифмов чисел | 1977 |

|

SU741263A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-15—Публикация

1985-05-27—Подача