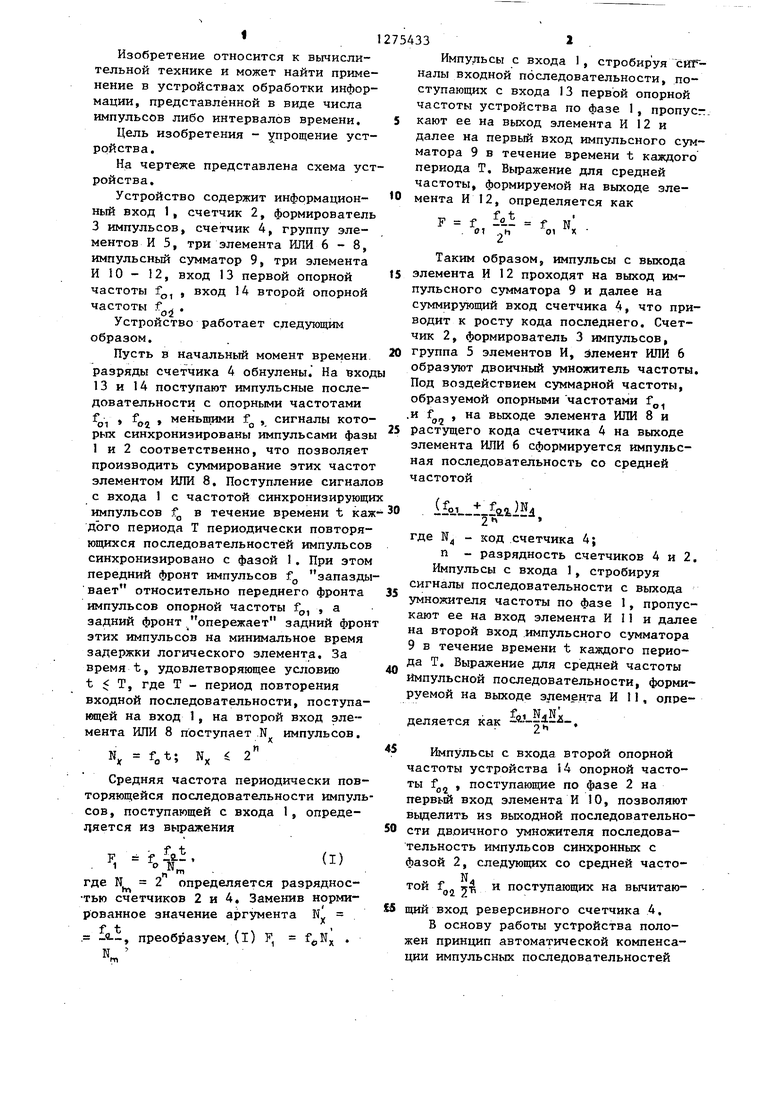

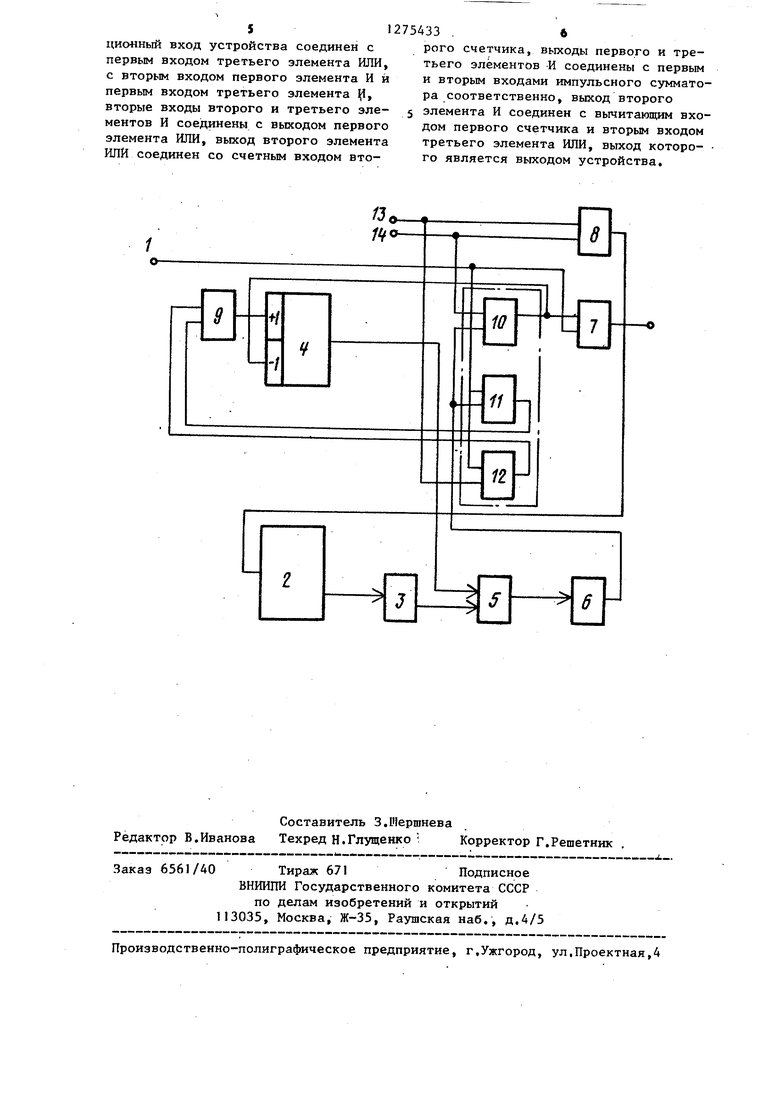

Изобретение относится к вычислительной технике и может найти применение в устройствах обработки информации, представленной в виде числа импульсов либо интервалов времени. Цель изобретения - упрощение устройства. На чертеже представлена схема уст ройства. Устройство содержит информационный вход 1, счетчик 2, формирователь 3 импульсов, счетчик 4, группу элементов И 5, три элемента ИЛИ 6-8, импульсный сумматор 9, три элемента И 10 - 12, вход 13 первой опорной частоты fp, , вход 14 второй опорной частоты fj . Устройство работает следующим образом. Пусть в начальный момент времени разряды счетчика 4 обнулены. На вход 13 и 14 поступают импульсные последовательности с опорными частотами f 02 меньшими f , сигналы которых синхронизированы импульсами фазы 1 и 2 соответственно, что позволяет производить суммирование этих частот элементом ИЛИ 8. Поступление сигнал с входа 1 с частотой синхронизирующи импульсов fg в течение времени t каж дого периода Т периодически повторяющихся последовательностей импульсов синхронизировано с фазой 1. При этом передний фронт импульсов f запазды вает относительно переднего фронта импульсов опорной частоты f,, , а задний фронт опережает задний фрон этих импульсов на минимальное время задержки логического элемента. За время t, удовлетворяющее условию t Т, где Т - период повторения входной последовательности, поступающей на вход 1, на второй вход элемента ИЛИ 8 поступает N импульсов. N. i 2 Njf fСредняя частота периодически повторяющейся последовательности импуль сов, поступающей с входа 1, опредедяется из вьфажения . -%„- . где N 2 определяется разрядностью счетчиков 2 и 4. Заменив нормированное значение аргумента . «., преобразуем, (l) F, . N 33 Импульсы с входа 1, стробируя сигналы входной последовательности, поступающих с входа 13 первой опорной частоты устройства по фазе 1, пропусг кают ее на выход элемента И 12 и далее на первый вход импульсного сумматора 9 в течение времени t каждого периода Т. Выражение для средней частоты, формируемой на выходе элемента И 12, определяется как f fot «я .,и Таким образом, импульсы с вькода элемента И 12 проходят на выход импульсного сумматора 9 и далее на суммирующий вход счетчика 4, что приводит к росту кода последнего. Счетчик 2, формирователь 3 импульсов, группа 5 элементов И, Элемент ИЛИ 6 образуют двоичный умножитель частоты. Под воздействием суммарной частоты, образуемой опорнь ми частотами Г„, и f , на выходе элемента ИЖ 8 и растущего кода счетчика 4 на выходе элемента ИЛИ 6 сформируется импульсная последовательность со средней частотой (foT « foa)N4 5 где N - ход счетчика 4; п - разрядность счетчиков 4 и 2. Импульсы с входа I, стробируя сигналы последовательности с выхода умножителя частоты по фазе 1, пропускают ее на вход элемента И П и далее на второй вход импульсного сумматора 9 в течение времени t каждого периода Т. Выражение для средней частоты Импульсной последовательности, формируемой на выходе элемента И 11, опре lL.. деляется как 2 Импульсы с входа второй опорной частоты устройства i 4 опорной частоты Гд , поступающие по фазе 2 на первый вход элемента И 10, позволяют вьщелить из выходной последовательности двоичного умножителя последовательность импульсов синхронных с фазой 2, следующих со средней частоN и поступающих на вычитающий вход реверсивного счетчика 4. В основу работы устройства положен принцип автоматической компенсации импульсных последовательностей 3 с использованием частотно-импульсной следящей системы. При наличии импуль сного потока, объединяемого и разделяемого в процессе формирования сигналов прямой и обратной связи, в резулътате чего воспроизводится дробно-рациональное выражение с частотным представлением выходной информации, причем перестройка вычисляемой элементарной функции осуществляется путем изменения значений частот опор ных импульсных последовательностей. В качестве схемы сравнения, вырабаты Бающей сигнал рассогласования, используется реверсивный счетчик 4. Условием динамического равновесия устройства является равенство приращений кодов суммирующих и вычитающих цепей в реверсивном счетчике 4 в течение периода следования входной последовательности импульсов, поступающей с входа 1, т.е. равенство средних частот импульсных последовательиостей, поступающих на суммирующий и вычитающий входы реверсивного счет чика 4. С учетом функционирования всех элементов устройства условием динамического равновесия будет kbLxJa а.я.Мд, отсюда 1| -Й7о 7 О1 Из вьфажения (3) непосредственно следует, что среднее значение частоты на выходе элемента И 10, поступающей на вычитаютций вход счетчика 4 и первый вход элемента ИЛИ 7, определяется как F о.о.Х f. , Сумма частот последовательностей импульсов, поступающих по фазе 1 и 2 на входы элемента ИЛИ 7 и формируемая на выходе этого : элемента, опреде ляет результат функционального преоб разования foz -fo, t- f f ) - .,lo.La.illlx. ift-iuL f x f,t/2 Обозначим X N, ., , где тогда из выражения (4) получим -(С. ., .Го1., где Г„ F F 3 fo, макс г мак максимальное значение частоты выходной импульсной последовательности. Полученное выражение представляет собой дробно-рациональную аппроксимацию для воспроизведения различных функций. Например, при задании опорных частот в виде 0,9154; f;, 0,0731; г; 0°0827, получаем рациональную дробь вида п qi s 1 п RAif К(Х) -i---т-Т7ТГ--т --- х т:пт5 Z макс которая аппроксимирует функцию arcsin X , 0,7 S 0,1 А, Аналогично, задавая значения опорных частот г; 0,78854; f 0,18826; f. 0,36768, можно изменить воспроизводимую зависимость 0,78854 х R(x) Х-1,9530 которая аппроксимирует функцию Sh(x),,n , В 0,2%, а при f 0,64026; f 0,34677; f 0,62005, получаем рациональную дробь . - т,/ - 0,64026х -1,7649Х RU)FTTTSBBT гмоко аппроксимирующую функцию X Vl -А « SiO,7%; ,1 . Формула изобретения Устройство для вычисления элементарньпс функций, содержащее два счетчика, (Формирователь импульсов, импульсный сумматор, группу элементов И, три элемента ИЛИ, три элемента И, выход импульсного сумматора соединен с суммирующим входом первовьтход второго счетчика го счетчика, с входом формирователя имсоединенпульсов, выход которого соединен с первыми входами элементов И группы, вторые входы которых соединены с выходами первого счетчика, выходы элементов И группы соединены с входами первого элемента ИЛИ, отличающееся тем, что, с целью упрощения устройства, вход первой опорной частоты устройства соединен с первыми входами второго элемента ИЛИ и первого элемента И, вход второй опорной частоты устройства соединен с вторым входом первого элемента ИЛИ и первым входом второго элемента И, информа$ 1

цисжный вход устройства соединен с первым входом третьего элемента ИЛИ, с вторым входом первого элемента И и первым входом третьего элемента ;1, вторые входы второго и третьего элементов И соединены с выходом первого элемента ИЛИ, выход второго элемента ИЛИ соединен со счетным входом вто275433 ,6

рого счетчика, выходы первого и третьего элементов И соединены с первым и вторым входами импульсного сумматора соответственно, выход второго 5 элемента И соединен с вычитающим входом первого счетчика и вторым входом третьего элемента ИЛИ, выход которого является выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1985 |

|

SU1430963A1 |

| Аналого-цифровой преобразователь сдвига фаз | 1979 |

|

SU788376A1 |

| Устройство для воспроизведения функций | 1986 |

|

SU1361549A1 |

| Число-импульсный функциональный преобразователь | 1982 |

|

SU1043645A1 |

| Электропривод переменного тока | 1984 |

|

SU1197032A1 |

| Устройство для функционального преобразования ШИМ-сигналов | 1984 |

|

SU1211749A1 |

| Умножитель частоты следования импульсов | 1985 |

|

SU1270886A1 |

| Автоматический регулятор компенсирующего устройства | 1990 |

|

SU1704145A1 |

| Регулятор конденсаторной батареи | 1989 |

|

SU1697067A1 |

| Функциональный преобразовательчиСлА иМпульСОВ B цифРОВОй КОд | 1979 |

|

SU807285A1 |

Изобретение относится к вычислительной технике и может найти применение в устройствах обработки информации, представленной в виде числа импульсов или интервалов времени. Цель изобретения - упрощение устрой- . ства при одновременном повьшении помехоустойчивости. Сущность изобретения состоит в создании простого и помехоустойчивого цифрового устройства для вычисления элементарных функций, преобразующего число - импульсные сигналы периодически с использованием итерационного метода реализации оператора усреднения путем функционального обобщения двоичного умножителя частоты за счет совмещения фазирования и модуляции импульсных последовательностей и создания благодаря этому возможности аппроксимирующего вычисления элементарных функций. Цель i изобретения достигнута за счет исключения счетчика, двух формирователей (Л импульсов, группы элементов И, импульсного сумматора и введения новых связей между оставшимися элементами прототипа. 1 ил. ю ел 4; .со 00

/VO

| Функциональный преобразователь | 1980 |

|

SU955040A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU955041A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-07—Публикация

1985-04-08—Подача