Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении функциональных преобразователей, а также в специализированных вычислительных устройствах для умножения частоты следования импульсных сигналов на параллельный двоичный код.

Известно устройство, предназначено для преобразования входного кода в среднюю частоту или в число импульсов. Оно содержит шестиразрядный двоичный синхронный счетчик и ряд логических цепей. К инверсному выходу каждого триггера счетчика присоединена ячейка И (И1-И6), сигнал на выходе которой может быть равен единице только тогда, когда данный триггер находится в нуле, а все предыдущие - в единице. На все входы ячеек И1-И6 подаются внешние управляющие сигналы Е5-Ео, разрешающие или запрещающие единичные сигналы на выходах ячеек. Счетчик имеет комплементарные выходы Q и  , выход переноса Свых (после подсчета 63 импульсов), входы сброса и останова счета, а также служебный вход для последовательного соединения этих счетчиков в случае наращивания разрядности схемы. Тактовая частота fo подается на вход С счетчика. Выходную частоту устройства можно рассчитать по выражению

, выход переноса Свых (после подсчета 63 импульсов), входы сброса и останова счета, а также служебный вход для последовательного соединения этих счетчиков в случае наращивания разрядности схемы. Тактовая частота fo подается на вход С счетчика. Выходную частоту устройства можно рассчитать по выражению

fвых = (fo/64) (E5 ˙25 + E4˙24 +

+E3 ˙23 + E2 ˙22 +E1 ˙21+ Eo ˙2o), где Ео-Е5 - данные на входах разрешения, причем значение каждого коэффициента Еi (i = 0-5) может быть "1" или "0".

Недостатками устройства являются сложность и ограниченные функциональные возможности, так как его код управления может задаваться только обычным цифровым двоичным кодированием в виде логических "0" и "1" и обеспечивает возможность умножения частоты только на двоичный коэффициент, т. е. устройство реализует лишь линейное преобразование кода в частоту. Кроме того, длительность выходных импульсов жестко связана с длительностью импульсов входной частоты.

Известен цифро-частотный умножитель, функциональные возможности которого расширены за счет снятия ограничения на длительность входного импульса в диапазоне от времени срабатывания элементов до полупериода опорной частоты. Он содержит частотный вход, делитель частоты, состоящий из n-1 последовательно включенных триггеров, n импульсно-потенциальных элементов И, элемент ИЛИ, n установочных входов и выходной триггер. Импульсная последовательность Х с частотой fx поступает на частотный вход. На выходах триггеров делителя частоты возникают импульсные последовательности с частотами fx ˙2-1, fx ˙2-2, . . . , fx ˙2-(n-1). На установочные входы подается n-разрядный код числа N, задающего коэффициент умножения, причем старший разряд Nn кода подается на вход S1, а младший N1 - на вход Sn. Средняя частота fy импульсной последовательности на выходе элемента ИЛИ определяется выражением

fy = Nnfx2o + Nn-1fx2-1 + . . . + N1fx2-(n-1), где Ni - значение i-го разряда кода числа N, равное "1" или "0", или

fy= [(fx)/(2n-1)]  2i-1N1.

2i-1N1.

Так как

N=  2i-1N1, то

2i-1N1, то

fy= (fxN)/2n-1.

Тогда средняя выходная частота fz импульсной последовательности на выходе триггера определяется выражением

fz= (fxN)/2n.

Недостатком цифро-частотного умножителя являются ограниченные функциональные возможности, так как его код управления может задаваться только обычным цифровым двоичным кодированием в виде логических "0" и "1" и обеспечивает возможность умножения частоты только на двоичный коэффициент, т. е. устройство реализует лишь линейное преобразование кода в частоту. Кроме того, длительность выходных импульсов не может быть больше полупериода опорной частоты.

Известен двоичный умножитель, функциональные возможности которого расширены за счет обеспечения изменения длительности выходных импульсов путем регулировки длительности входных сигналов до длительности пауз между входными импульсами умножителя. Он содержит счетчик, D-триггеры, управляющие входы, информационный вход и выход. На управляющий вход двоичного умножителя подается информация о коэффициенте умножения, на информационный вход - сигналы умножаемой частоты, которые подсчитываются счетчиком по заднему фронту каждого импульса. В момент прихода очередного заднего фронта входного импульса один из разрядов счетчика переходит из состояния логического "0" в состояние логической "1", т. е. на его выходе формируется передний фронт импульса, поступающего на тактовый вход соответствующего D-триггера. При этом D-триггер в зависимости от состояния сигнала на его информационном входе либо переключается в единичное состояние, либо сохраняет состояние логического "0". Следующий импульс, поступающий с информационного входа умножителя, сбрасывает ранее ус тановленный D-триггер. Таким образом, на выходах тех D-триггеров, на информационных входах которых поддерживается сигнал логической "1", формируются импульсы длительностью, равной длительности паузы между импульсами входной частоты. Причем упомянутые импульсы, формируемые на выходах D-триггеров, не пересекаются во времени, поскольку за один период сигналов входной частоты возможно переключение их состояния "0" в состояние "1" только одного разряда счетчика. Поэтому возможно объединение выходных сигналов D-триггеров логическим элементом ИЛИ, выход которого является выходом двоичного умножителя.

Средняя частота выходных сигналов двоичного умножителя

fвых= f , где fx - частота выходных сигналов двоичного умножителя;

, где fx - частота выходных сигналов двоичного умножителя;

К - десятичное число, соответствующее двоичному коду, подаваемому на управляющие входы двоичного умножителя;

n - число разрядов счетчика.

Недостаток двоичного умножителя являются ограниченные функциональные возможности, так как его код управления может задаваться только обычным цифровым двоичным кодированием в виде логических "0" и "1" и обеспечивает возможность умножения частоты только на двоичный коэффициент, т. е. устройство реализует лишь линейное преобразование кода в частоту.

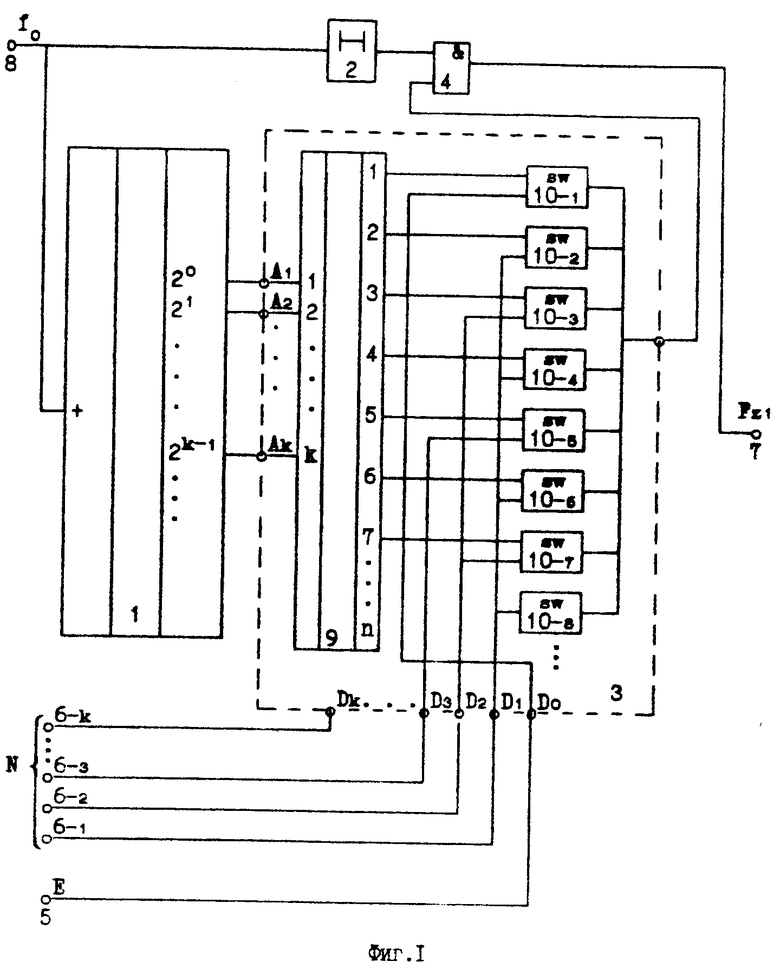

Наиболее близким по совокупности признаков и по технической сущности к заявляемому устройству является двоичный умножитель, который обеспечивает более широкие функциональные возможности благодаря реализации не только линейного преобразования кода в частоту, но в линейной амплитудной модуляции выходного импульсного потока. Он (фиг. 1) содержит двоичный счетчик 1, элемент 2 задержки, n-канальный мультиплексор 3 (n - число разрядов счетчика) и первый элемент И 4, первый вход которого соединен с выходом элемента 2 задержки. Выходы разрядов двоичного счетчика 1 соединены с соответствующими адресными входами n-канального мультиплексора 3, нулевой информационный вход которого соединен с управляющим входом 5 умножителя, а информационные входы с первого по n-й - с входами соответствующих разрядов цифрового входа 6 умножителя. Выход мультиплексора соединен с вторым входом элемента И 4, подключенного выходом к выходу 7 двоичного умножителя, вход 8 опорной частоты которого объединен с входом элемента 2 задержки и счетным входом счетчика 1.

Мультиплексор 3 выполнен в виде дешифратора 9, информационные входы которого являются адресными входами мультиплексора, ключей 10, первые входы которых соединены с соответствующими выходами дешифратора 9, а вторые являются информационными входами мультиплексора, выход которого объединен с выходами ключей 10. Причем второй вход первого ключа подключен к нулевому информационному входу мультиплексора 3, а вторые входы остальных n ключей соединены между собой по m входов и образуют группы с номерами j, число которых не превышает log2n и равно возможному числу разрядов цифрового входа двоичного умножителя, где n = 2,4,8, . . . , 2k, a k - разрядность двоичного умножителя. При этом число m соединенных между собой входов, входящих в j-ю группу, принимает значения от 1 до n/2j, а номер ключа SWj, соединенного с j-м информационным входом и входящего в j-ю группу, находится из выражения

SWj = 2mj - 2j-1 + 1.

При необходимости наращивания разрядности двоичного умножителя, когда по техническим причинам невозможно получить простую реализацию n-канального мультиплексора 3 с большим числом каналов, к управляющему входу 5 умножителя, являющемуся нулевым информационным входом мультиплексора, может быть подключен выход аналогичного мультиплексора, адресные входы которого подключаются к дополнительной группе незадействованных выходов разрядов двоичного счетчика 1, а информационные входы соединены между собой по указанным правилам и образуют группу младших разрядов кода управления двоичным умножителем.

Работа двоичного умножителя основана на принципах мультиплексирования αi ui состояний, где αi - коэффициенты, принимающие значения "0" или "1" в зависимости от логического состояния соответствующего i-го разряда цифрового входа двоичного умножителя (i = 1,2, . . . , k) k-разрядного кода управления в последовательности, задаваемой двоичным счетчиком 1.

Прототип работает следующим образом.

В исходном состоянии на входах 6 мультиплексора 3 присутствуют параллельный код управления N. При поступлении на счетный вход двоичного счетчика 1 входного импульсного потока с частотой следования импульсов fo изменяются его состояние и, следовательно, адреса коммутируемого канала мультиплексора 3. При этом на выходе мультиплексора появляются уровни напряжений "единичных" и "нулевых" состояний разрядов кода управления умножителем. Задержанные элементом 2 задержки импульсы входной частоты fo, совпадающие во времени с высокими уровнями напряжений, поступающими на второй вход элемента И 4 с выхода мультиплексора 3, разрешают им прохождение на выход 7 умножителя. В результате на выходе 7 присутствует импульсный поток, средняя частота которого пропорциональна коду управления:

fвых= fo (α1/2i)= (foN)/2k

(α1/2i)= (foN)/2k

Недостатками прототипа являются его ограниченные функциональные возможности, что обусловлено наличием лишь линейных преобразований в функциональной характеристике устройства.

Сущность изобретения состоит в создании двоичного умножителя с большими функциональными возможностями при применении метода частотной коммутации импульсных последовательностей в процессе формирования выходного импульсного потока и введении отрицательной обратной связи для осуществления операции деления, благодаря чему выходной импульсный поток представлен характеристикой простой дроби с аргументом как в числителе, так и в знаменателе, а разностный импульсный поток - характеристикой простой дроби с аргументом только в знаменателе, при сохранении режима линейного преобразования.

Существенные признаки изобретения состоят в том, что в двоичный умножитель, содержащий двоичный счетчик, элемент задержки, n-канальный мультиплексор и первый элемент И, первый вход которого соединен с выходом элемента задержки, причем выходы разрядов двоичного счетчика соединены с соответствующими адресными входами n-канального мультиплексора, нулевой информационный вход которого соединен с управляющим входом умножителя, а информационные входы с первого по n-й - с входами соответствующих разрядов цифрового входа умножителя, введены триггер, второй элемент И и формирователь импульсов, при этом первый информационный выход умножителя соединен со счетным входом двоичного счетчика и выходом второго элемента И, первый вход которого соединен с входом опорной частоты умножителя, входом формирователя импульсов и стробирующим входом n-канального мультиплексора, вход расширения и выход переноса которого соединены соответственно с входом расширения и выходом переноса умножителя, второй информационный выход которого соединен с выходом мультиплексора и входом элемента задержки, вход задания режима работы умножителя соединен с вторым входом первого элемента И, выход которого соединен со счетным входом триггера, вход сброса которого соединен с выходом формирователя импульсов, а инверсный выход - с вторым входом второго элемента И.

Вышеизложенное свидетельствует о наличии в заявляемом техническом решении отличительных от прототипа признаков, включающих как дополнительные элементы (триггер, элемент И, формирователь импульсов), так и ранее неизвестные связи между ними и элементами прототипа. Эти элементы находят широкое применение в устройствах цифровой вычислительной техники. Триггер осуществляет функцию деления частоты входного сигнала в 2 раза, элемент И - функцию конъюнкции, а формирователь импульсов - функцию формирования коротких импульсов по срезу входных сигналов. В заявляемом техническом решении все элементы устройства используются по прямому назначению, проявляя при этом в отдельности известные свойства. Однако взятые в совокупности эти элементы, элементы прототипа и новая организация связей проявляют новое свойство, не присущее ни прототипу, ни одному из известных аналогов - реализация нелинейного преобразования вида простой дроби. Это свойство не повторяет ни одного из известных свойств отличительных признаков и не является их суммой. Другими словами, каждый из введенных элементов, отдельно взятый, необходим для обеспечения сформулированного положительного эффекта, а все они вместе, т. е. с учетом всех взаимосвязей, достаточны, чтобы отличить устройство в целом от других подобного назначения и характеризовать его в том качестве, которое проявляется в сверхсуммарном техническом результате, а именно в расширении функциональной возможности двоичного умножителя путем реализации также нелинейного преобразования кода в частоту.

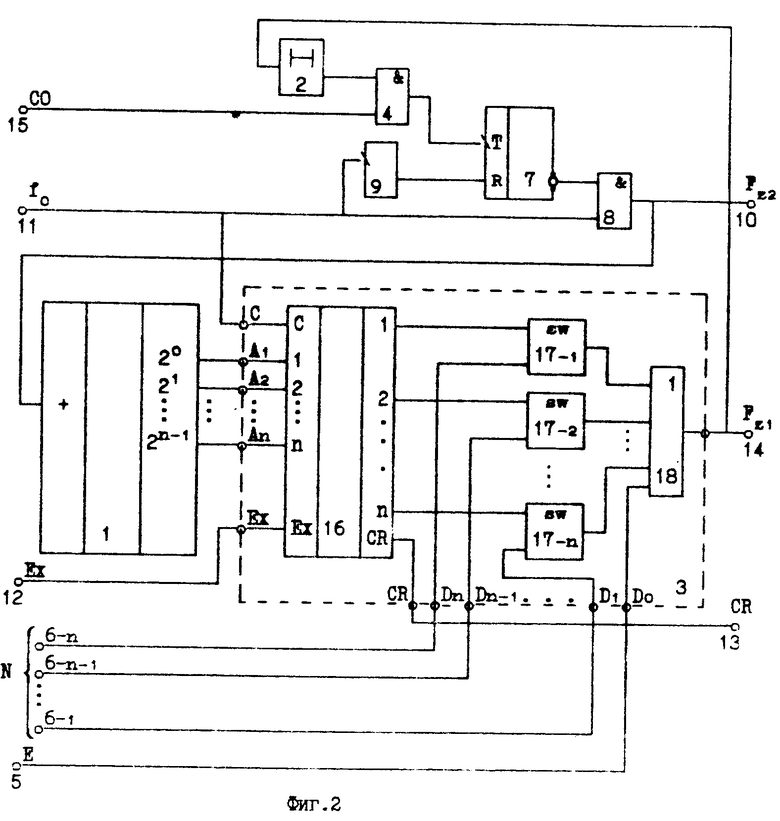

Предлагаемый умножитель (фиг. 2) содержит двоичный счетчик 1, элемент 2 задержки, n-канальный мультиплексор 3 и первый элемент И 4, первый вход которого соединен с выходом элемента 2 задержки. Выходы разрядов двоичного счетчика 1 соединены с соответствующими адресными входами n-канального мультиплексора 3, нулевой информационный вход которого соединен с управляющим входом 5 умножителя, а информационные входы с первого по n-й - с входами соответствующих разрядов цифрового входа 6 умножителя. Умножитель также содержит триггер 7, второй элемент И 8 и формирователь 9 импульсов. Первый информационный выход 10 умножителя соединен со счетным входом двоичного счетчика 1 и выходом второго элемента И 8, первый вход которого соединен с входом 11 опорной частоты умножителя, входом формирователя 9 импульсов и стробирующим входом n-канального мультиплексора 3. Вход 12 расширения и выход 13 переноса мультиплексора соединены соответственно с входом расширения и выходом переноса умножителя, второй информационный выход 14 которого соединен с выходом мультиплексора и входом элемента 2 задержки. Вход 15 задания режима работы умножителя соединен с вторым входом первого элемента И 4, выход которого соединен со счетным входом триггера 7, вход сброса которого соединен с выходом формирователя 9 импульсов, а инверсный выход - с вторым входом второго элемента И 8.

Мультиплексор 3 содержит дешифратор 16, информационные входы которого являются адресными входами мультиплексора, ключи 17, первые входы которых соединены с соответствующими выходами дешифратора 16, а вторые являются информационными входами мультиплексора. Старший разряд n дешифратора подается на первый ключ 17-1, следующий разряд n-1 - на второй ключ 17-2 и т. д. до первого разряда, подаваемого на n-й ключ 17-n. Мультиплексор 3 содержит также дизъюнктор 18, первый вход расширения которого является нулевым информационным входом мультиплексора, остальные соединены с выходами ключей, а выход является выходом мультиплексора. Дешифратор 16 имеет стробирующий вход, вход расширения и выход переноса, являющиеся аналогичными входами и выходом мультиплексора.

Умножитель работает следующим образом.

Пусть в начальный момент времени триггер 7 находится в нулевом состоянии. На вход 11 подается импульсная последовательность fo, на вход 15 - сигнал управления "1" или "0" в зависимости от режима работы умножителя, а на цифровом входе 6 присутствует параллельный код N управления. Входы 5 и 12 являются служебными, например для наращивания разрядности двоичного умножителя, как и выход 13 переноса. В данном случае на служебных входах 5, 12 присутствуют соответственно сигналы нулевого и единичного уровня. При этом период следования импульсной последовательности fo должен быть не менее суммарной задержки всей последовательной цепи элементов двоичного умножителя.

Импульсная последовательность опорной частоты fo поступает на стробирующий вход мультиплексора 3 и под управлением состояния инверсного выхода триггера 7 подается через элемент И 8 на счетный вход двоичного счетчика 1. Формирователь 9 по срезу входных импульсов формирует короткие импульсы, которые сбрасывают триггер 7 в нулевое состояние. При поступлении импульсов с выхода элемента И 8 на счетный вход счетчика 1 изменяется его состояние, следовательно, адреса коммутируемого канала мультиплексора 3. Под управлением разрядов цифрового входа 6 двоичного умножителя на выходе мультиплексора вырабатывается последовательность неравномерно распределенных во времени импульсов. Они поступают непосредственно на выход 14 двоичного умножителя и через элементы 2 задержки и И 4 под управлением сигнала на входе 15 на счетный вход триггера 7.

Элемент 2 задержки в схеме двоичного умножителя исключает возможность совпадения задних фронтов импульсов, поступающих на Т-вход счета и на R-вход сброса триггера 7. Более того задний фронт импульсов должен поступать на Т-вход триггера 7 позже импульсов, сформированных на его R-входе. Следовательно, элемент 2 служит для задержки выходного импульса мультиплексора 3 на время, большее длительности импульса, сформированного формирователем 9, что обеспечивает правильное функционирование триггера 7.

Первый импульс, появившийся на Т-входе триггера 7, по своему заднему фронту устанавливает его в единичное состояние. В результате сигналом с инверсного выхода триггера 7 элемент И 8 закрывается для прохождения следующего импульса опорной импульсной последовательности foна счетный вход счетчика 1. Однако этот заблокированный импульс опорной частоты по своему заднему фронту через формирователь 9 сбрасывает триггер 7 в нулевое состояние, после чего элемент И 8 открывается для прохождения последующего импульса опорной частоты, и процесс повторяется аналогично.

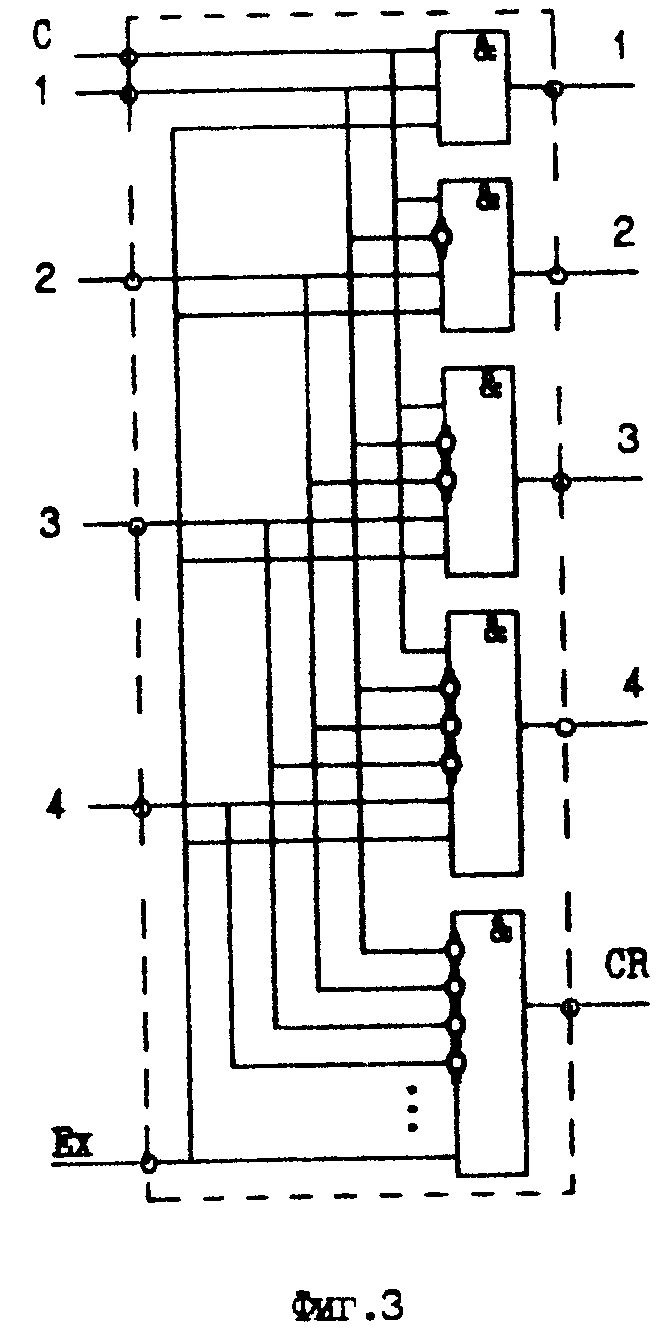

Все элементы предлагаемого двоичного умножителя хорошо известны. Если, например, представить реализацию двоичного умножителя на элементах ТТЛ, то можно выбрать следующие микросхемы. В качестве двоичного счетчика 1 можно использовать, например, микросхему К155ИЕ2, элемент 2 задержки может быть реализован, например, на основе микросхемы К155ЛЛ1, в качестве элементов И 4, 8 можно использовать микросхему К155ЛИ1, в качестве триггера 7 - К155 ТМ2, формирователь 9 импульсов может быть выполнен, например, на основе микросхем К155ЛА7 и К155ЛА8, дешифратор 16 может быть выполнен, например, на основе конъюнкторов, как показано на фиг. 3, в качестве ключей 17 можно использовать, например, микросхемы К155ЛИ1.

При необходимости наращивания разрядности двоичного умножителя, когда по техническим причинам невозможно получить простую реализацию n-канального мультиплексора 3 с большим числом каналов, к входу 5 может быть подключен выход аналогичного мультиплексора, адресные входы которого подключаются к дополнительной группе незадействованных выходов разрядов двоичного счетчика 1, его информационные входы образуют группу младших разрядов кода управления двоичным счетчиком, при этом стробирующий вход этого мультиплексора надо соединить с входом 11 двоичного умножителя, а его вход расширения - с выходом переноса n-канального мультиплексора 3.

Работа предлагаемого двоичного умножителя основана на принципах мультиплексирования α1 состояний, где α1 - коэффициенты, принимающие значения "0" или "1" в зависимости от логического состояния соответствующего i-го разряда цифрового входа двоичного умножителя (i = 1,2, . . . , n) n-разрядного кода управления в последовательности, задаваемой двоичным счетчиком, при введении отрицательной обратной связи для уменьшения опорной последовательности на количество импульсов, прошедших с выхода мультиплексора, благодаря чему создается возможность реализовать не только линейную функцию преобразования кода в частоту, но и нелинейную функцию воспроизведения простой дроби двух типов.

В общем случае дешифратор 16 совместно с двоичным счетчиком 1 образует суммирующий двоичный счетчик с динамическими выходами, т. е. в каждом такте импульса на входе счетчика 1 лишь на одном из выходов дешифратора 16 появляется импульс, за исключением такте установки в "0" по переполнению. В этом случае ни на одном из выходов дешифратора 16 нет импульсного сигнала. При этом если обеспечить равномерное поступление опорной частоты fo на счетный вход счетчика 1 (на вход 15 подать сигнал логического "0"), то каждая последующая импульсная последовательность на выходе дешифратора 16 сдвинута относительно предыдущей на величину

t1 = To2i-2, (i =  ), To = 1/fo (см. временную диаграмму на фиг. 4).

), To = 1/fo (см. временную диаграмму на фиг. 4).

Пример реализации такого дешифратора показан на фиг. 3.

Согласно функциональной схеме предложенного умножителя на выходе дешифратора 16, соответствующем разряду счетчика 1, в котором появляется "1", вырабатывается выходной сигнал (если ни в одном разряде счетчика 1 нет "1", то нет и импульса на выходе дешифратора). Таким образом, с выходов дешифратора 16 снимаются последовательности импульсов с частотами

fi=  , (i = 1,2, . . . , n), где Fz2 - частота импульсной последовательности на счетном входе счетчика 1, поступающая с выхода элемента И 8 и одновременно являющаяся второй выходной частотой умножителя;

, (i = 1,2, . . . , n), где Fz2 - частота импульсной последовательности на счетном входе счетчика 1, поступающая с выхода элемента И 8 и одновременно являющаяся второй выходной частотой умножителя;

n - разрядность счетчика 1;

i - номер соответствующего разряда счетчика 1.

Выходы дешифратора 16 объединены на ключах 17 с входами кода так, что младший разряд цифрового входа двоичного умножителя управляет последовательностью импульсов старшего разряда n дешифратора, следующий разряд - последовательностью импульсов разряда n-1 дешифратора и т. д. до старшего разряда, который управляет последовательностью импульсов, получаемой с первого разряда дешифратора.

Параллельный двоичный код поступает на первые входы ключей 17, выходы которых объединены дизъюнктором 18. На вторые входы ключей 17 поступают последовательности импульсов с соответствующих выходов дешифратора 16.

При поступлении на вход одного из ключей импульса с дешифратора 16 и наличии "1" в соответствующем разряде входного кода на выходе этого ключа появляется импульс, а следовательно, и на выходе мультиплексора 3 появляется импульс. Таким образом, на выходе мультиплексора вырабатывается последовательность неравномерно распределенных во времени импульсов с частотой

Fz1= (Fz2/2n)  α1·2i-1= (Fz2/2n)N, (1) где

α1·2i-1= (Fz2/2n)N, (1) где  - разряды кода N на цифровом входе умножителя.

- разряды кода N на цифровом входе умножителя.

Каждый появившийся импульс на выходе мультиплексора 3 через элементы 2 и 4 поступает на Т-вход триггера 7 и через него закрывает элемент И 8 для прохождения очередного импульса опорной частоты на вход счетчика 1. В результате количество импульсов на первом информационном выходе 10 умножителя определяется как разность между количеством импульсов опорной последовательности fo и количеством импульсов, прошедших с выхода мультиплексора 3, т. е. поступивших на второй информационный выход 14 умножителя.

Следовательно, при непрерывной циклической работе умножителя на счетный вход счетчика 1 поступает импульсная последовательность с частотой

Fz2 = fo - U˙ Fz1, (2) где Fz1 - частота импульсной последовательности на выходе мультиплексора 3;

U - логический уровень управляющего сигнала на входе 15.

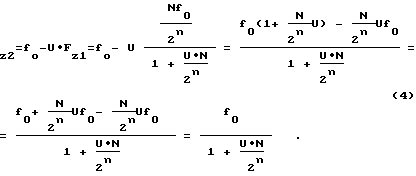

С учетом выражений (1) и (2)

Fz1= (Fz2/2n)N= [(fo-U·Fz1)/2n] N= (fo/2n)N-(UN/2n)Fz1

Отсюда

Fz1+(UN/2n)Fz1= (fo/2n)N или Fz1[1+(N/2n)U] = (N/2n)fo.

Тогда выходная частота умножителя по выходу 14 описывается выражением

Fz1= [(Nfo/2n)] /[1+(U·N/2n)] . (3)

Подставляя функциональную характеристику умножителя в выражение (2), получают

F

Таким образом, умножитель в зависимости сигнала U на его входе 15 выполняет следующие функции.

При U = "0" на выходе 14 умножителя вырабатывается импульсная последовательность вида

Fz1 = Nfo/2n, что соответствует функциональной характеристике прототипа.

При U = "1" на выходе 14 вырабатывается импульсная последовательность вида

Fz1=  =

=  , (5) где m = N/2n.

, (5) где m = N/2n.

Если представить аргумент Х = am, где а - натуральное число, то

m = X/a .

Тогда выражение (5) имеет вид

Fz1 = [(X/a)fo] /[1+X/a] = (foX)/(a+x) .

Эта функциональная характеристика представляет собой простую дробь с аргументом Х в числителе и знаменателе, зависящим от входного кода, и отличается от функциональной характеристики прототипа, обладающего линейной зависимостью коэффициента передачи от входного кода.

С помощью предложенного умножителя при наличии логической "1" на его входе 15 задания режима работы возможно воспроизведение нелинейностей для различных функций, аппроксимируемых с использованием простых дроблей вида

y = (dX)/(γ+X) .

При наличии на служебном входе 15 управления логического "0" предлагаемый двоичный умножитель реализует линейное преобразование кода в частоту, а при фиксированном значении кода вырабатывает фиксированное значение частоты.

Таким образом, с помощью заявляемого умножителя можно воспроизводить аппроксимации широкого набора функций, включающие постоянную составляющую, линейную зависимость и нелинейность вида простой дроби. Из этого набора в качестве примера представлены аппроксимации тригонометрической и показательной функций.

Функция y = cos ( π/2)X аппроксимируется с приведенной погрешностью δ≅0,29% в диапазоне Х ∈ [0; 1] выражением вида

y = 0,997-2,66X + 4,154X/(1,5+X) .

Функция y = e-X аппроксимируется с приведенной погрешностью δ≅0,15% в диапазоне Х ∈ [0; 3] выражением вида

y = 1,0015 + 0,162 X - 2,3800X/(2+X).

При U = "1" на первом информационном выходе 10 умножителя вырабатывается импульсная последовательность вида +N/2n] = fo/(1+m)= fo/[1+X/a] = (afo)/(a+X).

+N/2n] = fo/(1+m)= fo/[1+X/a] = (afo)/(a+X).

Эта функциональная характеристика также, как и по выходу 14, представляет собой простую дробь с аргументом Х, но только в знаменателе. В отличие от прототипа, здесь также имеет место нелинейное преобразование.

Таким образом, с помощью заявляемого умножителя, используя информационный выход 10, можно воспроизводить нелинейности различных функций, аппроксимируемых с использованием простых дробей вида

y = d/(γ+X).

В качестве примера далее представлены аппроксимации логарифмической и дробнопоказательной функций. Функция y =  аппроксимируется с приведенной погрешностью δ≅0,03% в диапазоне Х ∈[0,1; 1] выражением вида

аппроксимируется с приведенной погрешностью δ≅0,03% в диапазоне Х ∈[0,1; 1] выражением вида

y= 3,0464- 9,7893/(3,4102+X)+ 0,5336/(0,1589+X).

Функция y = log X аппроксимируется с приведенной погрешностью δ≅0,13% в диапазоне Х ∈ [0,1; 1] выражением вида

y = 0,8622 + 0,2575X - 0,1479/(0,2495+X).

Таким образом, подтверждается возможность осуществления изобретения, сущность которого характеризуется признаками, выраженными общими понятиями, а именно линейным и нелинейными преобразованиями кода в частоту по зависимости простой дроби двух типов - с аргументом в числителе и знаменателе, а также с аргументом только в знаменателе. (56) Авторское свидетельство СССР N 1575179, кл. G 06 F 7/68, 1990.

Авторское свидетельство СССР N 1159018, кл. G 06 F 7/68, 1985.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ АППРОКСИМАЦИИ ФУНКЦИЙ | 1992 |

|

RU2010324C1 |

| УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНОГО ПРЕОБРАЗОВАНИЯ ШИРОТНО-ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2006935C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА | 1991 |

|

RU2006916C1 |

| ЦИФРОВОЙ ТЕРМОМЕТР | 1992 |

|

RU2039953C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ | 1991 |

|

RU2029986C1 |

| УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНОГО ПРЕОБРАЗОВАНИЯ ШИРОТНО-ИМПУЛЬСНЫХ СИГНАЛОВ | 1992 |

|

RU2041499C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СИМВОЛЬНОЙ ИНФОРМАЦИИ | 1991 |

|

RU2010319C1 |

| КОРРЕЛЯЦИОННАЯ ИЗМЕРИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2007753C1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ АКТИВНОЙ МОЩНОСТИ | 1993 |

|

RU2074397C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ | 1991 |

|

RU2065202C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении функциональных преобразователей, а также в специализированных вычислительных устройствах для умножения частоты следования импульсных сигналов на параллельный двоичный код. Цель изобретения - расширение функциональных возможностей за счет реализации нелинейного преобразования кода в частоту. Сущность изобретения заключается в применении метода частотной коммутации импульсных последовательностей в процессе формирования выходного импульсного потока и введении отрицательной обратной связи для осуществления операции деления, благодаря чему выходной импульсный поток представлен характеристикой простой дроби с аргументом как в числителе, так и в знаменателе, а разностный импульсный поток - характеристикой простой дроби с аргументом только в знаменателе, при сохранении режима линейного преобразования. 4 ил.

ДВОИЧНЫЙ УМНОЖИТЕЛЬ, содержащий двоичный счетчик, элемент задержки, n-канальный мультиплексор (n - число разрядов счетчика) и первый элемент И, первый вход которого соединен с выходом элемента задержки, выходы разрядов двоичного счетчика соединены с соответствующими адресными входами n-канального мультиплексора, нулевой информационный вход которого соединен с управляющим входом умножителя, а информационные входы с первого по n-й - с входами соответствующих разрядов цифрового входа умножителя, отличающийся тем, что в него введены триггер, второй элемент И и формирователь импульсов, причем первый информационный выход умножителя соединен со счетным входом двоичного счетчика и выходом второго элемента И, первый вход которого соединен с входом опорной частоты умножителя, входом формирователя импульсов и стробирующим входом n-канального мультиплексора, вход расширения и выход переноса которого соединены соответственно с входом расширения и выходом переноса умножителя, второй информационный выход которого соединен с выходом n-канального мультиплексора и входом элемента задержки, вход задания режима работы умножителя соединен с вторым входом первого элемента И, выход которого соединен со счетным входом триггера, вход сброса которого соединен с выходом формирователя импульсов, а инверсный выход - с вторым входом второго элемента И.

Авторы

Даты

1994-01-30—Публикация

1992-02-03—Подача