Изобретение относится к электро- технике и может использоваться в уст ройствах регулирования тока через нагрузку или регулируемого отбора мощности, напримерJ при испытаниях усилителей или нсточ1гиков питания.

Цель изобретения повышение динамической стабильности токз повышение надежности и расширение функциональных возможностей регулятора за счет введения режима модуляции тока и цифрового управления.

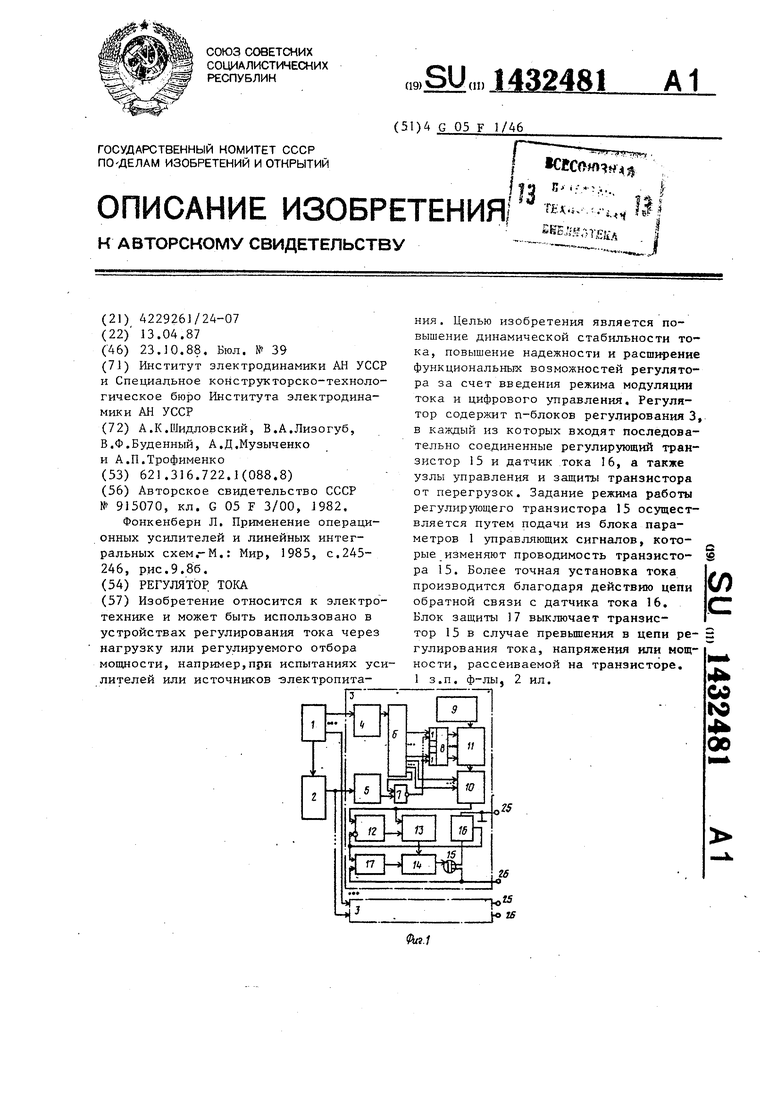

На фиг представлена стру1стурная

группы которого подключен к другому входу логического элемента И-НЕ 7, Выходы блока 8 логических элементов ИЛИ подк;шчены к управляющим входам цифроаналогового преобразователя 1, опорный вход которого подключен к выходу источника 9 стабильного напряжения. Выход цифроаналогового преобразователя П подключен к опорному входу цифроаналогового преобразователя 0, выход которого подключен к первым входам дифференциального усилителя 12 и аналогового сумматора 13, второй

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизированная трехфазная система питания | 1989 |

|

SU1777128A1 |

| Устройство для регулирования напряжения | 1987 |

|

SU1599844A1 |

| Емкостный уровнемер | 1987 |

|

SU1582020A1 |

| Устройство для перемещения и колебаний сварочной горелки | 1988 |

|

SU1547995A1 |

| Устройство для управления преобразователем частоты с непосредственной связью и широтно-импульсным регулированием | 1989 |

|

SU1624629A1 |

| Устройство дискретного воспроизведения изменяющегося магнитного поля | 1984 |

|

SU1213445A1 |

| Высокочастотный импульсный регулятор постоянного напряжения | 1990 |

|

SU1764046A1 |

| Стабилизатор переменного напряжения | 1987 |

|

SU1582181A1 |

| Устройство для компенсации реактивной мощности | 1985 |

|

SU1272401A1 |

| Регулятор тока | 1987 |

|

SU1501011A1 |

Изобретение относится к электротехнике и может быть использовано в устройствах регулирования тока через нагрузку или регулируемого отбора мощности, например,при испытаниях уси лителей или источников -электропитаГз ния. Целью изобретения является повышение динамической стабильности тока, повышение надежности и расширение функциональных возможностей регулятора за счет введения режима модуляции тока и цифрового управления, Регулятор содержит п-блоков регулирования 3, в каждый из которых входят последовательно соединенные регулирующий транзистор 15 и датчик тока 16, а также узлы управления и защиты транзистора от перегрузок. Задание режима работы регулирующего транзистора 15 осуществляется путем подачи из блока параметров 1 управляющих сигналов, которые изменяют проводимость транзистора 15. Более точная установка тока производится благодаря действию цепи обратной связи с датчика тока 16, Блок защиты 17 выключает транзистор 15 в случае превьшения в цепи регулирования тока, напряжения или мощности, рассеиваемой на транзисторе. 1 3.п. ф-лы J 2 ил. (Л Од Isd «1 СХ 25

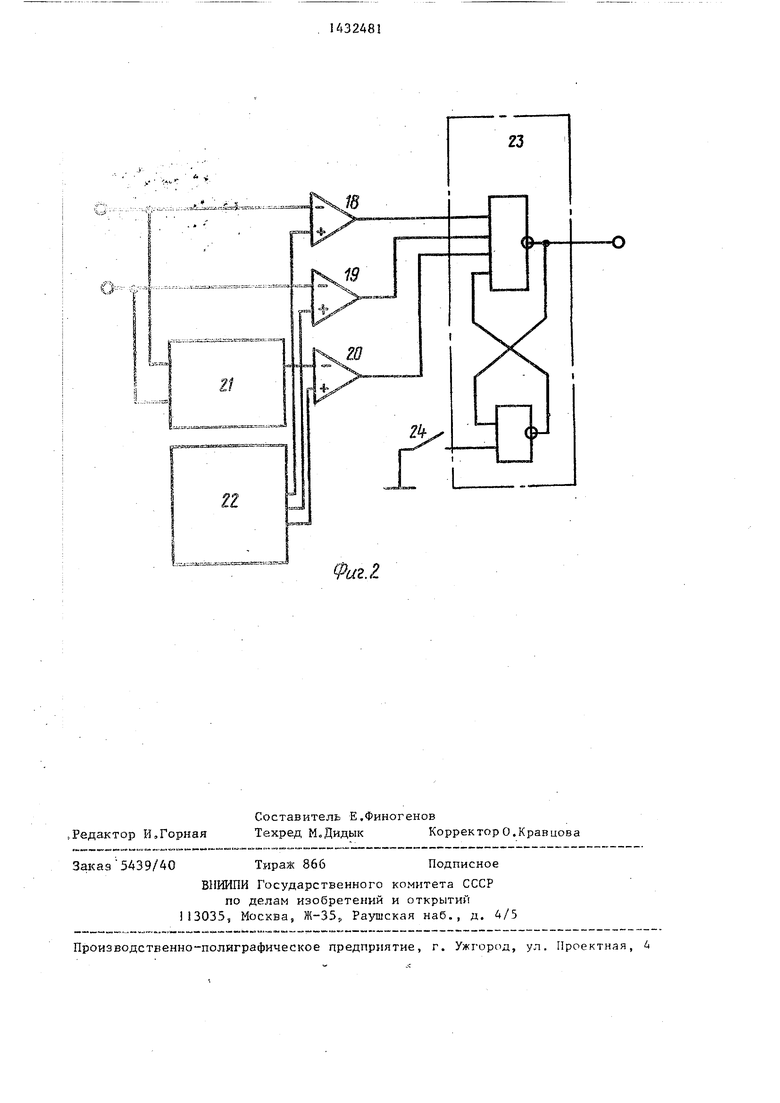

схема регулятора тока на фиг,2 - струк- 5 вход которого подключен к выходу диф- турная схема блока защиты.

ференциального усилителя 12, второй вход которого подключен к выходу дат- чт;а 16 тока. Выход аналогового сумматора подключен к yпpaвляющe -ry выводу регулирующего транзистора 15 через размыкаемые контакты аналогового клоча 14, управляющий вход которого подключен к выходу блока J7 защиты. Регулирующий транзистор 15 первым силовым выводом соедине с первым входным вь водом датчика 16 тока, второй входной вывод которого соединен с первым входным вьюодом 25, второй входной вывод 26 подключен к второму силовому выводу регулирующего транзистора 15

Регулятор тока содеря ит блок 1 ввода параметровSкодоуправляемъш ге- кератор 2j п блоков 3 рег-улнрования, Блок регулирования содерлсит первый 4 и второй 5 блоки гальваниче ской раз вязки, регистр 6, логический элемент И-ИЁ 7s блок 8 элементов tLHlisHC точник 9 стабушьног О напряжения, пер вый 10 и второй 1,1 цифроа1 алоговые преобразователи, дифференциальный усилитель 12, аналоговый суммато; аналоговый ключ 14, регулирующий зистор 15, датчик 16 тока и блок 17 защиты от перегрузок Последний содержит компараторы 18-20,, перемножитель 21, блок 22 опорных напряжений, RS-триггер 23 и коммутад1-юннь;й элемент 24о Силовым входом регулятора являются выводы 25 и 26.,

Первьге выходы блока 1 ввода параметров сое/яинены с первыми входами блоков 3 регулирования, вторые входы которых объединены и подключены к выходу кодоуправляемого импульсного I генератора 2, вход которого подклю-, Iчен к первому выходу блока 1 ввода i параметров,, Вход1 1 блоков 4 и 5 гальванической 1эазвязки являются соответственно первым и вторым управляющими входами блока регулирования, Выход блока 4 гальванической развязки под- кхпочен к входу регистра 6, выходы первой группы которого подключены к управляющим входам цифроаналогового преобразователя 10. Выход блока 5 гальванической развязки подключен к одному ЁХОД2 логш-геского элемента И-НЁ 7, выход которого подключен к объединенньпч одним входам блока 8 логических элементов ИШ, другие входы которых подк.точены к выходам второй группы регистра 6, выход третьей

5 вход которого подключен к выходу диф-

0

5

0

5

5

O

5

ференциального усилителя 12, второй вход которого подключен к выходу дат- чт;а 16 тока. Выход аналогового сумматора подключен к yпpaвляющe -ry выводу регулирующего транзистора 15 через размыкаемые контакты аналогового клоча 14, управляющий вход которого подключен к выходу блока J7 защиты. Регулирующий транзистор 15 первым силовым выводом соедине с первым входным вь водом датчика 16 тока, второй входной вывод которого соединен с первым входным вьюодом 25, второй входной вывод 26 подключен к второму силовому выводу регулирующего транзистора 15

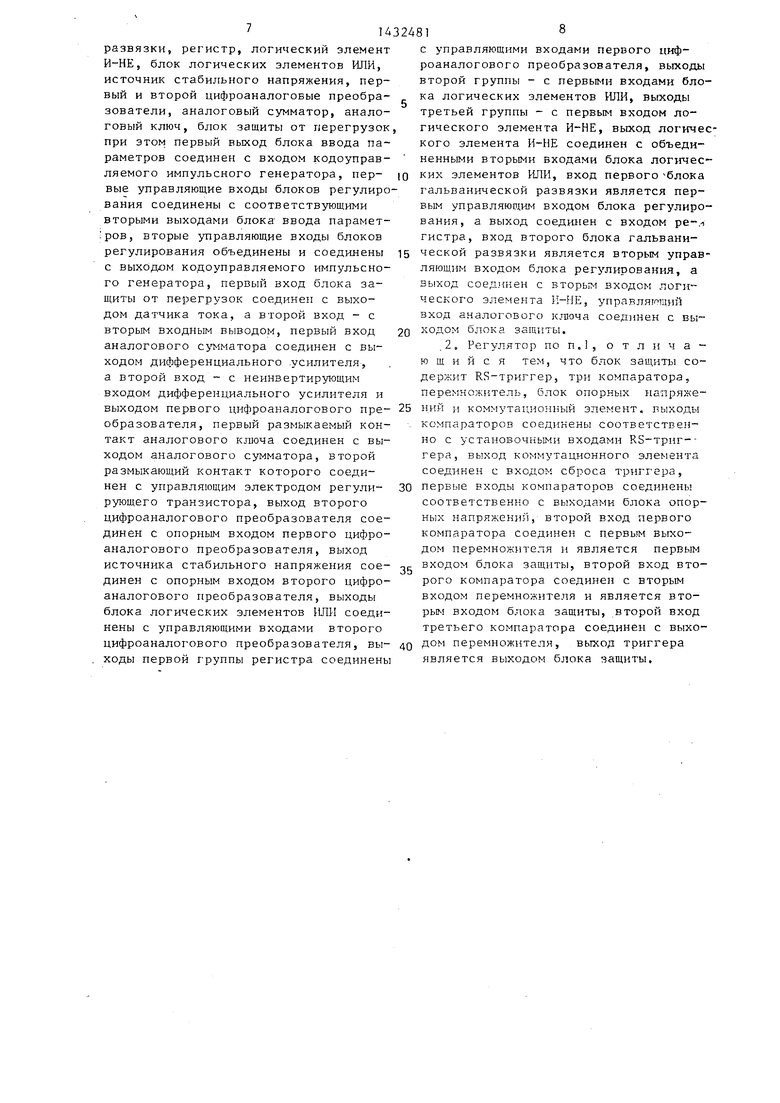

Второй входной вывод 26 и выход датчика 16 тока подключены соответственно к первому и второму входам блока 17 защиты от перегрузок, которыми являются соответственно первые входы компараторов 18 и 19, которые соединены с входами пepe шoжитeля 21, Выход перемножителя соединен с первым входом компаратора 20. Вторые входы компараторов 18-20 соединены с выходами блока 22 опорных напряжений. Выходы компараторов 18-20 подключены к входам установки RS-триггера 23, вход сброса которого подключен к выходу коммутационного элемента 24. Выход RS-триггера 23 является выходом блока 17 защиты.

Регулятор тока работает следующим образом.

В исходном состоянии регистр 6 находится в обнуленном состоянии, логический элемент И-НЕ 7 запрещает прохождение модулирующих импульсов, а нулевое состояние на управляющих входах цифроаналогового преобразователя to приводит к тому, что на его выходе - нулевое напряжение„ Это напряжение проходит через дифференпиальный

усилитель 12, аналоговый сумматор 13 и аналоговый ключ 14 на управляющий вывод транзистора 15 и запирает его. Ток в регулируемой цепи не проходит независимо от напряжения на входных силовых выводах 25 и 26,

При подаче из блока 1 ввода параметров управляющих сигналов происходит установка частоты в кодоуправляе- ю нов, высокий уровень которого такой мом импульсном генераторе 2 и через же, как и в первом случае, а низкий блок 4 гальванической развязки устауровень пропорционально соответствует уровню провала тока при его модуляции.

навливается управляющий код в регистре 6. .

При этом возможны два случая. 15

В первом случае на выходе третьей группы регистра 6 устанавливается уровень логического нуля. Тогда логический элемент И-Pffi 7 блокирует прохождение импульсов от кодоуправляемо- 20водит к усГтаковлению некоторого, го импульсного генератора 2 черезблизкого к заданному, тока в цепи блок 5 гальванической развязки и навывод 26 - транзистор 15 - датчик 16 первые входы блока 8 логических эле-тока - вьшод 25 (при этом предполага- ментов ШИ поступает уровень логичес-ется, что между выводами 25 и 26 кой единицы. На выходах блока 8 логи- 25приложено напряжение от некоторого ческих элементов ИЛИ устанавливаетсяиспытываемого внешнего источника), уровень логической единицы и напряже-Более точно ток устанавливается в ре- ние источника 9 стабильного напряже-зультате действия обратной связи, ния без изменений поступает через циф-напряжение которой от датчика 16 то- роаналоговый преобразователь 11 на 30ка поступает на инверсный вход диф- опорный вход цифроаналогового преобра-ференциального усилителя J2, где зователя 10. Напряжение на выходе поНапряжение с выхода цифроаналогового преобразователя 10 поступает через аналоговый с мматор 3 и аналоговый ключ 14 на управляющий электрод регулирующего транзистора J5, Это присравнивается с выходным напряжением цифроаналогового преобразователя JO, и сигнал ошибки через аналоговый сумматор 13 и аналоговый ключ J4 воз- дер1ствует на управляющий электрод. транзистора 15. После этого ток в цепи выводов 25 и 26 устанавливается более точно. На входы блока 17 защиты

следнего устанавливается постоянным и пропорциональным числовому значению кода, поступающего с выхода первой группы регистра 6 на управляющие входы цифроаналогового преобразователя 10,

Во втором случае на выходе третьей группы регистра 6 устанавливается уровень логической единицы. Тогда логический элемент И-НЕ 7 разрешает прохождение импульсного напряжения от кодоуправляемого импульсного генератора 2 через блок 5 гальванической развязки на первые входы блока 8 элементов ИЛИ. При уровне логической единицы на этих входах уровни напряжений на выводах цифроаналогового преобразователя 10 те же, что и в первом случае, а при уровне логического нуля код с выходов второй группы регистра 6 поступает на управляющие входы цифроаналогового преобразователя J1 и напряжение на его выходе уменьшается пропорционально числовому значению кода на его управляющих входах. Поскольку это напряжение поступает на опорный вход цифроаналогового преобразователя 10, пропорционально уменьшается и напряжение на выходе цифро- аналогового преобразователя 10,

Таким образом, на выходе цифроана- логового преобразователя 10 в первом случае формируется постоянное напряжение, пропорциональное задаваемому току, а во втором случае - прямоугольнов, высокий уровень которого такой же, как и в первом случае, а низкий

уровень пропорционально соответствует уровню провала тока при его модуляции.

водит к усГтаковлению некоторого, близкого к заданному, тока в цепи вывод 26 - транзистор 15 - датчик 16 тока - вьшод 25 (при этом предполага- ется, что между выводами 25 и 26 приложено напряжение от некоторого испытываемого внешнего источника), Более точно ток устанавливается в ре- зультате действия обратной связи, напряжение которой от датчика 16 то- ка поступает на инверсный вход диф- ференциального усилителя J2, где

Напряжение с выхода цифроаналогового преобразователя 10 поступает через аналоговый с мматор 3 и аналоговый ключ 14 на управляющий электрод регулирующего транзистора J5, Это при0водит к усГтаковлению некоторого, близкого к заданному, тока в цепи вывод 26 - транзистор 15 - датчик 16 тока - вьшод 25 (при этом предполага- ется, что между выводами 25 и 26 5приложено напряжение от некоторого испытываемого внешнего источника), Более точно ток устанавливается в ре- зультате действия обратной связи, напряжение которой от датчика 16 то- 30ка поступает на инверсный вход диф- ференциального усилителя J2, где

35

сравнивается с выходным напряжением цифроаналогового преобразователя JO, и сигнал ошибки через аналоговый сумматор 13 и аналоговый ключ J4 воз- дер1ствует на управляющий электрод. транзистора 15. После этого ток в цепи выводов 25 и 26 устанавливается более точно. На входы блока 17 защиты

40 от перегрузок поступают напряжения, пропорциональные напряжению между выводами 26 и 25 и току в цепи этих выводов. В блоке защиты эти напряжения и/или их функции сравниваются с за45 данными, и в случае превышения заданных постоянных значений блок защиты воздействует на управляющий вход аналогового KjB04a и переключает транзистор 15 в безопасное состояние,

50 В качестве примера на фиг,2 показан блок 17 защиты от перегрузок, защищающий транзистор 15 от избыточног тока, избыточной мощности, избыточного напряжения путем запирания тран55 зистора (и замыкания перехода база- эмиттер при применении биполярного транзистора). Напряжение, пропорциональное току в цепи силовых выводов транзистора 15 поступает на первые.

вкоды компаратора 18 и перемножителя 21 , Напрялсение с выводов 25 и 26 поступает на второй вход перемножителя 21 и на первый вход компаратора 19 С выхода перемножителя 2J напряжение пропорциональное мощности, рассеиваемой на транзисторе 15, поступает на первый вход компаратора 20, На вторые входы компараторов 18-20 подают постоянные напряжения от блока 22 опорных напряжений.

При превьш1ении указанными током, напряжением или мощностью заданных Значений напряжение на первом входе минимуи одного из компараторов 18-20 Становится большим, чем напряжение на втором входе того же компаратора н последний устанавливает RS-триг- гер 23. Уровень логической единицы с выхода RS-триггера 23 действует на аналоговый ключ 14, который отключае управляющий электрод транзистора 15 от выхода аналогового сумматора,обес- Печтзая запдату транзистора от пере- Грузок, В случае применения биполярнго транзистора 15 аналоговый ключ 14 Замыкает эмиттерный переход транзистора и, благодаря тому, транзистор может выдержать большее напряжение эмиттер-коллектор.

Для восстановления работоспособности регулятора после срабатывания 8ащиты необходимо замкнуть коммутационный элемент 24, который переводит RS-триггер 23 в сброшенное состояние

Для испытаний вторичных источников гэлектропитания с большим числом выходных каналов или при испытаниях Многоканальных усилителей число бло- koB регулирования может быть установ- jneHo равным числу выходов испытывае- ого устройства.

При резком изменении напряжения иежду выводами 25 и 26 или при моду- ляции тока, формируемого на выходе цифроаналогового преобразователя 10 прямоугольным напряжением в цепи обратной связи могут возникать возмуще

ния. Относительная амплитуда возмущения зависит от соотношения напряжения Ujj на выходе цифроаналогового преобразователя 10 и диапазона АИ изменения напряжения на выходе дифференциального усилителя 12 и может достичь значения

7S

и

u;

Такая амплитуда возмущения соответствует, например, скачкообразному нарастанию напряжения между выводами 25 и 26 от нулевого значения до некоторого постоянного, когда напряжение ошибки на выходе дифференциального усилителя 12 переходит от максимального одной полярности к максимальному противоположной полярности (ограниченному диапазоном выходных напряжений дифференциального усилителя 12) значению.

Повышение надежности достигается благодаря ограничению режимов работы транзистора 5 областью работоспособности .(ограничению по напряжению, по току и по мощности) и отключению этого транзистора при выходе его режима из зоны области работоспособности. Этим снижается вероятность выхода из строя транзистора из-за пробоя или перегрева.

Расширение функциональных возможностей регулятора достигается введением отсутствующего в известном регуляторе режима модуляции тока, необходимого для динамических испытаний источников электрического тока, и введением цифрового управления, позволяющего включать регулятор тока в состав испытательных комплексов, управляемых от ЭВМ, и тем самым автоматизировать процесс испытаний источников питания или усилителей.

Формула изобретения

1, Регулятор тока, содержащий блок регулирования, в который входят датчи тока, дифференциальный усилитель и регулирующий транзистор, первый силовой вывод которого через датчик тока соединен с первым входным выводом, второй силовой вьшод регулирующего транзистора является вторым входным выводом, выход датчика тока подключен к инвертирующему входу дифференциального усилителя, отличающий- с я тем, что, с целью повышения динамической стабильности тока, повышения надежности и расширения функциональны возможностей за счет введения режима модуляции тока и цифрового управления в него введены блок ввода параметров, кодоуправляемый ампульсный генератор п-дополнительных блоков регулирования во все блоки регулирования введены первый и второй блоки гальванической

7

развязки, регистр, логический элемент И-НЕ, блок логических элементов ИЛИ, источник стабильного напряжения, первый и второй цифроаналоговые преобразователи, аналоговый сумматор, анало14

говый ключ, блок зашиты от перегрузок при этом первый выход блока ввода параметров соединен с входом кодоуправ- ляемого импульсного генератора, пер- вые управляющие входы блоков регулирования соединены с соответствующими вторыми выходами блока ввода парамет- :ров, вторые управляющие входы блоков регулирования объединены и соединены с выходом кодоуправляемого импульсного генератора, первый вход блока защиты от перегрузок соединен с выходом датчика тока, а второй вход - с вторым входным выводом, первый вход аналогового c T iMaTopa соединен с выходом дифференциального .усилителя, а второй вход - с неинвертирующим входом дифференциального усилителя и

выходом первого цифроаналогового пре- 25 ний и коммутационный элемент, лыходы образователя, первый размыкаемый кон- компараторов соединены соответствеи

такт аналогового ключа соединен с выходом аналогового сумматора, второй размыкающий контакт которого соединен с управляющим электродом регулирующего транзистора, выход второго цифроаналогового преобразователя соединен с опорным входом первого цифро- аналогового преобразователя, выход источника стабильного напряжения сое- динен с опорным входом второго цифро- аналогового преобразователя, выходы блока логических элементов ИЛИ соединены с управляющими входами второго цифроаналогового преобразователя, выходы первой группы регистра соединены

т 15

к, -ю о-

432481

с управляющими входами первого циф- роаналогового преобразователя, выходы второй группы - с первыми входами блока логических элементов ЖИ, выходы третьей группы - с первым входом логического элемента И-НЕ, выход логического элемента И-НЕ соединен с объединенными вторь ш входами блока лог гчес- ких элементов ИЛИ, вход первого -блока гальванической развязки является первым управляюо ш- входом блока регулирования, а выход соединен с входом pe-.i гистра, вход второго блока гальванической развязки является вторым управляющим входом блока регулирования, а выход с вторьм входом логического элемента И-ЫЕ, управляюгаий вход аналогового ключа соединен с выходом блока защиты.

2, Регулятор по п.1, отличающийся тем, что блок защиты содержит КЯ-триггер, три компаратора, перемножитель, блок опорных па-пряже20

но с установочными входами RS-триг-- гера, выход коммутационного элемента соединен с входом сброса триггера, первые входы компараторов соединены соответственно с выходами блока опорных напряжений, второй вход первого компаратора соединен с первым выходом перемножителя и является первым входом блока защиты, второй вход второго компаратора соединен с вторым входом перемножителя и является вторым входом блока защиты, второй вход третьего компаратора соединен с выхо- дом перемножителя, выход триггера является выходом блока защиты.

;--

az2

| Авторское свидетельство СССР № 915070, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Фонкенберн Л | |||

| Применение операционных усилителей и линейных интегральных схем.-М.: Мир, 1985, с.245- 246, рис.9.86. | |||

Авторы

Даты

1988-10-23—Публикация

1987-04-13—Подача