4 00 rsd

sj

Ч

114

Изобретение относится к вычислительной и измерительной технике и может быть использовано в системах автоматического регулирования технологическими процессами.

Цель изобретения - повышение точности и функциональной надежности.

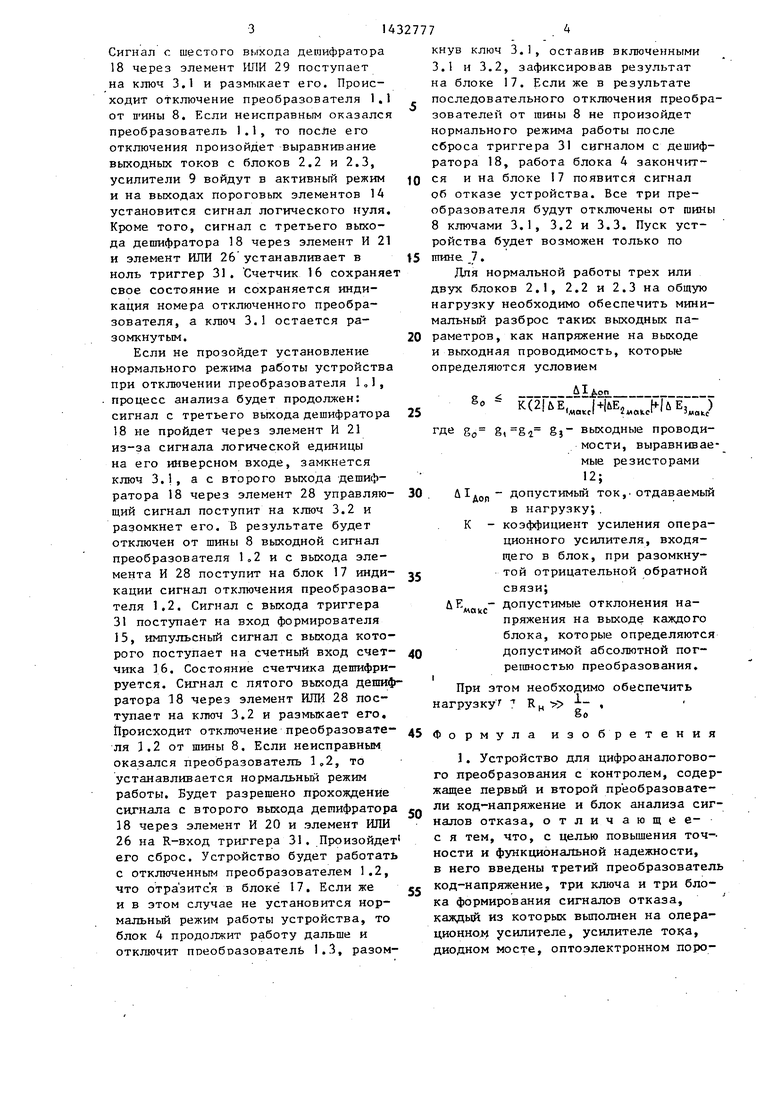

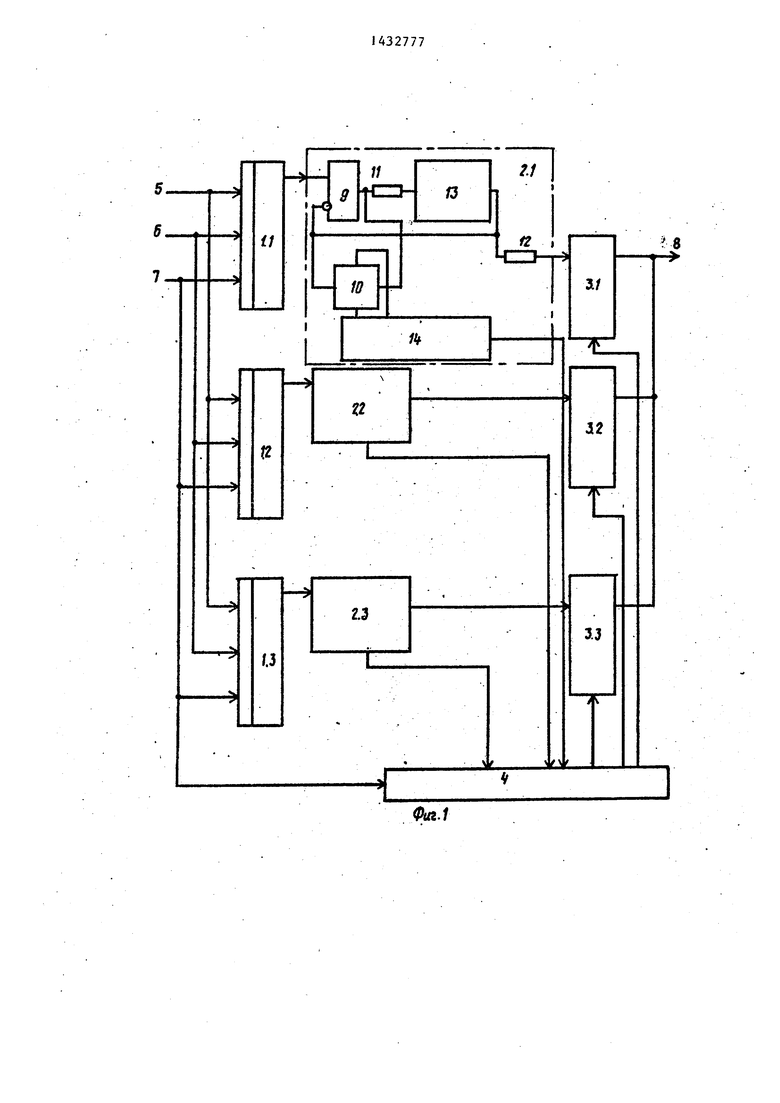

На фиг. 1 приведена функциональная схема устройства; на фиг, 2 - пример реализации блока анализа сигналов отказа.

- Устройство содержит три преобразователя 1.1, 1.2 и 1.3 код-налряже- ние, три блока 2.1, 2.2 и 2.3 формирования сигналов отказа, три ключа 3.1, 3.2 и 3.3, блок 4 анализа сигналов отказа, входную информационную шину 5, шину 6 управления, шину 7 Начальная установка и выходную шину 8.

Блок 2 формирования сигналов отказа -(фиг,) содержит операционньй усилитель 9, диодный мост 10,/токо- огранич1шающий 11 и токовыравниваю- щий 12 элементы, выполненные на резисторе, усихштель 13 тока и опто- электронньш пороговьй элемент 14.

Блок 4 анализа сигналов отказа (фиг. 2) содержит формирователь 15 импульсов, счетчик 16 импульсов, : блок 17 индикации, дешифратор 18, элементы И 19-21, элементы ИЛИ 22-29 и RS-триггеры 30 и 31.

Устройство работает следующим образом.

Начальная установка устройства осществляется сигналом, поступающим по шине 7. При этом обнуляются регистры преобразователей 1.1, 1.2 и 1.3, в блоке 4 обпулится счетчик IBiW на выходах блока 4 установятся сигналы нулевого потенциала, открьгоающие ключи 3. 1 , 3.2 и 3.3.

Преобразуемый код с шины 5 поступает параллельно на входы первого 1. второго J.,2 и третьего 1 ..3 преобразователей. Сигналом по 6 он одновременно записьгоается в преобразователи. Аналоговый сигнал с выхода ка;кдого преобразователя поступает на вход соответствуилцего блока формирования сигналов отказа (2.1, 2,2, 2.3 В блоке сигнал поступает на неинвер- тирзтощ1й вход операционного усилителя 9, с выхода которого через резистор 11 поступает на усилитель 13 тока, где усиливается по мо,щности без изменения входного напряжения, и

10

5

20

25

через резистор 12 поступает на ключ 3.

Если выходной сигнал преобразователей находится в пределах допустимых погрешностей для данного устройства, сигнал с диодного моста 10 будет лежать ниже уровня срабатьшаиия порогового элемента 14, что свидетельствует об исправности преобразователей код-напряжение, и имеет место нормальньй режим работы.

На входах элементов ИЛИ 22-24 блока 4.при этом сохранится сигнал нулевого уровня и такие же сигналы будут на выходе блока, т.е. ключи 3,1, 3,2 и 3.3 остаются открытыми. В результате аналоговые сигналы с выходов преобразователей пройдут через ключи на шину 8, где произойдет их усреднение.

Если напряжение на выходе хотя бы одного из преобразователей будет отличаться от номинального на величину допустимой погрешности, то произойдет перераспределение выходных токов блоков 2,1, 2.2 и 2.3, операционные усилители 9 войдут в насыщение; а в диодном мосте 10 каждого 30 блока возникает ток, вызьюающий сра- батьшание порогового элемента 14, с выхода которого поступит сигнал отказа в блок 4, Срабатьюание пороговых элементов свидетельствует о нарушении нормального режима работы устройства,

В функции блока 4 входит выявление неисправного преобразователя код-напряжение, отключение его от выхода устройства, выдача информации об аварийной ситуации и номере неисправного преобразователя с целью ло кализации неисправности. Дри этом, если отказал один преобразователь из трех, устройство сохраняет работоспособность, БлЪк 4 при этом работает следукяцин образом. Сигпал отказа с блоков 2. Г, 2.2 и 2.3 -через элементы ИЛИ 22-25 поступает на S- входы RS-триггеров 30 и 31 и устанавливает их в единичное состояние,, Сигнал с выхода триггера 30 поступает на вход блока 17 для отражения отключения преобразователя 1.1. Сигнал с выхода триггера 31 поступает на вход формирователя 15, имлуль- сный сигнал с выхода которого прсту- пает иа счетный вход счетчика 16. Состояние счетчика дешифрируется.

5

0

5

0

5

Сигнал с шестого выхода дешифратора 18 через элемент ИЛИ 29 поступает на ключ 3.1 и размыкает его. Происходит отключение преобразователя 1.1 от п ины 8. Если неисправным оказался преобразователь 1.1, то после его отключения произойдет выравнивание выходных токов с блоков 2.2 и 2.3, усилители 9 войдут в активный режим и на выходах пороговых элементов 14 установится сигнал логического нуля. Кроме того, сигнал с третьего выхода дешифратора 18 через элемент И 21 и элемент ИЛИ 26 устанавливает в ноль триггер 31. Счетчик 16 сохраняе свое состояние и сохраняется индикация номера отключенного преобразователя, а ключ 3.1 остается разомкнутым.

Если не прозойдет установление нормального режима работы устройства при отключении преобразователя 1,1, процесс анализа будет продолжен: сигнал с третьего выхода дешифратора 18 не пройдет через элемент И 21 из-за сигнала логической единицы на его инверсном входе, замкнется ключ 3.1, ас второго выхода дешифратора 18 через элемент 28 управляю- щий сигнал поступит на ключ 3.2 и разомкнет его. В результате будет отключен от шины 8 выходной сигнал преобразователя 1о2 и с выхода элемента И 28 поступит на блок 17 инди- кации сигнал отключения преобразователя 1.2. Сигнал с выхода триггера 31 поступает на вход формирователя 15, импульсный сигнал с выхода которого поступает на с четный вход счет- чика 16, Состояние счетчика дешифрируется. Сигнал с пятого выхода дешифратора 18 через элемент ИЛИ 28 поступает на ключ 3.2 и размыкает его. Происходит отключение преобразовате- ля 1.2 от шины 8. Если неисправным оказался преобразователь 1,2, то устанавливается нормальный режим работы. Будет разрешено прохождение сигнала с второго выхода дешифратора 18 через элемент И 20 и элемент ИЛИ 26 на R-вход триггера 31. Произойдет его сброс. Устро-йство будет работать с отключенным преобразователем 1.2, что отразится в блоке 17. Если же и в этом случае не установится нормальный режим работы устройства, то блок 4 продолжит работу дальше и отключит преобразователь 1.3, разом

10

ts

20

25 30 « 40j« 27774

кнув ключ 3.1, оставив включенными 3.1 и 3.2, зафиксировав результат на блоке 17. Если же в результате последовательного отключения преобразователей от шины 8 не произойдет нормального режима работы после сброса триггера 31 сигналом с дешифратора 18, работа блока 4 закончится и на блоке 17 появится сигнал об отказе устройства. Все три преобразователя будут отключены от шины 8 ключами 3.1, 3.2 и 3.3. Пуск устройства будет возможен только по гаине 7.

Для нормальной работы трех или двух блоков 2.1, 2.2 и 2.3 на общую нагрузку необходимо обеспечить минимальный разброс таких выходных параметров, как напряжение на выходе и выходная проводимость, которые определяются условием

е

00

.

К K(,,HuEs«J де g g,g gj- выходные проводимости, выравниваемые резисторами 12; UI. допустимый ток,, отдаваемый

в нагрузку;.

коэффициент усиления операционного усилителя, входящего в блок, при разомкнутой отрицательной обратной связи;

допустимые отклонения напряжения на выходе каждого блока, которые определяются допустимой абсолютной погрешностью преобразования.

ЛЕ

маис

При ЭТОМ необходимо обеспечить

нагрузку

Формула изобретения

1. Устройство для цифроаналогового преобразования с контролем, содержащее первый и второй преобразователи код-налряжение и блок анализа сигналов отказа, отличающее- с я тем, что, с целью повьш1ения точ-- ности и функциональной надежности, в него введены третий преобразователь код-напряжение, три ключа и три блока формирования сигналов отказа, каждый из которых вьтолнен на операционном усилителе, усилителе тока, диодном мосте, оптоэлектронном пороговом элементе и токоограличивагацем- и токовыравнивающем элементах, выполненных соответственно на первом и ;втором резисторах, nptf4eM одвшимен- :ные Ш1формационные входы первого, ;второго и третьего преобразователей код-напряжение объединены и образуют входную информационную шину, уп- ;равля1ощие входы объединены и являют- ;ся шиной управления устройства, ,а |установочные входы объединены с пер- |Вьтм входом блока анализатора сигна- |лов отказа и являются шиной Началь- ная установка, выход каждого 1-го |преобразователя код-напряжение (i 1, 2, 3) соединен с неинвертирующим входом операционного усилителя i-ro |блока формирования сигналов отказа, :выход операционного усилителя соединен с первым входом диодного моста ill с- первым вьшодом первого резистора |второй вьшод которого соединен с пхо |дом усилителя тока, выход которого |Соединен с инвертирующим входом опе- |рационпого усилителя, с первым выводом второго резистора и с вторым :входом диодного моста, первый и вто- :рой выходы которого соединены соответственно с первым и вторым входами оптоэлектронного порогового элемента, выходы оптоэлектронных пороговых :Элементов первого, второго и третьего блоков формирования сигнааюв от- каза соединены соответственно с вторым, третьим и четвертым входами блока анализа сигналов отказа, первый, второй и третий вькоды которого соединены с управляющими входами первого, второго и третьего ключей соответственно, информационные входы которых соединены с вторьми вьгоодами вторых: резисторов соответственно лер вого, второго и третьего блоков формирования сигналов отказа, выходы первого, второго и третьего кгаочей объединены и являются вьгходной: шиной

2, Устройство по По 1, о т л и- чающееся тем, что, с целью обеспечения возможности локализации неисправности, блок анализа .сигналов отказа содержит формирователь им лульсов, счетчик импульсов, блок индикации, три элемента И, восемь

элементов ИЛИ ,и дешифратор, входы которого соединены с соответствзпо- щими вькодами счетчика импульсов, первый, второй и третий выходы соединены с прямыми входами соответственно первого, второго и третьего элементов И, объединенными с первыми входами соответственно первого,

второго и третьего элементов ИЛИ, вторые входы которых подключены соответственно к четвертому, пятому и шестому выходам дешифратора, а выходы являются соответственно первым, вторым

и третьим в ыходами блока и соединены с первым, вторым и третьим входами блока индикации соответственно, седьмой выход дешифратора соед инен с первым входом четвертого элемента ИЛИ

и с четвертым входом блока индикации, пятьй вход которого подключен к выходу первого RS-триггера, R-вход которого, объединенный с вторым входом четвертого элемента 1-ШИ и с входом

Сброс счетчика, является первым входом блока, а S-вход, объединенный с S-входом второго RS-триггера, подключен к входу пятого элемента ИЛИ, первьш, второй и третий входы которого, объединенные с инверсными

входами соответственно первого, второго и третьего элементов И, подключены к выходам соответственно шесто35

го, седьмого и восьмого элементов ИЛИ, первый вход шестого элемента

ИЛИ, объединенный с первым входом седьмого элемента ИЛИ, является вторым входом блока, второй вход шестого элемента ИЛИ, объединенный с пер40 вым входом восьмого элемента ИЛИ, является третьим входом блока, второй вход седьмого элемента ИЛИ, объединенный с вторым входом восьмого элемента ИЛИ, является четвертым

45 входом блока, выходы первого, второго и третьего элементов И соединены соответственно с третьим, четвертым и пятым входами четвертого элемента ИЛИ, выход которого соединен с RgQ входом второго триггера, выход которого соединен с входом формирователя импульсов, выход которого соединен со счетным входом счетчика импульсов о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU868843A1 |

| Устройство для передачи телеизмерений | 1982 |

|

SU1018140A2 |

| Устройство приоритетного выбора непрерывного дискретизированного сигнала по принципу "большинства | 1984 |

|

SU1252937A1 |

| Многоканальный резервированный коммутатор | 1989 |

|

SU1737723A1 |

| Устройство для контроля параметров | 1985 |

|

SU1267437A1 |

| ДИСКРЕТНЫЙ ЭЛЕКТРОННЫЙ ЗАДАТЧИК ТЕМПЕРАТУРЫ | 1993 |

|

RU2067358C1 |

| Резервированный усилитель амплитудно-модулированных сигналов | 1985 |

|

SU1378096A1 |

| СЕЛЕКТОР СИГНАЛОВ ПО ДЛИТЕЛЬНОСТИ | 1990 |

|

RU2028027C1 |

| ВСЕСОЮЗНАЯ Л. А. Шойхет, А. С. Белима, А. Г. Мелик-Аскаров, }j^,..^,..,.. ^^^,,,,.,.^^В. М. Гаврилюк, Б. И. Семеняк и А. А. Казьмина р^"—"!Н1'~1':ХН'''-;5\?{ЛЯ | 1970 |

|

SU287550A1 |

| Устройство для стабилизированного питания приемников энергии | 1987 |

|

SU1545290A1 |

Изобретение относится к вычислительной и измерительной технике и может быть использовано в системах автоматического регулирования технологическими процессами. Изобретение позволяет повысить точность и функциональную надежность цифроаналогового преобразования з.а счет усреднения выходного сигнала трех параллельно работающих преобразователей код-напряжение и обнаружения неисправности при выходе аналогового сигнала за пределы номинального значения на величину допустимой погрешности с отключением неисправного преобразователя Устройство позволяет выявить отказы не только катастрофического характера, но и медленные отказы 1 з.п, ф-лы, 2 ил.S

| Устройство контроля работоспособности | 1972 |

|

SU469212A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство парафазного цифроаналогового преобразования с самоконтролем | 1976 |

|

SU668087A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-10-23—Публикация

1987-01-19—Подача