Изобретение относится к вычислительной технике и может быть использовано для построения параллельных коммутационных устройств в универсальных системах и структурах высокой производительности, ориентированных на реализацию в виде СБИС.

Целью изобретения является повышение надежности работы устройства.

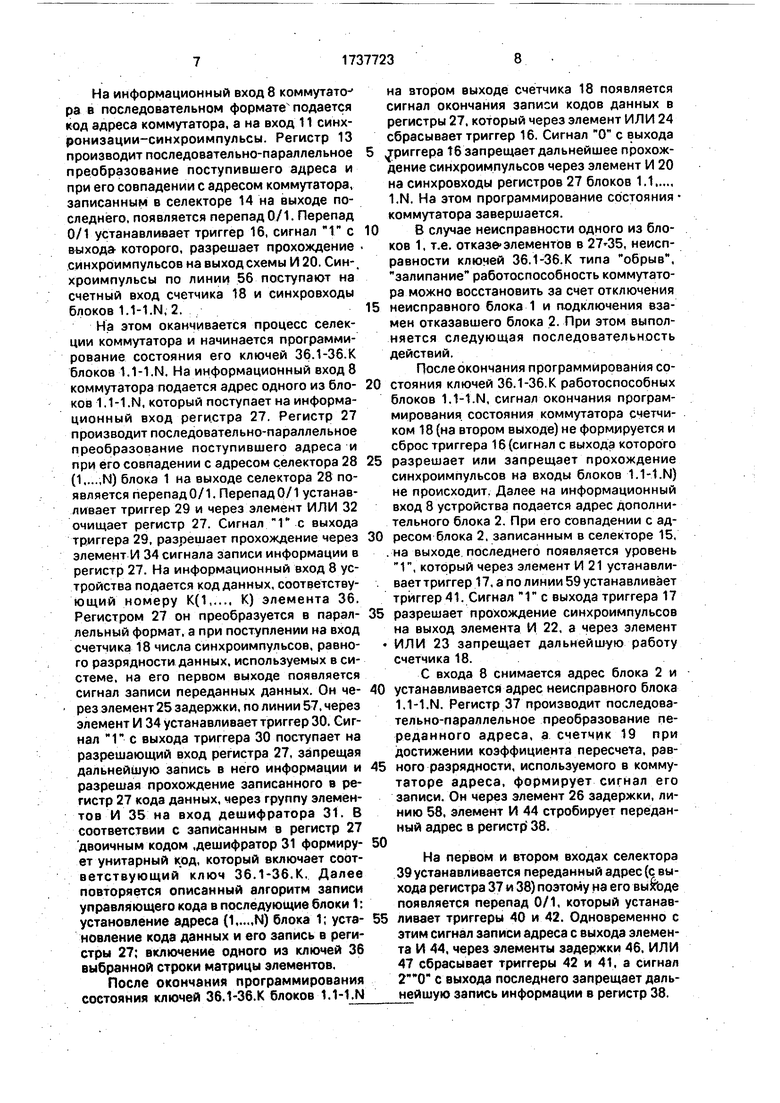

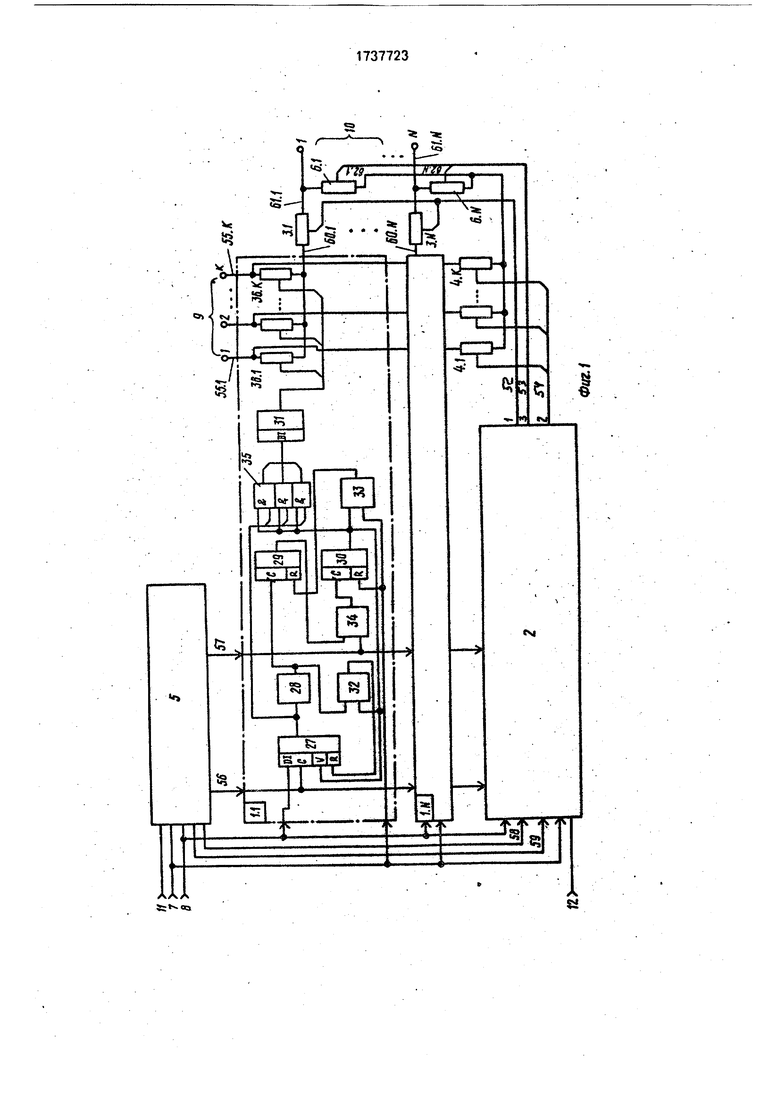

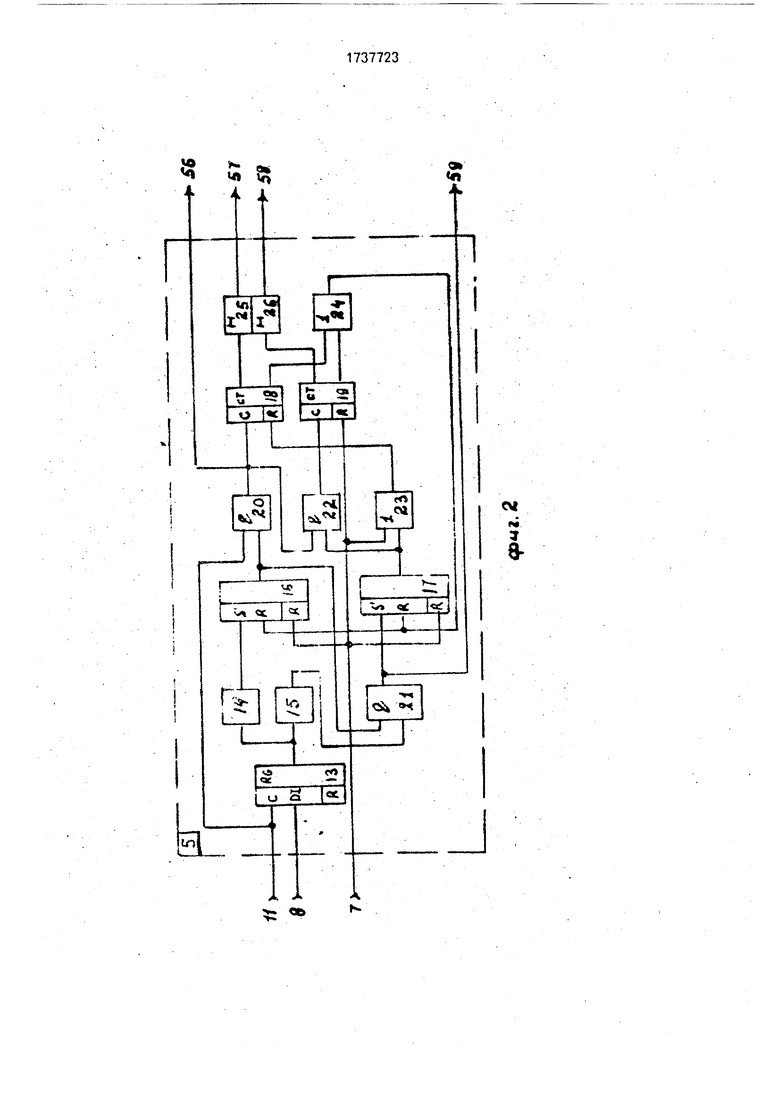

На фиг.1 представлена функциональная схема многоканального коммутатора; на фиг.2 - функциональная схема адресного дешифратора; на фиг.З - функциональная схема дополнительного блока.

Многоканальный коммутатор содержит N основных блоков 1.1-1.N, дополнительный блок 2, первую группу ключевых элементов, содержащую N ключей 3.1-3.N, вторую группу ключевых элементов, содержащую К ключей 4.1-4.К, адресный дешифратор 5, третью группу ключевых элементов, содержащую N ключей 6.1-6.N, вход 7 начальной установки, информационный вход 8, входную шину 9, выходную шину 10, вход 11 синхронизации, дополнительный вход 12 начальной установки.

Адресный дешифратор 5 содержит регистр 13, первый 14, второй 15 адресные селекторы, первый 16, второй 17 триггеры, первый 18, второй 19 счетчики, пеовый 20. второй 21, третий 22 элементы И, первый 23, второй 24 элементы ИЛИ, первый 25, второй 26 элементы задержки.

Основной блок 1 содержит регистр 27, адресный селектор 28, первый 29 и второй 30 триггеры, дешифратор 31, первый 32, второй 33 элементы ИЛИ, элемент И 34, группу элементов И 35, К ключей 36.1-36.К.

Дополнительный блок 2 содержит первый 37 и второй 38 регистры, адресный селектор 39, первый 40, второй 41, третий 42, четвертый 43 триггеры, первый 44, второй - 45 элементы И, элементы 46 задержки, ИЛИ 47, первую 48, вторую 49 группы элементов

со

с

VI

СА) VI XJ Ю СА

И. первый 50, второй 51 дешифраторы. Уп- равляющие входы ключей 3.1-3.N соединены с первой выходной шиной 52 дополнительного блока 2, выходы ключей 4.1-4.К объединены, а управляющие входы (линии 53.1-53.К) образуют шину 54 и соединены с второй выходной шиной дополнительного блока 21. Вход 7 начальной установкпи, информационный вход 8, входная шина 9 (образованная линиями 55.1- 55.К) основных 1.1-1.М- и дополнительного 2 блоков соединены с одноименным входом и шинами многоканального коммутатора. Входы адресного дешифратора 5 начальной установки 7, синхронизации 11, а также информационный вход 8 соединены с одноименными входами многоканального коммутатора, выходы дешифратора 5 синхронизации - линия 56, записи данных - линия 57 и адресов - линия 58, разрешения работы - линия 59 связаны с соответствующими входами дополнительного 2 и основных блоков 1.1-1.N, выходы блоков 1.1-1.N, линиями 60.1-60.N соединены с входами одноименных ключей 3.1-3.N, выходы которых линии 61.1-61.N образуют выходную шину 10 и связаны с выходами ключей 6.1-6.N, входы которых объединены и связаны с выходами ключей 4.1-4.К. Управляющие входы ключей 6.1-6.N, линии 62.1-62N образуют шину 63 и соединены с третьей выходной шиной дополнительного блока 2, дополнительный вход 12 начальной установки которого .является одноименным входом многоканального коммутатора.

Информационный вход 8 и вход 11 синхронизации адресного дешифратора 5 под- ключенысоответственнок

информационному входу регистра 13 и его входу синхронизации, соединенного, кроме того, с первым входом элемента И 20. выход регистра 13 через адресный селектор 14 соединен с единичным входом триггера 16, а через адресный селектор 15, элемент И 21 - с единичным входом триггера 17. выход которого связан с первыми входами элемента ИЛИ 23. выход которого соединен с входом нулевой начальной установки счетчика 18 и элемента И 22. Выход элемента И 22 подключен к счетному входу счетчика 19, выход триггера 16 соединен с входами элементов И 20 и 21, выход элемента И 20 связан со счетным входом счетчика 18 и вторым входом элемента И 22, выход которого соединен со счетным входом счетчика 19, первые выходы счетчиков 18 и 19 через элементы 25 и 26 задержки соответственно соединены с выходами записи адресов и данных дешифратора 5. Вторые выходы счетчиков 18 и 19, подключены к входам элемента ИЛИ 24, выход элемента ИЛИ 24 связан с нулевым входом триггерова 16 и 17, Вход начальной установки дешифратора 5 соединен с нулевым входом начальной установки триггеров

4$ и 17- счетчика 19, вторым входом элемента ИЛИ 23, выходы элементов И 20 и 21 являются выходами дешифратора 5 синхронизации работы и разрешения работы соответственно.

0 В каждом из блоков 1.1-1.N информационный и вход синхронизации соединен соответственно с одноименным входом 8 коммутатора и выходом синхронизации, линия 56 дешифратора 5 подключена к одно5 именным входам регистра 27, выходы которого соединены с соответствующими первыми входами группы элементов И 35 и входом селектора 28. выход селектора 28 через элемент ИЛИ 32 соединен с входом

0 сброса регистра 27 и связан со счетным входом триггера 29, выход которого через элемент И 34 соединен со счетным входом триггера 30, выход триггера 30 соединен с разрешающим входом регистра 27, вторы5 ми входами группы элементов И 35, вторыми первыми входами соответственно элементов ИЛИ 32 и 33, выход последнего соединен с нулевым входом начальной установки триггера 29, выход группы элементов

0 И 35, соединен с входом дешифратора 31, выход которого связан с управляющими входами ключей 36.1-36.К, входы которых соединены с одноименными линиями 55.1- 55.К. а выходы объединены и являются вы5 ходом блока 1. В каждом из блоков 1.1-1.N вход начальной установки соединен с вто- рым входом элемента ИЛИ 33, нулевым входом начальной установки триггера 30, а вход блоков 1.1-1.N записи данных линией 57 со0 единен с вторым входом соответствующего элемента И 34.

Входы информационный и синхронизации блока 2 подключены к одноименным входам регистра 37, выход которого соеди5 ней с первыми входами селектора 39, второй группы элементов И 49, информационным входом регистра 38, выход регистра 38 связан с первым входами группы элементов И 48 и через селектор 39

0 со счетными входами триггеров 40 и 42. Вход разрешения работы блока 2 связан со счетным входом триггера 41, выход которого через элемент И 44 соединен с входом записи регистра 38 и через элементы 46

5 задержки, ИЛИ 47 соединен с входами сброса триггера 41 и 42. выход последнего через элемент И 45 связан со счетным входом триггера 43, выход которого подключен к разрешающему входу регистра 37 и вто- рым входам группы элементов И 49. Выход

группы элементов И 49 через дешифратор 51 подключен к второму выходу блока 2, выход группы элементов И 48 соединен с дешифратором 50, прямой и инверсный выходы которого являются соответственно первым и третьим выходом блока 2. Входы блока 2 адресов и данных соединены с вторыми входами элементов И 44 и 45 соответственно, вход начальной установки связан с входами сброса регистра 37, триггера 43, вторым входом элемента ИЛИ 47, дополнительный вход 12 начальной установки подключен к входам сброса регистра 38, триггера 40.

Адресный дешифратор 5 предназначен

для селекции А (1 А) многоканального

коммутатора и формирования сигналов, управляющих его работой (А - общее число используемых в системе многоканальных коммутаторов).

Первая группы ключей 3.1-3.N предназначена для отключения отказавших ключевых элементов любого из блоков 1.1-1.N от выходной шины 10 коммутатора.

Третья группа ключей 6.1-6.N предназначена для подключения резервной группы ключей 4.1-4.К взамен отказавших ключевых элементов любого из блоков 1.1-1.N к выходной шине 10 коммутатора. Вход 7 служит для приема сигналов начальной установки блоков коммутатора, вход 8 - приема сигналов адресов и данных, вход 11 - приема сигналов синхронизации работы адресного дешифратора 5, вход 12 - приема сигналов стирания адреса отказавшего 1.1- 1 .Nрсновного блока.

Регистры 13, 27 и 37 служат для последовательно-параллельного преобразования кода данных и адресов: селектор 14 селекция адреса А (1А) многоканального

коммутатора; селектор 15 - селекция адреса дополнительного блока 2; триггера 16 - формирования сигнала разрешения прохождения синхроимпульсов, при выборке А (1,..,, А) многоканального коммутатора, на выход дешифратора 5; триггер 17 -формирования сигнала блокировки работы счетчика 18; счетчик 18 - формирования сигналов записи данных (выход 1) и окончания программирования структуры связей ключей основных блоков (выход 2); счетчик 19 - формирования сигналов записи адресов отказавших 1.1-1.N блоков (выход 1) и окончания записи адреса отказавших блоков (выход 2).

Коэффициент пересчета счетчика 18 по первому выходу равен разрядности передаваемых данных, а по второму выходу-числу используемых в коммутаторе основных блоков 1.1-1.N. Элемент 25 задержки служит для формирования сигнала записи данных

в регистры 27 и 37 в момент времени окончания его преобразования регистрами из последовательного формата в параллельный, элемент 26 задержки - формирования 5 сигнала записи адреса отказавшего блока 1.1-1.N в момент времени окончания его преобразования из последовательного фор- мата в параллельный, селектор 28 - селекции адреса блока 1.1-1.N, триггер 29 - 0 формирования сигнала разрешения прохождения импульса записи данных, триггер 30 - формирования сигналов запрета работы регистра 27, регистр 38 - запоминания кода адреса неисправного 1.1-1.N блока, се- 5 лектор 38 - селекции адреса блока 1.1-1.N при работе коммутатора с дополнительным блоком 2, триггер 40 - разрешения прохождения кода адреса неисправного блока 1.10 1.N на вход дешифратора 50, триггер 41 - разрешения прохождения импульса записи кода адреса отказавшего 1.1-1.N блока; триггер 42 - разрешения прохождения импульса записи данных, триггер 43 - запрета

5 работы регистра 37 и разрешения прохождения кода данных на вход дешифратора 51, дешифратора 50 - формирования двоичных кодов управляющих отключением (шина 52) и подключением (шина 63)

0 неисправных ключевых элементов (ключей) 36.1-36.К к цепям выхода устройства, дешифратор 51 - формирования кодов управления резервной строкой ключей 4.1-4,К (шина 54, линии 53.1-53.К). Линия 56 служит

5 для передачи сигналов синхронизации работы основных 1.1-1.N и дополнительного 2 блоков, линия 57 - сигналов записи данных, линия 58 - сигналов записи адреса отказавшего блока 1.1-1.N, линия 59 - сигнала раз0 решения работы дополнительного блока 2. В начальный момент времени на выходе селекторов 14, 15, 28 и 39, триггеров 16, 17, 29, 30, 41, 42 и 43, счетчиков 18 и 19, регистров 13,27, 37 и 38 находится уровень

5 О. В начальный момент времени элементы 3.1-3.N находятся в замкнутом состоянии, элементы 6.1-6.N в разомкнутом состоянии. Наиболее полно положительный эффект предполагаемого устройства проявит0 ся при его реализации в виде БИС. При этом адресные селекторы представляют собой широко известную комбинационную схему на основе вентилей И, ИЛИ, триггеры, регистры - последовательные схемы на базе

5 аналогичных вентилей с обратными связями, дешифраторы могут представлять ПЛМ, в качестве ключевых релейных элементов могут быть применены полевые структуры. Многоканальный резервированный коммутатор работает следующим образом.

На информационный вход 8 коммутато- ра в последовательном формате4 подается код адреса коммутатора, а на вход 11 синх- ронизации-синхроимпульсы. Регистр 13 производит последовательно-параллельное преобразование поступившего адреса и при его совпадении с адресом коммутатора, записанным в селекторе 14 на выходе последнего, появляется перепад 0/1. Перепад 0/1 устанавливает триггер 16, сигнал 1 с выход которого, разрешает прохождение синхроимпульсов на выход схемы И 20. Синхроимпульсы по линии 56 поступают на счетный вход счетчика 18 и синхровходы блоков 1.1-1.N,2.

На этом оканчивается процесс селекции коммутатора и начинается программирование состояния его ключей 36.1-36.К блоков 1.1-1.N. На информационный вход 8 коммутатора подается адрес одного из блоков 1.1-1.N, который поступает на информационный вход регистра 27. Регистр 27 производит последовательно-параллельное преобразование поступившего адреса и при его совпадении с адресом селектора 28 (1N) блока 1 на выходе селектора 28 появляется перепад 0/1. Перепад 0/1 устанавливает триггер 29 и через элемент ИЛИ 32 очищает регистр 27. Сигнал 1 с выхода триггера 29, разрешает прохождение через элемент И 34 сигнала записи информации в регистр 27. На информационный вход 8 устройства подается код данных, соответствующий номеру К(1 К) элемента 36.

Регистром 27 он преобразуется в параллельный формат, а при поступлении на вход счетчика 18 числа синхроимпульсов, равного разрядности данных, используемых в системе, на его первом выходе появляется сигнал записи переданных данных. Он через элемент 25 задержки, по линии 57, через элемент И 34 устанавливает триггер 30. Сигнал Г с выхода триггера 30 поступает на разрешающий вход регистра 27, запрещая дальнейшую запись в него информации и разрешая прохождение записанного в регистр 27 кода данных, через группу элементов И 35 на вход дешифратора 31. В соответствии с записанным в регистр 27 двоичным кодом .дешифратор 31 формирует унитарный код, который включает соответствующий ключ 36.1-36.К. Далее повторяется описанный алгоритм записи управляющего кода в последующие блоки 1: установление адреса (1,..„М) блока 1; установление кода данных и его запись в регистры 27; включение одного из ключей 36 выбранной строки матрицы элементов.

После окончания программирования состояния ключей 36.1-36.К блоков 1.1-1.N

на втором выходе счетчика 18 появляется сигнал окончания записи кодов данных в регистры 27. который через элемент ИЛИ 24 сбрасывает триггер 16. Сигнал О с выхода

риггера t6 запрещает дальнейшее прохождение синхроимпульсов через элемент И 20

на синхровходы регистров 27 блоков 1.1

1.N, На этом программирование состояния- коммутатора завершается.

0 В случае неисправности одного из блоков 1, т.е. отказе- элементов в , неисправности ключей 36.1-36.К типа обрыв, залипание работоспособность коммутатора можно восстановить за счет отключения

5 неисправного блока 1 и подключения взамен отказавшего блока 2. При этом выполняется следующая последовательность действий.

После окончания программирования со0 стояния ключей 36.1-36.К работоспособных блоков 1.1-1.N, сигнал окончания программирования состояния коммутатора счетчиком 18 (на втором выходе) не формируется и сброс триггера 16 (сигнал с выхода которого

5 разрешает или запрещает прохождение синхроимпульсов на входы блоков 1.1-1.N) не происходит. Далее на информационный вход 8 устройства подается адрес дополнительного блока 2. При его совпадении с ад0 ресом блока 2. записанным в селекторе 15, . на выходе последнего появляется уровень 1, который через элемент И 21 устанавливает триггер 17, а по линии 59 устанавливает триггер 41. Сигнал Г с выхода триггера 17

5 разрешает прохождение синхроимпульсов на выход элемента И 22, а через элемент ИЛИ 23 запрещает дальнейшую работу счетчика 18.

С входа 8 снимается адрес блока 2 и

0 устанавливается адрес неисправного блока 1.1-1.N. Регистр 37 производит последовательно-параллельное преобразование переданного адреса, а счетчик 19 при достижении коэффициента пересчета, рав5 ного разрядности, используемого в коммутаторе адреса, формирует сигнал его записи. Он через элемент 26 задержки, линию 58, элемент И 44 стробирует переданный адрес в регистр 38.

0

На первом и втором входах селектора 39 устанавливается переданный адрес (с выхода регистра 37 и 38) поэтому на его выводе появляется перепад 0/1, который устанав5 ливает триггеры 40 и 42. Одновременно с этим сигнал записи адреса с выхода элемента И 44, через элементы задержки 46, ИЛИ 47 сбрасывает триггеры 42 и 41, а сигнал с выхода последнего запрещает дальнейшую запись информации в регистр 38.

Записанный в регистр 38 адрес (1N)

неисправного блока 1,через группу элементов 48 поступает на вход дешифратора 50. В соответствии с поступившим адресом с первого выхода дешифратора 50 по шине 52 передается унитарный код, который отключает ключом 3.1-3.N неисправную N(1N)

строку ключей 36.1-36.К от выходной шины 10. На третьем выходе дешифратора 50 устанавливается код, инверсный коду на его первом выходе. В соответствии с ним резервная строка ключей 4 через ключи 6.1-6.N подключается к выходной шине 10. После передачи адреса отказавшего блока 1.1-1.N на втором выходе счетчика 19 формируется сигнал окончания передачи адреса, который через элемент ИЛИ 24 сбрасывает триггеры 16 и 17. Сигнал О с выходов триггеров 16 и 17 блокирует дальнейшую работу коммутатора (так как запрещается подача синхро- импульсов в блоки 1 и 2 коммутатора).

Дальнейшая работа коммутатора с восстановленной работоспособностью аналогична рассмотренному.

На вход 8 коммутатора подается его ад- рее, а затем адреса основных блоков 1.1....1.N. При поступлении адреса неисправного блока 1.1-1.N с работоспособностью, восстановленной с помощью блока 2, коммутатор работает следующим образом.

Регистр 37 производит последовательно-параллельное преобразование поступившего кода адреса, в соответствии с которым на выходе селектора 39 появляется перепад 0/1. Он устанавливает триггер 42, уровень 1 с выхода которого разрешает прохождение сигналов записи данных через элемент И 46. На входе 8 устанавливается код данных, регистр 37 преобразует его в параллельный формат, а по линии 57 счет- чик 18 формирует сигнал его записи. Он через элемент И 45 устанавливает триггер 43, сигнал 1, с выхода которого подается на вторые входы элементов И 49 и запрещает работу регистра 37. Записанный в ре- гистр 37 код данных через первые входы группы элементов И 49 поступает на вход дешифратора 51. В соответствии с поступившим кодом дешифратор 51 формирует унитарный код, который включает один из ключей 4.1-4.К.

Формула изобретения

Многоканальный резервированный коммутатор, содержащий N блоков коммутации, дополнительный блок коммутации, первую группу N ключей, вторую группу К ключей, входы начальной установки, информационных N блоков коммутации, дополнительного блока коммутации и входные шины N блоков коммутации соединены с одноименными входами и входной шиной многоканального коммутатора соответственно, управляющие входы первой группы ключей соединены с первой выходной шиной дополнительного блока коммутации, одноименные входные шины соединены с соответствующими входами второй группы ключей, выходы последних объединены, а управляющие входы соединены с второй выходной шиной дополнительного блока коммутации, причем каждый блок коммутации содержит регистр, адресный селектор, первый триггер, дешифратор, первый, второй элементы ИЛИ. элемент И, К ключей, выход адресного селектора соединен с первым входом одноименного элемента ИЛИ нечетным входом первого триггера, выход последнего соединен с первым входом элемента И, выход дешифратора соединен с управляющими входами К ключей, входы которых соединены с соответствующими входными шинами, выходы объединены и являются выходом блока коммутации, информационный вход последнего подключен к одноименному входу регистра, вход начальной установки блока коммутации подключен к первому входу второго элемента ИЛИ, вход записи данных блока коммутации связан с вторым входом элемента И, при этом дополнительный блок коммутации содержит первый и второй регистры, адресный селектор, первый и второй триггеры, элементы И, элемент ИЛИ, первый и второй дешифраторы, выход адресного селектора соединен со счетным входом первого триггера, выход элемента ИЛИ соединен с нулевым входом начальной установки второго триггера, а его первый вход подключен к входу начальной установки дополнительного блока коммутации, соединенного, кроме того, с входом нулевой начальной установки первого регистра, информационный вход которого подключен к информационному входу дополнительного блока коммутации, а прямые выходы первого и второго дешифраторов являются одноименными выходами дополнительного блока коммутации, отличающийся тем, что, с целью повышения надежности, в него введен адресный дешифратор, третья группа N ключей, входы начальной установки, синхронизации, а также информационный вход адресного дешифратора соединены с одноименными входами многоканального коммутатора, выходы адресного дешифратора синхронизации, записи данных и адресов, разрешения работы связаны с соответствующими входами дополнительного блока коммутации и N блоков коммутации, выходы N блоков коммутации соединены с одноименными

входами N ключей первой группы, выходы которых связаны с одноименными цепями выходной шины многоканального коммутатора, соединенными с выходами одноименных ключей третьей группы, входы последних объединены и связаны с выходами второй группы ключей, а управляющие входы соединены с третьей выходной шиной дополнительного блока коммутации, дополнительный вход начальной установки которого является одноименным входом многоканального коммутатора, при этом адресный дешифратор содержит регистр, первый и второй адресные селекторы, первый и второй триггеры, счетчик, первый, второй и третий элементы И, первые и вторые элементы ИЛИ задержки, информационная шина и вход синхронизации адресного дешифратора подключены соответственно к информационному входу регистра и его входу синхронизации, соединенного, кроме того, с первым входом одноименного элемента И, выход регистра через первый адресный селектор соединен с единичным входом первого триггера, а через второй адресный селектор, второй элемент И - с единичным входом второго триггера, выход которого связан с первыми входами одноименного элемента ИЛИ, выход которого соединен с входом нулевой начальной установки первого счетчика, и третьего элемента И, выход которого подключен к счетному входу второго счетчика, выход первого триггера соединен с вторыми входами второго и первого элементов И, выход последнего связан со счетным входом первого счетчика и вторым входом третьего элемента И, выход которого соединен со счетным входом второго счетчика, первые входы первого и второго счетчиков через одноименные эле- менты задержки соединены с выходами за- писи адресов и данных адресного дешифратора, а вторые выходы счетчиков подключены к входам второго элемента ИЛИ, выход последнего связан с нулевым входом первого и второго триггеров, причем вход начальной установки адресного дешифратора соединен с нулевым входом начальной установки первого и второго триггеров, второго счетчика, вторым входом первого элемента ИЛИ, а выходы первого и второго элементов И являются выходами адресного дешифратора синхронизации работы и разрешения работы соответственно, причем в N блоков коммутации введены второй триггер, группа элементов И, синхровход блока соединен с одноименным входом регистра, нулевой вход начальной установки которого связан с выходом первого элемента ИЛИ, выходы регистра соединены с

«первыми входами группы элементов И и входом адресного селектора, выход второго триггера связан с разрешающим входом регистра, вторыми входами группы элементов И, вторым и первым входами соответственно первого и второго элемента ИЛИ, выход последнего соединен с нулевым входом начальной установки первого триггера, выход группы элементов И соединен с дешифратором, а вход начальной установки блока коммутации соединен с вторым входом одноименного элемента ИЛИ, нулевым входом начальной установки второго триггера, счетный вход которого соединен с выходом элемента И, кроме того, в дополнительный

блок коммутации введены третий и четвертый триггеры, первая и вторая группы элементов И, элемент задержки, выход первого регистра соединен с первыми входами адресного селектора, и второй группы элементов И, информационным входом второго регистра, выход которого связан с первыми входами первой группы элементов И и через адресный селектор соединен со счетным входом третьего триггера, вход разрешения

работы дополнительного блока коммутации подключен к счетному входу второго триггера, выход первого элемента И соединен с входом записи второго регистра и через элементы задержки, ИЛИ - с входом сброса

третьего триггера, выход последнего через второй элемент И связан со счетным входом четвертого триггера, выход которого подключен к разрешающему входу первого регистра, вторым входом одноименной

группы элементов И, выход которой соединен с входом второго дешифратора, выход первой группы элементов И соединен с первым дешифратором, инверсный выход которого является третьим выходом

дополнительного блока коммутации, причем входы дополнительного блока коммутации записи адресов и данных соединены с вторыми входами первого и второго элементов И соответственно, вход начальной установки связан с входом сброса четвертого триггера, вход синхронизации соединен с одноименным входом первого регистра, а дополнительный вход начальной установки подключен к входу нулевой начальной установки второго регистра и входу сброса первого триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ КОММУТАТОР | 1991 |

|

RU2026605C1 |

| Перестраиваемое логическое устройство | 1990 |

|

SU1815647A1 |

| Устройство для обмена информацией | 1979 |

|

SU842773A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ НА ГАЗОРАЗРЯДНОЙ ИНДИКАТОРНОЙ ПАНЕЛИ | 1993 |

|

RU2069018C1 |

| Устройство для ввода информации | 1982 |

|

SU1062683A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

| Система коммутации | 1985 |

|

SU1317448A1 |

| Устройство для сопряжения ведущей и N ведомых цифровых вычислительных машин | 1988 |

|

SU1531104A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения параллельных коммутационных устройств в универсальных системах и структурах высокой производительности, ориентированных на реализацию в виде СБИС. Целью изобретения является повышение надежности работы. В многоканальный резервированный коммутатор, который содержит N основных блоков, дополнительный блок и две группы ключевых элементов, введены адресный дешифратор, третья группа ключевых элементов, а также новые связи между указанными блоками. Введение новых элементов в основной и дополни- тельный блоки коммутации позволило осуществить надежное резервирование при выходе из строя любого из элементов блоков коммутации. 3 ил.

«.

ш.

SLL,

f

Ш1Ш

01

м

8

| Авторское свидетельство СССР № 1483623,кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-05-30—Публикация

1989-10-19—Подача