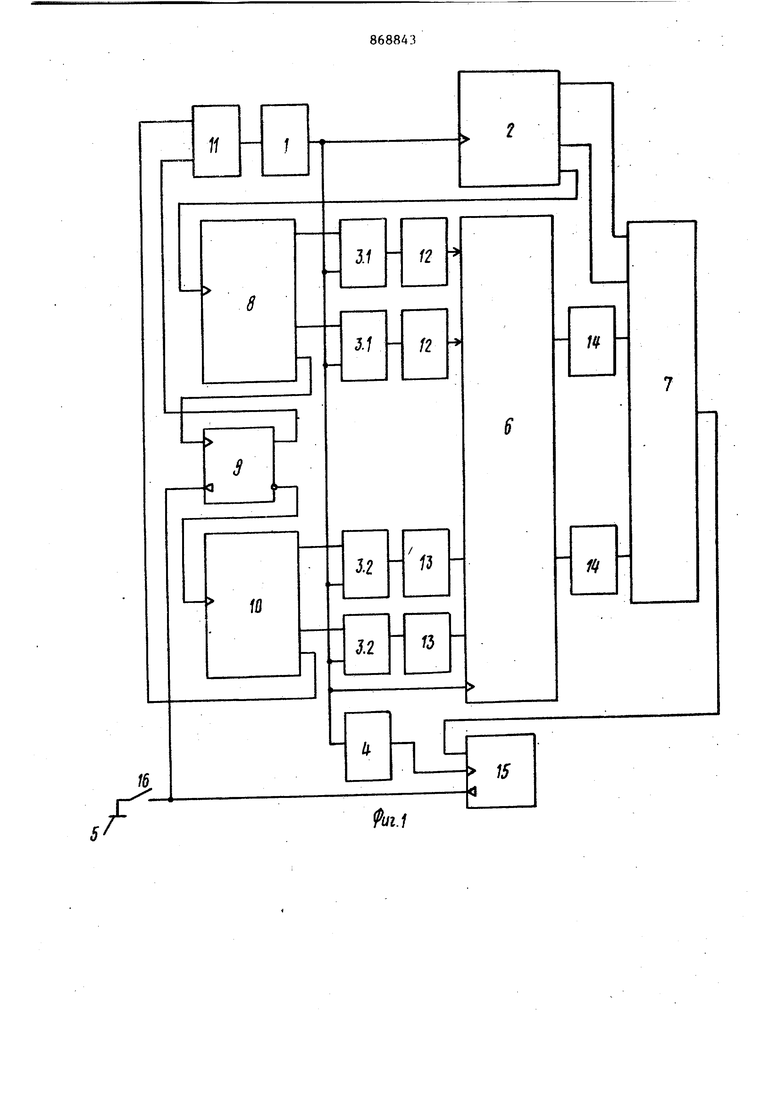

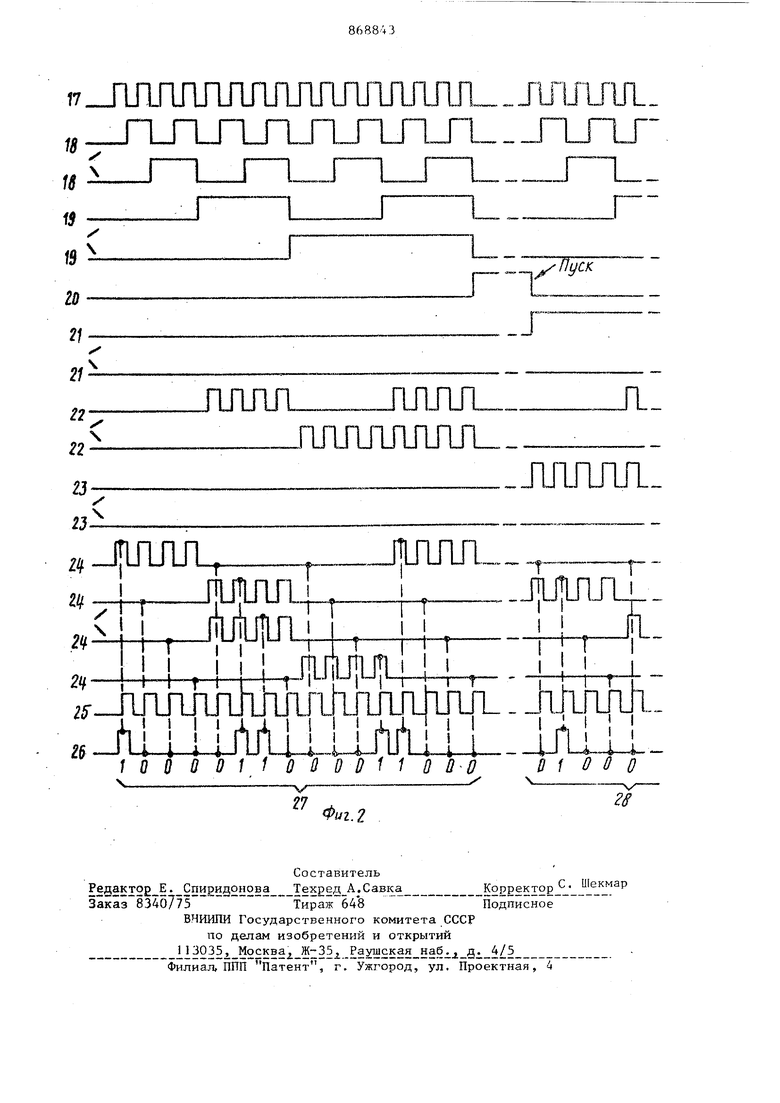

Изобретение относится к запоминающим устройствам и может быть использовано в контрольно-испытательной аппаратуре для проверки постоянной памяти, а также в устройствах автоматики и вычислительной техники для их профилактического контроля. Известно устройство для контроля блоков постоянной памяти, содержащее генератор тактовых импульсов, генератор тестовых импульсов, адресш Й блок мультиплексор, накопители, блок со-г гласования, регистры, элементы ИЛИ, компаратор и блок управления D Недостатком этого устройства являются большие аппаратурные затраты. Наиболее близким к предлагаемому является устройство для контроля блоков постоянной памяти, содержащее генератор сигналов, счетчик адресов, сигнатурный анализатор , (в него вхо дят регистр сдвига, сумматор по модулю два, преобразователь кодов; группа индикаторов, причем выход сумматора ПО модулю два подключен к информационному входу регистра сдвига, выходы которого соединены с входами преобразователя кодов, одни из выходов - со входами сумматора по модулю два, а выходы преобразователя кодов подключены ко входам индикаторов , счетчик выходных сигналов, группу элементов И, элемент задержки, коммутатор, группу формирователей уровней сигналовi хфуппу пороговых элементов, причем выход генератора сигналов соединен с первыми входами элементов И, выходом устройства и входами элемента задержки и счетчика выходных сигналов, адресные выхода которого подключены к ад7 ресиым входам коммутатора, а выход переполнения - ко входу счетчика адресов, адресные выходы которого соединены со вторыми входами элементов И, выходы которых подключены соответственно ко входам формирователей уровней сигналов,, выходы которых соединены с адресными входами устройCTB&i выходы пороговых элементов подключены ко входам устройства, а выходы - к другим входам коммутатора, выход которого соединен с информационным входом сумматора по модулю два, выход элемента задержки подключен к тактовому входу регистра сдвига 2 Это устройство формирует сигнатуру (сочетание символов на индикаторах) , которая свидетельствует об исправности проверяемой постоянной памяти, если она совпадает с заранее известной эталонной сигнатурой, а .1 также обеспечивает малую точность и глубину контроля, так как дает недостаточную информацию о месте возникновения неисправности. Цель изобретения - повышение точности контроля постоянной памяти, состоящей-, например, из полупроводниковых микросхем. Поставленная цель достигается тем что в устройство для контроля блоков постоянной памяти, содержащее генератор сигналов, основной счетчик адресных сигналов, анализатор, счетчик выходных сигналов, основные элементы И и формирователи выходных сигналов, элемент задержки, коммутатор, пороговые элементы, приче м выход генератора сигналов соединен с первыми ,входами основных элементов И, выходом устройства и входами элемента задержки и счетчика выходных сигналов, адресные выходы которого подключены к одним из входов коммутатора, а выход переполнения - ко входу основного счётчика адресных сигналов, адресные выходы которого соединены со вторыми входами основных элементов И, выходы которых подключены соответственно ко входам основных формирователей выход ных сигналов, выходы которых являются одними из адресных выходов устройства, входы пороговых элементов я ляются входами устройства, а выходы подключены к другим входам коммутатора, выход которого соединен с информационным входом анализатора, так товый вХод которого подключен к выходу элемента задержки, введены эле. мент , дополнительные элементы И и формирователи выходных сигналов , триггер, ключ и дополнительный счетчик адресных сигналов, выходы ко торого соединены с одними из входов .дополнительных элементов И, другие входы которых соединены с выходом ге нератора сигналов, а выходы - со вхо дами дополнительных формирователей выходных сигналов, выходы которых являются другими адресными выходами устройства, вход дополнительного счетчика адресных сигналов подключен к инверсному выходу триггера, установочный вход которого подключен к выходу переполнения основного счетчика адресных сигналов, вход сброса триггера соединен со входом сброса анализатора и с одним из выводов ключа, другой вывод которого соединен с шиной нулевого потенциала, а прямой выход триггера и выход переполнения дополнительного счетчика адресных сигналов соединены со входами элемента ИЛИ-НЕ, выход которого соединен с управлякУщим входом генератора сигналов. При работе устройство формирует сигнатуры поочередно для каждой из микросхем постоянной памяти, исправность или неисправность которых определяется раздельно, чем обеспечивается локализация неисправной микросхемь1, т.е. увеличивается точность и глубина контроля. На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - временные диаграммы сигналов. Устройство (фиг. 1) содержит генератор 1 сигналов, счетчик 2 выходных сигналов, основные 3.1 ,и дополнительные 3.2 элементы И, элемент 4 задержки, шину 5 нулевого потенциала. Ко входам и выходам устройства подключается блок 6 контролируемой постоянной памяти. Устройство также содержит коммутатор 7, основной счетчик 8 адрес- ных сигналов, триггер 9, дополнительный счетчик 10 адресных сигналов, элемент ИЛИ-НЕ 11, основные формирователи 12 выходных сигналов, дополнительные формирователи 13 выходных сигналов, пороговые элементы 14, анализатор 15 и ключ 16. Выходы формирователей 12 являются одними из адресных выходов устройства. Выходы счетчика.10 соединены с одними из входов элементов И 3.2, другие входы которых соединены с выходом генератора 1, а выходы - с входами формирователей 13, выходы которых являются другими адресными выходами устройства. Вход счетчика 10 подключен к инверсному выходу триггера 9, установочный вход которого подключен к выходу переполнения счетчика 8. Вход 5 сброса триггера 9 соединен со входом сброса анализатора 15 и с одним из в водов ключа 16, другой вывод которого соединен с шиной 5 нулевого потен циала. Прямой выход триггера 9 и выход переполнения счетчика 10 соедине ны со входами элемента ИЛИ-НЕ 11, вы ход которого соединен с управляющим входом генератора 1. Анализатор 15 представляет собой сдвигающий регист с линейными обратными связями через сумматор по модулю два, к выходам ко торого через дешифраторы присоединены алфавитно-цифровые индикаторы (не показаны). Тактовым и сбросовым входами сигнатурного анализатора являются соответственно тактовый и сбросовый вход сдвигакицего регистра, а информационным входом - дополнительный вход сумматора .по модулю два. Та товый вход анализатора 15 соединен с выходом элемента 4 задержки, а вход сброса - с входом сброса триггера 9 и ключом 16 промежуточного пуска уст ройства. На временной диаграмме сигналов работы устройства (фиг. 2) показаны импульсы 17, генерируемые генератором 1, сигналы 18 и 19 соответственн счетчиков 2 и 8, сигнал 20 триггера сигналы 21 счетчика 10, сигналы 22 на выходах формирователей 12, сигналы 23 на выходах формирователей 13, сигналы 24 на выходах пороговых элементов 14 сигнал 25 на выходе элемента задержки 4, сигнал 26 на инфор мационном входе анализатора 15, двоичные последовательности 27 и 28, формирующие сигнатуры соответственно для первой и К.-ой микросхемы памяти. Устройство работает следующим образом, В исходном состоянии счетчики 2, 8 и 10, триггер 9 и анализатор 15 сброшены (цепи сброса и пуска на фиг. 1 не показаны). При эапуске уст ройства генератор 1 начинает генерировать импульсы 17 (фиг. 2), которые стробируют элементы И 3.1 и 3.2 и из меняют состояние счетчика 2. При это на адресные входы проверяемого блока 6 постоянной памяти код одного и того же адреса будет поступать до тех пор, пока при помощи счетчика 2 и .коммутатора 7 не будут опрошены вс выходы блока 6 контролируемой постоян ной памяти. После этого состояние счетчика 8 изменится (по сигналу переполнения с выхода счетчика 2), и бу 3 дут ВНОВЬ опрашиваться выходы блока 6. Генератор 1 выдает импульсы до тех пор, пока не будут опрошены выходы блока. 6 при всех возможных состояниях счетчика 8, после чего взводится триггер 9, который через элемент ШШ-НЕ 11 запирает генератор I. Так как счетчик 8 формирует коды младших разрядов адреса блока 6, которые обычно выбирают слова из одной микросхемы, определяемой кодом старших разрядов адреса, то на выходе коммутатора 7 сформируется двоичная последовательность 27, каждый бит которой соответствует содержимому одной ячейки первой микросхемы проверяемого блока 6. Анализатор 15 осуществляет цреобразование двоичной последовательности в сочетание символов сигнатуру. При изменении бо входной последовательности хотя бы одного бита сигнатура резко меняется. Эталонная сигнатура для каждой -микросхе исправного блока 6 постоянной памяти может определяться экспериментально или путем математических расчетов на ЭВМ. Она может быть занесена в документацию и использоваться для визуального сравнения с реальной сигнатурой или храниться в запоминающем устройстве ЭВМ и использоваться для автоматического сравнения с результатом контроля. . После того как будет определена исправность или неисправность первой микросхемы проверяемого блока 6 памяти, нажимается ключ 16 для промежуточного пуска устройства. При этом сбрасываются анализатор 15 и триггер 9, а содержимое.счетчика 10 увеличивается на единицу. Поэтому в проверяемом блоке 6 памяти выбирается вторая микросхема, которая контролируется аналогичным образом. Контроль блока 6 памяти заканчивается после того, как заполнится счетчик 10, т.е. поочередно будут выбраны все микросхемы блока 6 памяти, и для каждой из них сформирована своя сигнатура. Технико-экономическое преимущество предлагаемого устройства заключается в том, что оно позволяет снизить затраты времени на диагностирование неисправности блоков постоянной памяти для сложных вычислительных компексов. Формула изобретения Устройство для контроля блоков постоянной памятиt содержащее генератор сигналов, основной счетчик адресных сигналов, анализатор, счетчик выходных сигналов, основные элементы И и формирователи выходных сигналов, элемент задержки, коммутатор, пороговые элементы, причем выход генератора сиг налов соединен с первыми входами основньЬс элементов И, выходом устройства и ВХОДШ4И элемента задержки и счетчика выходных сигналов, адресные выходы которого подключены к одним из входов коммутатора, а выход переполнения - ко входу основного счетчика адресных сигналов, адресные выходы которого соединены со вторыми входами ословньпс элементов И, выходы которых подключены соответственно ко входам основных формирователей выходных сигналов, выходы которых являются одннми из адресных выходов устройства входы пороговых элементов являются входами устройства, а выходы подключены к другим входам коммутатора, выход которого соединен с информационным входом анализатора, тактовый вход которого подключен к выходу элемента задержки, отличающееся тем что, с целью повьшения точности контроля, оно содержит элемент ИЛИ-НЕ, дополнительные элементы И и формирова тели выходных сигналов, триггер, ключ и дополнительный счетчик адресных сигналов, выходы которого соединены с одними из входов дополнительных элементов .И, другие входы которых соединены с выходом генератора сигналов, а выходы - с входами дополнительных формирователей выходных сигналов, выходы которых являются другими адресными выходами устройства, вход дополнительного счетчика адресных сигналов подключен к инверсному выходу триггера, установочный вход которого подключен к выходу переполнения основного счетчика адресных, сигналов, вход сброса триггера соединен со входом сброса анализатора и с одним из выводов ключа, другой вывод которого соединен с шиной нулевого потенциала, прямой выход триггера и выход переполнения дополнительного счетчика адресных сигналов соединены со входами элемента ИЛИ-НЕ, выход которого соединен с управляющим входом генератора сигналов. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР по заявке № 2855182/18-24, кл. G и С 29/00, 1979. 2.Авторское свидетельство СССР по заявке №.2709645/24, кл. G 11 С 29/00, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1985 |

|

SU1302323A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1451781A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1985 |

|

SU1302220A2 |

| Устройство сигнатурной проверки аналого-цифровых преобразователей | 1979 |

|

SU790293A1 |

| Логический анализатор | 1986 |

|

SU1381512A1 |

| Устройство для контроля постоянной памяти | 1979 |

|

SU777742A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

Авторы

Даты

1981-09-30—Публикация

1980-01-07—Подача