1

00

4J

СП

Vr.r14

ется вторым ШИМ 9, и третий РЭ 10, включаемый через резистор 11, 5шрав- леиие которым осуществляется третьим ШИМ 12. Согласование работы всех ШИМ обеспечивается логическим блоком 16 согласования работы регулирующих элементов. Первый ЕЭ 5 обеспечивает

инвариантность вькодного напряжения ВХОДНОМУ, второй РЭ 7 - инвариантность выходного напряжения при скачкообразном уменьшении тока нагрузки, а третий РЭ 10 - инвариантность выходного напряжения при скачкообразном увеличении тока нагрузки, 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный стабилизатор напряжения | 1987 |

|

SU1408428A1 |

| Импульсный стабилизатор постоянного напряжения | 1987 |

|

SU1467542A1 |

| Способ стабилизации выходного напряжения импульсного стабилизатора | 1985 |

|

SU1376069A1 |

| Стабилизатор постоянного напряжения | 1988 |

|

SU1541574A1 |

| РЕЛЕЙНЫЙ РЕГУЛЯТОР ТОКА | 1992 |

|

RU2111526C1 |

| Импульсный стабилизатор постоянного напряжения | 1986 |

|

SU1403035A1 |

| Импульсный стабилизатор напряжения | 1983 |

|

SU1117608A1 |

| Импульсный стабилизатор напряжения с защитой от перегрузок по току | 2019 |

|

RU2711138C1 |

| Импульсный стабилизатор напряжения | 1983 |

|

SU1121659A1 |

| Импульсный понижающий стабилизатор постоянного напряжения | 1990 |

|

SU1786477A1 |

Изобретение относится к электротехнике и может быть использовано во вторичных источниках электропитания радиоэлектронной аппаратуры. Цель изобретения - повыше1ше динамической точности стабилизации выходного напряжения за счет обеспечения его инвариантности при скачкообразных изменениях тока нагрузки. Стабилизатор содержит DLC-фильтр 1, первый регулирующий элемент (РЭ) 5, управление которьш осуществляется первым широтно-импульсным модулятором (ШИМ) 6, второй РЭ 7, включаемый через диод 8, управление которым осуществля- О)

1

Изобретение относится к электротехнике и может быть использовано во вторичных источниках электропитания радиоэлектронной аппаратуры.

Целью изобретения является повышение динамической точности стабилизации выходного напряжения за счет обеспечехшя его инвариантности при скачкообразных изменениях тока нагрузки.

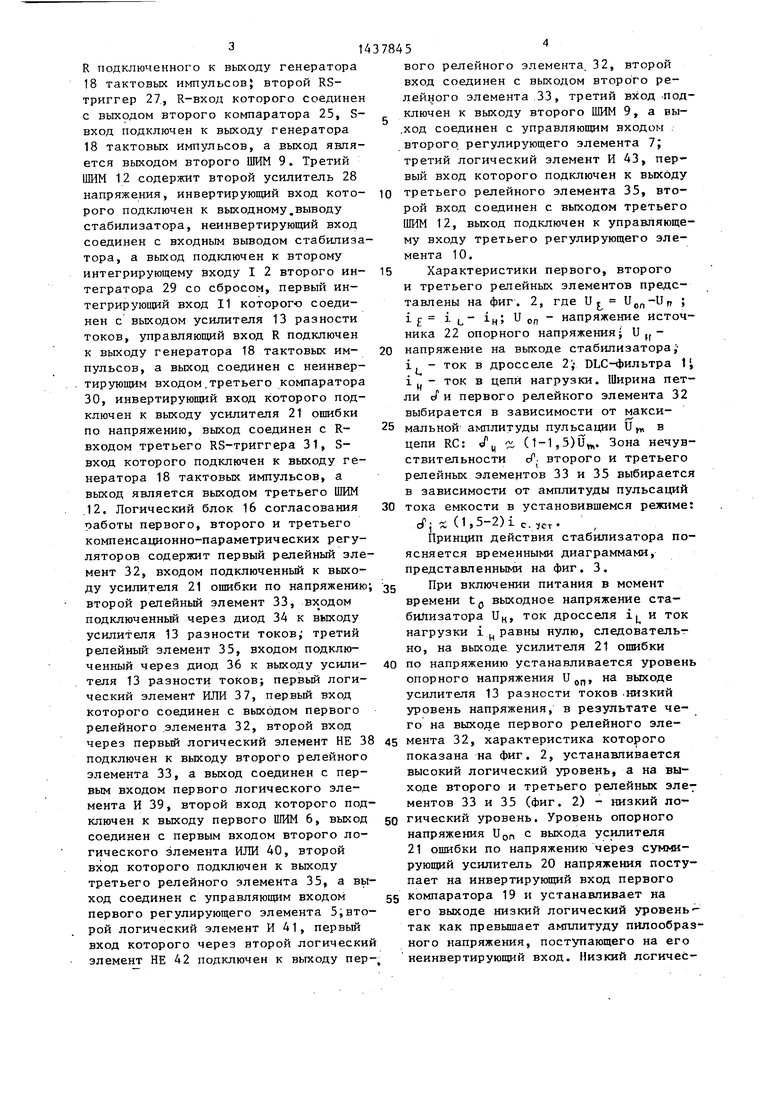

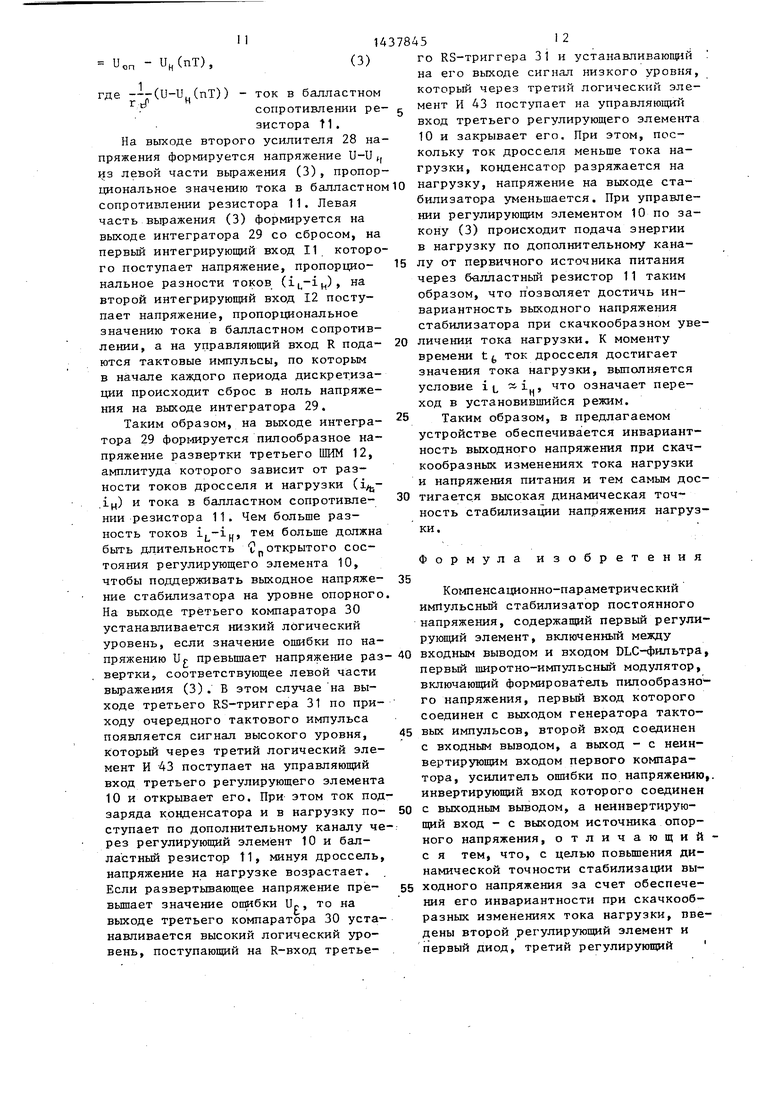

На фиг. 1 представлена схема ком пенсационно-параметрического импульсного стабилизатора постоянного напряже шя на фиг. 2 - характеристики первого, второго и третьего релейных элементов; на фиг. 3 - временные диаграг шг, поясняющие принцип работы компенсационно-параметрического .иьтульсного стабилизатора напряжения

Компенсационно-параметрический импульсный стабилизатор постоянного напряже1Шя (фиг. 1) содержит DLC- фильтр 1, состоящий из дросселя 2, коьщенсатора 3 и замыкающего диода 4, первый регулирующий элемент 5 и первы ,Ш1-1ротно-импульсный модулятор (ШИМ) 6| второй регулирующий элемент 7j вттюченньй через первый диод 8 параллельно входу-выходу DLC-фильтра 1, и второй ШИМ 9J третий регулирую- щий элемент 10, включенный последовательно с резистором 11 между входным и выходньм выводами стабилизатора, и третий ШИМ 12; усилитель 13 разности токов, инвертирующий вход которого подключен к выходу датчика 14 тока, включенного между выходом DLC- фильтра и выходным выводом, неинвертирующий вход соединен с выходом датчика 15 тока, включенного в цепь дросселя 2 DLC-фильтра 1, логический блок 16 согласования работы первого, второго и третьего компенсационно

5

0

5

0

5

0

параметрических регуляторов. Датчики 14 и 15 тока реализованы по схеме, в основе которой используются низкоом- ный резистор (0,1 Ом) и операционный усилитель, напряжение на выходе которого пропорционально измеряемому току, проходящему через этот резистор. Первьй ШРМ 6 содержит формирователь 17 пилообразного напряжения, первый вход которого соединен с выходом генератора 18 тактовых иг-тульсов, второй вход подключен к входному выводу стабилизатора, а выход соединен с неинвертирующим входом первого компаратора 19, инвертирующий вход которого подключен к выходу суммирующего усилителя 20 напряжения, инвертирующий вход которого соединен с выходом усилителя 13 разности токов, неинвертирующий вход подключен к выходу усилителя 21 ошибки по напряжению, неинвертирующим входом соединенного с выходом источника 22 опорного напряжения, а инвертирующим входом подключенного к выходному выводу стабилизатора i первый RS-триггер 23, R- вход которого соединен с выходом первого компаратора 19, S-вход подключен к выходу генератора 18 тактовых импульсов, а выход является выходом первого иММ 6. Второй ШЖ 9 содержит первый усилитель 24 напряжения, инвертирующий вход которого соединен с выходом усилителя 21 ошибки по напряжению, неинвертирующий вход подключен к выходу усилителя 13 разности токов, выход соединен с инвертирующим входом второго компаратора 25, неинвер- тирующий вход которого подключен к выходу первого интегратора 26 со сбросом, интегрирующим входом I соединенного с выходом усилителя 13 разности токов, а управляющим входом

R подключенного к выходу генератора 18 тактовых импульсов} второй RS- триггер 27, R-вход которого соединен с выходом второго компаратора 25, S- вход подключен к выходу генератора 18 тактовых импульсов, а выход является выходом второго ШИМ 9. Третий ШИМ 12 содержит второй усилитель 28 напряжения, инвертирующий вход кото- ю рого подключен к выходному,выводу стабилизатора, неинвертирующий вход соединен с входным выводом стабилизатора, а выход подключен к второму интегрирующему входу I 2 второго ин- 15 тегратора 29 со сбросом, первый интегрирующий вход II которого соединен с выходом усилителя 13 разности токов, управляющий вход R подключен к выходу генератора 18 тактовых им- 20 пульсов, а выход соединен с неинвертирующим входом.третьего компаратора 30, инвертирующий вход которого подключен к выходу усилителя 21 ошибки по напряжению, выход соединен с R- входом третьего RS-триггера 31, S- вход которого подключен к выходу генератора 18 тактовых импульсов, а выход является выходом третьего ШИМ .12, Логический блок 16 согласования 30 работы первого, второго и третьего компенсационно-параметрических регуляторов содержит первый релейный элемент 32, входом подключенньй к выходу усилителя 21 ошибки по напряжению; 35 второй релейный элемент 33, подключенный через диод 34 к выходу усилителя 13 разности токов, третий релейный элемент 35, входом подключенный через диод 36 к выходу усилителя 13 разности токов; первый логический элемент ИЛИ 37, первый вход которого соединен с выходом первого релейного .элемента 32, второй вход

вого релейного элемента, 32, второй вход соединен с выходом второго релейного элемента 33, третий вход -подключен к выходу второго ШИМ 9, а вы- .ход соединен с управляющим входом . второго, регулирующего элемента 7; третий логический элемент И 43, первый вход которого подключен к выходу третьего релейного элемента 35, второй вход соединен с выходом третьего НИМ 12, выход подключен к управляющему входу третьего регулирующего элемента 10.

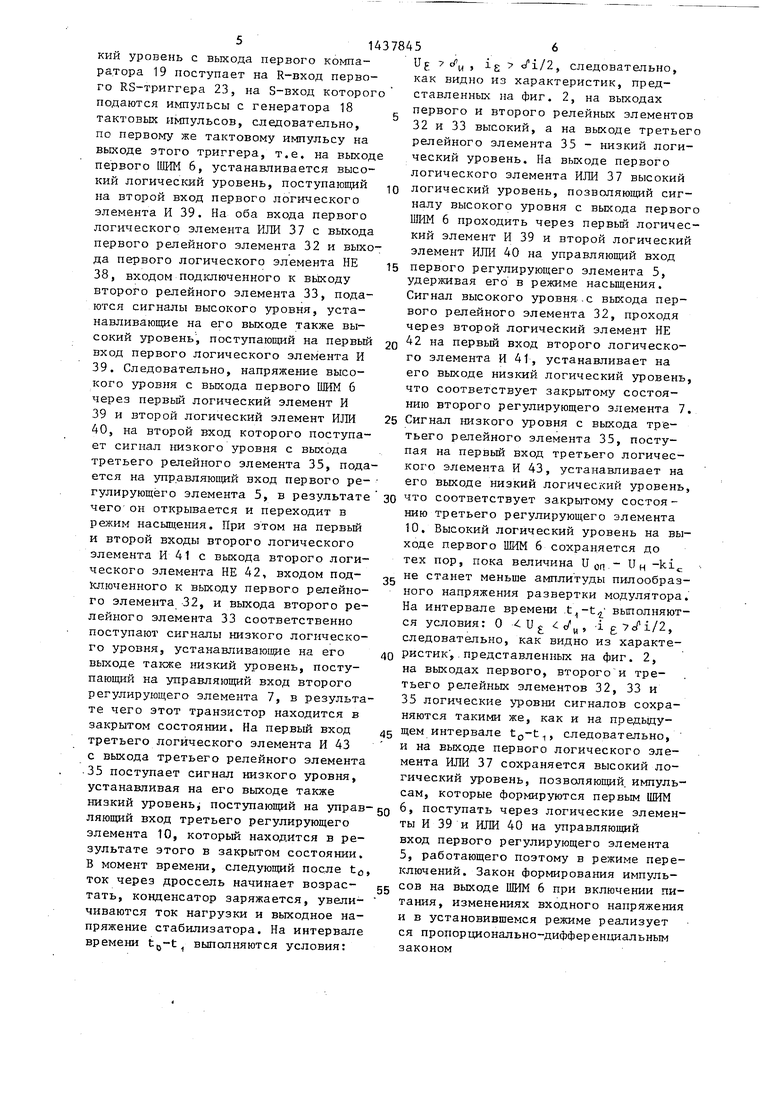

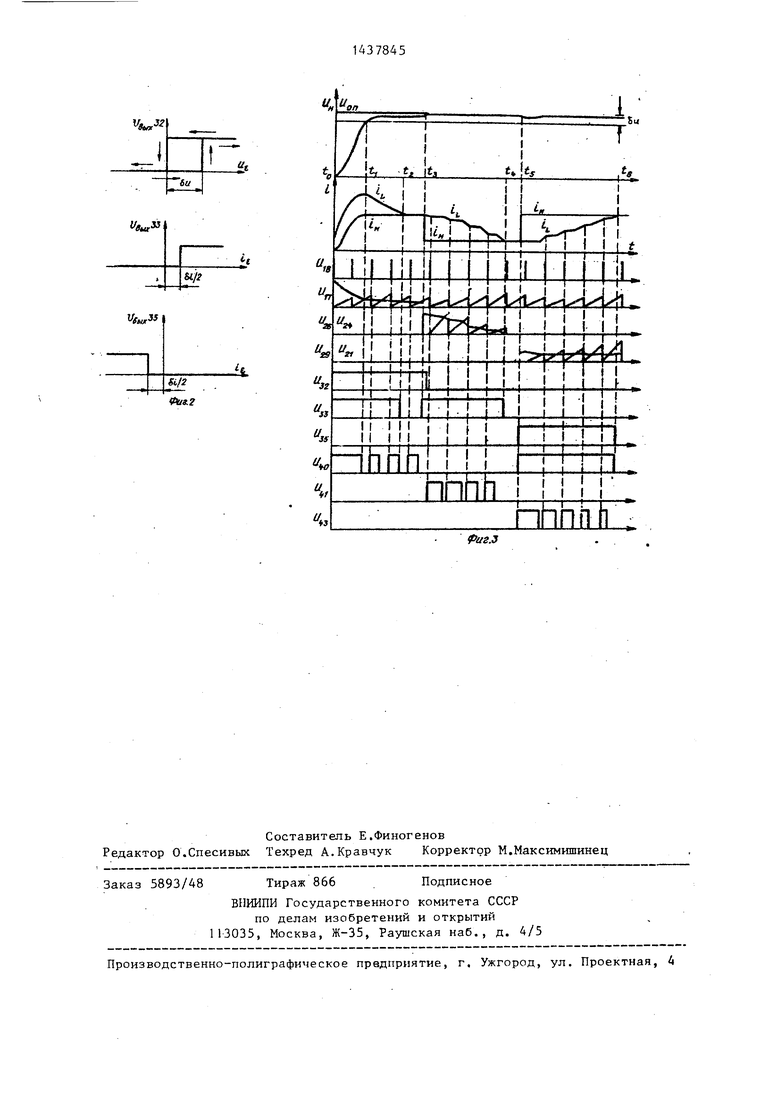

Характеристики первого, второго и третьего релейных элементов представлены на фиг. 2, где Ur ; i-L- IK; on напряжение источника 22 опорного напряжения; U jj- напряжение на выходе стабилизатора j- i. - ток в дросселе 2 DLC-фильтра 1, i .. - ток в цепи нагрузки. Ширина пет-

п

ли t/ и первого релейного элемента 32 выбирается в зависимости от макси- 25 мальной амплитуды пульсации U в

цепи RC: Oi (1-1,5)11,,. Зона нечувствительности (/. второго и третьего релейных элементов 33 и 35 выбирается в зависимости от амплитуды пульсаций тока емкости в установившемся режиме:

)ic.:/CT

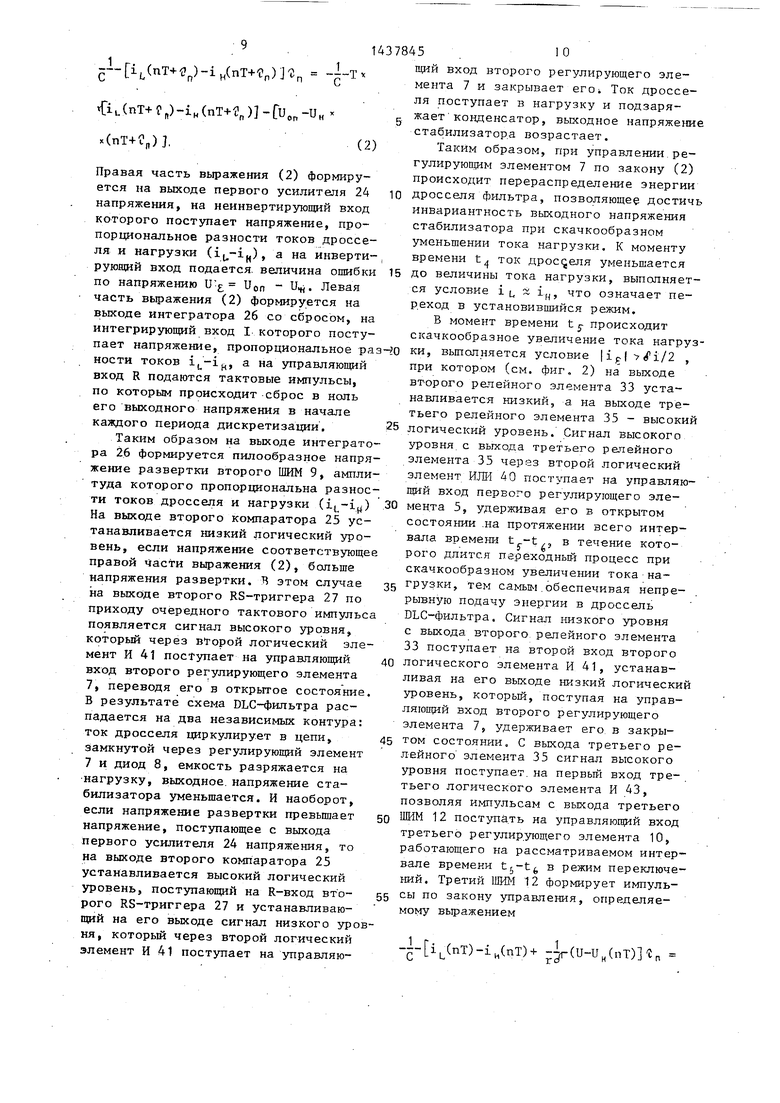

Принцип действия стабилизатора поясняется временными диаграммами, представленными на фиг. 3.

При включении питания в момент времени t выходное напряжение стабилизатора UH, ток дросселя 1ц И ток нагрузки i . равны нулю, следовательп

но, на выходе усилителя 21 ошибки

40 по напряжению устанавливается уровень опорного напряжения U,, на выходе усилителя 13 разности токов .низкий уровень напряжения, в результате чего на выходе первого релейного эле- через первый логический элемент НЕ 38 45 мента 32, характеристика которого подключен к выходу второго релейного показана на фиг. 2, устанавливается

элемента 33, а выход соединен с первым входом первого логического элемента И 39, второй вход которого подключен к выходу первого ШИМ 6, выход соединен с первым входом второго логического элемента ИЛИ 40, второй вход которого подключен к выходу третьего релейного элемента 35, а выход соединен с управляющим входом первого регулирующего элемента 5;второй логический элемент И 41, первый вход которого через второй логический элемент НЕ 42 подключен к выходу пер-.

0 5

вого релейного элемента, 32, второй вход соединен с выходом второго релейного элемента 33, третий вход -подключен к выходу второго ШИМ 9, а вы- .ход соединен с управляющим входом . второго, регулирующего элемента 7; третий логический элемент И 43, первый вход которого подключен к выходу третьего релейного элемента 35, второй вход соединен с выходом третьего НИМ 12, выход подключен к управляющему входу третьего регулирующего элемента 10.

Характеристики первого, второго и третьего релейных элементов представлены на фиг. 2, где Ur ; i-L- IK; on напряжение источника 22 опорного напряжения; U jj- напряжение на выходе стабилизатора j- i. - ток в дросселе 2 DLC-фильтра 1, i .. - ток в цепи нагрузки. Ширина пет-

п

ли t/ и первого релейного элемента 32 выбирается в зависимости от макси- 5 мальной амплитуды пульсации U в

цепи RC: Oi (1-1,5)11,,. Зона нечувствительности (/. второго и третьего релейных элементов 33 и 35 выбирается в зависимости от амплитуды пульсаций тока емкости в установившемся режиме:

)ic.:/CT

Принцип действия стабилизатора поясняется временными диаграммами, представленными на фиг. 3.

При включении питания в момент времени t выходное напряжение стабилизатора UH, ток дросселя 1ц И ток нагрузки i . равны нулю, следовательп

но, на выходе усилителя 21 ошибки

высокий логический уровень, а на выходе второго и третьего релейных эле7 ментов 33 и 35 (фиг. 2) - низкий логический уровень. Уровень опорного напряжения с выхода усилителя 21 ошибки по напряжению через суммирующий усилитель 20 напряжения поступает на инвертирующий вход первого

компаратора 19 и устанавливает на

его выходе низкий логический уровень - так как превышает амплитуду пилообразного напряжения, поступающего на его неинвертирующий вход. Низкий логический уровень с выхода первого компаратора 19 поступает на R-вход первого RS-триггера 23, на S-вход которого подаются н fflyльcы с генератора 18 тактовых импульсов, следовательно, по первому же тактовому импульсу на выходе этого триггера, т.е. на выходе первого ШИМ 6, устанавливается высокий логичес1шй уровень, поступающий на второй вход первого логического элемента И 39. На оба входа первого логического элемента ИЛИ 37 с выхода первого релейного элемента 32 и выхода первого логического элемента НЕ

38,входом под1шюченного к вьЬсоду второго релейного элемента 33, подаются сигналы высокого уровня, устанавливающие на его выходе также высокий уровень, поступающий на первый вход первого логического элемента И

39,Следовательно, напряжение высокого уровня с выхода первого ШИМ б через первьй логический элемент И 39 и второй логический элемент ИЛИ

40,на второй вход которого поступает сигнал 1ШЗКОГО уровня с выхода третьего релейного элемента 35, подается на управляющий вход первого ре-

гулирующёго элемента 5, в результате зо что соответствует закрытому состоячего он открывается и переходит в режим насыщения. При этом на первый и второй входы второго логического элемента И 41 с выхода второго логилейного элемента 33 соответственно поступают сигналы низкого логического уровня, устанавливающие на его выходе также низкий уровень, поступающий на управляющий вход второго регулирующего элемента 7, в результаческого элемента НЕ 42, входом под- gg не станет меньше амплитуды пилообраз- Ключенного к выходу первого релейно- ного напряжения развертки модулятора. Го элемента 32, и выхода второго ре- На интервале времени .. выполняются условия: О iU f, Е, i/2 следовательно, как видно из характе- 40 ристик,.представленных на фиг. 2, на выходах первого, второго и третьего релейных элементов 32, 33 и 35 логические уровни сигналов сохрате чего этот транзистор находится в закрытом состоянии. На первый вход третьего логического элемента И 43 с выхода третьего релейного элемента .35 поступает сигнал низкого уровня, устанавливая на его выходе также

няются такими же, как и на предьщу- 45 щем интервале .,, следовательно, и на выходе первого логического элемента ИЛИ 37 сохраняется высокий логический уровень, позволяющий, импульсам, которые формируются первым ШИМ низкий уровень поступающий на управ-до поступать через логические элемен- ляющий вход третьего регулирующего ты И 39 и ИЛИ 40 на управляющий

вход первого регулирующего элемента 5, работающего поэтому в режиме переключений. Закон формирования импуль-

элемента 10, которьй находится в результате этого в закрытом состоянии. В момент времени, следующий после t.

ток через дроссель начинает возрас- gg сов на выходе ШИМ 6 при включении питать, конденсатор заряжается, увеличиваются ток нагрузки и выходное напряжение стабилизатора. На интервале времени выполняются условия:

Ug 7 с , IE , следовательно, как видно из характеристик, представленных на фиг. 2, на выходах первого и второго релейных элементов 32 и 33 высокий, а на выходе третьего релейного элемента 35 - низкий логический уровень. На выходе первого логического элемента ИЛИ 37 высокий логический уровень, позволяющий сигналу высокого уровня с выхода первого ШИМ 6 проходить через первьш логический элемент И 39 и второй логический элемент ИЛИ 40 на управляющий вход

5 первого регулирующего элемента 5, удерживая его в режиме насыщения. Сигнал высокого уровня.с выхода первого релейного элемента 32, проходя через второй логический элемент НЕ 42 на первый вход второго логического элемента И 41, устанавливает на его выходе низкий логический уровень, что соответствует закрытому состоянию второго регулирующего элемента 7.

5 Сигнал низкого уровня с выхода третьего релейного элемента 35, поступая на первый вход третьего логического элемента И 43, устанавливает на его выходе низкий логический уровень.

0

нию третьего регулирующего элемента 10. Высокий логический уровень на выходе первого ШИМ 6 сохраняется до тех пор, пока величина U oq. - U н -ki..

тания, изменениях входного напряжения и в установившемся режиме реализует ся пропорционально-дифферен1щальным законом

714378458

с/(и) orrUf(nT+Or,)-kie(nT+ I) , (1)та 35 - низкий логический уровень.

При выполнении условия U

и

де Т - период дискретизации;

1 - длительность открытого сос- ТОЯ1ШЯ силового транзистора на (п+1)-м периоде дискретизации, п О, о ; d(и) - коэффициент наклона пилы,

прямо пропорционально зави- сяпщй от напряжения питания и DLC-фильтра;

ip - ток через конденсатор DLC- фильтра,

К - коэффициент передачи по току 15 первый логический элемент И 39, на

емкости фильтра.

В момент времени t- стабилизатор входит в установившийся режим работы, которьш характеризуется вьшолнением условия равенства токов дросселя и нагрузки , т.е. I i.g I «/.i/Z,

следовательно (см. фиг. 2), на выходах второго и третьего релейных элементов 33 и 35 низкий логический уровень. На выходе первого логического элемента-ИЛИ 37 высокий логический уровень, позволяющий импульсам с выхода первого ШИМ 6 через логические элементы И 39 и ИЛИ 40 поступать на управляющий вход первого регулирующего элемента 5. Сигналы низкого уровня с выходов второго и третьего релейных элементов 33 и 35, поступая соответственно на второй вход второго логического элемента И 41 и первый вход третьего лсЗгичес- кого элемента И 43, устанавливают на их выходах низкий логический уровень, что соответствует закрытому состоянию второго и третьего регулирующих элементов 7 и 10. Таким образом, при включении питания и в установившемся режиме стабилизация напряжения на нагрузке осуществляется

выходе которого устанавливается низкий логический уровень, поступающий на первый вход второго логического элемента ИЛИ 40, на второй вход кото20 рого поступает сигнал низкого уровня с выхода третьего релейного элемента 35. Следовательно, с выхода второ го логического элемента ИЛИ 40 на управляющий вход первого регулирующего

25 элемента 5 подается низкий уровень

напряжения, в результате чего регу- . лирующий элемент 5 закрывается и переходит в режим отсечки.

Таким образом, стабилизатор отключается от источника входного питающего напряжения U на весь интервал времени tj-t, в течение которого длится переходный процесс- при

35 скачкообразном уменьшении тока нагрузки. При этом на первый и второй входы второго логического элемента И 41 с выхода второго логического элемента НЕ 42 и второго релейного

40 элемента 33 соответственно поступают сигналы высокого уровня, позволяющие импульсам с выхода второго ШИМ 9 проходить через второй логический элемент И 41 на управляющий вход второ50

за счет переключений первого регули- го регулирующего элемента 7,работаю рующего элемента 5 под управлением первого ШИМ 6 по пропорционально- дифференциальному закону (1), устраняющему перерегулирование напряжения на нагрузке.

В момент времени t происходит скачкообразное уменьшение тока нагрузки, в результате вьшолняется условие ig cf i/2 и напряжение на на- грузке начинает возрастать. Следовательно (см. фиг. 2), на выходе второго релейного элемента 33 высокий, а на выходе третьего репейного элеменщего на рассматриваемом интервале времени tj-n, в режиме переключений. Сигнал низкого уровня с выхода третьего релейного элемента 35, поступая на первый вход третьего логического элемента И 43, устанавливает на его выходе низкий логический уровень, что соответствует закрытому состоянию третьего регулирующего элемента 55 10. Второй ШИМ 9, управляющий.вторым регулирующим элементом 7, формирует импульсы по закону управления, опре- д еля емому выр аже ни ем

логический уровень.

условия U

и

и

т.е.

Up о, на выходе пер-вого релейного элемента 32 устанавливается низкий логический уровень, который сохраняется до тех пор, пока выполняется условие Ujr с/(фиг. 2). В этом случае на обоих входах первого логического элемента ИЛИ 37 низкий логический уровень, в результате чего на его выходе также устанавливается низкий уровень, запрещающий ийпульсам с выхода первого ШИМ 6 проходить через

выходе которого устанавливается низкий логический уровень, поступающий на первый вход второго логического элемента ИЛИ 40, на второй вход которого поступает сигнал низкого уровня с выхода третьего релейного элемента 35. Следовательно, с выхода второго логического элемента ИЛИ 40 на управляющий вход первого регулирующего

элемента 5 подается низкий уровень

напряжения, в результате чего регу- лирующий элемент 5 закрывается и переходит в режим отсечки.

Таким образом, стабилизатор отключается от источника входного питающего напряжения U на весь интервал времени tj-t, в течение которого длится переходный процесс- при

скачкообразном уменьшении тока нагрузки. При этом на первый и второй входы второго логического элемента И 41 с выхода второго логического элемента НЕ 42 и второго релейного

элемента 33 соответственно поступают сигналы высокого уровня, позволяющие импульсам с выхода второго ШИМ 9 про, ходить через второй логический элемент И 41 на управляющий вход второ

го регулирующего элемента 7,работаю

щего на рассматриваемом интервале времени tj-n, в режиме переключений. Сигнал низкого уровня с выхода третьего релейного элемента 35, поступая на первый вход третьего логического элемента И 43, устанавливает на его выходе низкий логический уровень, что соответствует закрытому состоянию третьего регулирующего элемента 10. Второй ШИМ 9, управляющий.вторым регулирующим элементом 7, формирует импульсы по закону управления, опре- д еля емому выр аже ни ем

(nT-fl),)j J, -g-T Ciu(nT-f J-i,(nT+)-rU, -U, X

(,

Правая часть выражения (2) формируется на выходе первого усилителя 24 напряжения, на неинвертирующий вход которого поступает напряжение, пропорциональное разности токов дросселя и нагрузки (), а на инвертирующий вход подается, величина ошибки по напряжению U Uon U, Левая часть выражения (2) формируется на выходе интегратора 26 со сбросом, на интегрирующий вход I которого поступает напряжение, пропорциональное ра ности токов , а на управляющий вход R подаются тактовые импульсы, по которым происходит сброс в ноль его выходного напряжения в начале каждого периода дискретизации.

Таким образом на выходе интегратора 26 формируется пилообразное напряжение развертки второго ШИМ 9, амплитуда которого пропорциональна разности токов дросселя и нагрузки () На выходе второго компаратора 25 устанавливается низкий логический уровень, если напряжение соответствующе правой части выражения (2), больше напряжения развертки. В этом случае на выходе второго RS-триггера 27 по приходу очередного тактового импульс появляется сигнал высокого уровня, который через второй логический элемент И 41 поступает на управляющий вход второго регулирующего элемента 7, переводя его в открытое состоя ние В результате схема DLC-фильтра распадается на два независимых контура: ток дросселя циркулирует в цепи, замкнутой через регулирующий элемент 7 и диод 8, емкость разряжается на нагрузку, выходное, напряжение стабилизатора уменьшается. И наоборот, если напряжение развертки превышает напряжение, поступающее с выхода первого усилителя 24 напряжения, то на выходе второго компаратора 25 устанавливается высокий логический уровень, поступающий на R-вход второго RS-триггера 27 и устанавливающий на его выходе сигнал низкого уроня, который через второй логический элемент И 41 поступает на управляю(2)

щий вход второго регулирующего элемента 7 и закрывает eroi Ток дросселя поступает в нагрузку и подзаря- (- жает конденсатор, выходное напряжение

стабилизатора возрастает.

Таким образом, при управлении.регулирующим элементом 7 по закону (2) происходит перераспределение энергии 10 дросселя фильтра, позволяющее достичь инвариантность выходного напряжения стабилизатора при скачкообразном уменьшении тока нагрузки. К моменту времени t ток дрос(еля уменьшается 15 до величины тока нагрузки, выполняет

ся условие 1 , IH, что означает переход в установившийся режим.

В момент времени t происходит скачкообразное увеличение тока нагрузки, вьтолняется условие |ig.| , при котор.ом (см. фиг. 2) на выходе второго релейного элемента 33 устанавливается низкий, а на выходе третьего релейного элемента 35 - высокий

логический уровень. Сигнал высокого уровня, с выхода третьего релейного элемента 35 через второй логический элемент ИЛИ 40 поступает на управляющий вход первого регулирующего элемента 5, удерживая е.го в открытом состоянии .на протяжении всего интер- вагш времени t -t ,, в течение которого длится переходный процесс при скачкообразном увеличении тока нагрузки, тем самым.обеспечивая непрерывную подачу энергии в дроссель DLC-фильтра. Сигнал низкого уровня с выхода второго, релейного элемента 33 поступает на второй вход второго логического элемента И 41, устанавливая на его выходе низкий логический уровень, который, поступая на управляющий вход второго регулирующего элемента 7, удерживает его. в закрытом состоянии. С выхода третьего релейного элемента 35 сигнал высокого уровня поступает, на первый вход третьего логического элемента И 43, позволяя импульсам с выхода третьего ШИМ 12 поступать на управляющий вход третьего регулир.ующего элемента 10, работающего на рассматриваемом интервале времени в режим переключений. Третий НИМ 12 формирует импульсы по закону управления, определяемому выражением

(пТ)-1,(пТ)+ (и-и,(пТ)п

on - UH

(пТ),

где (и-иц(пТ)) - ток в балластном

сопротивлении ре- g зистора 11 .

На выходе второго усилителя 28 напряжения формируется напряжение U-U j, из левой части выражения (3), пропорциональное значению тока в балластном 10 сопротивле ши резистора 11. Левая часть выражения (3) формируется на выходе интегратора 29 со сбросом, на первьй интегрирующий вход II которого поступает напряжение, пропорцио- 15 нальное разности токов (), на второй интегрирующий вход 12 поступает напряжение, пропорциональное значению тока в балластном сопротивлении, а на управляющий вход R подаются тактовые импульсы, по которым в начале каждого периода дискретизации происходит сброс в ноль напряжения на выходе интегратора 29.

Таким образом, на выходе интегратора 29 фор1.{ируется пилообразное напряжение развертки третьего ШИМ 12, амплитуда которого зависит от разности токов дросселя и нагрузки (i/tj . и тока в балластном сопротивлении резистора 11. Чем больше разность токов , тем больше должна быть длительность С|, открытого состояния регулирующего элемента 10, чтобы поддерживать выходное напряже- 35 ние стабилизатора на уровне опорного На выходе третьего компаратора 30 устанавливается низкий логический уровень, если значение ошибки по на-

на его выходе сигнал низкого уровня, которьш через третий логический элемент И 43 поступает на управляющий вход третьего регулирующего элемента 10 и закрывает его. При этом, поскольку ток дросселя меньше тока нагрузки, конденсатор разряжается на нагрузку, напряжение на выходе стабилизатора у 1еньшается. При управлении регулирующим элементом 10 по закону (3) происходит подача энергии в нагрузку по дополнительному каналу от первичного источника питания через балластньш резистор 11 таким образом, что п озвсляет достичь инвариантность выходного напряжения стабилизатора при скачкообразном увеличении тока нагрузки. К моменту времени t (, ток дросселя достигает значения тока нагрузки, выполняется условие IL iu означает переход в установившийся режим.

Таким образом, в предлагаемом устройстве обеспечивается инвариантность выходного напряжения при скачкообразных изменениях тока нагрузки и напряжения питания и тем самым достигается высокая динамическая точность стабилизации напряжения нагрузки,

Формула изобретения

Компенсационно-параметрический импульсный стабилизатор постоянного напряжения, содержащий первый регулирующий элемент, включенный между

20

25

30

пряжению Ur превышает напряжение раз- 40 входным выводом и входом БЬС-фильтра,

вертки, соответствующее левой части выражения (3). Б этом случае на выходе третьего RS-триггера 31 по приходу очередного тактового импульса появляется сигнал высокого уровня, 45 который через третий логический элемент И 43 поступает на управляющий вход третьего регулирующего элемента 10 и открывает его. При этом ток под- заряда конденсатора и в нагрузку по- 50 ступает по дополнительному каналу через регулируюш:ий элемент 10 и балластный резистор 11, минуя дроссель, напряжение на нагрузке возрастает. Если развертывающее напряжение прё- 55 вышает значение одабки Up, то на выходе третьего компаратора 30 устанавливается высокий логический уровень, поступающий на R-вход третьепервый широтно-импульсный модулятор, включающий формирователь пилообразного напряжения, первый вход которого соединен с выходом генератора тактовых импульсов, второй вход соединен с входным выводом, а выход - с неинвертирующим входом первого компаратора, усилитель ошибки по напряжению, инвертирующий вход которого соединен с выходным выводом, а неннвертирую- щий вход - с выходом источника опорного напряжения, отличающий с я тем, что, с целью повьшения динамической точности стабилизации выходного напряжения за счет обеспечения его инвариантности при скачкообразных изменениях тока нагрузки, введены второй регулирующий элемент и первый диод, третий регулирующий

- g

м 10 1535

го RS-триггера 31 и устанавливаюш;ий

на его выходе сигнал низкого уровня, которьш через третий логический элемент И 43 поступает на управляющий вход третьего регулирующего элемента 10 и закрывает его. При этом, поскольку ток дросселя меньше тока нагрузки, конденсатор разряжается на нагрузку, напряжение на выходе стабилизатора у 1еньшается. При управлении регулирующим элементом 10 по закону (3) происходит подача энергии в нагрузку по дополнительному каналу от первичного источника питания через балластньш резистор 11 таким образом, что п озвсляет достичь инвариантность выходного напряжения стабилизатора при скачкообразном увеличении тока нагрузки. К моменту времени t (, ток дросселя достигает значения тока нагрузки, выполняется условие IL iu означает переход в установившийся режим.

Таким образом, в предлагаемом устройстве обеспечивается инвариантность выходного напряжения при скачкообразных изменениях тока нагрузки и напряжения питания и тем самым достигается высокая динамическая точность стабилизации напряжения нагрузки,

Формула изобретения

Компенсационно-параметрический импульсный стабилизатор постоянного напряжения, содержащий первый регулирующий элемент, включенный между

20

25

30

первый широтно-импульсный модулятор, включающий формирователь пилообразного напряжения, первый вход которого соединен с выходом генератора тактовых импульсов, второй вход соединен с входным выводом, а выход - с неинвертирующим входом первого компаратора, усилитель ошибки по напряжению, инвертирующий вход которого соединен с выходным выводом, а неннвертирую- щий вход - с выходом источника опорного напряжения, отличающий с я тем, что, с целью повьшения динамической точности стабилизации выходного напряжения за счет обеспечения его инвариантности при скачкообразных изменениях тока нагрузки, введены второй регулирующий элемент и первый диод, третий регулирующий

элемент и резистор, первьй и второй ; датчики тока, усилитель разности тока, второй широтно-импульсньй модулятор в составе первого усилителя напряжения, второго компаратора, первого интегратора со сбросом и второго RS-триггера, третий широтно-импульсньй модулятор в составе второго усилителя напряжения, третьего компаратора, второго интегратора со сбросом и третьего RS-триггера, логический блок согласования работы регулирующих элементов в составе первого, второго и третьего релейных элементов, второго и третьего диодов, первого и второго логических элементов НЕ, первого и второго логических элементов ИЛИ, первого, второго и третьего логических элементов И, а первый RS-триггер и суммирующий усилитель - в первьй широтно-импульсный модулятор, при этом R-вход первого RS-триггера соединен с выходом первого компаратора, S-вход - с выходом генератора тактовых импульсов, а

выход является выходом первого широт- но-импульсного модулятора, вькод усилителя ошибки по напряжению соединен . с неинвертирующим входом суммирующего усилителя, инвертирующими входами первого усилителя напряжения и третьего компаратора и входом первого релейного элемента, инвертирующий

эход усилителя разности токов соеди- og ИЛИ, второй вход которого соединен

нен с выходом первого датчика тока, включенного между выходом DLC-фильт- ра и выходным выводом, кеинвертирую- щий вход соединен с выходом второго датчика тока, включенного последовательно с обмоткой дросселя DLC-фипьт- ра, а выход - с инвертирующим входом суммирующего усилитеря, с входами второго и третьего релейных элементов через второй и третий диоды соответственно, информационнь м входом первого интегратора, первым информационным входом второго интегратора и неинвертирующим входом первого усилителя напряжения, вторОЙхрегулирующий

элемент через первьй диод включен между входом и выходом DLC-фильтра, третий регулирующий элемент через резистор подключен между входным выводом и выходом DLC-фильтра, выход первого усилителя напряжения соединен

с инвертирующим входом второго компаратора, неинвертиругощи вход которого соединен с выходом первого интегратора, второй усилитель напряжения неинвертирующим входом соединен с входным выводом, инвертирующим входом - с выходньм выводом, а выходом - С вторым информационным входом второ о интегратора, выход которого соединен с неинвертирующим входом третьего компаратора, выход генератора тактовых импульсов соединен с S-вхо- дами второго и третьего триггеров и

R-входами первого и второго интеграторов, выходы второго и третьего компараторов соединены с R-входами второго и третьего RS-триггеров соответственно, выход второго RS-триггера является выходом второго широтно- импульсного модулятора, выход третьего RS-триггера является выходом третьего широтно-импульсного модулятора, первьй вход первого логического элемента ИЛИ соединен с выходом первого релейного элемента, второй вход через первый логический элемент НЕ соединен с выходом второго релейного элемента, а в.ыход соединен с первым

входом первого логического элемента И, второй вход которого соединен с вькодом первого широтно-импульсного модулятора, выход соединен с первым входом второго логического элемента

с выходом третьего релейного элемента, а вькод соединен с управляющим входом первого регулирующего элемента, вход второго логического элемента НЕ соединен с выходом первого релейного элемента, первый вход вто-- рого логического элемента И соединен с выходом второго логического элемента НЕ, второй вход соединен с выходом второго релейного элемента, третий вход соединен с выходом второго широтно-импульсного модулятора, а выход соединен с управляющим входом второго регулирующего элемента, первый вход третьего логического элемента И соединен с выходом третьего релейного элемента, второй вход соединен с выходом третьего широтно-импульсного модулятора, а выход соединен с управляющим входом третьего регулирующего элемента.

и.

Чг«,35

й/г

Фаа.г

hhntiti

| Импульсный стабилизатор напряжения | 1983 |

|

SU1117611A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Импульсный стабилизатор | 1980 |

|

SU875361A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Шуваев Ю.Н | |||

| и др | |||

| Компенсационно- параметрический импульсный стабилизатор напряжения | |||

| Электронная техника в автоматике | |||

| Под ред Ю.И.Конева | |||

| М.: Радио и связь, 1985, вып | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Способ запрессовки не выдержавших гидравлической пробы отливок | 1923 |

|

SU51A1 |

Авторы

Даты

1988-11-15—Публикация

1987-05-29—Подача