Изобретение относится к электротехнике и может быть использовано во вторичных источниках электропитания радиоэлектронной аппаратуры.

Цель изобретения - повьшение КПД при сохранении динамической стабильности во всех переходных режимах.

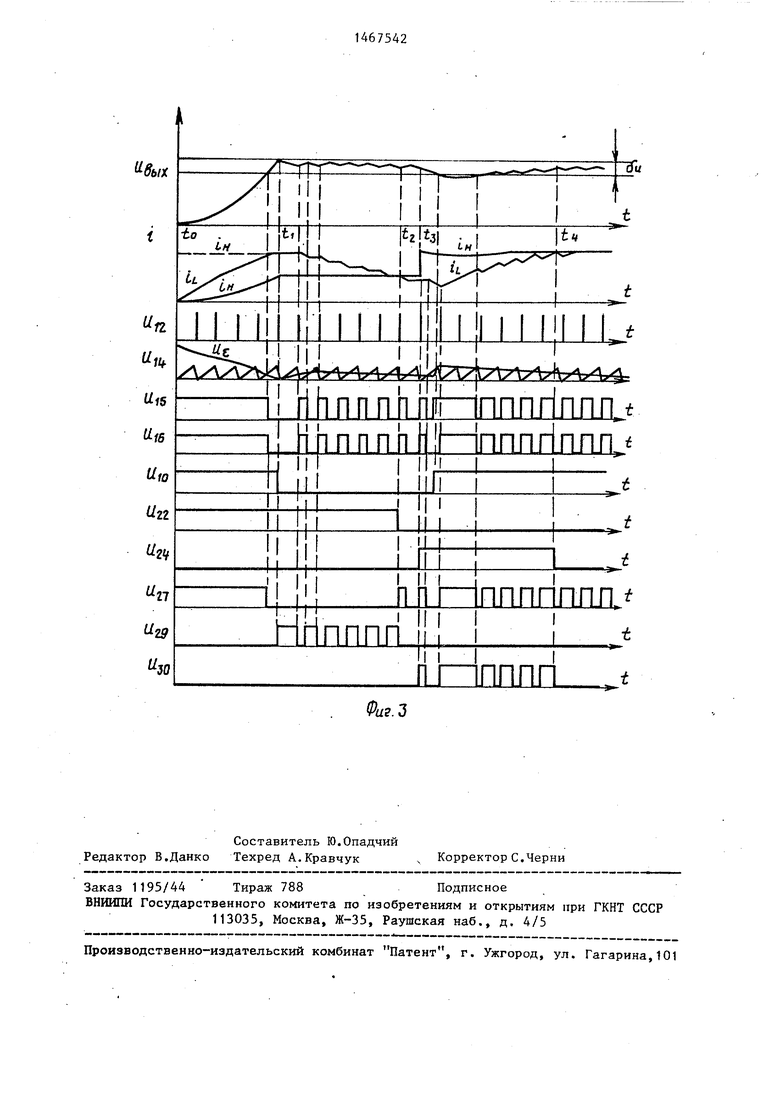

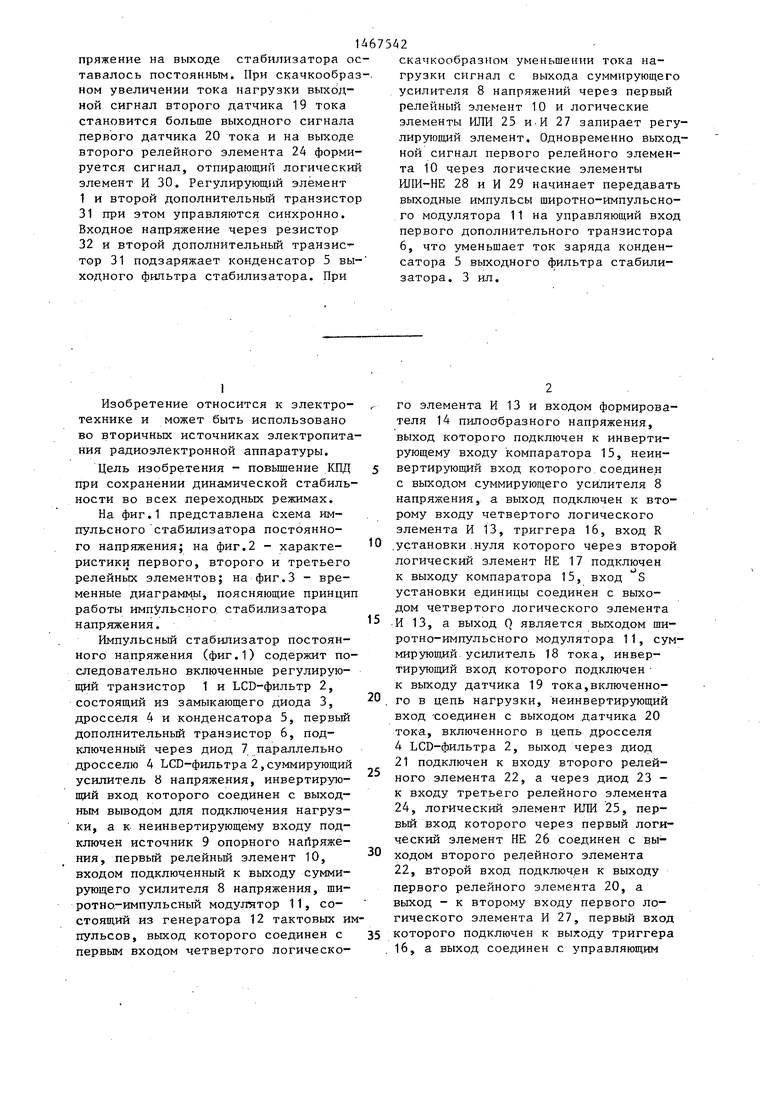

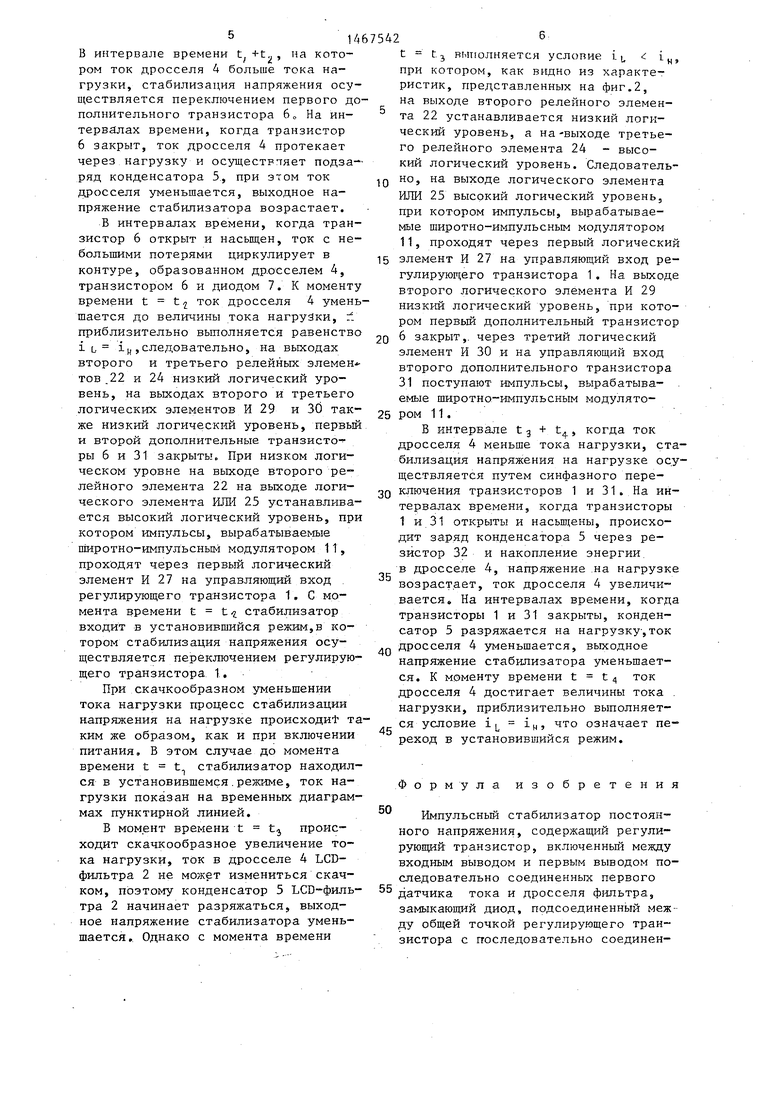

На фиг,1 представлена схема импульсного стабилизатора постоянного напряжения; на фиг,2 - характе- ристики первого, второго и третьего релейных элементов; на фиг,3 - временные диаграммы, поясняющие принцип работы импульсного стабилизатора напряжения,

Импульсный стабилизатор постоянного напряжения (фиг,1) содержит последовательно включенные регулирующий транзистор 1 и LCD-фильтр 2, состоящий из замыкающего диода 3, дросселя 4 и конденсатора 5, первый дополнительньш транзистор 6, подключенный через диод 7 параллельно дросселю 4 ЬСВ-фильтра 2,суммирующий усилитель 8 напряжения, инвертирующий вход которого соединен с выходным выводом для подключения нагрузки, а к неинвертирующему входу подключен источник 9 опорного найряже- ния, первый релейный элемент 10, входом подключенный к выходу суммирующего усилителя 8 напряжения, щи- ротно-импульсный модулятор 11, состоящий из генератора 12 тактовых импульсов, выход которого соединен с первым входом четвертого логическо-

5

0

5

0

го элемента И 13 и входом формирователя 14 пилообразного напряжения, выход которого подключен к инвертирующему входу компаратора 15, неин- вертирзтощий вход кот-орого соединен с выходом суммирующего усилителя 8 напряжения, а выход подключен к второму входу четвертого логического элемента И 13, триггера 16, вход R .установки .нуля которого через второй логический элемент НЕ 17 подключен к выходу компаратора 15, вход S установки единицы соединен с выходом четвертого логического элемента И 13, а выход Q является выходом ши- ротно-импульсного модулятора 11, суммирующий усилитель 18 тока, инвертирующий вход которого подключен к выходу датчика 19 тока,включенного в цепь нагрузки, неинвертирующий вход -соединен с выходом датчика 20 тока, включенного в цепь дросселя 4 LCD-фильтра 2, выход через диод 21 подключен к входу второго релейного элемента 22, а через диод 23 - к входу третьего релейного элемента 24, логический элемент ИЛИ 25, первый вход которого через первый логический элемент НЕ 26 соединен с выходом второго ре:1ейного элемента 22, второй вход подключен к выходу первого релейного элемента 20, а выход - к второму входу первого логического элемента И 27, первый вход которого подключен к выходу триггера 16, а выход соединен с управляющим

31

входом регулирующего транзистора 1, логический элемент ИЛИ-НЕ 28, первы вход которого соединен с выходом триггера 16, второй вход подключен к выходу первого релейного элемента 10, а выход соединен с вторым входом второго логического элемента И 29, первый вход которого подключен к выходу второго релейного элемента 22, а выход - к управляющему входу первого дополнительного транзистора 6, третий логический элемент И 30, первый вход.которого подключен к .выходу третьего релейного элемента 24, второй вход сединен с выходом триггера 16, выход подключен к управляющему входу второго дополнительного транзистора 31, включенного последовательна с резистором 32 между входным и выходным вьшодами стабилизатора.

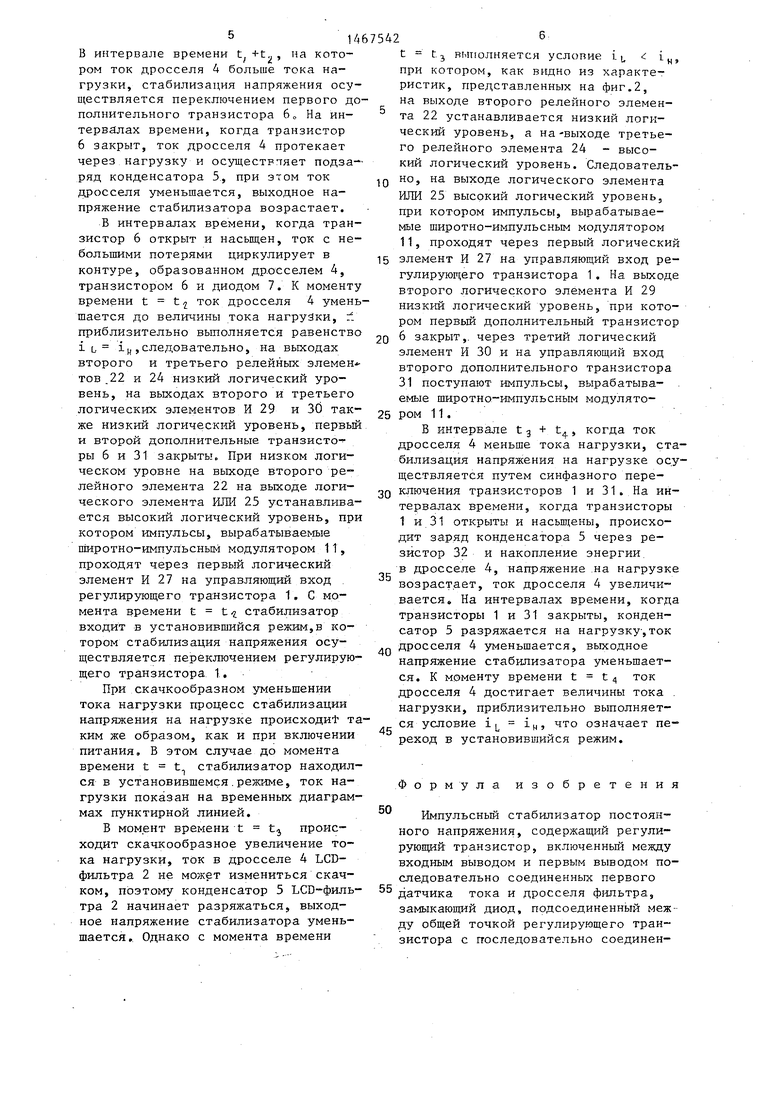

Характеристики первого, второго и третьего релейных элементов пред

ставлены на фиг.2, где i IL i ,f, -UH. Зона нечувствительности «Г; релейных элементов 22 и 24 выбирается в зависимости от ампли- тур;ы пульсаций тока емкости в установившемся режиме tf ( + + 2) i У(. . Ширина петли сГи релейного элемента 10 выбирается равной амплитуде линейной развертки.

Принцип действия стабилизатора поясняется временными диаграммами, представленными на фиг.З.

При включении питания в момент времени t t выходное напряжение, стабилизатора, ток дросселя и ток нагрузки равны нулю. До момента вре- мени t t ,, в который напряжение . на выходе стабилизатора достигает уровня опорного напряжения,на выходе первого релейного элемента 10, характеристика которого показана на фиг.2, высокий логический уровень, на выходе логического элемента ИЛИ 25 также высокий логический уровень, следовательно, импульсы, вьфабатыва- емые широтно-импульсным модулятором 11 проходят через первый логиче- ский элемент И 27 на управляющий вхо регулирующего транзистора 1. До тех пор, пока отклонение выходного напряжения от опорного больше амплиту

ды пилообразного напряжения, на вы ходе широтно-импульсного модулятора 11 сохраняется высокий логический уровень, при котором регулирующий

,-

транзистор 1 открыт и находится в насыщении.

В интервале времени to-t , ил пы- ходе логического элемента ИЛН-НЕ 26 низкий логический уровень, на выходе второго логического элемента И 29 также низкий логический уровень,следовательно, первый дополнительный транзистор 6 закрыт. Диод 7 исключает подачу обратного напряжения на транзистор 6 в интервалах времени, соответствующих открытому состоянию транзистора 1. В рассматриваемом интервале времени с - t , происходит заряд конденсатора 5 LCD-фильтра 2. При этом для токов выполняется соотношение

1 1 ic + IH,

Q 5 20

35

25 ЗО ., 45

55

; где IL, (- н токи через дрос- сель 4, конденсатор 5 и нагрузку, соответственно. Имеет место условие 1ц 5 i, при котором на выходе суммирующего усилителя 18 тока положительный потенциал, следовательно, как видно из характеристик, приведенных на фиг.2, на выходе второго релейного элемента 22 высокий логический уровень, а на выходе третьего релейного элемента 24 низкий логический уровень, на выходе третьего логического элемента И 30 также низкий логический уровень, при котором второй дополнительный транзистор 31 закрыт.

В момент времени t t,, когда отклонение выходного напряжения от опорного равно нулю, на выходе первого релейного элемента 10 устанавливается низкий логический уровень. Условие i ц i н продолжает вьшол- няться, следовательно, на выходе второго релейного элемента 22 высокий логический уровень, значит на обоих входах логического элемента ИЛИ 25 , низкий логический уровень, на его выходе низкий логический уровень, ре- гулир тощий транзистор 1 закрыт. При низком логическом уровне на выходе первого релейного элемента 10 и высоком логическом уровне на выходе ., второго релейного элемента 22 импульсы, вьграбатьгоаемые широтно-им- пульсным модулятором 11, инвертируются логической схемой ИЛИ-НЕ 28 и через вторую логическую схему И 29 проходят на управляюгаиь вход первого дополнительного тран-ч гтора 6.

1467542

В интервале времени t +t,;

на кото-

ром ток дросселя 4 больше тока нагрузки, стабилизация напряжения осуществляется переключением первого дополнительного транзистора 6 о На интервалах времени, когда транзистор 6 закрыт, ток дросселя 4 протекает через нагрузку и осущестрпяет подза- ряд конденсатора 5, при этом ток дросселя уменьшается, выходное напряжение стабилизатора возрастает.

В интервалах времени, когда транзистор 6 открыт и насыщен, ток с небольшими потерями циркулирует в контуре, образованном др.осселем 4, транзистором 6 и диодом 7, К моменту времени t t ток дросселя 4 уменьшается до величины тока нагрузки, : приблизительно вьшолняется равенство io i, следовательно, на выходах второго и третьего релейных элемен тов .22 и 24 низкий логический уровень, на выходах второго и третьего логических элементов И 29 и 30 также низкий логический уровень, первый и второй дополнительные транзисторы 6 и 31 закрыты. При низком логическом уровне на выходе второго ре- лейного элемента 22 на выходе логического элемента ИЛИ 25 устанавливается высокий логический уровень, при котором импульсы, вырабатываемые пшротно-импульсным модулятором 11, проходят через первый логический элемент И 27 на управляющий вход . регулирующего транзистора 1, С момента времени t t стабилизатор входит в установившийся режим,в котором стабилизация напряжения осуществляется переключением регулирующего транзистора 1,

При скачкообразном уменьшении тока нагрузки процесс стабилизации напряжения на нагрузке происходиФ таким же образом, как и при включении питания, В этом случае до момента времени t t стабилизатор находился в установившемся.режиме, ток нагрузки показан на временных диаграммах пунктирной линией.

В момент времени t tj происходит скачкообразное увеличение тока нагрузки, ток в дросселе 4 LCD- фильтра 2 не может измениться скачком, поэтому конденсатор 5 LCD-фильтра 2 начинает разряжаться, выходное напряжение стабилизатора уменьшается. Однако с момента времени

6

t t J выполняется условие i (, i при котором, как видно из характеристик, представленных на фиг,2, на выходе второго релейного элемента 22 устанавливается низкий логический уровень, а на-выходе третьего релейного элемента 24 - высокий логический уровень. Следователь0

ИЛИ 25 высокий логический уровень, при котором импульсы, вырабатываемые широтно-импульсным модулятором 11, проходят через первый логический

5 элемент И 27 на управляюрдий вход регулирующего транзистора 1. На выходе второго логического элемента И 29 низкий логический уровень, при котором первьш дополнительный транзистор 6 закрыт,, через третий логический элемент И 30 и на управляющий вход второго дополнительного транзистора 31 поступают импульсы, вырабатываемые широтно-импульсным модулято5 ром 11,

В интервале t- + t, когда ток дросселя 4 меньше тока нагрузки, стабилизация напряжения на нагрузке осуществляется путем синфазного пере0 ключения транзисторов 1 и 31. На интервалах времени, когда транзисторы 1 и 31 открыты и насьш1;ены, происходит заряд конденсатора 5 через резистор 32 и накопление энергии.

в дросселе 4, напряжение .на нагрузке

5/

возрастает, ток дросселя 4 увеличивается. На интервалах времени, когда транзисторы 1 и 31 закрыты, конденсатор 5 разряжается на нагрузку, ток

„ дросселя 4 уменьшается, выходное напряжение стабилизатора уменьшается. К моменту времени t t 4 ток дросселя 4 достигает величины тока . нагрузки, приблизительно выполняет45

что означает пе-

ся условие 1 1,

реход в установившийся режим.

о р м у л а

изобретения

50

55

Импульсный стабилизатор постоянного напряжения, содержащий регулирующий транзистор, включенный между входным выводом и первым выводом последовательно соединенных первого датчика тока и дросселя фильтра, замыкающий диод, подсоединенный между общей точкой регулирующего транзистора с последовательно соединен

71

ными первым AarqviKOM тока и дросселем фильтра и общей шиной, конденсатор фильтра, включенный последовательно с вторым датчиком тока между выходным выводом и общей шиной, усилитель рассогласования по напряжению, одним входом подключенньй к выходному выводу, а другим входом подключенный к источнику опорного напряжения, широтно-импульсный модулятор, одним входом подключенный к выходу усилителя рассогласования по напряжению, а другим входом подсоединенный к выходу генератора пилообразного напряжения, первый допол- .нительный транзистор, включенный по- следовательно с резистором между входным выводом и общей точкой кон- денсатора фильтра с вторым датчиком тока и входом подсоединенный через первый логический элемент к выходу широтно-импульсного модулятора, второй дополнительный транзистор, включенный параллельно последовательно соединенным дросселю фильтра к первому датчику тока,усилитель рассогласования по току, подключенный вхдами к выходам первого и второго датчиков тока, первый и второй ре- лейные элементы, подключенные к выхду усилителя рассогласования по. току, второй и третий логические элементы И, логический элемент НЕ и тртий релейньй элемент, причем вход второго логического элемента И подключен к управляющему входу второго дополнительного транзистора, выход третьего логического элемента И со

8

единен с управляющим входом porynvr- рующего транзистора, первый вход третьего элемента И подключен к выходу широтно-импульсного модулятора, отличающийся тем, что, с целью повышения КПД при сохранении динамической стабильности во всех переходных режимах, в него введены логический элемент ИЛИ-НЕ, логический элемент ИЛИ, а третий релейньп элемент выполнен с гистерезисной характеристикой, причем выход усилителя рассогласования по напряжению подключен к входу третьего релейного элемента, выход которого подключен к первому входу логического элемента ИЛИ-НЕ и первому входу логического элемента ИЛИ, выход первого релейного элемента подключен к первому входу первого логического элемента И, выход второго релейного элемента подключен к первому входу второго логического элемента И и через логический элемент НЕ подключен к второму входу логического элемента ИЛИ, выход которого подключен к второму входу третьего логического элемента И, выход широтно-импульсного модулятора подключен к второму входу логического элемента ИЛИ-НЕ, выход логического элемента ИЛИ-НЕ подключен к второму входу второго логического элемента И, общая точка последовательно соединенных конденсатора фильтра с вторым датчиком тока .подключен к второму выводу последовательно соединенных дросселя фильтра и первого датчика тока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный стабилизатор напряжения | 1987 |

|

SU1408428A1 |

| Импульсный стабилизатор напряжения | 1987 |

|

SU1508262A1 |

| Импульсный стабилизатор напряжения | 1986 |

|

SU1334134A1 |

| Компенсационно-параметрический импульсный стабилизатор постоянного напряжения | 1987 |

|

SU1437845A1 |

| Импульсный стабилизатор напряжения | 1983 |

|

SU1121659A1 |

| Импульсный стабилизатор | 1980 |

|

SU875361A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ С ИМПУЛЬСНЫМ РЕГУЛИРОВАНИЕМ | 1991 |

|

RU2014646C1 |

| Параметрический импульсный стабилизатор постоянного напряжения | 1980 |

|

SU935929A1 |

| Импульсный стабилизатор постоянного напряжения | 1985 |

|

SU1343401A1 |

Изобретение относится к источникам вторичного электропитания радиоэлектронной аппаратуры. Целью изобретения является повьщение КПД при сохранении динамической стабильности в переходных режимах. Широтно- импульсный модулятор 11 по сигналу суммирующего усилителя 8 изменяет относительную длительность включенного состояния регулирующего трак- - зистора 1 так, чтобы выходное на

| Импульсный стабилизатор напряжения | 1983 |

|

SU1117611A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Импульсный стабилизатор напряжения | 1987 |

|

SU1408428A1 |

Авторы

Даты

1989-03-23—Публикация

1987-01-29—Подача