4ik. Од

qD to

9иг.1

1437912

Изобретение относится к вычислительной технике и может быть использовано в информационно-вычислительных системах для перезаписи информации из блока постоянной памяти в блок оперативной памяти.

Цель изобретения - снижение потребляемой устройством мопиюсти от источника постоянного питания при сох- Q ранении достоверности перезаписи информации из блока постоянной памяти в блок О Перативной памяти.

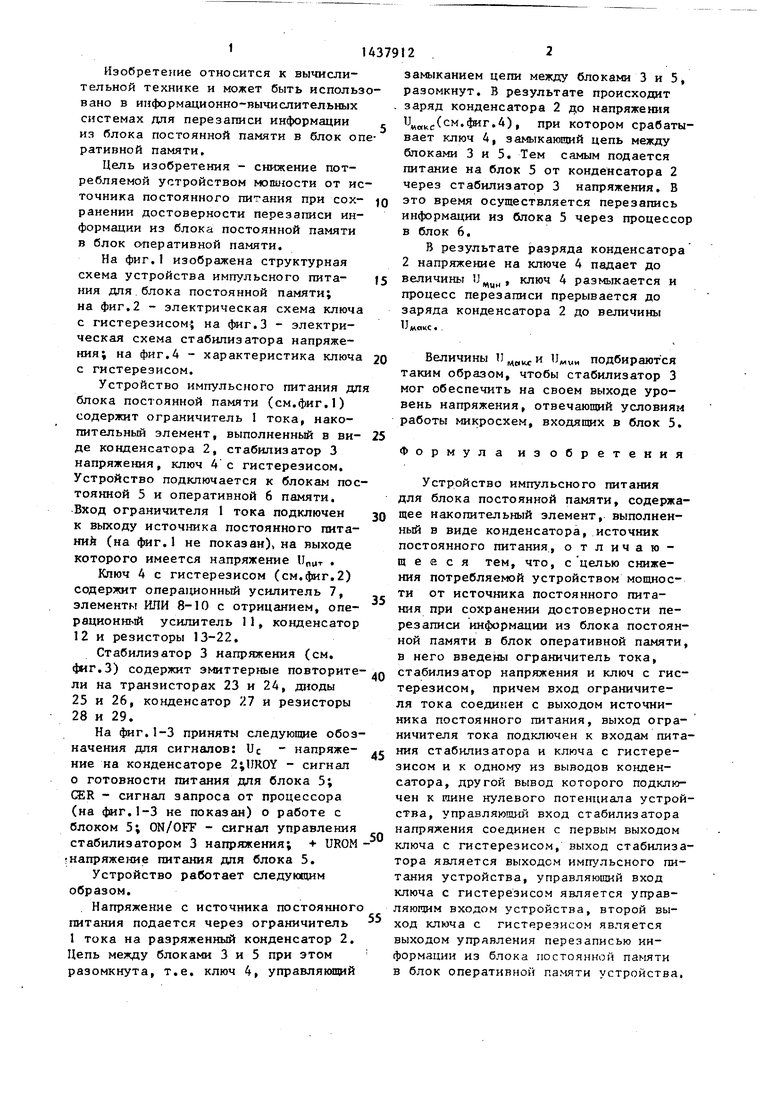

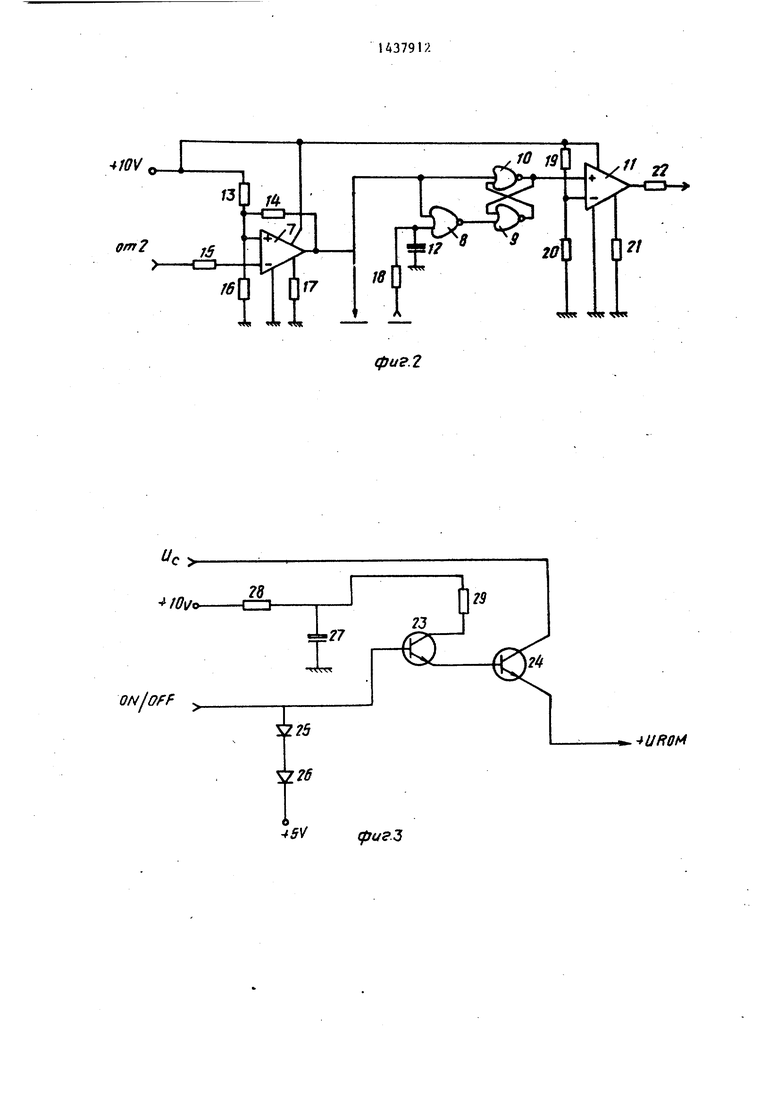

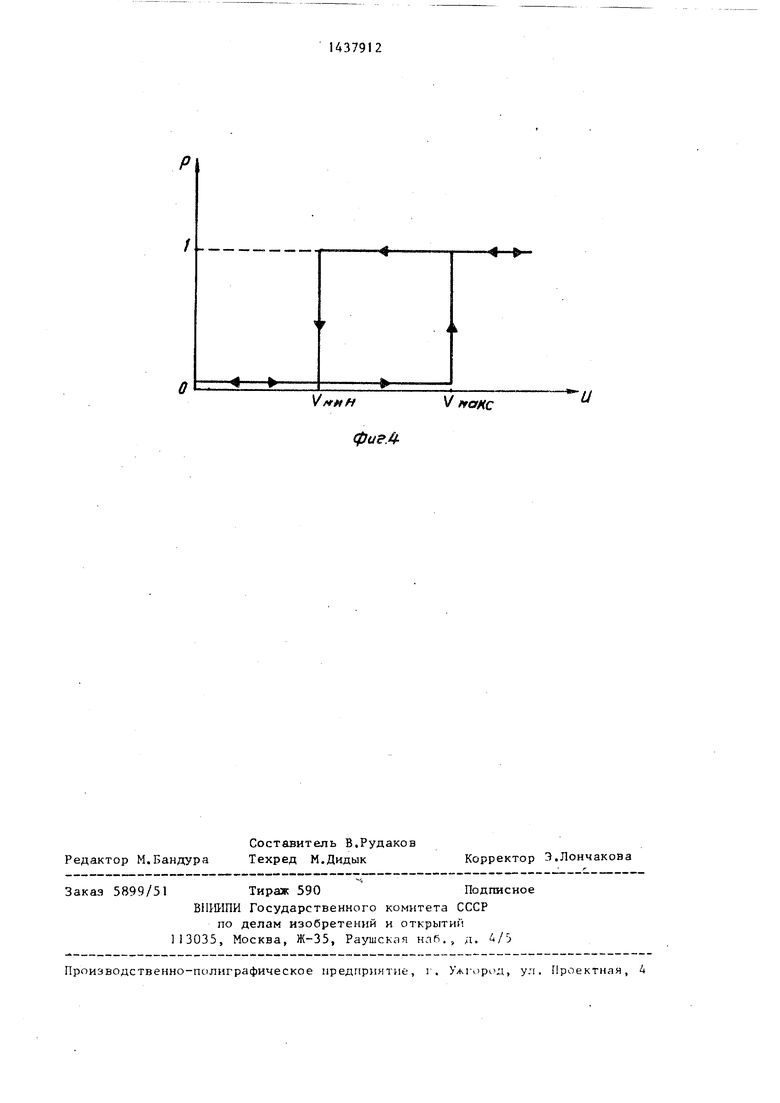

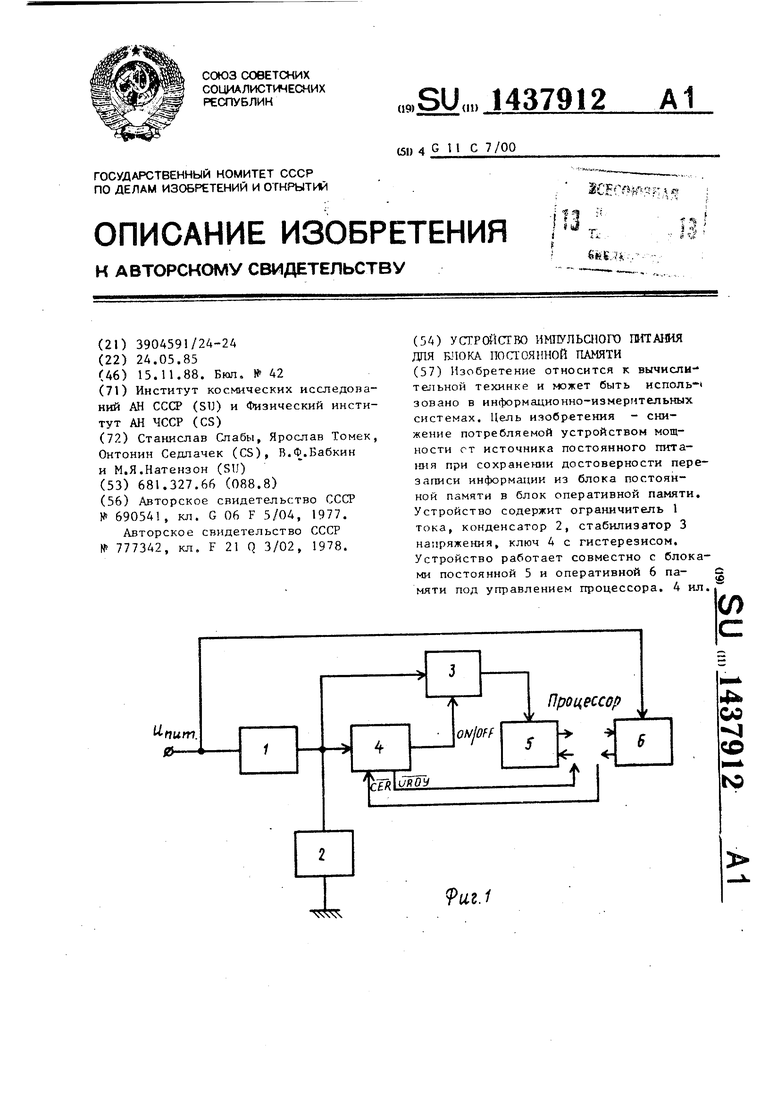

На фиг.1 изображена структурная схема устройства импульсного пита- |5 ния дпя блока постоянной памяти; на фиг,2 - электрическая схема ключа с гистерезисом-; на фиг,3 - электрическая схема стабилизатора напряжения; на фиг,4 - характеристика ключа 20 с гистерезисом.

Устройство импульсного питания дпя блока постоянной памяти (см,фиг,1) содержит ограничитель I тока, накопительный элемент, выполненный в ви- 25 е конденсатора 2, стабилизатор 3 напряжения, ключ 4с гистерезисом. стройство подключается к блокам посоянной 5 и оперативной 6 памяти. Вход ограничителя 1 тока подключен зо выходу источника постоянного питаий (на фиг, 1 не показан), на выходе которого имеется напряжение .

Ключ 4 с гистерезисом (см,фиг,2) содержит опера1Ц1онный усилитель 7, лементы ИЛИ 8-10 с отрицанием, опеационный усилитель 11, конденсатор 12 и резисторы 13-22,

Стабилизатор 3 напряжения (см, иг,3) содержит эмиттерные повторите-д«

35

и на транзисторах 23 и 24, диоды 5 и 26, конденсатор 27 и резисторы 28 и 29,

На фиг,1-3 приняты следующие обозачения дпя сигналов: Uc напряжеие на конденсаторе 2;икО - сигнал

готовности питания для блока 5; ER - сигнал запроса от процессора (на фиг,1-3 не показан) о работе с локом 5; ON/OFF - сигнал управления табилизатором 3 напряжения; + UROM апряжение питания дпя блока 5, Устройство работает следующим

бразом.

Напряжение с источника постоянного

итания подается через ограничитель

1тока на разряженный конденсатор 2, епь между блоками 3 и 5 при этом азомкнута, т,е, ключ 4, управлянядий

45

50

55

за ра за и ва бл пи че эт ин в

2 ве пр за

1 «

та мо ве ра

Ф

дл ще ны по щ ни ти ни ре но в ст те ля ни ни ни зи са че ст на кл то та кл ля хо вы фо в

замыканием цепи между блоками 3 и 5, разомкнут, В результате происходит заряд конденсатора 2 до напряжения .(см,фиг,4) , при котором срабатывает ключ 4, замыкающий цепь между блоками 3 и 5. Тем самым подается питание на блок 5 от конденсатора 2 через стабилизатор 3 напряжения, В это время осуществляется перезапись информации из блока 5 через процессо в блок 6,

В результате разряда конденсатора 2 напряжение на ключе 4 падает до величины , ключ 4 размыкается и процесс перезаписи прерывается до заряда конденсатора 2 до величины

1 «акС.

Величины П „ и „„„ подбираются таким образом, чтобы стабилизатор 3 мог обеспечить на своем выходе уровень напряжения, отвечающий условиям работы микросхем, входящих в блок 5,

Формула изобретения

Устройство импульсного питания для блока постоянной памяти, содержащее накопительный элемент, выполненный в виде конденсатора, источник постоянного питания,, отличающееся тем, что, с целью снижения потребляемой устройством мощности от источника постоянного питания при сохранении достоверности перезаписи информации из блока постоянной памяти в блок оперативной памяти, в него введены ограничитель тока, стабилизатор напряжения и ключ с гистерезисом, причем вход ограничителя тока соединен с выходом источни- ника постоянного питания, выход ограничителя тока подключен к входам питания стабилизатора и ключа с гистерезисом и к одному из выводов конденсатора, другой вывод которого подключен к тине нулевого потенциала устройства, управляющий вход стабилизатора напряжения соединен с первым выходом ключа с гистерезисом, выход стабилизатора является выходом импульсного питания устройства, управляющий вход ключа с гистерезисом является управляющим входом устройства, второй выход ключа с гистерезисом является выходом управления перезаписью информации из блока постоянной памяти в блок оперативной памяти устройства.

410

от

19 J .//

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации @ временных интервалов | 1981 |

|

SU1022109A1 |

| Вторичный источник питания постоянного напряжения | 1986 |

|

SU1325439A1 |

| Цифровая система регулирования соотношения скоростей многодвигательного электропривода | 1980 |

|

SU944045A1 |

| Устройство заряда накопительного конденсатора | 1986 |

|

SU1413705A1 |

| Устройство фазоимпульсной модуляции | 1985 |

|

SU1411958A1 |

| УСТРОЙСТВО СТИРАНИЯ ЗАПИСАННОЙ ИНФОРМАЦИИ | 2010 |

|

RU2428754C1 |

| Импульсный стабилизатор мощности | 1988 |

|

SU1686423A1 |

| УСТРОЙСТВО КОНТЕЙНЕРНОЕ ОПЕРАТИВНОГО УНИЧТОЖЕНИЯ ИНФОРМАЦИИ НА МАГНИТНЫХ НОСИТЕЛЯХ | 2008 |

|

RU2368019C1 |

| Электромагнитный преобразователь расхода | 1988 |

|

SU1739203A1 |

| БЛОК ПОСТОЯННОГО ЗАПАЗДЫВАНИЯ | 1971 |

|

SU321820A1 |

Изобретение относится к вычислительной техинке и может быть исполь- зовано в информационно-измерительных системах. Цель изобретения - снижение потребляемой устройством мощности от источника постоянного гогга- ния при сохранении достоверности перезаписи информации из блока постояи- ной памяти в блок оперативной памяти. Устройство содержит ограничитель 1 тока, конденсатор 2, стабилизатор 3 напряжения, ключ 4 с гистерезисом. Устройство работает совместно с блоками постоянной 5 и оперативной 6 памяти под управлением процессора. 4 ил. (Л

8

7

ONJOFF

25

45V

фи.2

D

29

r-d

(fju.:5

-4

V/vMff franc

фиеЛ

U

| Радиоприемник | 1946 |

|

SU69054A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство управления импульсными световыми маяками | 1978 |

|

SU777342A1 |

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

Авторы

Даты

1988-11-15—Публикация

1985-05-24—Подача