со ел

00

Изобретение относится к импульсной технике и может быть использовано в системах передачи информации с фазоимпульсной модуляцией при наличии реверберационных помех в канале связи.

Целью изобретения является повьпие- ние достоверности передаваемой информации.

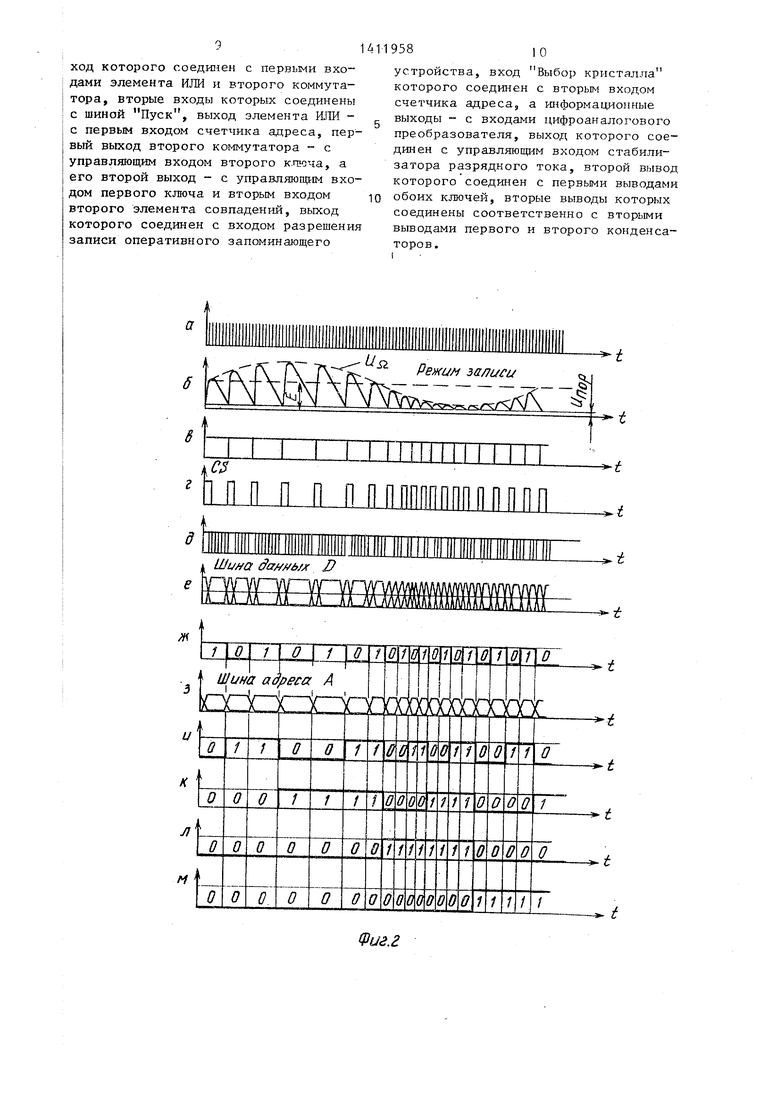

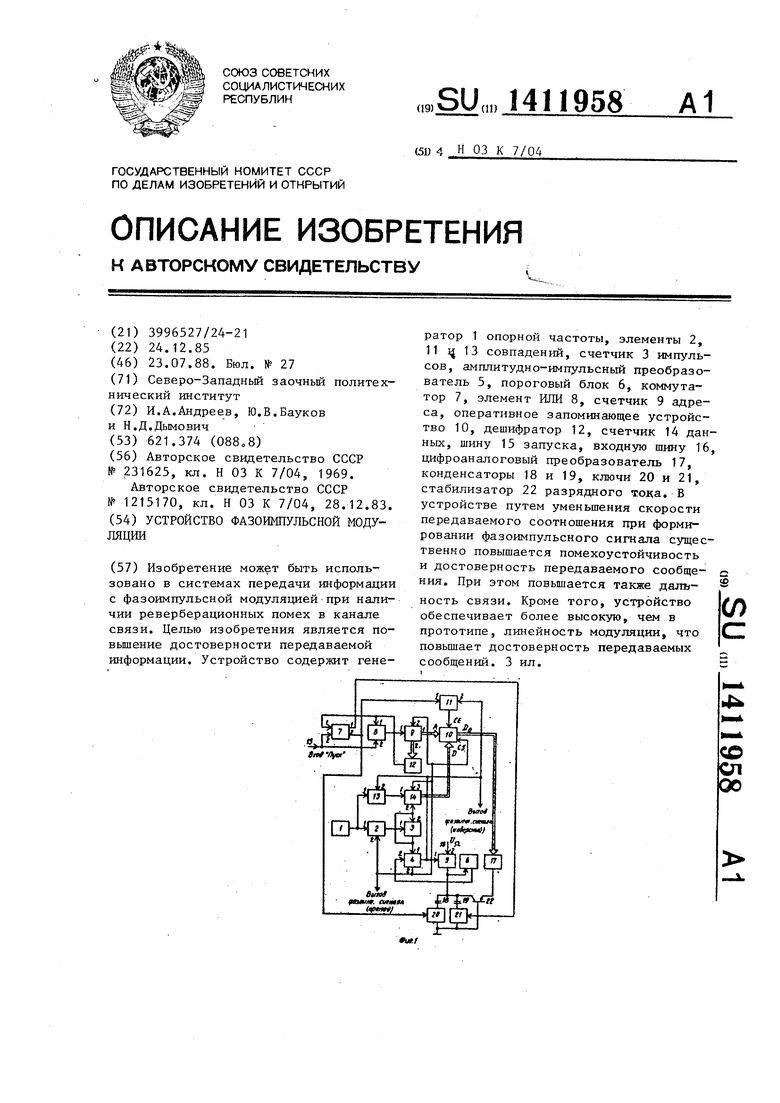

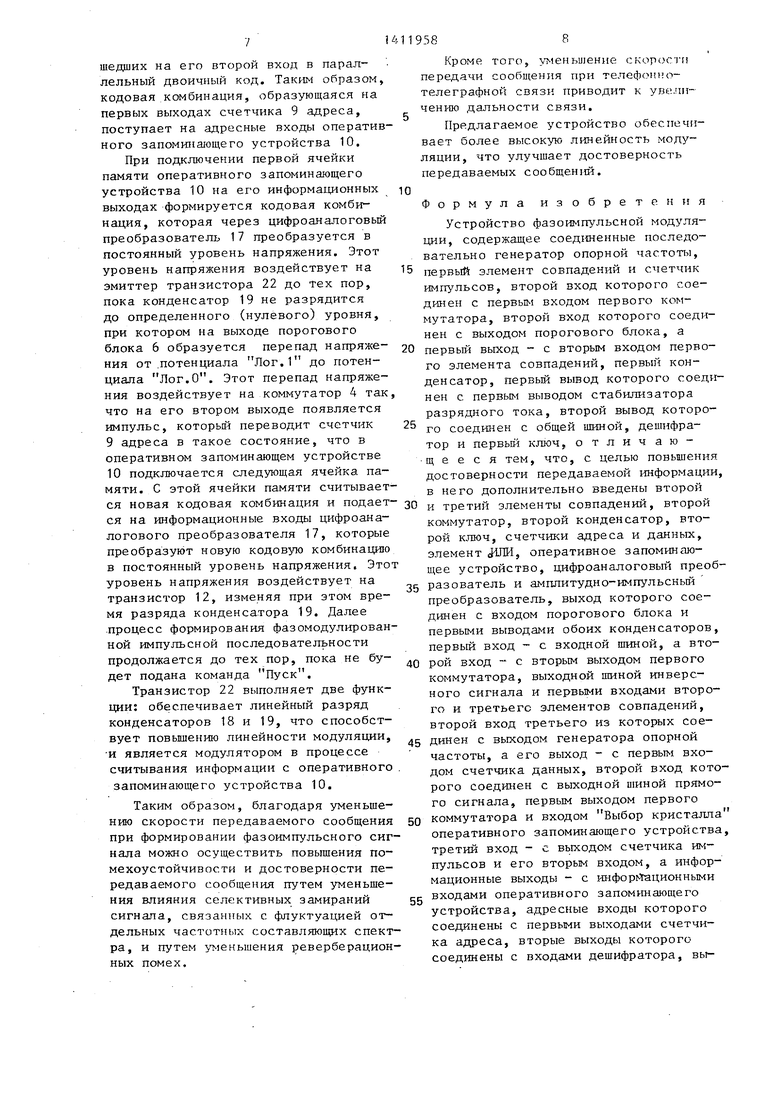

На фиг,1 приведена функциональная схема устройства фазоимпульсной модуляции; на фиг.2 - временные диаграммы работы устройства в режиме записи на фиг.З - то же, в режиме считыва- ния„

Устройство фазоимпульсной модуля- ции содержит генератор 1 опорной частоты, элемент 2 совпадений, счетчик 3 импульсов, коммутатор 4, амплитудно-импульсный преобразователь 5, пороговый блок 6, коммутатор-7, элемент ИЛИ 8, счетчик 9 адреса, оперативное запоминающее устройство 10,

0

5

0

с первым входом счетчика 9 ;щреса, первые выходы которого соединены с адресными входами оперативного запоминающего устройства 10, вторые выходы - с входами дешифратора 12, а второй вход - с вторым выходом коммутатора 4, выходной пшной прямого сигнала, вторым входом элемента 2 совпадений, третьим входом счетчика 14 данных и входом выбора кристалла оперативного запоминающего устройства 10, информационные входы которого соединены с выходами счетчика 14 данных, вход разрешения записи - с выходом элемента 11 совпадений, а информационные выходы - с входами цифро- аналогового преобразователя 17, выход которого соединен с управляющим входом стабилизатора 22 разрядного тока, а второй вход элемента 11 совпадений с вторым выходом коммутатора 7.

Коммутатор 4 может быть выполнен на основе D-триггера, инверсньй выход

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазоимпульсной модуляции | 1986 |

|

SU1458967A1 |

| Фазоимпульсный демодулятор | 1986 |

|

SU1415436A1 |

| Устройство для отладки многопроцессорных систем | 1987 |

|

SU1446624A1 |

| Устройство для контроля блоков оперативной памяти | 1989 |

|

SU1689994A2 |

| ПРЕОБРАЗОВАТЕЛЬ КОД-НАПРЯЖЕНИЕ | 1991 |

|

SU1826837A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1541616A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1829117A1 |

| Сенсорный переключатель | 1986 |

|

SU1425824A1 |

| Стереотелевизионная камера с автоматической фокусировкой | 1989 |

|

SU1774518A1 |

Изобретение может быть использовано в системах передачи информации с фазоимпульсной модуляцией при нали чии реверберационных помех в канале связи. Целью изобретения является повышение достоверности передаваемой информации. Устройство содержит генератор 1 опорной частоты, элементы 2, 11 ц 13 совпадений, счетчик 3 импульсов, амплитудно-импульсный преобразователь 5, пороговый блок 6, коммутатор 7, элемент ИЛИ 8, счетчик 9 адреса, оперативное запоминающее устройство 10, дешифратор 12, счетчик 14 данных, шину 15 запуска, входную шину 16, цифроанапоговый преобразователь 17, конденсаторы 18 и 19, ключи 20 и 21, стабилизатор 22 разрядного тода. В устройстве путем уменьшения скорости передаваемого соотношения при формировании фазоимпульсного сигнала существенно повышается помехоустойчивость и достоверность передаваемого сообщения. При этом повышается также дальность связи. Кроме того, устройство обеспечивает более высокую, чем в прототипе, линейность модуляции, что повьш1ает достоверность передаваемых сообщений. 3 ил. (С (Л

30

элемент 11 совпадений, дешифратор 12, 25 которого соединен с его D-входом, а элемент 13 совпадений, счетчик 14 данных, шину 15 пуска, входную шину

16,цифроаналоговый преобразователь

17,конденсаторы 18 и 19, ключи 20 и 21, стабилизатор 22 разрядного тока, при этом выход генератора 1 опорной частоты через элементы 13 и 2 совпадений подключен соответственно к первым входам счетчика 14 данных и счетчика 3 импульсов, вторые входы которых соединены с выходом счетчика 3 импульсов и первым входом коммутатора 4, второй вход которого соединен с выходом порогового блока 6, а первьй выход - с вторым входом элемента 13 совпадений, с первым входом элемента

40

синхронизирующий вход и R-вход подключены к первому и второму входам коммутатора соответственно. Коммутатор 7 может быть выполнен на основе RS-триггера, S-и R-входы которого подключены е первому и второму входам коммутатора соответственно. Стабилизатор 22 ра,зрядного тока может быть выполнен на транзисторе, коллек тор и база которого соединены с выво дами стабилизатора, а эмиттер являет ся его управляющим входом, ток в ко- торьш обеспечивает цифроаналоговьй преобразователь 17. Оперативное запо минающее устройство 10 может быть вы полнено на микросхемах памяти 155 ил 565 серий.

11 совпадений, с выходной ишной ин-

версного сигнала и первым входом амплитудно-импульсного преобразователя 3, второй вход которого соединен с

входной шиной 16, а выход - с входом порогового блока 6 и первыми выводами конденсаторов 18 и 19 и стабилизатора 22 разрядного тока, вторые выводы которых соединены соответственно через ключи 20 и 21, а стабилизатора 22 непосредственно с общей шиной, причем управляющие входы ключей 21 и 20 соединены соответственно с первым и вторым входами коммутатора 7, первый вход которого соединен с первым входом элемента ИЛИ 8 и выходом дешифратора 12, а второй вход- с шиной 15 пуска и входом элемента ИЛИ 8, выход которого соединен

которого соединен с его D-входом, а

синхронизирующий вход и R-вход подключены к первому и второму входам коммутатора соответственно. Коммутатор 7 может быть выполнен на основе RS-триггера, S-и R-входы которого подключены е первому и второму входам коммутатора соответственно. Стабилизатор 22 ра,зрядного тока может быть выполнен на транзисторе, коллектор и база которого соединены с выво- дами стабилизатора, а эмиттер является его управляющим входом, ток в ко- торьш обеспечивает цифроаналоговьй преобразователь 17. Оперативное запоминающее устройство 10 может быть выполнено на микросхемах памяти 155 или 565 серий.

На фиг.2 показаны сигнал на выходе генератора 1 опорной частоты (а), сигнал на входе порогового блока 6 (б), сигнал на выходе порогового блока 6 в режиме записи (в), фазомодулирован- ный сигнал на втором выходе коммутатора 4 (г), на процесс преобразования интервала времени в количество импульсов (д), происходящий в счетчике 14 данных, сигнал на выходе счетчика 14 данных в режиме записи (е), сигналы на первых выходах счетчика 9 адреса в режиме записи (ж-м).

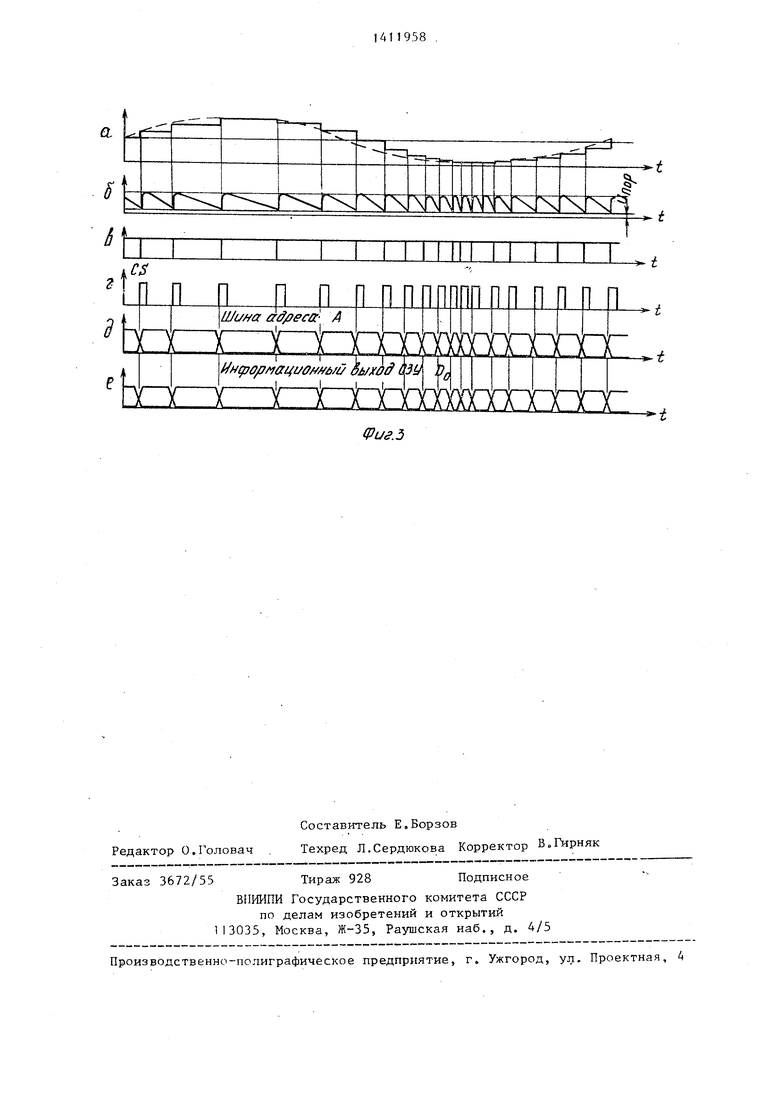

На фиг.З показаны сигнал, на выходе цифроаналогового преобразователя 17 в режиме считывания (а), сигнал на входе порогового блока 6 в режиме считывания (б), сигнал на выходе по

31

рогового блока 6 п режлме считывания

(в), фазоимпульсный сигнал на втором выходе коммутатора 4 в режиме считывания (г), сигналы на шине адреса и выходной информационной тине опера- тивного запоминающего устройства 10 в режиме считывания (д,е).

Устройство фазоимп льсной модуляции работает следующим образом.

По команде Пуск на шину 15 по- дается короткий пусковой импульс длительностью несколько микросекунд, при этом коммутатор 7 устанавливается в такое положение, что на его первом выходе появляется потенциал Лог.О, который закрывает ключ 21, По этой команде на входную шину 16 поступает входной сигнал, а на втором выходе (инверсном) коммутатора 7 появляется потенциал Лог.1, кото- рый открывает ключ 20 и создает разрешение по первому входу элементу 11 Открытый ключ 20 замыкает второй вывод конденсатора 18 на общую шину. Таким образом, на обкладках конденсатооа 18 в начальный момент времени нулевой потенциал по отношению к общей шине. Поэтому на выходе порогового блока 6 образуется потенциал Лог.О. Этот потенциал Лог„0 устанавливает коммутатор 4 таким образом что на его первом (прямом) выходе появляется потенциал Лог.О, а на втором (инверсном) - потенциал Лог.1, который открывает по второ- му входу элемент 2 совпадений.

С выхода генератора 1 опорной частоты сигнал в виде меандра поступает на первый вход элемента 2, который

открывается на время ТхМ, где

Т - период следования импульсов опорной частоты, а М - число импульсов. С выхода элемента 2 импульсы подаютс на первый вход счетчика 3 импульсов, который -срабатывает только в те но- менты времени, когда на втором входе элемента 2 присутствует потенциал Лог.1. Сосчитав М импульсов счетчик 3 импульсов устанавливает себя

по второму входу в исходное состояни

(импульсом сброса), Импульс сброса подается также на первый вход коммутатора 4.

Коммутатор 4 управляет работой элемента 2 и амплитудно-импульсного преобразователя 5.

Импульс сброса, поступающий с выхода счетчика 3 импульсов, воздействует на коммутатор 4 так, что на его

5

0 - 0 5

0

5

Q

5

9584

первом выходе появляется потенциал Лог.1, а на втором (инверсном) выходе - Лог.О, Последний закрывает по второму входу элемент 2.

Амплитудно-импульсный преобразователь 5 вьфабатывает постоянное напряжение , на которое накладывается входное переменное напряжение, поступающее по ш1-ше 16. Это происходит только в те моменты времени, когда на первом выходе коммутатора 4 появляется потенциал Лог.О. В это время происходит заряд конденсатора 18. При появлении потенци ала Лог.1 на первом выходе коммутатора 4 прекращается заряд и начинается разряд конденсатора 18 до определенного (нулевого) уровня, при котором на выходе порогового блока 6 образуется перепад напряжения от потенциала Лог.1 до потенциала Лог.О, этот перепад напряжения подается на второй вход (вход установки нуля) коммутатора 4 и управляет его работой. Например, при подаче на. второй вход коммутатора 4 потенциала Лог,О на его первом выходе возникает потенциал Лог.О, а на втором (инверсном вы- . ходе) ЛоГо Г с. Потенциал Лог.Г от коммутатора 4 подается на второй вход элемента 2 и открывает его.

В результате на втором входе элемента 2 появляется последовательность фазомодулированных импульсов положи-, тельной полярности, а на первом выходе коммутатора 4 последовательность фазомодулированных импульсов противоположной полярности.

Фазомодулированная последовательность импульсов, которая образуется на первом выходе коммутатора 4, поступает на второй вход элемента 13 и открывает его на время Т-М, где Тл - время между соседними импульсами фазомодулированной импульсной последовательности. На первый вход элемента 13 поступает сигнал опорной частоты с генератора 1 опорной частоты. Таким образом, на выходе элемента 13 возникает серия (пачка импульсов), число импульсов в пачке зави сит от Та и равно Р (TO- Т-М)/Т. Следовательно, число импульсов в пачке содержит в себе информацию о времени TO. С выхода элемента 13 серии импульсов поступают на первый вход счетчика J4 данных, который преобразует число импульсов в двоичный код (параллельный код). Кодовая комбина10

15

51411958

ция, образующаяся на информационных выходах счетчика 14 данных, поступает на информационные входы оперативного запоминающего устройства 10 только в те моменты времени, когда на третий вход счетчика 14 данных поступает им,пульс разрешения считывания данных, который снимается с второго выхода коммутатора 4, По окончании импульса разрешения считывания данных происходит сброс (отпирание информации) счетчика 14 данных путем подачи на его второй вход (вход установки нуля) импульса сброса, который формируется на выходе счетчика 3 импульсов. Далее процесс формирования кодовых комбинаций повторяется,

По команде Пуск пусковой импульс поступает на второй вход элемента 8 и с его выхода - на первый вход счетчика 9 адреса, обнуляя его. С второго выхода коммутатора 4 последователь- ность фазомодулированных импульсов положительной полярности поступает на второй вход счетчика 9 адреса, который преобразует последовательность импульсов в двоичный код, т.е. десятичное выражение числа ш пульсов пришедших на второй вход счетчика 9 адреса будет преобразовано в двоичное число. Таким образом, кодовая комбинация, образующаяся на первых выходах счетчика 9 адреса, поступает на адресные входы оперативного запоминающего устройства 10.

По команде на первом входе элемента 11 появляется сигнал разрешекристалла на вход разрешения загиси при наличии сигнала Выбор кристалла осуществляет операцию записи. Таким образом, происходят преобразование интервалов времени между импульсами фазомодулированной импульсной последовательности в двоичный код и запис этого кода в оперативное запоминающее устройство 10.

Емкость оперативного запоминающег устройства определяется по формуле С ),cp , где Та - время цикла записи; Т .р - среднее время между соседними импульсами фазомодулирован ной импульсной последовательности. Например, чтобы записать звуковой сигнал с граничной верхней частотой 2,5 кГц, в течение цикла записи, например, 10 с необходимо оперативное запоминающее устройство емкостью 50000 бит, при этом число разрядов должно быть 8-12.

Сосчитав, например, 50000 импульсов фазомодулированной импульсной последовательности счетчик 9 адреса формирует на выходе дешифратора 12 сигнал, который через элемент 8 пода ется на первый вход счетчика 9 адрес и обнуляет его. Кроме того, этот сиг нал подается на первый вход коммутатора 7 и устанавливает его в такое положение, что на его первом выходе появляется сигнал Лог.1, а на втором выходе сигнал Лог.О. Сигнал 35 Лог,О закрывает ключ 20 и элемент 11, запрещая при этом запись в опера тивное запоминающее устройство 10,

20

25

30

ния Лог.1, который позволяет осу- а сигнал Лог.1 поступает на вход ществить прохождение через этот эле- 21 и открывает его, при этом мент фазомодулированной последователь- О второй вывод конденсатора 19 замыка- ности импульсов, которая является сиг- ется на общую шину.

При замыкании второго вывода кон- ден сатора 19 на общую шину на втором выходе кoм yтaтopa 4 появляется пос- 45 ледовательность импульсов, при этом период следования импульсов зависит от величины емкости конденсатора 19. Кроме того, величина емкости конденсатора 19 определяет скорость считыналом разрешения записи. Этот сигнал снимается с первого выхода коммутатора 4 и подается через элемент 11 на вход разрешения записи оперативного запоминающего устройства 10.

С второго выхода коммутатора 4 снимается последовательность фазомодулированных импульсов положительной

При замыкании второго вывода кон- ден сатора 19 на общую шину на втором выходе кoм yтaтopa 4 появляется пос- 45 ледовательность импульсов, при этом период следования импульсов зависит от величины емкости конденсатора 19. Кроме того, величина емкости конденсатора 19 определяет скорость считыполярности, которая является одновре- 50 вания информации (уменьшение, увели- менно сигналом Выбор кристалла и чение) в оперативном запоминающем подается на вход Выбор кристалла оперативного запоминающего устройства 10. Сигнал Выбор кристалла выустройетве 10.

Последовательность импульсов, снимаемая С второго выхода коммутатора

бирает требуемую микросхему из опера- 55 4,поступает на вход Выбор кристалла тивного запоминающего устройства 10, оперативного запоминающего устройст- состоящего из ряда микросхем. Подача ва 10 и на второй вход счетчика 9 управляющего сигнала на вход разреше- адреса, который преобразует десятич- ния записи при наличии сигнала Выбор ое выражение числа i-iMnyjn.coB, про0

5

кристалла на вход разрешения загиси при наличии сигнала Выбор кристалла осуществляет операцию записи. Таким образом, происходят преобразование интервалов времени между импульсами фазомодулированной импульсной последовательности в двоичный код и запись этого кода в оперативное запоминающее устройство 10.

Емкость оперативного запоминающего устройства определяется по формуле С ),cp , где Та - время цикла записи; Т .р - среднее время между соседними импульсами фазомодулирован- ной импульсной последовательности. Например, чтобы записать звуковой сигнал с граничной верхней частотой 2,5 кГц, в течение цикла записи, например, 10 с необходимо оперативное запоминающее устройство емкостью 50000 бит, при этом число разрядов должно быть 8-12.

Сосчитав, например, 50000 импульсов фазомодулированной импульсной последовательности счетчик 9 адреса формирует на выходе дешифратора 12 сигнал, который через элемент 8 подается на первый вход счетчика 9 адреса и обнуляет его. Кроме того, этот сигнал подается на первый вход коммутатора 7 и устанавливает его в такое положение, что на его первом выходе появляется сигнал Лог.1, а на втором выходе сигнал Лог.О. Сигнал 35 Лог,О закрывает ключ 20 и элемент 11, запрещая при этом запись в оперативное запоминающее устройство 10,

0

5

30

а сигнал Лог.1 поступает на вход 21 и открывает его, при этом второй вывод конденсатора 19 замыка- ется на общую шину.

а сигнал Лог.1 поступает на вход 21 и открывает его, при этом второй вывод конденсатора 19 замыка- ется на общую шину.

При замыкании второго вывода кон- ден сатора 19 на общую шину на втором выходе кoм yтaтopa 4 появляется пос- ледовательность импульсов, при этом период следования импульсов зависит от величины емкости конденсатора 19. Кроме того, величина емкости конденсатора 19 определяет скорость считышедших на его второй вход в параллельный двоичный код. Таким образом, кодовая комбинация, образующаяся на первых выходах счетчика 9 адреса, поступает на адресные входы оперативного запоминающего устройства 10. При подключении первой ячейки памяти оперативного запоминающего устройства 10 на его информационных выходах формируется кодовая комбинация, которая через цифроаналоговый преобразователь 17 преобразуется в постоянный уровень напряжения. Этот уровень напряжения воздействует на эмиттер транзистора 22 до тех пор, пока конденсатор 19 не разрядится до определенного (нулевого) уровня, при котором на выходе порогового блока 6 образуется перепад напряже- НИН от .потенциала Лог.1 до потенциала Лог.О. Этот перепад напряжения воздействует на коммутатор 4 так что на его втором выходе появляется импульс, которьй переводит счетчик

9адреса в такое состояние, что в оперативном запоминающем устройстве

10подключается следующая ячейка памяти. С этой ячейки памяти считывается новая кодовая комбинация и подает ся на информационные входы цифроана- логового преобразователя 17, которые преобразуют новую кодовую комбинацию

в постоянный уровень напряжения. Это уровень напряжения воздействует на транзистор 12, изменяя при этом время разряда конденсатора 19. Далее .процесс формирования фазомодулирован ной импульсной последовательности продолжается до тех пор, пока не будет подана команда Пуск.

Транзистор 22 выполняет две функции: обеспечивает линейный разряд конденсаторов 18 и 19, что способствует повышению линейности модуляции, и является модулятором в процессе считывания информации с оперативного запоминающего устройства 10.

Таким образом, благодаря уменьще- нию скорости передаваемого сообщения при формировании фазоимпульсного сигнала можно осуществить повышения помехоустойчивости и достоверности передаваемого сообщения путем уменьще- ния влияния селективных замираний сигнала, связанных с флуктуацией отдельных частотных составляющих спектра, и путем уменьшения реверберационных помех.

5 0 5

о

0 5

5

0

5

Кроме того, уменьшение скорости передачи сообщения при телефошго- телеграфной связи приводит к увеличению дальности связи.

Предлагаемое устройство обеспечивает более высокую линейность модуляции, что улучшает достоверность передаваемых сообщений.

Формула изобретения

Устройство фазоимпульсной модуляции, содержащее соед шенные последовательно генератор опорной частоття, первый элемент совпадений и счетчик импульсов, второй вход которого соединен с первым входом первого коммутатора, второй вход которого соединен с выходом порогового блока, а первый выход - с вторым входом первого элемента совпадений, первый конденсатор, первый вывод которого соединен с первьЕм выводом стабилизатора разрядного тока, второй вывод которого соединен с общей шиной, дешифратор и первый ключ, отличаю- щ е е с я тем, что, с целью повышения достоверности передаваемой информации, в него дополнительно введены второй и третий элементы совпадений, второй коммутатор, второй конденсатор, второй ключ, счетчики адреса и данных, элемент (ИЛИ, оперативное запоминающее устройство, цифроаналоговый преобразователь и амплитудно-импульсньш преобразователь, выход которого соединен с входом порогового блока и первыми выводами обоих конденсаторов, первый вход - с входной шиной, а второй вход - с вторым выходом первого коммутатора, выходной шиной инверсного сигнала и первыми входами второго и третьего элементов совпадений, второй вход третьего из которых соединен с выходом генератора опорной частоты, а его выход - с первым входом счетчика данных, второй вход которого соединен с выходной шиной прямого сигнала, первым выходом первого коммутатора и входом Выбор кристалла оперативного запоминающего устройства, третий вход - с вьгходом счетчика импульсов и его вторым входом, а информационные выходы - с информационными входами оперативного запоминающего устройства, адресные входы которого соединены с первыми выходами счетчика адреса, вторые выходы которого соединены с входами дешифратора, вы9

ход которого соединен с первыми входами элемента ИЛИ и второго коммутатора, вторые входы которых соединены с шиной Пуск, выход элемента ИЛИ - с первым входом счетчика адреса, первый выход второго коммутатора - с управляющим входом второго к.пюча, а его второй выход - с управляющим входом первого ключа и вторым входом второго элемента совпадений, выход которого соединен с входом разрешения записи оперативного запоминающего

С

ПП О П П ПО

1}

41195810

устройства, вход Выбор кристалла которого соединен с вторым входом счетчика адреса, а информационные выходы - с входами цифроаналогового преобразователя, выход которого соединен с управляющим входом стабилизатора разрядного тока, второй вывод которого соединен с первыми выводами 10 обоих ключей, вторые выводы которых соединены соответственно с вторыми выводами первого и второго конденсаторов.

i

Режим залиси

попоп

Фиг.г

иг.2

| УСТРОЙСТВО ДЛЯ ФАЗО-ИМПУЛЬСНОЙ МОДУЛЯЦИИ | 0 |

|

SU231625A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство фазово-импульсной модуляции | 1983 |

|

SU1215170A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-07-23—Публикация

1985-12-24—Подача