i-11;-;

т

j

1 о li.

1 r j e с

(

r-o, 1 ч T 1-,,.

H,-- .ue .

a-i-i , г j

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с абонентами | 1987 |

|

SU1441409A1 |

| Устройство для сопряжения электронных вычислительных машин с каналами связи | 1988 |

|

SU1569838A1 |

| Устройство для ввода информации | 1986 |

|

SU1372317A1 |

| Программируемый таймер | 1987 |

|

SU1441407A1 |

| Устройство для управления ведомым локомотивом с ведущего | 1986 |

|

SU1406622A1 |

| Устройство для формирования ошибок в цифровом сигнале | 1986 |

|

SU1441406A1 |

| Устройство для контроля микропроцессорной системы | 1985 |

|

SU1392562A1 |

| Устройство для слежения по стыку | 1989 |

|

SU1696202A1 |

| Устройство для ввода информации | 1986 |

|

SU1397924A1 |

| Регулируемый преобразователь переменного напряжения в переменное | 1987 |

|

SU1494172A1 |

Изобретение отиосиго; к вь числ:-г- тельной , может быть использовано для объединення процессоров в высоконадежных агп-оматизироваипых

cHcreN ax управления и является усо- першенствованнем устройстиа по авт. ев, № 130403 i.

Цель;с изобретения Яг :1яется уменьшение времени восстановления работо- способное тн и с1-шженг о влияния слу- ;;-пных помех на магистралях системь; за с -ч г pii jpemeHHH работы ксч.т рсля TojibKo при наличии на у .форма- циоаных шинах маг)стралк ус 1 ройстна не менее двух наборов ичформанионньп-; c ;r:::4jiOji.

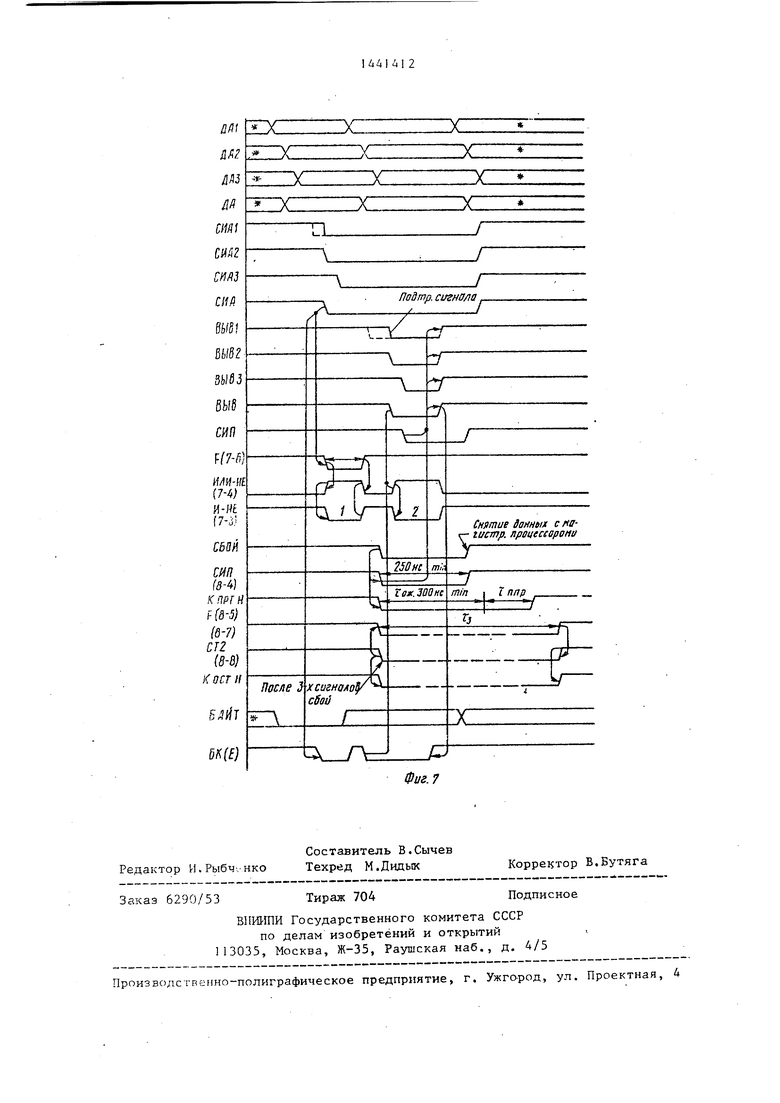

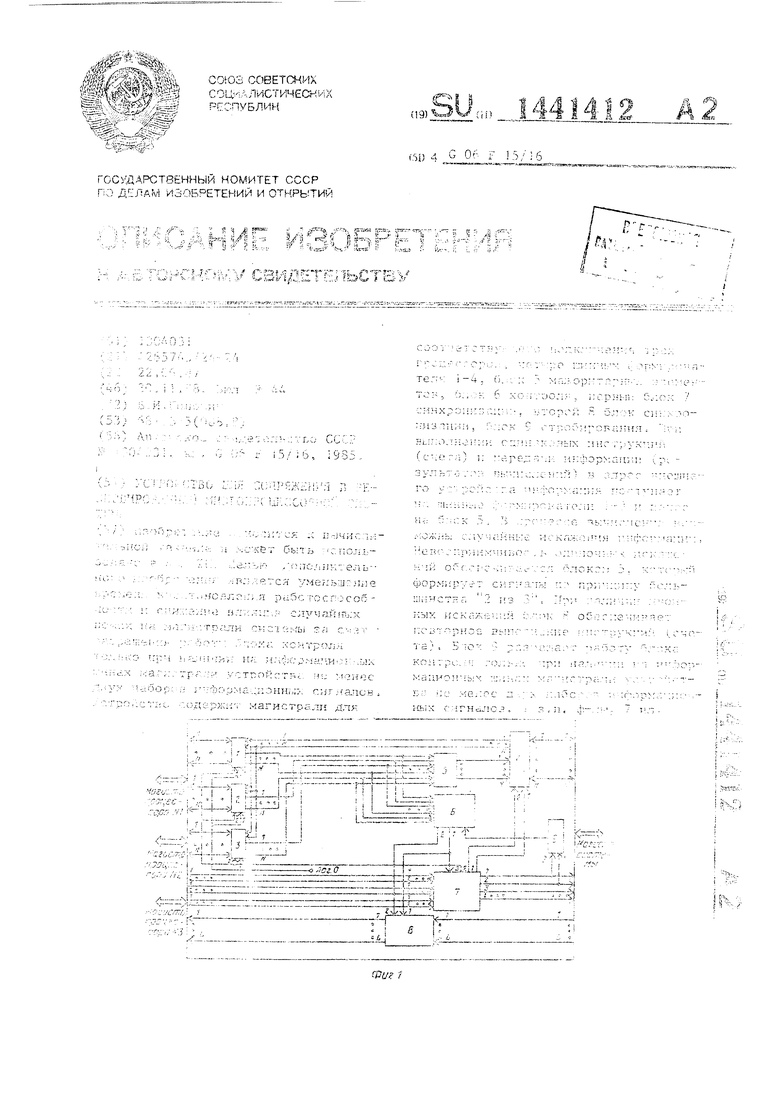

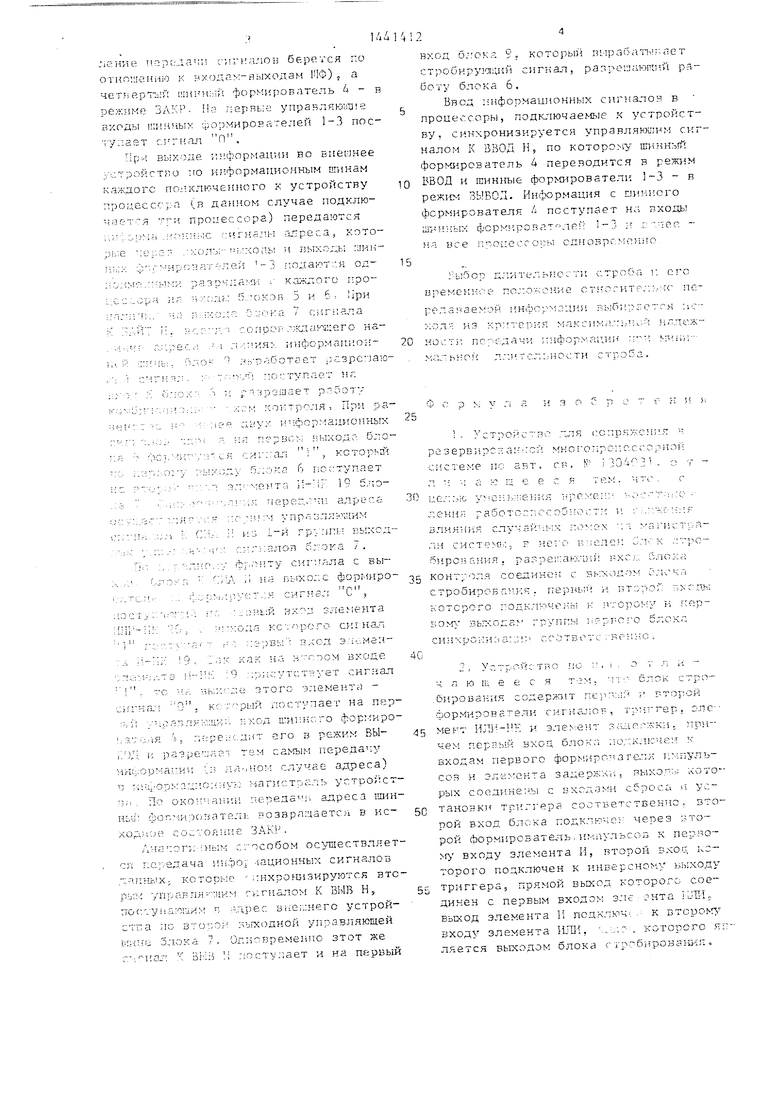

с.-:с -:а тт -едлагаемог-о устройства; - а дкг. функцнональнал схе::а блока хои:, (БК) ; на фиг. 1 и 4 - фу)к- 1.;;.оиальнъ:е схем, г:ервс ч i второго З юков синхпонизании (БС- и ВС2); на фнг,5 - функнионал. --.ная схема блока строСирования (БСТ); на фиг .б - вре- Ь;ен;;ал диаграмма работм БСТ; на . / jipeMSHHaH диаграмг ка работы устронст-- ва,

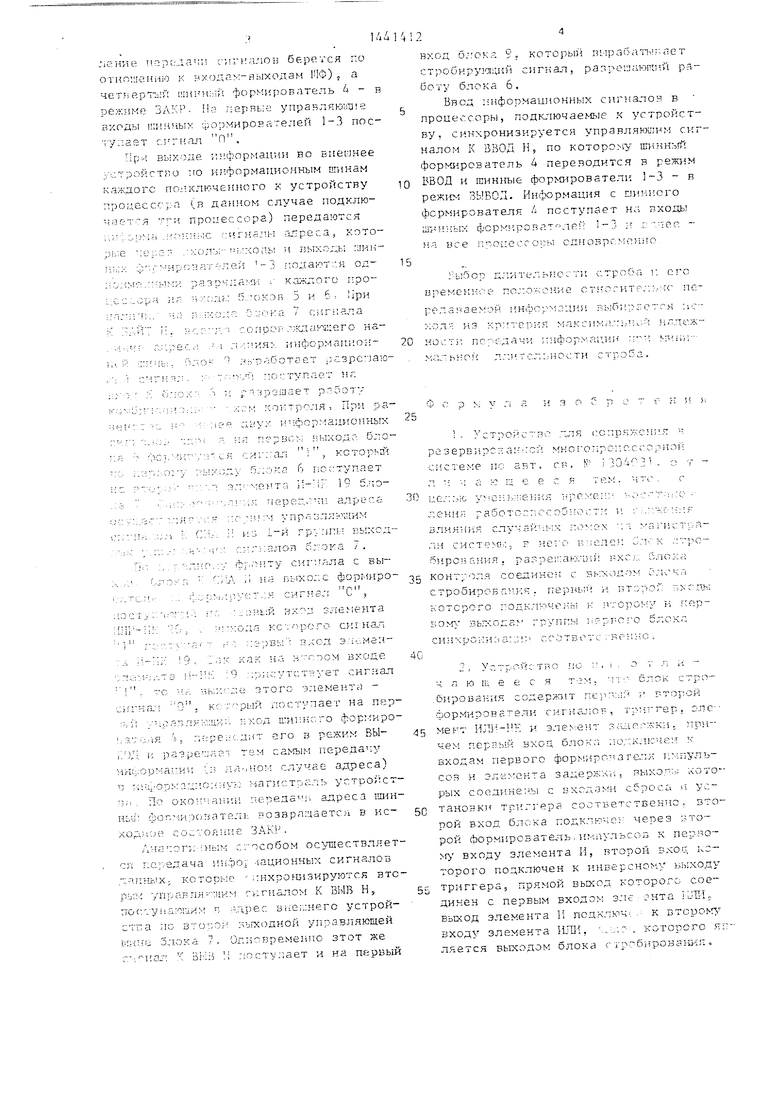

Устройс но (фиг,1) соаер;№Т че- Li;-f5:Hfcix фср ммро В ат сля ; - 4, блок 5 мгжоритар1Гь х эле.ментов; .ьК 6; г-реп ;лзначенпый для сравнения от трех процессоров информанир к вырабатываго- i:rn; уг рЛБг-1ЯНП1 1е сигналы, нервьш блс 7 сипхрон)-зании, г;редназ} ачен- 1ПЛЙ для фор;чнрования сигналов упра;:;- ., еипя Бводол; и ВгБ :;цом кнформац1Н, ;гторой б. /ок 8 сннх)онизации, Г редна: - наченкг 4 ,{ля форь1ирсва и-гя iecтныx

cnrsiajfOB ун 5авле:Л1я; Г оггупаюших к трем процессорам и осу ;;ес гвляю1ц:их HOBTOpe;;i-.e UHKJJOB вьшол/- -5нформании, при наличии сбоев -.-ри передаче информации, блок 9 стробнрования5 пред назначенмы для разрешения работьг БК 6 тол1-.; ;о при наличии Данных адреса или информадии te менее чем от двух пронессоров и формирования временной длительности и пололчег ия стро ба.

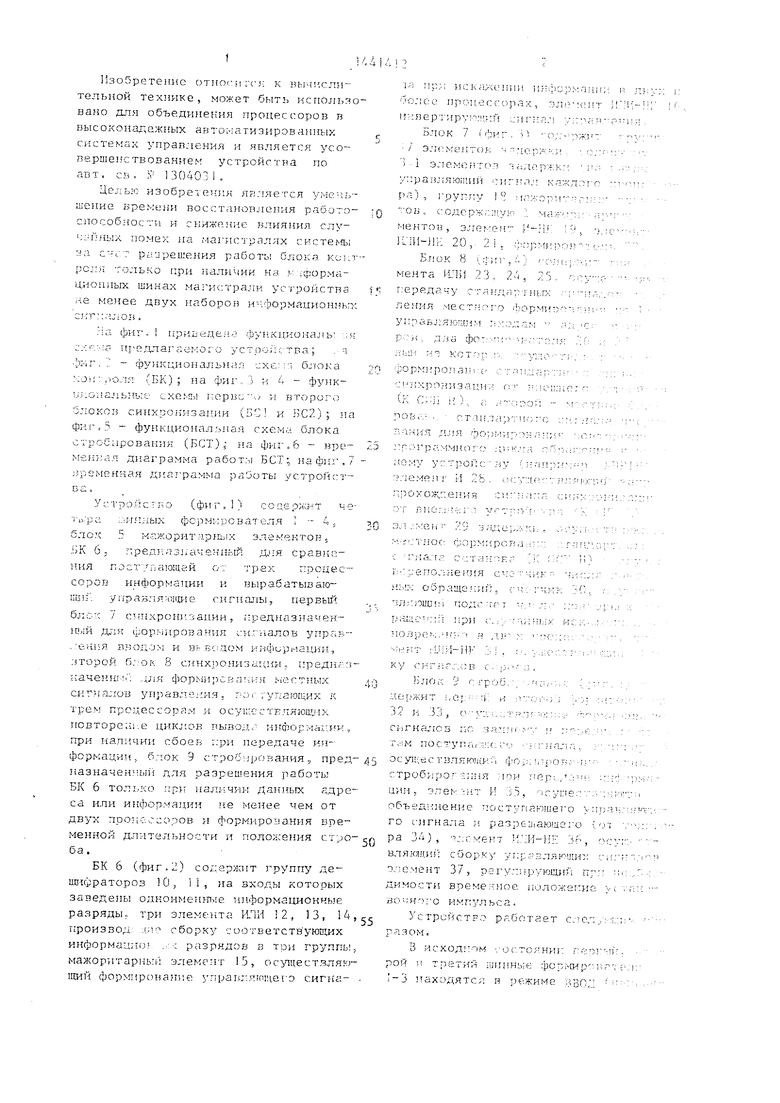

БК 6 (фиг.2) содержит группу дешифраторов 10; il, на входы которых заведены одноименго Ее ин-формациониые разряды,, три элемента ИЛИ 12, 13, гфоизвод . н- сборку соответств ующих информацпог .:ч разрядов в тр;; группы мажоритарный элемент 15, осущестзляю 1ЦИН упра1 :;я;о1цего сигна-

ifi прл ис ( HHiiiOLJMai

более прс нассорах, зл : :с1

и;:вертиру:- : ;ий сигна. v:::v

Блок 1 ; fbs-T , i -(

/ ЭЛ(;CHTOf;

i 1 3;ieMenTc:i; а;тар-т:к:; ; у::раиля)оп1ий кажлат ра) , группу I :(ажормт; г; ОБ, содсрж;:. 1 чау, ментов, злег- ен -МГ л iLiH-flK 20,. 2 U ;;:;;рмипон-: Блок 8 :гп;г ,;0 . OHi-v,o мента li Iil 23, 24, 25- ;с г:ередачу стан/ ар ; ньс-; ,;-;

ЛеНИЯ МеСТ ;РГО iijOpMHlV- ;-

унраБЛЯ О-цнм г::-:;}дам ал ч реи, даа фо:;:. -.; --;--/:т;;ля 2

ФOp : rptзnaIhч- г т-ii.r;a;v:-;i С пхрпи1-5заии;-; с; т . г- (.; I: ) . ;; ;; (.;оо; - ; pOBi-.- , T{lH;} U) L::-;;

- г р;

мно;

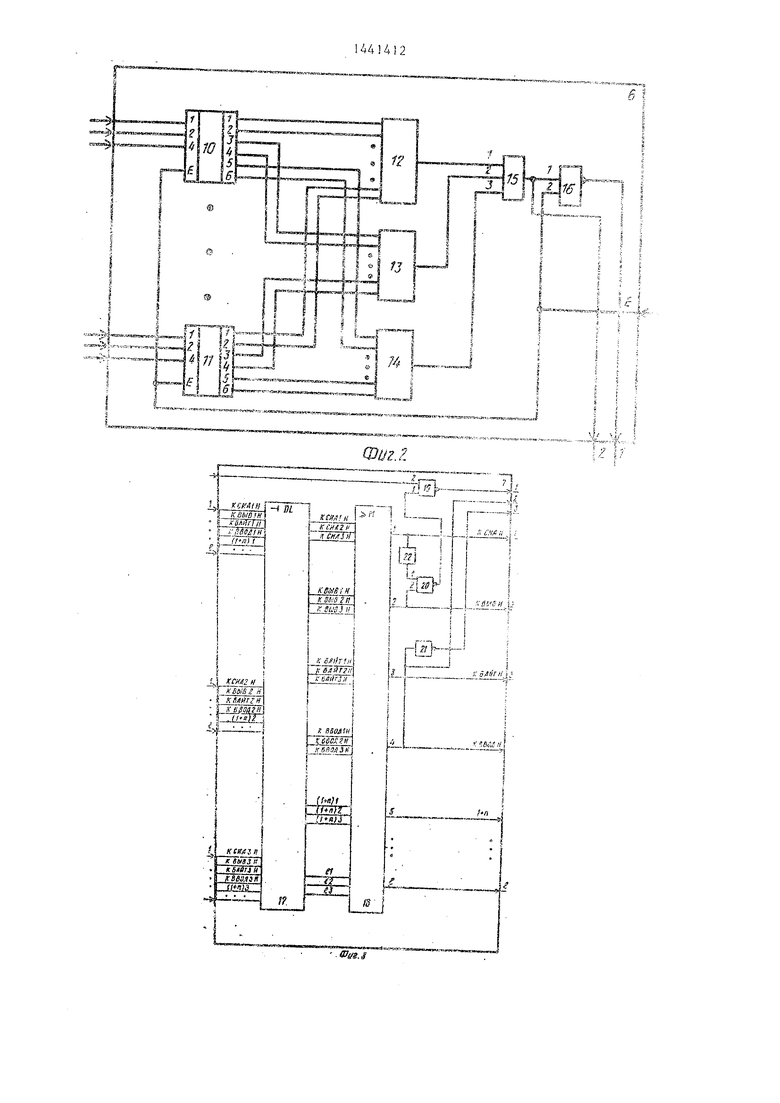

эл-С- ен .-.:; з;;,цер,к ;ь , ссу; : ;: : ) : ;-г-; .:Т;ЮС- фОр ИрСВа:;::. : .: га;;;-;: г ; . ,. ; :

с Г;:а.а сстг Нг:ЕГ К м) -;

Г),: :,;еполне1Ч1Я с :С ;ик чл;;лг / - ньк обраще ни;; 5 сч2 гчкк 2(, : .v Ui;:nuu ;i нодс :m -, л- ;;-;; .- ::

НОЛрс -;,к;,- /j /U : с;;::. . -, ; -ент 2 : . . V.IA ;-. ;-;- :;;:.:.- ку сигнг.:-..ов с, р,- .;:: .

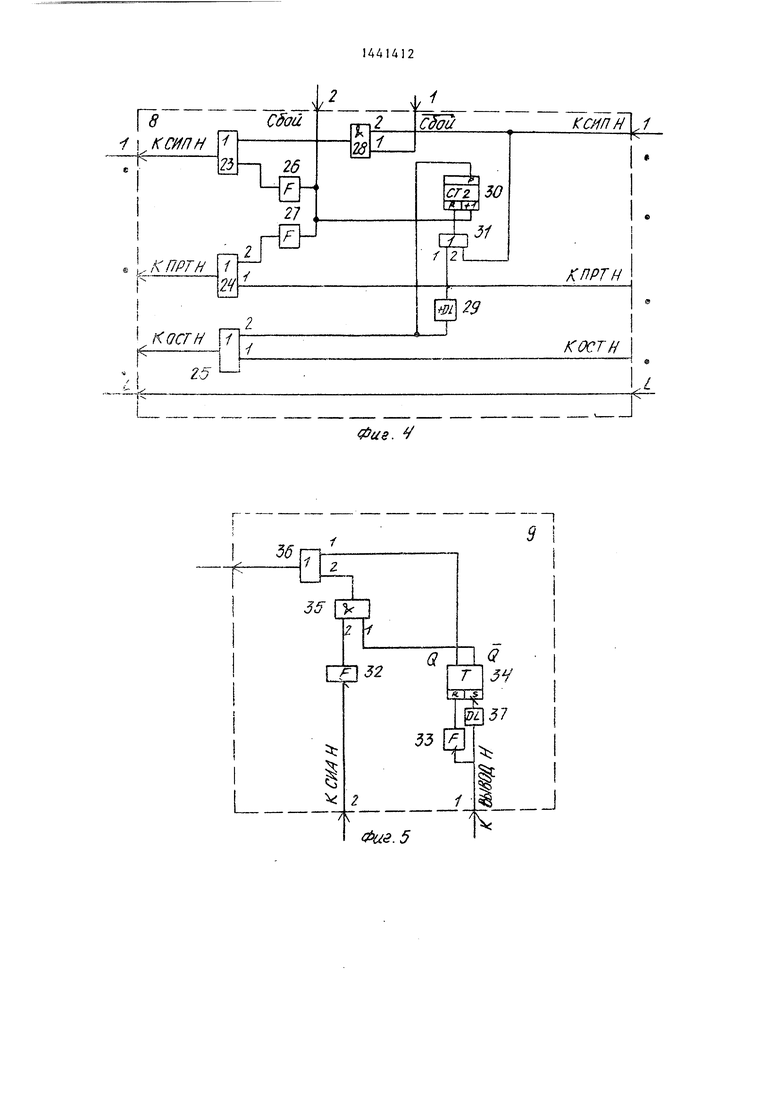

Ьло;:; 9 г; гроб. ,...;: ; :: ,:, ,е;;- i и ; ;,л .. 32 к 33, с- уи,,,,т -Л: :;;:;::;- -:--- -.,: , CijrHajiCB ПС за. ; м ..с;- . : TriM nociT ynai/iiKM- j гггала, ; :;:;

OCyi ieC т (И; (I OpMj-i OR; -П - ;,

cTpo6iJpO -лцш /юн .д, ;::;

ЦИИ , ЭЛеМ -НТ И 33, супес V:-,-; .:FI -:-:I

объединение лоступаюшет о пт апл;; - го сигнала и разреа1аю дсго (, л; /;: ра 34), -::смен7 i. 3, осуг - Бля;ад1 й сборку упразляющит; , . 37, регул;|рующ}тй -ic.,. димости временное ноложекис v(v;;H импульса,

Устрсйстро работает сле;: : г::; разом,

3 исходном . ОСТОЯНИ : Г:е 1Г -: Й.

рой V- третий iiiHHHb;e фор;-шр па ; находятся в режиме 3302:

jiGiiiie с-; г ;алов берется по OTHouiCHiiio к чкодам-йыходам П1Ф) , а , iiiHini::;; ; tjOpNinpoBaTe. ib 4 - в режиме ЗЛКР- На первь;е управляЮ1Ш е входы iiiiniUbix орормировате. ШЙ 1-3 пос тулает cnrnan П .

При вь Ходе имформаш-ш во внешнее ;/сг:зойстло ;ю н;;формационным шинам каждого по.1 ключеииого х устройству npouecccj:a (в данном случае подклю- процессора) передаются : ;,р;;а ,.;с ;алреса, кото- ;);-е :ера:- . холъ;- -г..,Ь и 1)Ыходь; 1-ь;х ф :г -.;иро7 ат-; Лей -3 полаютск од- :-олмг , :;;. оазрядаг-д; ; каждого гтро- ;.,сс:.ора ил м; -;;:.: б..4)коп 5 i-i 6 , При : П: ;: п ча г :;ходо 0 ; } ;а / сигнала : . .T ii. , 1 сопрор ;кдai iuero на- . i-: :; n.i peca .-1 fi ч- иях ; Нформан1;он ill. и ::ичь;- .O ; :з рлСотает :;азрс аю

;ipei:JaeT :м ко1:тро; Я , При ра- - 1;фор:-1ационных 1 псрвс:-: ныхода бло- :игхал ;, который блока 5 г оступает ме} та И-МГ 19 блэ- мере-а-п1 адреса Ч ;: - упразля; 1;ии ; 13 i,-и грулпр ; выход- -rxajTon блоз а 7 , .опту сигипла с 8Ы-

СИГНеЛ

м ::. йхт д элемента . ко ; -фого сигнал г- : ;: овы : пход ;. как на входе : лрисутст -;/ет сигнал У)Ь;;: ле этого элементе) - . КС v-i-pbiA г;остулает на пер- 1к;о:ц;-;с ;ход 1Ги1;}-сго формиро- г;;;ре;-с, его в режим ВЫ- ем caNfciM передачу но;- случае адреса) IT ;;1и Орь:ад: о;(иуг.; г агистраль устройст- n;i По окончании переда Л адреса иин- ньи: фоп -1ировате:п; возвра:цаетс 1 в ис- ходяой состояние ЗАКР.

Лиачогн HfciM способом осуществляет- су; г.ередача инфо -шционных сигналов д-П Нь Х; KOTophip чнхронизируютгя вто- рьк-: упракля -: 1и с;:гналом К ВЫВ Н,

TTOc-vyiiaiOuHX ч -.дрес вне;.:него устрой- с гга ло 3TO-:oj- зъгходной управляющей Уигш блока 7. Одновременно этот же с.-, 110 : Bb:i) ; лостулает и на первый

вход блока 9. который вырабат 1 г.ает строоирую Га-1Й сигнал, раз-ре паюипгЛ работу блока 6.

Ввод пнформашюннь Х сигналов в процессоры, подключаемые к устройству, синхронизируется унравляюшиг- cv:r- налом К ВВОД }{, по которо;--гу- Ш11нный формирователь 4 переводится в реж5- М ВВОД и шинные формирователи 1-3 - в режи ВЫВОД. Информация с пиглюго формирователя Л поступает на входь; miH ifcix формирователей 1-3 и .:.чеа - fia все rinoLieccocbi одноБрс-- С};;Го

;Ч;:5ор дл 1Тельности строба к его Бременное по::оконие отнопп рл лчо нс- релаяае :ой инфоу --1ации БЬ;бир;:с:тя ;ic-- :од из критерия шкс1 ма;:ь К;й надеж- ности передачи ;;нфор -аии -; :; ; n iiir- д::итсл:л1Ости строба.

Э ; V

резервирс;:ан/:ой нoгor;po;acc:opi oй cHCTeNie но авт. св. К i30i 3 . о т - л ч ч а :0 ц е е с я те;-:. , с uejx.,ic уме:;ь:мения ;-рс ;е;;ч -ос- / ачо ления работослос обчости и г:.ч-:{ чля- злияния случайных чо -:ех ча агистра- л:-1 систе Р,:, г него нчедеч :ч:-; о- бирот5а11ия. ра ое1;:а -лчий xci, бло;;а контроля соединен с 5ь: ;одом б;1оча стробироБ . г;ервый и БТЭРОЙ пхг пь; которого чодключены i-: }ггоро;- у и г;ер- вьп-;ода группы блока

3, Устрой:;-Tiio г:о ч, - о г л и - чающееся той чт . блок стро- .бирования содерЖ)Т пср:ч; ч ; второй формирователи сигналов, триггер, с-лемент ИЛИ-1 Е и 3aj:iPrKK;i. причем первый вход блока ::одкл1сче; - входа первого фор ;5ро-1аге.чк и:-;11уль- сов и зле - ента задержки, пыхог ь: кото соедине;.ы с вxoдa И сброса ч установки три.ггера соответственно,: второй вход, блока подклю-;еч через второй формирователь . и.мгГ. льсс В х первому входу элемента Н, второй вход ко- Topoi o подключен к инверсному ьыходу триггера, прямой выход которого соединен с первым входом э.чс ента ;1Л11„ выкод элемента 11 подключи . к второьгл входу элемента ИЛ11, ,.-„.: . которого я ляется выходом блока гтробдфова шя,

.iPyg.S

.

Авторы

Даты

1988-11-30—Публикация

1987-06-22—Подача