о: со со го

4

Изобретение относится к автоматизированным информагхионно-измеритель- ным системам, преляязначенным для с борл и обработки многоканальной ин- формации, а именно к устройствам, обеспечивающим ввол многоканальной иг мерительной информации в ЭВМ.

Цель Изобретения - повыгаение надежности устройства.

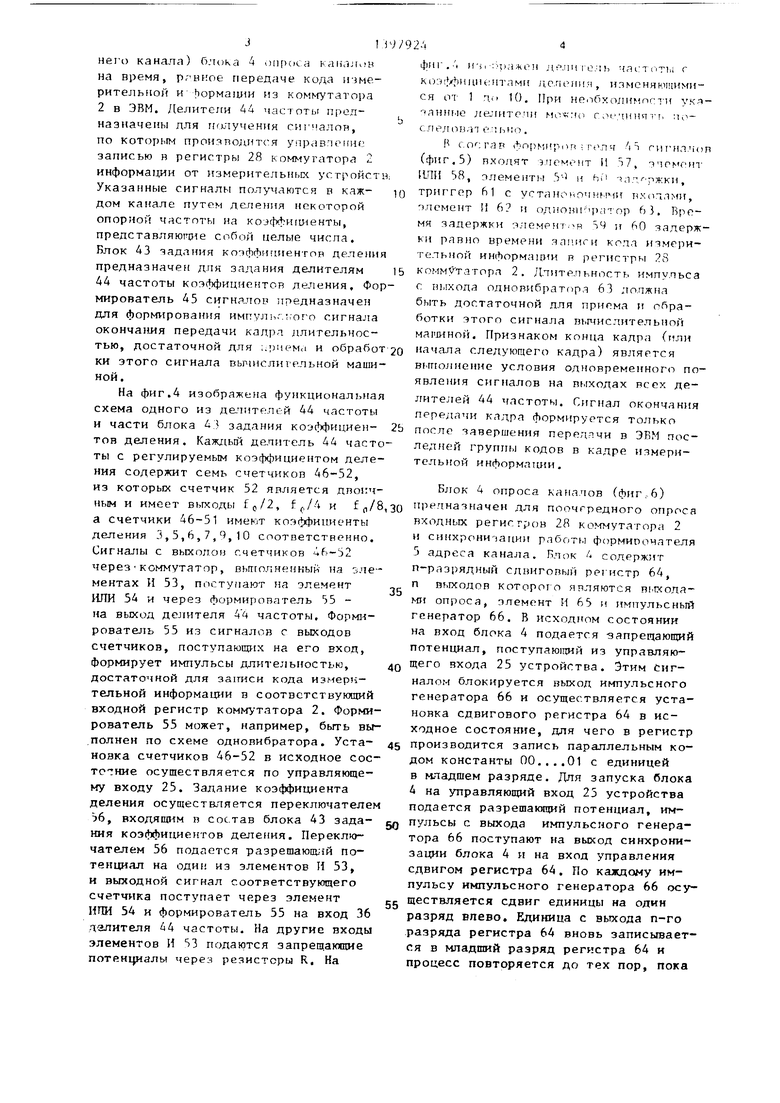

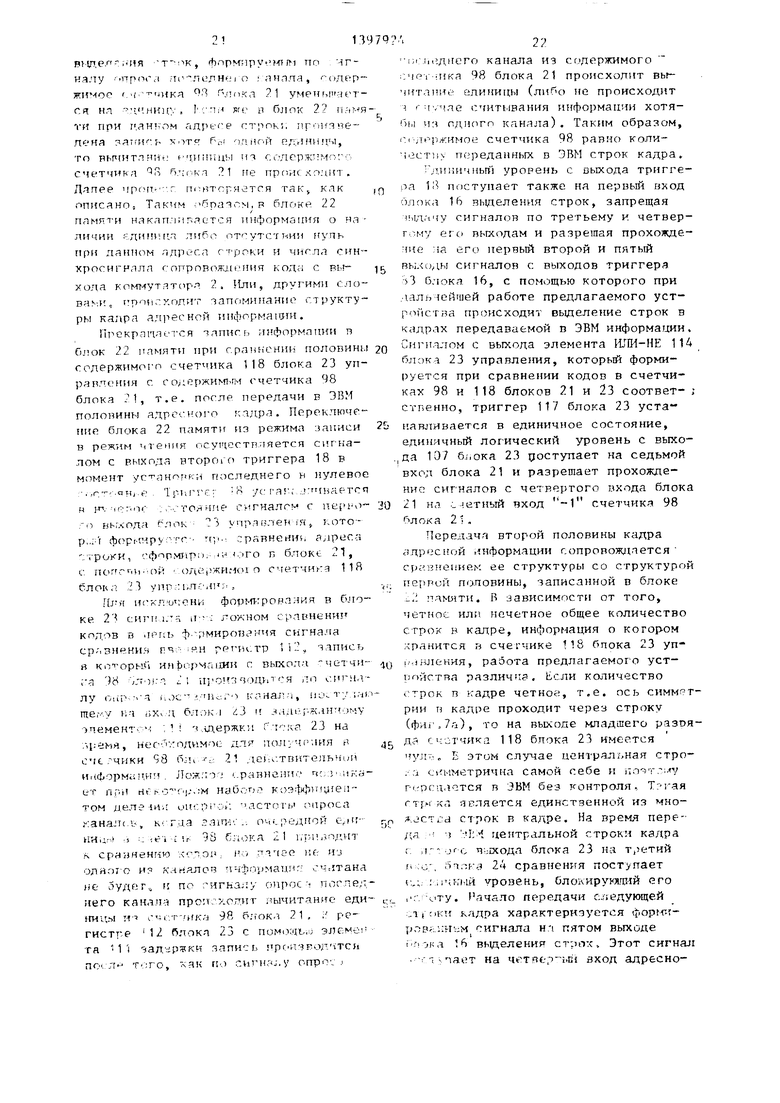

На фиг.1 представлена структурная схема устройства; на фиг.2 - структурная схема коммутатора; на фиг.З - структурная схема блока выбора каналов; на фиг.4 - схема делителя частоты; на фиг.З - схема формирователя сигналов} на фиг.6 - структурные схемы блока опроса каналов и формирователя адреса канала; на фиг.7 - временные дилг раммы работы четьфехканаль- кого устройства; на фиг.8 - схема формирователя кодов; на фиг.9 - схема формирователя границы кадра; на фиг.10 - схема блока вьщеления строку на фиг.11 - схема блока формирования адреса; на фиг.12 - схема блока уп- раапення; на фиг.13 - схема блока сравнения.

Устройсгяо для ввода информации Сфлг.О Содержит г информационных

1 по числу каналов, коммутатор / блок ii;6opa Kai d- .oB, блок 4 рпро ; ,л камалчч, форммро .атель 5 адреса каналов, ;1е11(ифратор 6, первый ключ 7, группу ключей 8, вторую группу Kjii-гчей 9, второй ключ 10, элемент И П, элемент 1ШИ 12, элемент ИСКЛЮЧАЮЩЕЕ ШБ 13, формирователь 14 кодов, формкропчтель 15 границы кадра, блок 6 вьщелення строк, первый и ьтог/он триггеры 17 и 18 первый и второй элем ты 19 и задержки, бпок 21 фрр. -пфозания адреса, блок 22 памяти, 23 ynpas- eHTfR, блок 24 срариени, управляющий вход 25, уп- равляющий пькод 26 и информационный выход 27.

п ииформа:г1:онных входов 1 устройства предназначены для приема цифро- B1JX кодов, поступаювдтх от измерительнык устройсгв или датчиков. Эти входы Подклю чены к информационным входам ком гутатора 2. Последний предназначен ,tyi,4 промежуточной записи отсчетов измерительной информации и выдачи этих отсчетов с синхроимпульсами сопровож- денил.

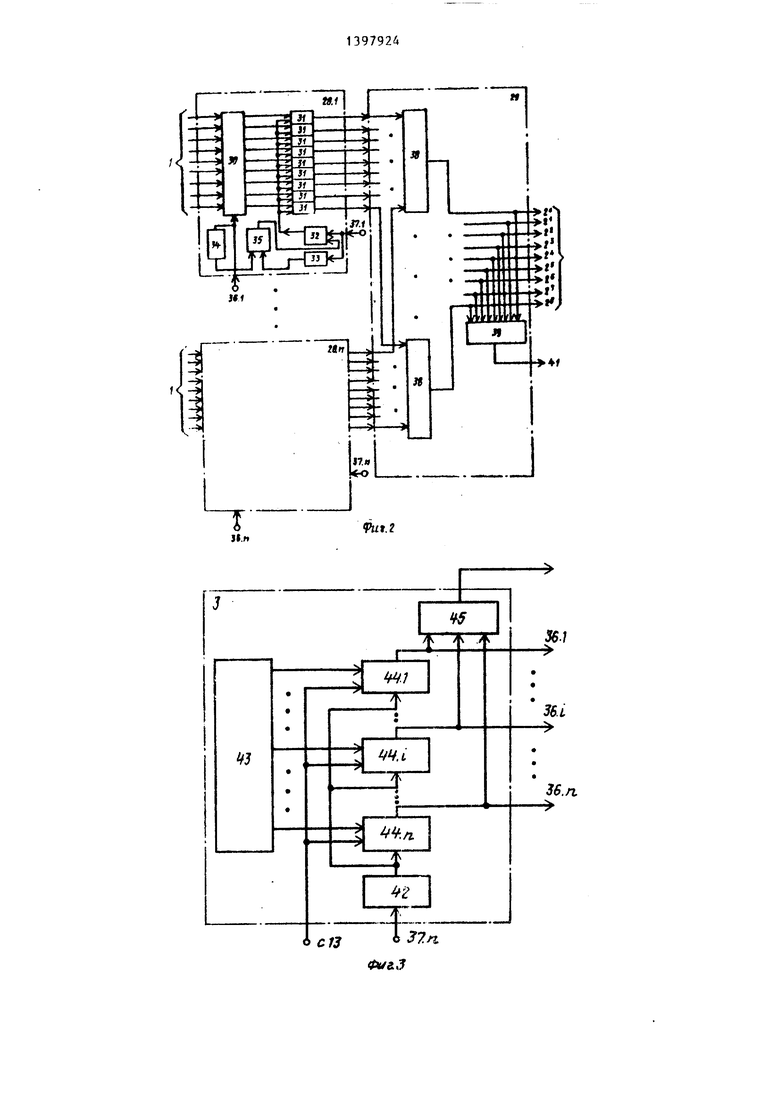

Коммутатор 2 (фиг.2) содержит регистры 28,1-28.п и блок 9 сопряжения. Регистр 28 содержит двоичный регистр 30, группу эпементов И 31, элемент И 32, два элеме}1та 33 и 34 задержки и триггер 35 с установочными входами. Запись кода в регистр 30 осуществляется при поступлении импульсного сигнала на вход 36 управления записью. Указанный сигнал, задержанный элементом 34 задержки на время, достаточное для занесения кода в регистр 30, переводит триггер 35 в единичное состояние, в результате чего на элемент И 32 с вькода триггера 35 подается разрешающий потенциал. Считьшание кода иэ регистра 30 осуществляется при поступлении сигнала опроса на вход i7 управления считыванием. По этому сигналу код с выходов регистра 30 через элемент 31 И поступает на выход входного регистра 28. Сигналом опроса, задержанным элементом 33 на .время, достаточное для приема кода вычислительной машиной триггер 35 устанавливается в нулевое состояние, нал элементом И 32 выдается запрещающий потенциал, которым блокируется поступление сигнала опроса на элементы И 31, и вьщача кода завершается. Блок 29 сопряжения соцержит элемен 1ы ИЛИ 38, каждый из которых имеет п входов, и O;UIH 9-нходсвой элемент 1ШИ 39, на тзькоде форм1 Груется :инхрсимп: Льс сопповождг;- ния, вццаваемый с у нформаиио; .-ого выхода 41. Так как значзние контрольного разряда кода формируется тлким, чтобы сумма по модулю 2 ссех р.азрядов была равна единице, код с конгр 1ль- ным разрядом имеет свойство сам . сип- хронизации, и cинкpocиг aл сопровождения кода можно получить как дизъюнк цию значений разрядов кодг. Пипримси, нулевой код имеет вид iOGOOOnO , r.iu старший разряд является капр.г },,.-, Тогда синхросигнал со гровожденпя 1+0- -0+0- -0+0+0+0+0 1.

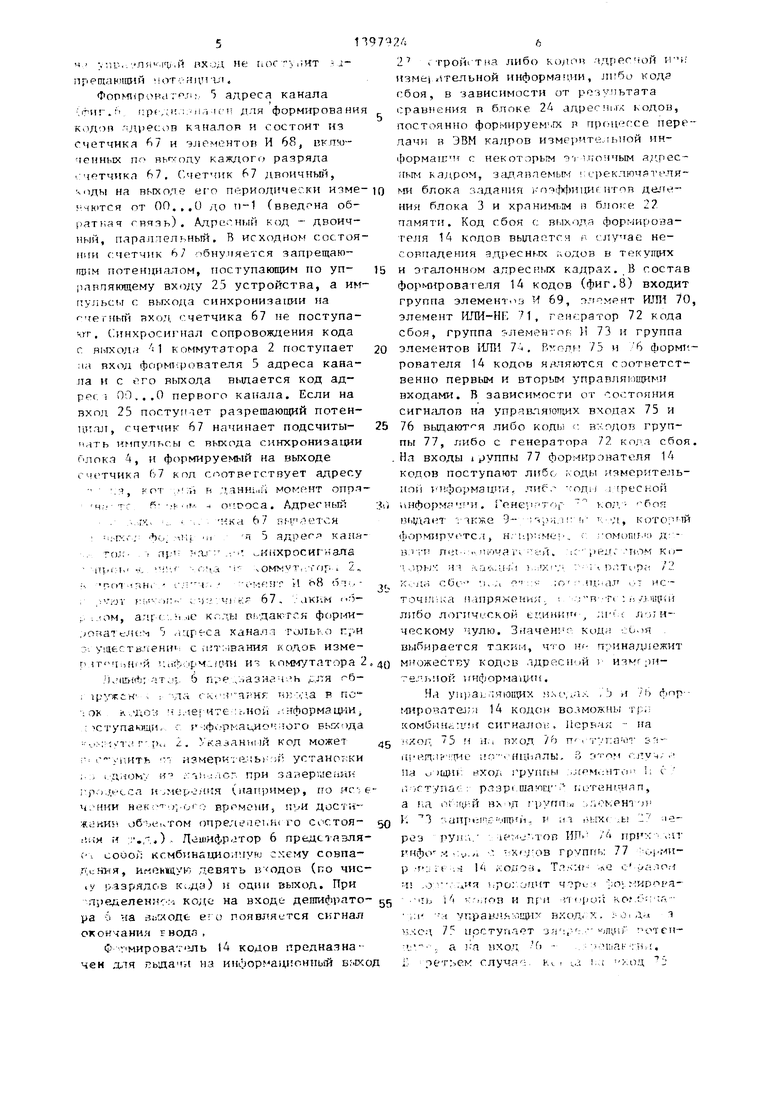

Блок 3 выбора канапов (фиг.З) пре,т0 азпачен для формирования гиг налов 36 упрявления записью измерит ль- ной ннфп. во входные регист{ь, 28 KOi.iV/TaTopa 2. В состак б.гтп|.а 3 вхо;. элемент 42 зад-ржки, блок 4j задания козффицие;ттпз дел.::-&г5, дели- т; Ш 44 частоты и формирователь сигналов. Элемент 4 задержки п е,-; для задержки лгнала, посту- гающего ня вход 37„. п ,с-ка 3 с п-го ,да опроса (вьгх хч спроса посл 1негч) канала) блока 4 опроса KanriJri B на время, р нное передаче кода измерительной и Ьормации из KOMNfyraTopa 2 в ЭВМ. Делитетги 44 частоты предназначены для получения сигналов, по которым произподится упрсшпеинг. записью н регистры 28 коммугатора 2 информации от измерительных, устройстн Указанные сигналы получаются в каж- дом канале путем деления некоторой опорной частоты на коэффициенты, представляюрсие собой целые числа. Блок ДЗ задания коэффициентов деления предназначен для задания делителям 44 частоты козффицие11тов деления. Формирователь 45 сигнялор лредназначен для формирования импуль..;;ого сигнала окончания передачи кадра длительносфлг,- | и ч I :: 1)ажо н д f.iiH I c. i i чл1.:тг 1ты г коэ(;х)ици«::нтпми дс.г|ения , илменяюпшми- ся от 1 п,(1 10, При необхолиности укя- танные делители гос/шнятг, :ui- следон.-л 1 :;ько.

Р со ;гаЕ формироп ; 4 S гиг нл.чоп (фиг. 5) входят jJiCMtMiT 11 57, ЯПИ 58, элементы 3-1 и ЬП , ржки, триггер fi 1 с устанонпчничи пхолями, элемент И 6 и одиони 1р;гт ор 63. Время задержки э;1емритов 59 ц 60 задержки равно времени яап.игн кола измерительной информации в регистры 33 коммутатора 2. Длительность импульса с выхода одновибраторя 63 должна быть достаточной для приема ) обработки этого сигнала вычислительной мапхиной. Признаком конца кадра (пли

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для ввода информации | 1984 |

|

SU1265783A1 |

| Устройство для сопряжения группы каналов ЭВМ с группой периферийных устройств | 1987 |

|

SU1520529A1 |

| Устройство для отображения информации | 1987 |

|

SU1474634A1 |

| Устройство для ввода информации от двухпозиционных датчиков | 1985 |

|

SU1304011A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Система для обмена информацией | 1980 |

|

SU980087A1 |

| Устройство для вывода графической информации | 1990 |

|

SU1783572A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1988 |

|

SU1575231A1 |

| Устройство для отображения графической информации | 1990 |

|

SU1772822A1 |

Изобретение относится к .ч- тизиронаиным и iфopмлциoннo-н: иepи- тельным системам, предназначенным pjin сбора и обработки многоканальной информации. Целью изобретения является повышение надежности устройства. Устройство для ввода информации содержит коммутатор 2, блок 3 выбора каналов. блок 4 опроса каналов, ключи 7 и 10, группы ключей 8 и 9, формирователь 5 адреса каналов, дешифратор 6, формирователь 14 кодов, формирователь 15 грании;ы кадра, блок 16 вьщелеиия строк, триггеры 17 и 18, блок 21 формирования адреса, блок 22 памяти, блок 23 управления, блок 24 сравнения. Контроль правильности сЛормирсл ания адресног о и информационного кадров основан на свойстве их симметрии, т,к, позволяет контролировать не только число каналов в кадре, но и последовательность„ СРой- ные ситуации при передаче кадра диагностируются, места сбоев в вводимом массиве помечаются кодами сбоев, а части кадров после обнаружения в них сбоев в ЭВМ не вводятся, 2 з.п. ф-лы, 13 ип. (О

тью, достаточной для ;.1)иема и обработ 20 начала следующего кадра) является

ки этого сигнала вычислиг ельной машиной.

На фиг.4 изображена функциональная схема одного из делителей 44 частоты и части блока 43 задания коэффициен- тов деления. Каждый делитель 44 частоты с регулируемым коэффициентом деления содержит семь счетчиков 46-52, из которых счетчик 52 является двоичным и имеет выходы , f,/4 и f(i/ а счетчики 46-51 имеют коэффициенты деления 3,5,6,7,4,10 соответственно. Сигналы с выходов счетчиков черезкоммутатор, выполненный на элементах И 53, поступают на элемент ИЛИ 54 и через формирователь 55 - на выход делителя 44 частоты. Формирователь 55 из сигналов с выходов счетчиков, поступающих на его вход, формирует импудьсь длительностью, достаточной для за1П{си кода измерительной информации в соответствующий входной регистр коммутатора 2. Формирователь 55 может, например, быть выполнен по схеме одновибратора. Установка счетчиков 46-52 в исходное состояние осушествляется по управляющему входу 25. Задание коэффициента деления ocyщecтвJ яeтcя переключателем b6f входящим п состав блока 43 задания коэффициентов деления. Переключателем 56 подается разрешающей потенциал на ОДИ1 из элементов И 53, и выходной сигнал соответствующего счетчика поступает через элемент ИПИ 54 и формирователь 55 на вход 36 Д злнтеля 44 частоты. На другие входы элементов И 53 подаются запрещаюсцие потенциалы через резисторы R, На

5

5 0

0

5

5

в1-гполнение условия одновременного появления сигналов на выходах всех делителей 44 частоты. Сигнал окончания передачи кадра формируется только после завершения передпчи в ЭВМ последней группы кодов в кадре измерительной информатщи.

Блок 4 опроса кар(алов (фиг,6) предназначен для поочередного опроса входных регистров 28 KoNfMyTaTopa 2 и синхронизации работы формипочателя 5 адреса канала. Блок - содерж;гг п-разрядный сдвиговый регистр 64, п выходов которого ярляются В1даода- я опроса, элемент И 65 и импульсный генератор 66. В исходном состоянии на вход блока 4 подается запрещающий потенциал, поступающий из управляющего входа 25 устройства. Этим Сигналом блокируется выход импульсного генератора 66 и осуществляется установка сдвигового регистра 64 в исходное состояние, для чего в регистр производится запись параллельным кодом константы 00....01 с единицей в младшем разряде. Для запуска блока 4 на управляющий вход 25 устройства подается разрешающий потенциал, импульсы с выхода импульсного генератора 66 поступают на выход синхронизации блока 4 и на вход управления сдвигом регистра 64. По каждому импульсу импульсного генератора 66 осуществляется сдвиг единицы на один разряд влево. Единица с выхода п-го разряда регистра 64 вновь эаписьгоает- ся в младший разряд регистра 64 и процесс повторяется до тех пор, пока

rioc

;ит

П97 Д2Д6

Фop nipoнclrf.n;/ 5 адреса канала (гчг.: i:p( ,;,H,),-iiл к п для формирования кодов v U eeoB кчналов и состоит из счетчика 1 и элементов И 68, включенных по ВЫ-ГОДУ каждого разряда :четчика , С четчик 67 двоичньв1, ч оды на выходе егч

f 4H)TCH от 00...О до Т1-1 (введона об- () гвязь). Адресный - двоичный, параллельный, В исходном состоя- HsiH счетчик 67 обну.чяется запрещаю- гщм потенциалом, поступающим по уп- 15 рлвляющему входу 25 устройства, а им- гтульсы с выхода синхронизации на г-чегньпЧ вход, счетчика 67 не поступа- чгг, С инхроси1 нал сопровождения кода с выхода ; 1 коммутатора 2 поступает 20 на вход формирователя 5 адреса канала и с его выхода выдается код адрес i 00,..О первого канала. Если на вход 25 поступает разрешающий потен- ци.тл, счетчик 67 начинает подсчиты- 25 иать импул с.ы с выхода сиьгхронизации олок.ч 4, и формируемый на выходе счетчика 67 код соответствует адресу

ti в ,,aHHi.,i i MOMRHT ОПр.Ч -

- о -роса. Адресный 4,,i

;-:ка 67 пы,,1е,тся I Ml н 5 адреся ка.чак О

«. ,

.о, г nS;

: ;-.: roJ;

v, ;;,

T-OI-iriHi

.:v,or Я L.OM, Hxp DC иг и ала

vOMNiVT, . ГОГ I 2

Mf:H r И (8 бт, - 67, ; ак1гм i Oзь

40

45

..ic кг:л,ы Pf,даются форми- ,jona7 v .гдреса канала только г.-и э. yiafcCTBJieHH i с {ь тмвания кодов изме- г-1Т ч,,нсй г.афмрм или И Коммутятора 2 ,

/iv iiij .ftr ., р 6 .,.азнгч. ь для сб- 1 ipysctK , ; .ла ск ;г-а; нг пг,-:, в ; ок А. до -- : ;.-1еги7е ;ьной .-.нформациИ; : ступающ. : г-:ф1, рна11,ио -: 5ого вьгхода -..;-: ; 1 - РС 2. Указаны |й код может г г -у11ить : измери-; р.;.Ы :;Г; устанотжи ;- . .,диому и ,j.icr. при saaeprjeaHit -po,j,i-4.ел и,мере,(пя (паг 1эимер, по ис-; еч, НИИ нек ;; врРмс ИИ, ЛЪН ДОСТИ«i. riH5 об ЬУкТом onpe.rieiieb i( го состоя- 50 : .ия. И :: ,л.)- )ифратор 6 прелсшзля- ( i. соОой ксмбт Нйцио- чую су.ему совпа- ,(я, нмекжаую девять (по чис- ly разрядов к.,да) и один выход. При Пределенн :.--- KO;.I;C на входе дегаифрато- gf pa 6 на в; гходь его появляется сигнал окончания г водя,

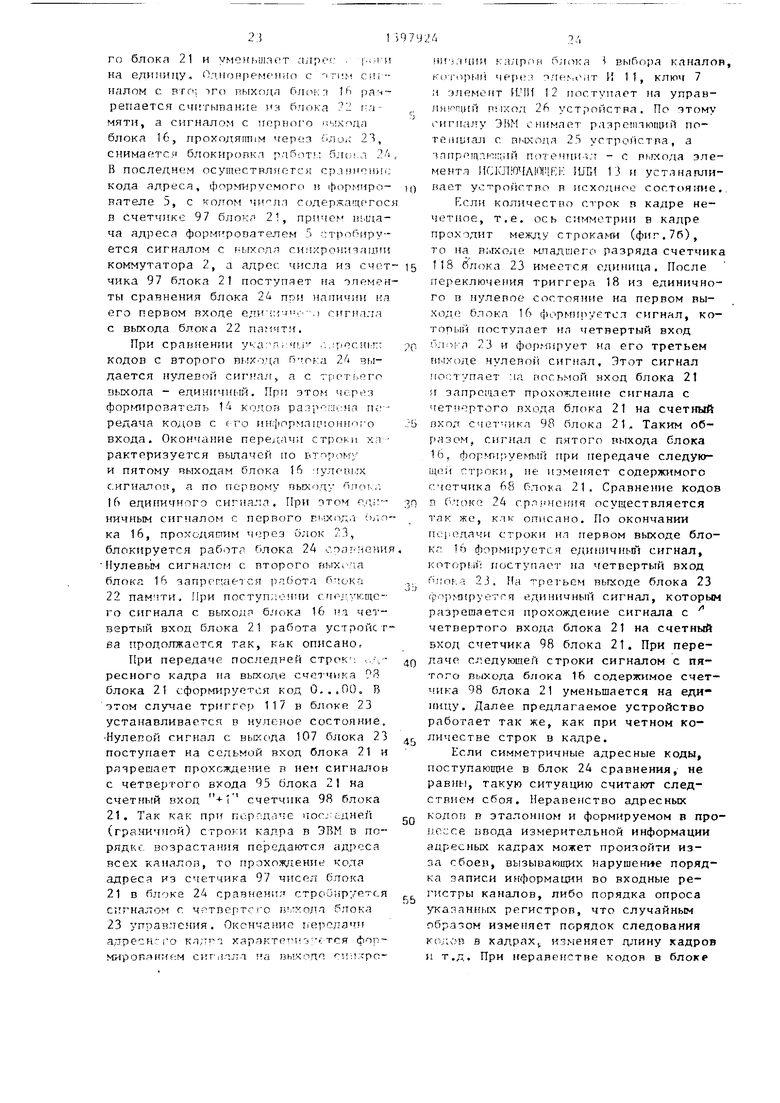

Ф г мирова71Ы1ь 14 кодов предназна- чен пьдач Л на информащюнны й

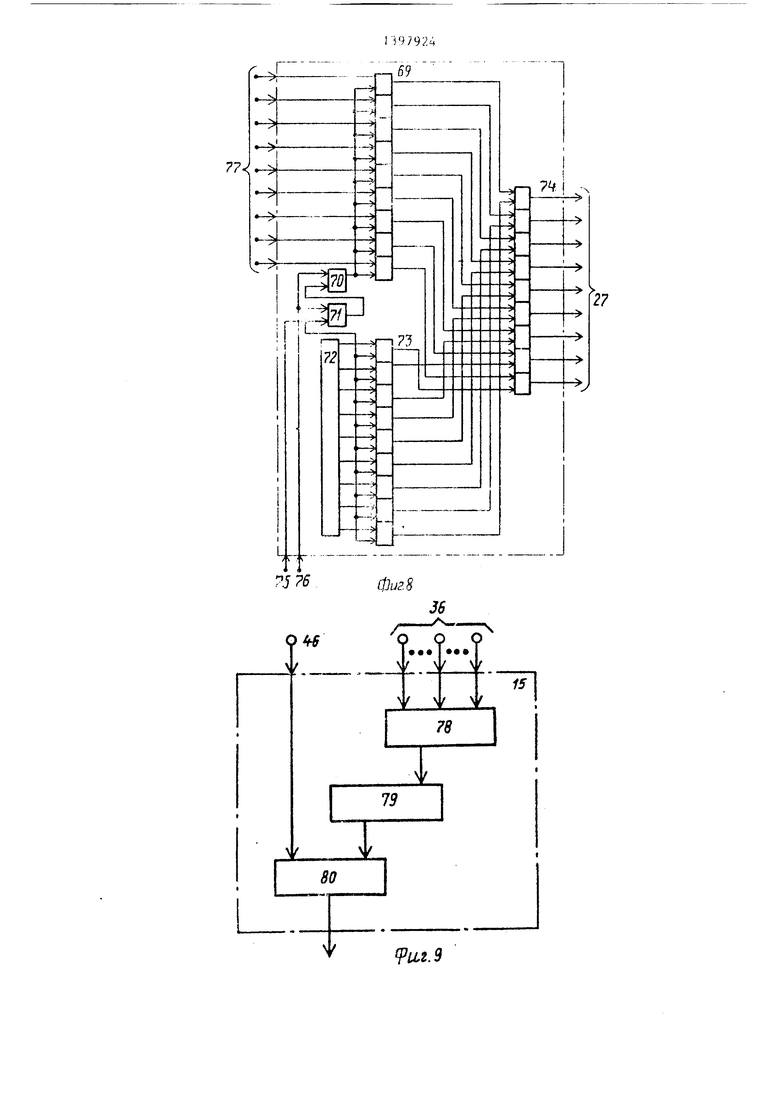

НИИ блока 3 и храним1.1м а бло се 2 памяти. Код сбоя с вь1хода формирователя 14 кодов выдается в слупае не- совгшдения адресных ;;одов в тег :ущих и этгшонном адресЕ Ь х кадрах. В состав фop oфoвaтeля 14 кодов (фиг.8) входит группа элементиз И 69, ИЛИ 70, элемент ИЛИ-НЕ М, генератор 72 кода сбоя, группа элементог; И 73 и группа элементов 1Ш11 7ч, Рогодц 75 и , 6 форм1 рователя 14 кодов являются соответственно первым и вторыг-1 управляющими входами. В зависимости от .оотояния сигн;шоп на управляготцих входах 75 и 76 вьщают я либо кодь; . .одов группы 77, либо с генератора 72 кода сбоя. На входы iруппы 77 формирователя 14 кодов поступают либо ;.:оды измер лтель- itoii информации, лиР.- информа ji H. Геие; РТ )Г Bi.V i. T- чкже 9- .. i

(bopMHpVfTC,4 , ) iMei

в 1 ти nei i ч-лча 14 i t Ti,

ч Лры-: чч .;.ь;а },.: у.г;

сбе К ;i : :- ;о

точ1 Г ка 11апряжени;г. ,

либо ЛОГИЧ1/СКОЙ et .

ческому улю. Зиачениг: . .:0.)я ,

выбирается таким, что Н(- принадлежит

МНОЖеСТКУ кодов ЛДреСНоЙ ИЗМГ ;)Цтель лой информа1 П{.

На уи);а г;я1ощих ;5.o,v i. .Ь и /i) фор- мировлте ;; 14 кодо)- возможны трг; KOM6i-iHiMj H сигнало -;, Первая - на jixoj v 75 ri H.i пход /6 П . i-vnaHiT зч- (; i i:iT- e и. у. нцгитлы. 3 этом ГЛУЦ,-,: па о )диг, вхо/1 rpyririhi ,,.;(ем,;нто- ; ё ii /п/упа -л : рлзрг.шаюц : га:тенг;ияп, а ;а pyrrn:,j - покент J}

ипр1глпг: : ..1ШТ)1.. 1 ; 1 ,ы -/ leРУИ:Л.- -ieT-i-J-.TOB ИЛе /4 прИХ :П

м- ...j./1 -. -Х угов групг(ь: 77 ч:.(.ми- -i А .коло-:. Тлл ПГ .ле с ja.io.-i .лИя ьро; ог1ит о-Г;ироря- кг,,гон и пг и riiipo;; гчО - г; ;л

одм 1 греснои .

|- т.;, Д., КОТО: 1Й . г ГОМОПИ К) Д: .:- pej-r; .-DOM KD- : - Ti pc iTtip;; /2

.T.V.-ЛЛ ; l ИСл; В Ti : .4 /.ьщр .и ;пм.с .Г1 .)1И; (

И Ч рез инфс Р

I ,0

iTb

;.:i

., а ь п яход d ретьем случя ;:, к , i,a

н ...ч-;ощих вход.

Пиан

Да 1 ттотеп50 5

,,i

ь

0

5

0 f

НИИ блока 3 и храним1.1м а бло се 2 памяти. Код сбоя с вь1хода формирователя 14 кодов выдается в слупае не- совгшдения адресных ;;одов в тег :ущих и этгшонном адресЕ Ь х кадрах. В состав фop oфoвaтeля 14 кодов (фиг.8) входит группа элементиз И 69, ИЛИ 70, элемент ИЛИ-НЕ М, генератор 72 кода сбоя, группа элементог; И 73 и группа элементов 1Ш11 7ч, Рогодц 75 и , 6 форм1 рователя 14 кодов являются соответственно первым и вторыг-1 управляющими входами. В зависимости от .оотояния сигн;шоп на управляготцих входах 75 и 76 вьщают я либо кодь; . .одов группы 77, либо с генератора 72 кода сбоя. На входы iруппы 77 формирователя 14 кодов поступают либо ;.:оды измер лтель- itoii информации, лиР.- информа ji H. Геие; РТ )Г Bi.V i. T- чкже 9- .. i

(bopMHpVfTC,4 , ) iMei

в 1 ти nei i ч-лча 14 i t Ti,

ч Лры-: чч .;.ь;а },.: у.г;

сбе К ;i : :- ;о

точ1 Г ка 11апряжени;г. ,

либо ЛОГИЧ1/СКОЙ et .

ческому улю. Зиачениг: . .:0.)я ,

выбирается таким, что Н(- принадлежит

МНОЖеСТКУ кодов ЛДреСНоЙ ИЗМГ ;)Цтель лой информа1 П{.

На уи);а г;я1ощих ;5.o,v i. .Ь и /i) фор- мировлте ;; 14 кодо)- возможны трг; KOM6i-iHiMj H сигнало -;, Первая - на jixoj v 75 ri H.i пход /6 П . i-vnaHiT зч- (; i i:iT- e и. у. нцгитлы. 3 этом ГЛУЦ,-,: па о )диг, вхо/1 rpyririhi ,,.;(ем,;нто- ; ё ii /п/упа -л : рлзрг.шаюц : га:тенг;ияп, а ;а pyrrn:,j - покент J}

ипр1глпг: : ..1ШТ)1.. 1 ; 1 ,ы -/ leРУИ:Л.- -ieT-i-J-.TOB ИЛе /4 прИХ :П

м- ...j./1 -. -Х угов групг(ь: 77 ч:.(.ми- -i А .коло-:. Тлл ПГ .ле с ja.io.-i .лИя ьро; ог1ит о-Г;ироря- кг,,гон и пг и riiipo;; гчО - г; ;л

одм 1 греснои .

|- т.;, Д., КОТО: 1Й . г ГОМОПИ К) Д: .:- pej-r; .-DOM KD- : - Ti pc iTtip;; /2

.T.V.-ЛЛ ; l ИСл; В Ti : .4 /.ьщр .и ;пм.с .Г1 .)1И; (

И Ч рез инфс Р

I ,0

iTb

;.:i

., а ь п яход d ретьем случя ;:, к , i,a

н ...ч-;ощих вход.

Пиан

Да 1 ттотеппоступает раярешаюпуи пптенциа 1, а на вход 76 - запрещающий, на общий вход группы элементов И 69 поступает запрещающий потенциал, а на общий вход группы элементов И 73 разрешающий. Вследствие этпго на выходы 27 через группу элементоп НИИ 74 выдается код сбоя с генератора 72 кола сбоя.

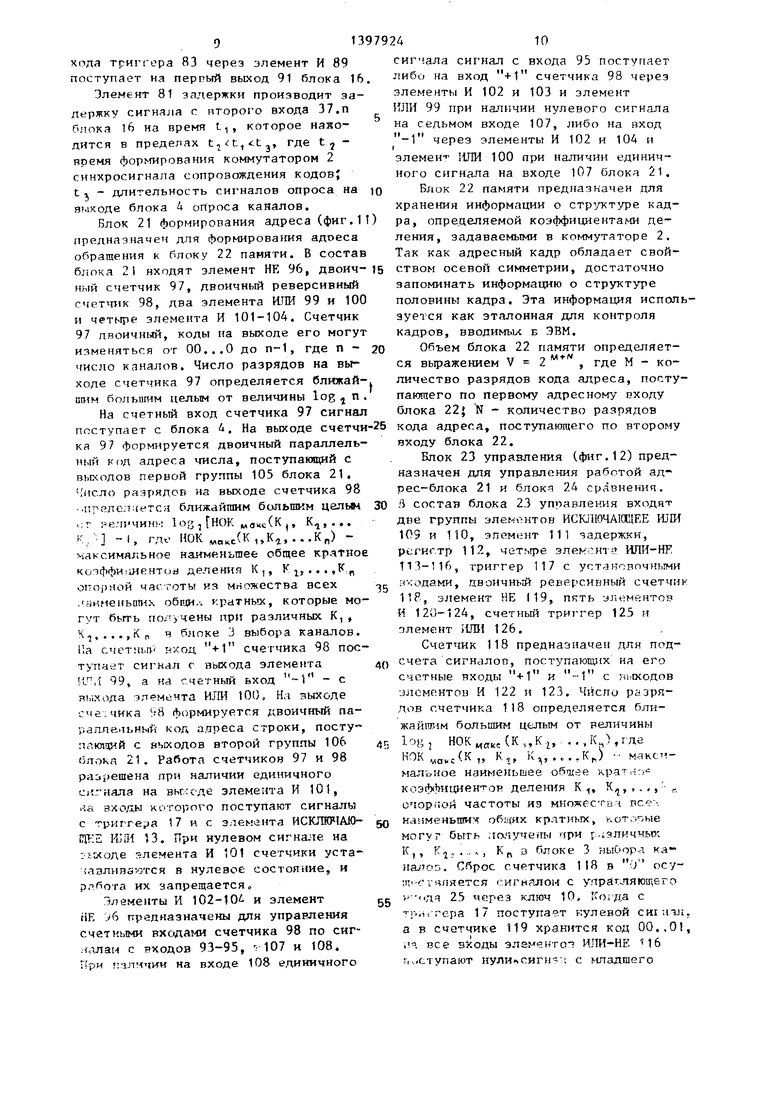

Формирователь 15 граниг1Ы кадра (фиг,9) предназначен для форг нрования сигнала, определяющего границу кадра. В состав формирователя 15 входят элемент И 78, триггер 79 с установочными входами и элемент И 80. Признаком границы кадра является выполнение условия одновременности ггояпления сигналов на всех ВЫХОДЛУ управления записью блока 3 выбора каналов.

Признак границы кадра формируется элементом И 78, когда на всех его входах одновременно появляются сигналы управления записью. В этом случае сигналом с выхода элемента И 78 триггер 79 устанавливается в единичное состояние, и с его единичного выхода вьщается разрешающий потенциал на один из входов элемента И 80, Сигнал на выходе формирователя 15 границы кадра сформируется после поступления на его первый вход,т.е. на вход элемента И 80, сигнала с п-го выхода опроси блока 4 опроса каналов.

Установка триггера 79 в исходное (нулевое) состояние осуществляется перед началом работы всего предлагаемого устрой-тва в целом сигналом, который переводит все блоки в исходное состояние, С целью повышения наглядности схемы, представленной на фиг.1, и упрощения ее восприятия, цепи установки блоков устройства в исходное состояние не показаны.

Блок 16 вьщеления строк предназначен для получения сигналов, указывающих на появление строки кадра адресной или измерительной информации. Под строкой кадра будем понимать последовательность кодов адресной или измерительной информации, полученных за один цикл опроса с первого по п-й входных регистров каналов блоком 4 опроса. Строка кадра может содержать от одного до п кодов. Признаком строки является наличие синхроимпульсов сопровождения кодов на выходе синхронизации коммутатора 2 в период времени мез1чцу опросами с первого по последний i Xiijii :.ix 11ег исгр|1В ра 2.

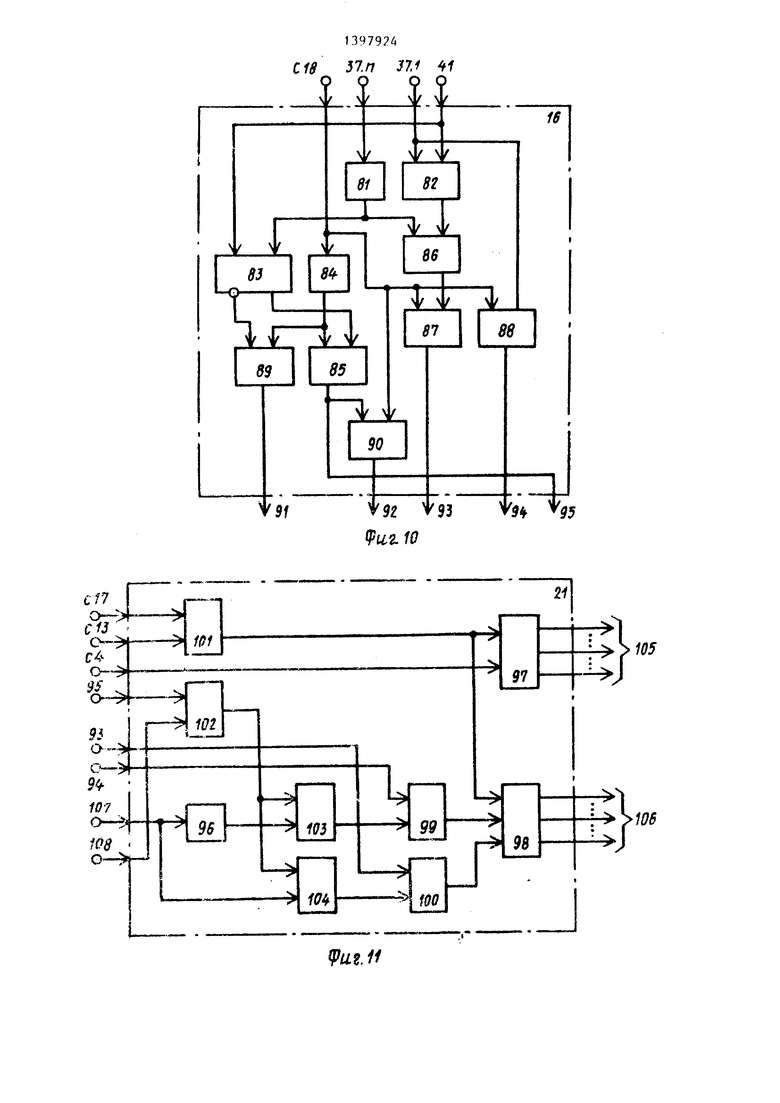

В состав блгжя 16 (фиг.10) входят элемент 81 задержки, тригт-еры 82 и

п ,

83 с установочными нхоцлми, элемент НЕ 84, элемент, И 83-89, элемент Ш1 90 и выходы 91-95. На перпмй вход блока 16 вьщеленич crpris: iTi r- ynaeT

сигнал с вькода втопгпчч триггера 18. Если на первый вход с триггера 18 поступает единичный сигр(ал, элементы И 89 и 85 заперты, и на выход 92 через элемент ИЛИ 90 щ.щается единичнь1й сигнал. Единичный сигнал, поступающий на вход 37 блока 16 устанаьли- вает триггер 82 в единичное состояние и через элемент И 88 проходит на четвертый вьгход 94 блока 16. Единичный

сигнал на третьем выходе 93 блока 16 сформируется по сигналу с второго входа 37.П блока 16 в том случае, если до поступления единичного сигнала на второй вход З7.п блока 16 на

его четвертый вход 41 не поступал

сигнал с выхода синхронизации коммутатора 2.

Если же синхросигнал на вход 4)

поступает раньше единичного сигнала на входе 37.п, то триггер 82 устанавливается в нулевое состояние, и элементы И 86 и 87 будут заперты. При поступлении на вход 37.1 следующего

единичного сигнала работа этой части блока 16 протекает аналогично описанному. Если на первый вход блока 16 поступает нулевой сигнал, элементы И 89 и 85 переводятся в открытое состояние, а элементы И 87 и 88 запираются. Триггер 83 устанавливается в единичное состояние единичным сигналом с четвертого входа 41 блока, а в нулевое состояние - сигналом с

выхода элемента 81 задержки, на вход которого поступает единичный сигнал с второго входа 37,п блока 16 вццеле- ния строк, В исходное нулевое состояние триггер 83 устанавливается при

приведении блока 16 в исходное состояние перед началом работы устройства в целом. Цепи установки блоков устройства в исходное состоя1Л1е на фиг.1 с целью упрощения схемы не показаны. Сигнал с единичного выхода триггера 83 через элемент И 85 поступает на пятый выход 95 блока 16 и через элемент ИЛИ 90 - на второй выход 92 блока 16. Сигнал с нулевого вы9139

ходя триггера 83 через элемент И 89 поступает на перпый выход 91 блока 16

Элемент 81 задержки производит задержку сигнала с второго входа З7.п б. тока 1б На время t, которое находится в пределах где время фop mpoвaния коммутатором 2 синхросигнала сопровождения кодов; t ,| - длительность сигналов опроса на я.1ходе блока 4 опроса каналов,

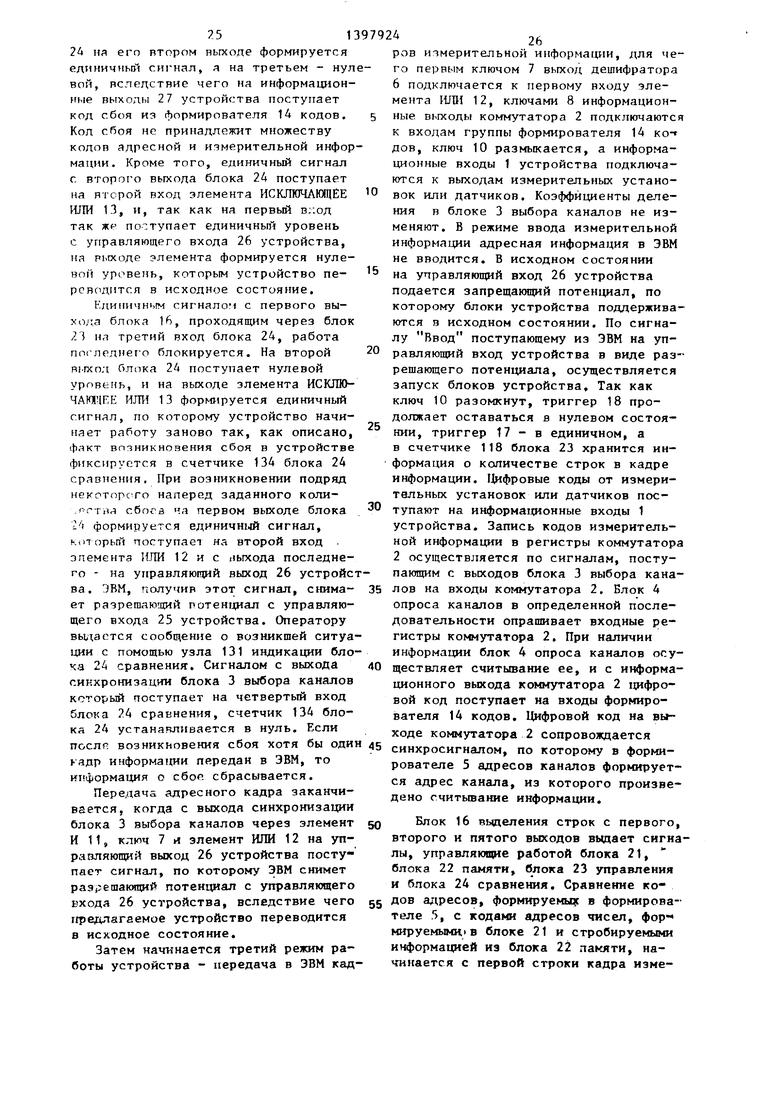

Блок 21 формирования адреса (фиг.11 предназначен для формирования адоеса обращения к блоку 22 памяти. В состав

Ч

блока 21 нходят элемент НЕ 96, двоим-15 ством осевой симметрии, достаточно

Нп1й счетчик 97, двоичный реверсивный счетчик 98, два элемента И.ПИ 99 и 100 и четыре элемента И 101-104. Счетчик 97 двоичный, коды на выходе его могут изменяться от 00...О до п-1, где п - 20 число каналов. Число разрядов на выходе счетчика 97 определяется ближай-. пим больпшм целым от величины log п .

запоминать информацию о структуре половины кадра. Эта информация испол зуется как эталонная для контроля кадров, вводимых Б ЭВМ.

Объем блока 22 памяти определяется выражением V 2 , где М - количество разрядов кода адреса, поступающего по первому адресному входу блока 22{ N - количество разрядов

На счетный вход счетчика 97 сигнал поступает с блока 4. На выходе счетчи-25 кода адреса, поступающего по второму ка 97 формируется двоичный параллель- входу блока 22. нын код адреса числа, поступакмций с

Блок 23 управления (фиг,12) предназначен для управления работой адрес-блока 21 и блока 24 сравнения.

выхода элемента

Г - с

выходов первой группы 105 блока 21, Ч ис.ло разрядов на выходе счетчика 98 .пг -Лел;(етс;-1 ближайшим большим целым .;г реличинм log, НОК „вксСК р К , . . , К, - I, НОК ,акс(К ,, Ка. . К п) - максимальное наименьшее общее кратно коэффи и1ентой деления К,, ...,K, опорной частоты из множества всех . аинемьпмх общил кратных, которые могут быть получены при различных К, , К,...,Кг, ч блоке 3 выбора каналов, iia счетные вход 41 счетчика 98 поступает сигнал г .- ГА 99, а ка счетный вход выхода элемента ИЛН 100, На зыходе сче;чика iS формируется двоичный па- ралле,1ьный код адреса строки, посту- паютцнй с выходов второй группы 106 блока 21, Работа счетчиков 97 и 98 разрешена при наличии единичного сигнала на вы;еде элемента И 101, входы которого поступают сигналы с триггера 17 и г. элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13. При нулевом сигнале на :-1Коде элемента И 101 счетчики уста- ;азлива ются в нулевое состояние, и работа их запрещается

Элементы И 102-104 и элемент (iE предназначены для управления счетными входами счетчика 98 по сиг- .чллаи с входов 93-95, г 107 и 108. При тмличии на входе 108 единичного

4

10

сигчала сигнал с входа 95 поступает либо на вход +t счетчика 98 через элементы И 102 и 103 и элемент ИЛИ 99 при наличии нулевого сигнала на седьмом входе 107, либо на вход 1 через элементы И 102 и 104 и элемен- ИЛИ 100 при наличии единичного сигнала на входе 107 блока 21.

Блок 22 памяти предназначен для хранения информации о структуре кадра, определяемой коэффициентами деления, задаваемыми в коммутаторе 2. Так как адресный кадр обладает свойзапоминать информацию о структуре половины кадра. Эта информация используется как эталонная для контроля кадров, вводимых Б ЭВМ.

Объем блока 22 памяти определяется выражением V 2 , где М - количество разрядов кода адреса, поступающего по первому адресному входу блока 22{ N - количество разрядов

кода адреса, поступающего по второму входу блока 22.

кода адреса, поступающего по второму входу блока 22.

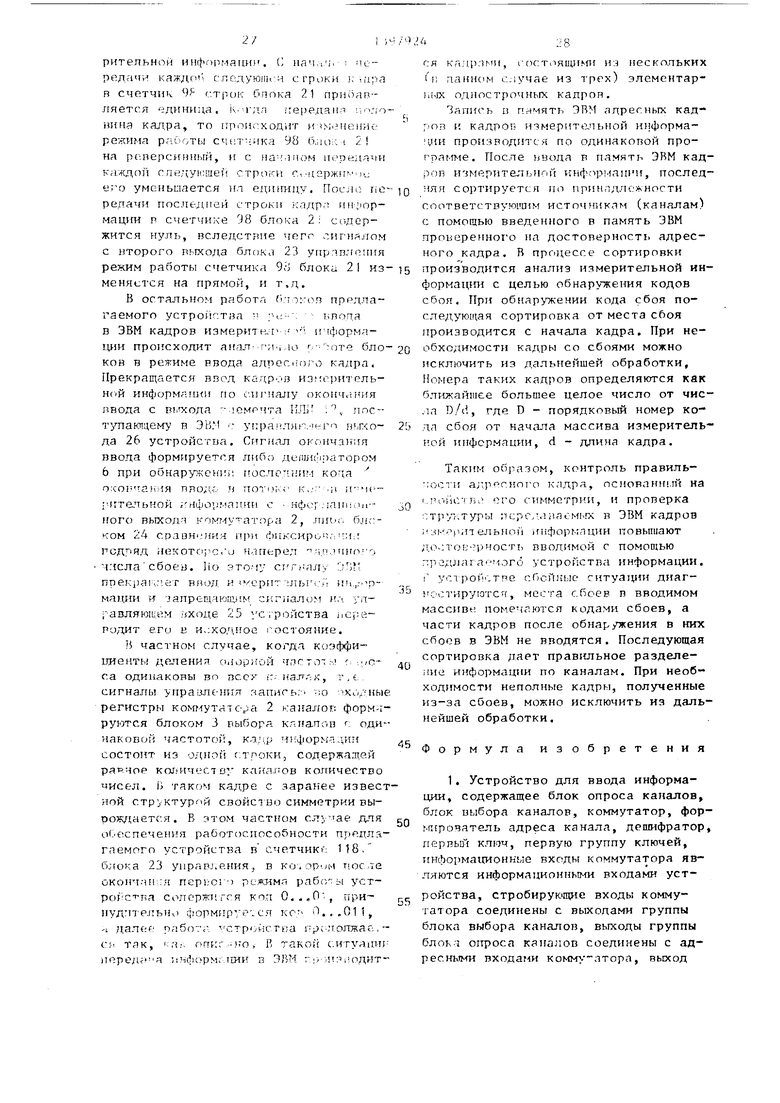

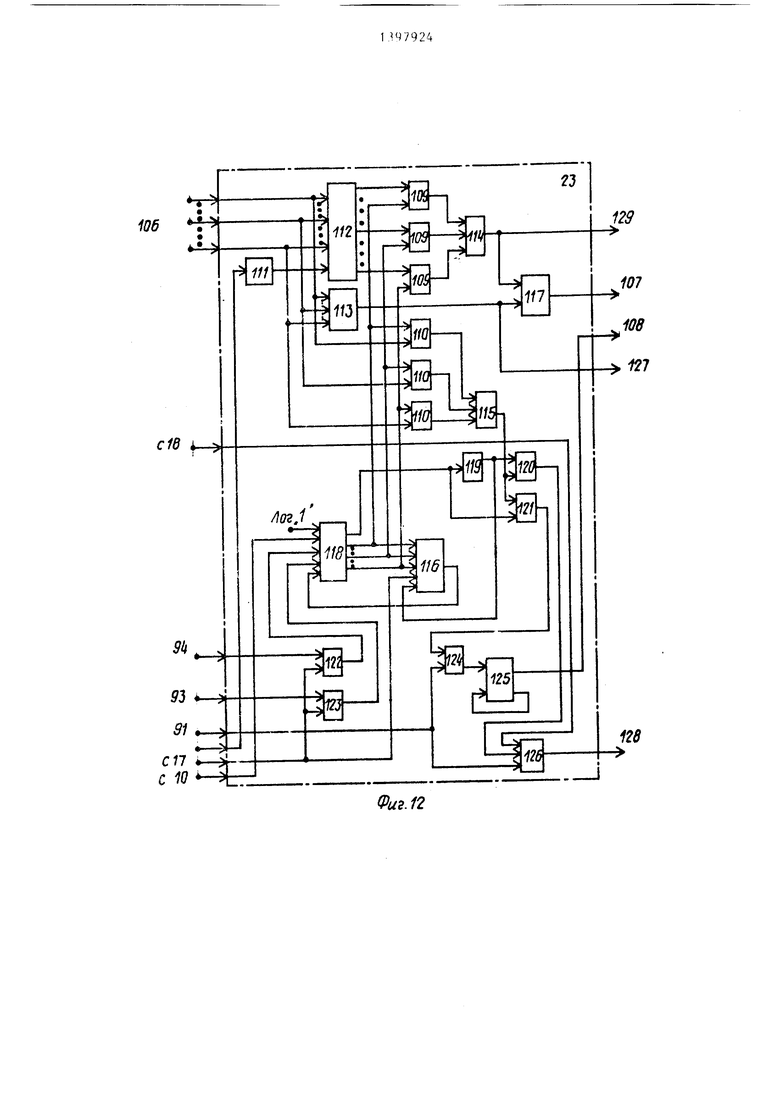

Блок 23 управления (фиг,12) предназначен для управления работой адрес-блока 21 и блока 24 сравнения.

состав блока 23 управления входят две группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 109 и 110, эпемент 111 задержки, pt;rHc.Tp 112, четмре элемент ИПИ-НК 113-Пб, триггер 117 с установочными

входами, двоичный реверсивный счетчик 11Р, элемент НЕ 119, пять элементов И 120-124, счетный триггер 125 и элемент jLTH 126,

Счетчик 118 предназначен для подсчета сигналоо, поступающ51х на его счетные входы +1 и -1 с выходов злсментоБ И 122 и 123, Число разрядов счетчика 118 определяется бли- жайпмм большим целым от величины

НОК „ИКС (К ,,К .J, j (К ,, К ,, К,

К),где

. .,, м.

акс:т1-т ,- -,:

log

КОК

мальное наименьшее обткее крат

коэЛЬидаентор деления К , К,,,.,

очораой частоты из множества рее: .

наименьшие общих крлтньпс, у.от,:лые

могу быть ла тучеиы при р.зличньк

К,

в блоке 3 гшОорл ка

И;

(

Сброс счетчика 11В в О осу

Ж - - г .пяется сигнапон с упрагляющего - «дч 25 (ерез ключ 10 Согда с Tr«.ii repa 17 поступает нулевой сигиги. а в счетчике 119 хранится код 00,.О, . П все в5соды элементов ИПИ-НЕ Л6 Гг..ступают нулилсигн :: с мпадшего

5

10

для пы11а ч)тки сигнала установки п единичное состояние триггера 117 и вьщачи этого сигнала на первый выход 129 блока 23 управления. Информация с входов 106 блока 2Т заносится в регистр 112 по сигналу, поступающему на пятьй вход блока 23 и задержанному элементом 111 задержки, к.торий предназначен для задержки сигнала, поступающего на его вход с пятого входа блока 23 на время t, которое находится в пределах t,. С помощью элемента ИСКЛЮЧАЩЕЬ: ИЛИ 109 и эле11139792412

разряда счетчика 110 поступает на

вход элемента 1ШИ-НЕ 116 через элемент НЕ 119 На выходе элемента

ИЛИ-НЕ 116 формируется сигнал, по

которому во второй разряд счетчика

118 записывается единица, т.е. формяруется код 0...01 .

Элемент ИЛИ-НЕ 113 предназнаион

для вьщачи сигнала на выходе 127

и анализа на равенство нулю кода,

поступающего на входы группы 106 блока 23, Единичным сигналом с вьгхода элемента ШТИ-НЕ 113, который форми- ,руется при наличии нулей на всех его вхо-15 мента 114 производится срав- дах, триггер 117 устанавливаетсянение кода, хранящегося в регистре

в нулевое состояние, ;: тот же сигнал112,с кодом содержимого счетчика

поступает на выход 1:- 7 П|.ока 23. С118, деленным на два. При сравнении

помощью элемента ИСКЛКП{АЮ11|1 :Е ИЛИ 110кодов на выходе элемента ИЛИ-НЕ 114

и элемента ИЛИ-НЕ 115 осуществляется 20 4)ормируется единичный сигнал, а при поразрядное сравнение кода, поступаю- несравнении - нулевой. Единичным сиг- щего на входы 106 блока 23 с кодом, получающимся в счетчике 110, деленным на два. Деление содержимого счетчика 118 на два осуществляется путем Ь пает на первый выход 129 блока 23 использования для сравнения всех разрядов счетчика 118 за исключением младшего, который используется для определен / четно либо нечетно содержимое счетчика 118, При равенстве кодов на выходе элемента ШШ-НЕ 115 формируется единичный сигнал, при неравенстзе кодов нулевой. На выход . 128 блока 23 сигнал поступает с вьгхо- да элемента ИЛИ 126. На выходе элемеи-з5 ситуаций и управление работой форми- та И 120 единичньп сигнал фopмзipyeтcя рователя кодов 14 в зависимости от при сравнении кодов (единичный сигнал на выходе элемента ИЛИ-НЕ 115) и равенстве нулю шшдшего разряда счетчи-. ка 118. При равенстве единице млад- 40 шего разряда счетчика 118 и сравне ши кодов на выходе элемента И 121 формируется единичньп сигнал, который проходит через элемент И 12А при наличии единицы на входе 91 блока 23, пере- 45 предназначена для стробирования пос- ключает триггер 125, который работает тупления в блок 24 кодов по входам в счетном режиме, т.е. переключает

налом с выхода элемента ItJW-HE 114 триггер 117 устанавливается в единичное состояние, этот же сигнал постууправления.

Блок 24 сравнения (фиг.13) предназначен для контроля адресных кодов, поступающих из формирователя 5 адре- 30 сов каналов, путем поразрядного сравнения этих кодов с эталонными адресными кодами, получаемыми с помощью блока 22 памяти и блока 21. Блок 24 осуществляет также индикадаю сбойных

результатов контроля адресных кодов. В состав блока 24 сравнения входят группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 130, узел 131 индика14ии, два элемента ИЛИ 132 и 133, десятичный счетчик 134, группа элемеитов И 135, три элемента И 136-138 и два элемента НЕ 139 и 140. Группа элементов И 135

второй группы 105. Управление группой элементов И 135 осуществляется сигналом с выхода элемента ИЛИ 133, на

свое состояние по каждому импульсу с выхода элементов И 124.

Установка счетного триггера 125 в исходное единичное состояние производится при установке исходного состояния блока 23 перед началом работы предлагаемого устройства. Цепь установки блока 23 в исходное состояние с целью упрощения схемы не показана. Элемент 111 задержки, регистр 112, группа элементов ИСКЛЮЧАЩЕЕ ИЛИ 109 и элемент 11ПИ-НЕ 114 предназначены

для пы11а ч)тки сигнала установки п единичное состояние триггера 117 и вьщачи этого сигнала на первый выход 129 блока 23 управления. Информация с входов 106 блока 2Т заносится в регистр 112 по сигналу, поступающему на пятьй вход блока 23 и задержанному элементом 111 задержки, к.торий предназначен для задержки сигнала, поступающего на его вход с пятого входа блока 23 на время t, которое находится в пределах t,. С помощью элемента ИСКЛЮЧАЩЕЬ: ИЛИ 109 и элемента 114 производится срав- нение кода, хранящегося в регистре

)ормируется единичный сигнал, а при несравнении - нулевой. Единичным сиг- пает на первый выход 129 блока 23 ситуаций и управление работой форми- рователя кодов 14 в зависимости от предназначена для стробирования пос- тупления в блок 24 кодов по входам

налом с выхода элемента ItJW-HE 114 триггер 117 устанавливается в единичное состояние, этот же сигнал посту)ормируется единичный сигнал, а при несравнении - нулевой. Единичным сиг- пает на первый выход 129 блока 23 ситуаций и управление работой форми- рователя кодов 14 в зависимости от предназначена для стробирования пос- тупления в блок 24 кодов по входам

управления.

Блок 24 сравнения (фиг.13) предназначен для контроля адресных кодов, поступающих из формирователя 5 адре- сов каналов, путем поразрядного сравнения этих кодов с эталонными адресными кодами, получаемыми с помощью блока 22 памяти и блока 21. Блок 24 осуществляет также индикадаю сбойных

)ормируется единичный сигнал, а при несравнении - нулевой. Единичным сиг- пает на первый выход 129 блока 23 ситуаций и управление работой форми- рователя кодов 14 в зависимости от предназначена для стробирования пос- тупления в блок 24 кодов по входам

результатов контроля адресных кодов. В состав блока 24 сравнения входят группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 130, узел 131 индика14ии, два элемента ИЛИ 132 и 133, десятичный счетчик 134, группа элемеитов И 135, три элемента И 136-138 и два элемента НЕ 139 и 140. Группа элементов И 135

)ормируется единичный сигнал, а при несравнении - нулевой. Единичным сиг- пает на первый выход 129 блока 23 ситуаций и управление работой форми- рователя кодов 14 в зависимости от предназначена для стробирования пос- тупления в блок 24 кодов по входам

второй группы 105. Управление группой элементов И 135 осуществляется сигналом с выхода элемента ИЛИ 133, на

входы которого поступают сигналы с первого входа 141 и второго входа 127 блока 24. Группа элементов ИСКЛЮ- ЧАКПЕЕ ИЛИ 130 и элемент ИЛИ .132 предназначены для поразрядного сравнения кодов. При сравнении кодов на выходе элексента ИЛК 132 формируется нулевой сигнал, а при несравнении - единичный. Элемент И 137 пр ед нагана- чен для выцачи на вькод 75 блока 24

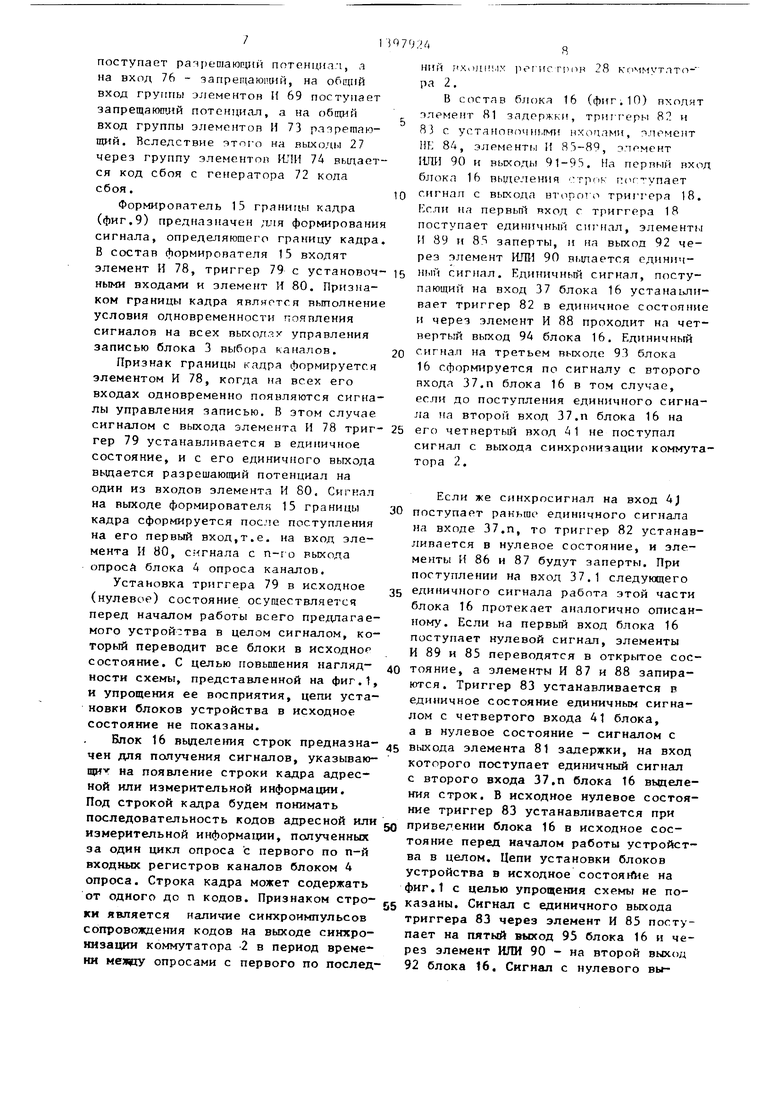

сигнала о месрапнении кодор, norty- пянодих па входы блока 2А, а элемент И 38 для выдачи на выход 76 блока 24 сигнала о сравнении этих кодов. Элементы И 137 и 138 стробируются сиг налом с вьосодя элемента НЕ 140, на яход кото(1ого поступает сигнал с третьего входа 128 блока 24, При нулевом сигнале на входе 128 элементы И 137 и 138 г)ткрываются, и результаты cpaHFieitHH поступают на выходы блока 24 сравнения. При единичном сигнаtia фиг, 7а изображены временные диаграммы работы 4-капального устройства , На первой диаграмме представлены сигналы, поступаюЕ1ие на второй мход блока выбора каналов с выхода опроса последнего канала блока опроса каналов, частота следования упомянутых сигналов , где частота опроса каналов. На последую- гоих четьфех диаграммах изображены сигналы управления записью во входные регистры каналов. Эти сигналы следу- toT с частотами ., где К - коэфле на входе 128 элементы И 137 и 138

яаперты, и результатов прав- IF.фициент деления частоты f длА i-ro нения на выходы 75 и 76 заблокирова-канала, Дпя приведенного примера на, в этом случае на эти выходы выда-отсчб .ты измерительной информации пос- нулевые сигналы. Счетчик 134прупают в первый, второй, третий и осуществляет подсчет числа подрядчетвертьй каналы с частотами соответ- :ледующих сбоев и имеет счетный вход, 20с -твенно равными f.-f/2 f f/3 , ня который поступает сигнал с выхода з э Входные регистры элемента И 137, и установочный вход,.опрашиваются с частотой f, очередна который поступает сигнал с четвер-ность опроса последовательная в по- того входа 142 блока 24 сравнения,рядке возрастания адресов каналов, по которому осуществляется обнуление счетчика, На фиг,7б изображены аналогичные

Предположим также, что обнуление- временные диаграммы работы 3-канальсчетчика 134 осуществляется и приного устройства. Отсчеты иямерите-льгг:;п чппг. бггока 24 q исходное состоя -ной гтнформащпт поступают в ;сррый, ;ие перен началом работы предлагаемо- 30 второй и третий каналы с частотямтт,

, . ус г ройс/li.;,. Лор устим, что счетчик ) является двукразрядным, т,е. мак- .тмальное чи Ло ппди.яп следутоп их ра 1} о т . ам, ь:хопы счетч1-:ка 134 .а ч:оч ны к вкод. м элемента И 136, л:; :-.ча содержимое очетц-ика достигает Ki;,,sa 11,Ч -,-. г одряд вьграбатг шакп ся три сигкячя о я°срапнении адресных кодов с вг-иода элемента И 137, на

bXvv ;.-- элемента И i 36 формируется ели- 40 ,i 7 i з i л i т ) i i т /, , i 7 1

MS/-, I , - , I , /. , ч 5 I , J .- , I , , , J --4 1 I , iC , I ,

Hi. гигн тп, которьги поступает на

3„,

jAbfxoA - лока 24, а также на узел J1 ,1рщикэш1р ; 1ля указания оператору

0не аботоспособном состоянии устрой1Р.ЯС45

адресный кадр

Для второго примера упомянутая юплсдовятельность адрс:сных кодов н адресный кадр имеют i.tH.i,

. ,/,2,-, .; ,1,3,3.,2, 3,1, 3,3. 3,1, 3.2, 3,3, 1,3, 3,3, 1,2,3,; 2,3,1,3.,

.адрес гий кадр

(. первого и ЕТорого примеров ,г.иоды сле;-1овткия кадров, определяе- ;;е наименьшим общим кратным (НОК) коэсМ ициеитов деления частоты f в ка- гтлах, соответственно равны:

г 1 .НПКГК., К,.

.Дп (к,, к,,,,.,к„); т, -- -12;

tia фиг, 7а изображены временные диаграммы работы 4-капального устройства , На первой диаграмме представлены сигналы, поступаюЕ1ие на второй мход блока выбора каналов с выхода опроса последнего канала блока опроса каналов, частота следования упомянутых сигналов , где частота опроса каналов. На последую- гоих четьфех диаграммах изображены сигналы управления записью во входные регистры каналов. Эти сигналы следу- toT с частотами ., где К - коэфной гтнформащпт поступают в ;сррый, второй и третий каналы с частотямтт,

соотяетственно ртяным Г , f- f/5, .

,Д,чя первого примера -ядресные коды г .ых.од формироватепя адреса каналов вьщаются в следуюгарй по -:ледоза- тельности, в которой можно .чгаделить периодически повторянзщуюся часть - адресHbrfi кадр ,,,,1,2,3,4,

адресный кадр

Для второго примера упомянутая юплсдовятельность адрс:сных кодов н адресный кадр имеют i.tH.i,

-Т- ЭДегшм строку кадг,-, как после- л- ). ельносгь адресных кодов, полу- uf;i-ii-rx за едки дакл опроса капало (т,- , прИ| однократнсм опросе с перво- г о пз последний каи л, )„ Цикл опроса f , .глов равен 1/ , К-:.1Кдая строка rcic, 15

тоит из последовательности чисел - адресных ко/;ов, количество которых может изменяться от 1 до п. Будем вьщелять строки в адресньк кадрах

а для второго:

(3)(3)(1,3)(3)(2,3)(1,3)(3)(3)(1,3)(2,3)(3)(1,3)(3)(3)(1,2,3) 12 3 A 36 78 9 10 11 12 13 1415

Граничные строки всевозможных кадров (в примерах строки № 8 и № 15) образуются адресами всех каналов, взятыми в порядке возрастания, и поэтому при различных К, и заданном п всегда постоянны и известны. Остальные же строки кадров являкясч переменными, так как зависят от коэффициентов Kj. Предположим, что переменные и граничные строки кадра образуют Соответственно переменную и постоянную части адресного кадра.

Анализируя структуру кадров (1) и (2) можно сделать вывод, что переменная часть адресных кадров обладае свойством симметрии относительно оси проходящей через середину кадра, т.е. строки, симметричные относительно середины кадра равны. В первом примере равны строки № 3 и Р 5, f 2 и ff 6, и т. д. во втором примере равны строки |Р7и№8, И 6и№9, №5

и № 10 и т.д. Ось симметрии проходит либо через центральную строку кадра при четном числе строк в адресном кадре (в первом примере через строку № 4), либо меяиу строками при нечетном числе строк в адресном кадре (но втором примере между строками Р 7 и 9 8).

Вследствие симметрии переменной части кадра содержащаяся в нем адрес ная информация является избыточной - дпч сортировки в ЭВМ достаточно знания половины кадра, так как вторую половину кадра можно восстановить по первой.

Устройство работает следующим образом.

Устройство работает в трех режи™ мах, которые определяются попожением ключей 7,8 и 10 к состоянием первого триггера 17,

В первом режиме - настройке - а блоке 23 управления осуществляется подсчет и запоминание числа строк в

139792416

кругльми скобкпми, а ниже проставлять их номера. Тогда fvia первого приьюра пoлyчae

t ( 1) (2) (1 . 3) (1 , 2, 4) (1, 3) (2) (1) (1 , 2, 3, i) 12245 f 78

(t)

(2)

5

0

5

0

5

0

g

5

кадре информации. В зависимости от тогО{ четно или нечетно это число блок 23 управления соответствующим образом настраивается на дальнейшую работу.

Во втором режиме осуществляется ввод в ЭВМ одного кадра адресной информации, сопровождаемый контролем вводи мого кадра, основанном на свойстве осевой симметрии его структуры. При передаче первой половины адресного кадра производится запоминание в определенной форме ее структуры, т.е. адресных кодов и порядка следования адресных кодов в кадре, в блоке 22 памяти, а при передаче второй половины адресного кадра производится сравнение ее структуры с хранящейся в блоке 22 памяти информацией, т.е. контроль ДОС.оверности вводимого кадра адресной информации. В случае несравнения, т.е. сбоя в вводимом адресном кадре, вместо сбойного адресного кода в ЭВМ вводится определенный код- код сбоя, чем помечается сбойный адресный кадр, который в дальнейшем для сортировки не используется. Устройство в этом случае переводится в исходное состояние, и далее повторяется ввод адресного кадра. В случае трех повторных подряд следующих сбоев фиксируется отказ, о чем указывается оператору сигналом из блока 24 сравнения, и ввод завершается. Если после контроля адресный кадр признан достоверным, запомненная структура половины такого кадра будет исполь зо- ваться как эталонная для контроля структуры вводимых в ЭВМ кадров измерительной информации.

В третьем режиме производится ввод в ЭВМ кадров измерительной информации с проверкой их достоверности путем контроля структуры передаваемых в ЭВМ кадров. Указанный контроль осуществляется сравнением адресных кадPDB, r OJiyqarMbDC (no не персдава pf if.ix в ЭРМ) к .фгцеггр or;ppLa канапов с зтлло.ч-м.. обра Ч( во 5 тором режим . , iifeprinn и рторая половины

каяи;ого ро.- учаем -)го для контроля адресного кадра сранняраются с половиной эталонного адресного кадра. В случае ресрапиенил вместо кода измерительной информации в кадре измери- тельной информации в ЭВМ передается код сбоя (гак и но втором режиме), тем самым по; ечается сбойный кадр измерительной информрл ии. Факт сбоя при образовании кадра измерительной информации необходимо знать ulя пра- последующей сортировки, так как после обнаружения сбоя предлагаемое устройство переводится в исходно Состояние, и процесс формирования

адра и мертп ельной информа1р1И начи- гтется заново. Р- случае определенног числа повторных подряд следующих сбоев (например, трех) фиксируется отказ, о чем указывается оператору, и ввод в ЭВМ завершается.

Перевод устройства из первого и

вТ Фого режимов в третий осуществля игг:- pyiHv j - ДЧОЬ; : мeнкI.; uepeK/iMut,:ei-; i-,-:i ui: Г, - и 10. IlepePOA из

n ;.; : : е/- - л I-, второй осущзс гзлч С-- л .мя/ическ - vp;- п рек;- :ч :.чии

:L г.1Я г/ ри .:..t 1 ;нии

% Н т1 10 сопг-lei :тву ,|Дем вводу ал..Г :;;; . ..- ИИ ,

ГТ

с- стоянии на упряш( - j /с : л (ства подается за- СИ I-. -.,г: из ЗЬМ, по которому блок 4 опроса 5 ядресов 5 грлнмцы

В и.

ИИ вход .T; еша1 гт}лГбчок 3 B;,.-;j a каналов, , ч срмлрова г ОЛЬ к ,i -iajioB . -PI/.-.: л , ejsi f UTV ч бл1.- 6 pb-jreji ::ния строк, 6j:ot .

2i ф|. )МИО )Ч :;, : аДОС- . Т И бЛ .ЧК 23 JII

, ;-. BJ i t ИИ я ,ержи;.аются f: исходном .-сг ч ti . 3 исходном состоянии б юк- 4 ч а;.оса :.Г | | . --сг и -рпый канал, фх.Ч ЧИгo jai t : i .TbvV i JT адрес первого 4;ii;u;,4, i рИ1 г 3V формирова f е ле , .-ргг/ср 83 в б аже 16, гчетчиблокр 21, счетчик 113 с ; riiiow;; ;км в нулевое тет ;:ый - ритг-ер 125 г. бло адини .о . Бктача сигналов по не производится

uvi У/ и Оь в : по1- е СОС 1Ч .:-;; Ичг ,

Kt ус 1 с новлен ч

KO, по ЧЫ .Т -уХУ 2 и

выкг-ГлУ 2 OTpOHCvaa

гп 4::ino,T «T установку коэф- S де. ьшя частоты в rr;i)«sii,oM .;омощь С пг:я: . иыбопа кас

5

c

l

0

п ,: . , Первоначально осуществляется подс-.itiT и запоминание количества строк в кадре информащ1И, настройка б|)(1ка 23 управления и далее - передача в ЭВМ кадра адресной информации. Ллч этого первым ключом 7 выход элемента И 11 подключается к первому в:;1:1ДУ элемента ИЛИ 12, ключс-м 8 выход ключей 9 подключается к входам группы формирователя 14 кодов и ключом 10, управляющий вход 25 устройс яа подключается к нулевому установочному входу триггера 17, единичному установочному входу триггера 18 и к седьмому входу блока 23 управления, В пер- BjK. двух режимах работы устройства передача в ЭВМ измерительной информации не производится, и поэтому подключать информационные входы 1 предлагаемого устройства к выходам измерительных установок или датчиков необязательно.

По сиг:1,.лу Ввод, поступающему из ЭВМ на управляющий вход 25 устройства в виде разрешающего потенциала,

осуществляется запуск блока 3, блока - и формирователя 5 триггер 1В уста- ьлв п-1вается в единичноJ СОСТОЯЯИР, а триггер 17 и счетчик 1 U п блоке П .праапгчшя устанавливаются я нуле- ;ip.j гостояш е. Зап . ешактцчй : отенииал t T l;т ;o о триггера 17 гоступа- : .-iii вхол элемсич я И 11 к второй рхол К.-1ЮЧСЙ 9, чем запрещается -пере- /лча через них сигналов г выхода син- кронизацил блока 3 выбора канаг:,,.в и с в;.кода формирователя 5. Кроме того, ,1прещающий потенц гал с прямого выхо- , :- триггера 17 пиодолжает удерживать Х ,ок 2 R исходном состо:1 -.ии. Единич уровень с инверсного выхода . ера

:, -,

7 поступая на шестой вход бг.о0

т1Ьг: : 5 гчетные входы 118 в lOKft 23 управления с гн;лл.5в с г; е- ГЬ - го .; че - T г/рТОГО Рс.УОДОБ блок. :

В де«:1Сг(Ия стр/--. Блок А опо;, а как :- . ЮЛ f.йрио1,ячески Р. определе но11 гг - v. te/ , H3 f ; ,v:i- юсти onpautvipiieT входные ...-.,.; .ом1-5утаторз ,. На входы ко- .; :р пс,;;ту11анл сигна. -г с. сс отвг т- -;.-,;, ;) ььг одов блока 3 rv..6opa кана- - итывание цифрового кода из

: л ых; регистров ко мутаторя 2 ппо- i .-.у.одиг 9 том с.пучя-:., когда р период i4, ,лу соседними cv THi; МИ опроса .;... э + из блока 3 поступает сигнал

19

управления записью информа105и во входной регистр.

Максимальная опорная частота tf, опроса каналов блоком 4 определяется допустимой скоростью ввода информаци в ЭВМ (пропускной способностью канал ввода-вывода ЭВМ). Частота сигнала, поступающего на второй вход блика 3 выбора каналов с выхода опроса последнего канала равна соответственно fj-fp/n где п - число канала устройства. Единичный уровень с выхода триггера 18 поступает на первый вход блока 16 выделения строк, открывая в блоке элементы И 87 и 88, на вход чтения-записи блока 22 памяти, который переводится в режим , и на первый вход блока 23 управления, В последнем этот единичный логический уровень проходит через элемент ИЛИ 126 и поступает на пятый выход 128 блока 23 и далее - на третий вхо блока 24 сравнения, блокируя его работу. Блок 16 вьщеления строк вьща- ет по третьему и четвертому выходам сигналы для подсчета количества стро в кадре, которые поступают на счетчик 118 блока 23 управления.

Подсчет количества строк в кадре производится таким образом, что по каждому сигналу с первого выхода блока 4 опроса каналов (выхода опроса первого канала) в счетчик 118 блока 23 добавляется единица, но если до вьдачи блоком 4 сигнала с п-го выхода (выхода опроса последнего канала) коммутатор 2 не вьдал синхрсюиг- нала сопровождения кода, единица из счетчика 118 блока 23 вычитается. В первом режиме устройства работа блока 22 памяти не важна. Подсчет количества строк в кадре прекращаетс при обнаружении границы кадра формирователем 15. Сигналом с выхода фор- М1грователя 15 триггер 17 устанавливается в единичное состояние, что характеризует начало второго режима работы устройства. Сигналом с прямого выхода триггера 17 разрешается работа адрес-блока 21, и через время, определяемое элементом 19 задержки, открывается элемент И 11 и ключи 9. Сигнал с инверсного выхода триггера 17 поступает на шестой вход блока 23 управления и запрещает передачу на счетные входы счетчика 118 блока.23 сигналов с третьего и чет-

20 рыходоп лока

1 fi пьиолгния

10

15

20

25

30

вертогч) строк.

Во втором режиме работы производится ввод в ЭВМ кадра адресной информации, контр(Х ть догтопериостн вводимого кадра и получение ттплона для контроля измерител1,ной ииформацим, Блок 4 продолжает опрос вхо;пп,гх регистров кoм f тaтopa 2, .мироратель 5 вырабатывает коды адресов каналом, которые через ключи 9 и 8 и ватель 14 кодов передаются на информационные выходы 27 устройства. Одновременно с передачей адресного кадра начинается запись его в блок 22 памяти, причем на время записи информа1и1И в блок 22 памяти блок 24 сравнения продолжает оставаться заблокированным сигналом с пятого выхода блока 23 управления. При этом на втором и третьем выходах блока 23 вьщаются нулевые логические уровни, которые поступают на формирователь 14 кодов и разрешают передачу через него кодов с входов группы. Адрес обращения к блоку 22 памяти формируется в блоке 21 счетчиком 97 чисел и счетчиком 98 строк,

Счетчик 97 блока 21 работает синхронно со счетчиком 67 формирователя 5 адресов каналов: на их счетные входы подается сигнал с выхода синхро- низа1щи блока 4 опроса каналов, Счет35 чик 98 блока 21 при записи информации в блок 22 памяти работает аналогично счетчику 118 блока 23 управления при подсчете количества строк в кадре, Очередным сигналом опроса первого канала с выхода блока 4, проходящим через блок 16 на шестой вход блока 21, в счетчик 98 блока 21 прибавляется единица, В счетчике 97 блока 21 содержимое изменяется от О,,,00 до п-1, и по каждому адресу, определяемому содержимым счетчиков 98 и 97, в блок 22 памяти записывается информация (нуль или единица) с выхода синхронизации коммутатора 2, т,е. бит информации.

Если до поступления в блок 16 выделения строк сигнала с выхлда опроса последнего канала блока 4 в коммутаторе 2 не сформировался хотя бы один

СЕ синхросигнал сопровождения кода, т.е. при данном адресе строки с выхода счетчика 98 блока 21 в блок 22 памяти не записалось ни одной единицы, то сигналом с третьего выхода блока 16

40

45

50

Btin.e.- : Ия , фпрмпруе пгм по чг- на.чу -.пр(1га пмлла, г-одер- жимоо -( .чл 21 умечр 1 ет- ся нл .НИЦ ,. 1 : П;( яге 14 блок 2 Ч И при г ян том адресе строк. nr iif: HeЛ1 НЯ ЗЯТГН ГЬ Х|1ТЯ PC ОЛИОЙ едИНИ. Ы,

то вьгчитлрп1 : (- ипицы и со,перж мпгс- с чет чикл 57Г1-.КЛ 21 tre пропс хо.чит. Длпее upoiTi- .r ги-нтсря- етгя так клк описано, Тлкчм : 6paTi M, в блоке. 22 ПЛМЯТИ нлклп:1иг;астся информация о наличии р.дииипл либо от утстьии нупь при ллмном гтдресл Г г ррки и чиглл син- хросигнллл сопровождения кода с хо,лл комт-1утятс1рл 2, Или, другими сло- ., роиг.ходи г злпоминание структуры кадр л ад1 еснон ииформатт.

Прскрлплется тапигл:, информации п блок 22 памяти при гранненин половины содержимого счетчика 118 блока 23 уп- раг ления с с одержи П П 1 гчетчика 98 блока 21, т.е. после передачи в ЭВМ полонины адресного кадра. Переключе- пио блока 22 памяти из режима записи в режим чтения осу1Г1ССТТ пяется сигь;а- лом с выхода BTOpoio триггера 18 в момент ус Т лномки последнего н нулевое , ,г - -.ciHj.e . Tpiii T er ус; гаг.; лГ чнается н 1-п.-:, р:-. о о : г.сгоячие с г гнадсм с nepi M- ; о ньглода fX ioK 3 упрлвленгя р,.;- ( .;иру: тг-. тг ,..-. cpsBHerfHs, адреса

строки, Сформяр:).;- ОГО П блоК€ 21,

с. ,ц.ч-)й с)/1,ержимсч Г) счетчика 11Я слоил 2 } упр;: I, ,

искпю гени формгроваиия в блоке 2 с:игн i. n LI-- ; лоА Ном сравнении кодов в .iPFib ф.-г миpo7Ja fия с1-1гнала ср гвиений пч,-; :р.н рет истр ii2, яапись в когорт ()MaiJHH с выхода четчи- га ) в ii п; оиг чпдьт(:я ло сигмл- лу оиГ -са lioc- i 4U:ro канала, 1)и,.( щег.,у Via ах д блокл iC3 л Jaitl ;.)мv пементо ; : ч.гл.ержкм Г Т ;яа 23 на .4;еня, Hec v:o/u -Moc пол:-чсиия в счс гчики 98 бл - ;: 21 деГ;с.тви7ельнии И1 .форма 1,ни . jlo;. |.-ранненио ч;;.} .икй- ет пг.и rit ,-,:м набс-г);: кС Э1|м|}щуте -- том деле ли, oitcni oi: - лстоть сшроса канале.:-, ксгда гапн .-.-. оч.;: едной е,и

НИ,д- . ::;ё-1 ; г: 93 бЛОКЯ 21 1.рИ.(ОДИТ

к сраннению лсло1 ; i ;/ т.чсс lU; из ОЛЯО7О и канялотз тгчфгтрмаииг: счггтана не оудег, и по rnrhajiy ciupoc - погле;:- него канала проилхсдит иычитание еди Ш11 ,. И г 4г.т-/ика 98 блока 21, : регистре 12 блока 23 с помочь.: элеме; та 1) эад йржки запись рС Г:--зрод 1ТС}1 по. того, по сигналу onpov

|;1Ми днего канала из содержимого .:ч( 1 - п-я 98 блока 21 происходит вы- чита1 ие единицы (либо не происходит 1 гчумле считывания информации хотя- .i ч: одного канала) . Таким образом, c:i ле}:жимое счетчика 98 равно коли- пс реданньгх. в ЭВМ строк кадра.

,и11ичньп 1 урорень с аыхода триггера 1Я поступает также на первьй вход шюка 16 выделения строк, запрещая ibLaa4y сигналов по третьему и четвер- Г ,-.му егс выходам и разрешая прохожде- 1ие иа его первый второй и пятый выходы сигналов с выходов триггера зЗ б. юка 16, с помощью которого при дальнейшей работе предлагаемого уст- poficTBa пр(исходит выделение строк в кадрах передаваемой п ЭВМ информатдии Сигн.алом с элемента 114 6j:c)Ka 23 управле1тя, который форми- (зуется при сравнении кодов в счетчиках 98 и 118 блоков 21 и 23 соответ- стпенно, триггер 117 блока 23 устанавливается в единичное состояние, единичный логический уровень с выхода 107 б/,ока 23 поступает на седьмой вхс Д блока 21 и разрешает прохождение сигналов с че7 вертого входа блока 21 на .-четный вход -1 счетчика 98 блока 21.

Передача второй половины кадра адресной .информации сопровождается сравнением ее структуры со структурой половины, записанной в блоке -2 - а№1ТИ. В аависимости от того, четное ил нечетное общее количество строк в кадре, информация о когор-ом хранится в счегчике 118 блока 23 уп- 1 анления, работа предлагаемого устройства различя. Если количество строк в кадре четное, т.е. ось симметрии в кадре проходит через строку (фиг.7а), то на выходе младшего разоя д.й счотчика 118 блока 23 имеется yjrr-„ Е этом случае центральная стро- . а С1Г1-1метрична самой себе и п/рсц.ются в ЭВМ без контроля, Тгм ая кл является единственной из мно- .j cTi;:d строк в кадре. На время пере- дл ч - I i центральной строки кадра . Л : 01-с B;jLXOAa блока 23 на третий fi .с;, йт:;ка 24 сравнен тя поступает .-,;: : ,1чки1й уровень, блолирукядий его | г. Ч ту. Начало передачи следующей -:.i(;iKif кадра характеризуется фор№;- рг;В ;-;:и .-м сигнала нл пятом выходе она t6 вь1деления ст .тх. Этот сигнал : т пает на четве-р ьп1 вход адресного блока 21 и умет,шлет лярес . и на единицу, (lI,кoнpe e к; o с -i гим с тг-- налом с в го; тго )дл блсм :: 1 fi рач- репается считывание из блока 2 г;л мяти, а сигналом с парного пухода блока 16, проходящим через бло,; 2Т, снимается блокнропкл рлботь: бло,, 2 i В последнем осушествляетог срл FJi nMiii: кода адреса, фор гирусмого н формиро- вателе 5, с коло содержащегос в счетчике 97 блокл 21, причеь ньиа- ча формировате-пем 5 стробиру- ется сигналом с Fibixnna сиихроиияаи.ии коммутатора 2, а адрес числа из счет чика 97 блока 21 поступает ия тлемен ты сравнения блока 2 при напичии ьм его первом входе едит.гп.-г.- , сигнала с выхода блока 22 памчти.

При сравнении ,.1 , :рес 1ьт:: кодов с второго вихода 2 Bt.i- дается нулевой сигна.и, а с третьего выхода - единичньй. При этом через форттровател, 14 кодов panp fnona пе-- редача кодов с с-го информаи,чонног-о входа. Окончание передачи строки характеризуется выдачей по ьт-ро -гу и пятому выходам 16 1улгв1|Гх сигналов, а по первому выходу плок,-; 15 единичного сигнала. При этом ед;;- яичным с первого ЕЫХОДЛ ка 16, прокодясгим через олок 23, блокируется работа блока 24 спаь.чсни Нулевь1М сигналом с второго вьп-;; 1а блока 16 запррги1е1ся рлбота бчока

22памчти. При поступг;онии спрд.укщс- го сигнала с выходл б.чока 16 IM четвертый вход блока 21 работа устройства продолжается так, как описано.

При передаче последней строк : .../,- ресного кадра на выходе счетчика 93 блока 21 сформируется код 0..,ПО. В этом случае триггер 117 в блоке 23 устанавливается в нулевое состояние. Нулевой сигнал с выхода 107 блока 23 поступает на седьм(лй вход блока 21 и разрешает прохождение в нем сигна-Г ов с четвертого входа 95 блока 21 на счетный вход счетчика 98 блока 21. Так как пртг перадлче 11ос. (граничной) строки кадра в ЭВМ в порядке возрастания передаются всех каналов, то прохождение кода адреса из счетчика 97 чисел блока 21 в блоке 24 сравненял строОяруется сигналом с ч твертсго вь ходл блока

23управления. Окончание ьерсдачи адресн-го кл;тп1 характртМ З- отся формированиям сиглллл пыходп ;и: ;-ро

lo 15

р .. Б зп .,,

о

5

0

Ь

ни злчии кгьчрпн блока i выбора каналон, К(1 | О11МЙ лe lt ит И 11, ключ 7 и элемент K llt 12 поступает на управ- рмход 26 устройства. По этому сигналу ЭНМ снимает разретлющий потенциал с выхода 25 устройства, а тлпррщл1П ;;ий потемпи-ч- т - с выхода элемента ИСК ЛЮЧЛКТЩЕК lUn 13 и устанавливает ycTpoficTBO в исходное состояи1 е.,

Если количество строк в кадре нечетное, т.е. ось си14метрии в кадре проходит между строками (фиг.7б), то на в;,глоде младшего разряда счетчика 118 блока 23 имеется единица. После переключения триггера 18 из единичного в нулевое состояние на первом выходе блока 16 форми1 уетсл сигнал, который поступает кп четвертый вход блог-а 23 и фо1)мирует на его третьем выходе нулевой сигнал. Этот сигнал поступает ;ia восьмой вход блока 21 и запре цает прохождение сигнала с четт тртого входа блока 21 на счетный вход счет 1ика 98 блока 21, Таким образом, сигнал с пятого выхода блока 16, формируемый при передаче следующей строки, не изме,няет содержимого счетчика 68 блока 21. Сравнение кодов 3 блоке 24 срл.пнеиия осуществляется так же, клк описано. По окончании ncpoдaч i строки нл первом выходе блока 16 формируется еди(а1чньп 1 сигнал, которы1 ; ггоступает на четвертый вход блока 23. Яа третьем выходе блока 23 rЬ lp пtpyется единичный сигнал, которым разрешается прохождение сигнала с четвертого входа блока 21 на счетный вход счетчика 98 блока 21. При передаче следующей строки сигналом с пятого выхода блока 16 содержимое счетчика 98 блока 21 уменьшается на единицу. Далее предлагаемое устройство работает так же, как при четном количестве строк в кадре.

Если симметричные адресные коды, поступающие в блок 24 сравнения, не равны, такую ситуацию считают следствием сбоя. Неравенство адресных кодоп в эталонном и формируемом в про- иессе ввода измерительной информации адресных кадрах может произойти из- за сбоев, вызывающих нарушение порядка записи информации во входные регистры каналов, либо порядка опроса укапанных регистров, что случайным образом изменяет порядок следования ко.;;оп в кадрах из еняет длину кадров и т.д. При неравенстве кодов в блоке

75

139792Д

2А ия его втором выходе формируется единичный сигнал, а на третьем - нулвой, вследствие чего на информационные выходы 27 устройства поступает код сбоя из формирователя 14 кодов. Код сбоя НС принадлежит множеству кодов адресной и измерительной информации. Кроме того, единичный сигнал с второго выхода блока 24 поступает на второй вход элемента ИСКЛЮЧАЮЩЕЕ Ш1И 13, и, так как на первый в;:од так же поступает единичньй уровень с уггравляющего входа 26 устройства, на рьсходе элемента формируется нулевой уровень, которым устройство переводится в исходное состояние.

Единичным сигналом с первого выхода блока 16, проходящим через блок 23 нл третий вход блока 24, работа последнего блокируется. На второй В1-ГХОД блока 24 поступает нулевой уровень, и на выходе элемента ИСКЛЮ- ЧАЩЕЕ ИЛИ 13 формируется единичный сигнал, по которому устройство начинает работу эаново так, как описано, факт возникновения сбоя в устройстве фиксируется в счетчике 134 блока 24 сравнения. При воэникновекии подряд некоторсто наперед заданного коли- ; -гтва сбоев .я первом выходе блока Z t формируется единичшдй сигнал, кпторьп поступав на второй вход . элемента И.ПИ 12 и с 1)ыхода последнего - на уиравляюгчий выход 26 устройсва. ЭВМ, получив этот сигнал, снима- ет разрешающий потенциал с управляющего вxoдLЧ 25 устройства. Оператору выдастся сообщение о возникшей ситуации с помощью узла 131 индикации блока 24 сравнения. Сигналом с выхода синхронизации блока 3 выбора каналов который поступает на четвертый вход блока 24 сравнения, счетчик 134 блока 24 устанавливается в нуль. Если послй возникновения сбоя хотя бы оди кадр информации передан в ЭВМ, то ит формация о сбое сбрасывается.

Передача адресного кадра заканчивается, когда с выхода синхронизации блока 3 выбора каналов через элемент И 11, ключ 7 и элемент ИЛИ 12 на уп- рааляющий выход 26 устройства поступает сигнал, по котороьгу ЭВМ снимет разрешающий потенциал с управляющего входя 26 устройства, вследствие чего предлагаемое устройство переводится в исходное состояние.

Затем начинается третий режим работы устройства - передача в ЭВМ кад

26

0

5

0

5

i

3540 45

ров измерительной информации, для чего первым ключом 7 вьгход дешифратора 6 подключается к первому входу элемента ШШ 12, ключами 8 информационные выходы коммутатора 2 подключаются к входам группы формирователя 14 ко-« дов, ключ 10 размыкается, а информационные входы 1 устройства подключаются к выходам измерительных установок или датчиков. Коэффициенты дапе- ния в блоке 3 выбора каналов не изменяют. В режиме ввода измерительной информации адресная информация в ЭВМ не вводится. В исходном состоянии на управляющий вход 26 устройства подается запрещающий потенциал, по которому блоки устройства поддерживаются в исходном состоянии. По сигналу Ввод поступающему из ЭВМ на управляющий вход устройства в виде разрешающего потенциала, осуществляется запуск блоков устройства. Так как ключ 10 разомкнут, триггер 18 продолжает оставаться в нулевом состоянии, триггер 17 - в единичном, а в счетчике 118 блока 23 хранится информация о количестве строк в кадре информации. Цифровые коды от измерительных установок или датчиков поступают на информат онные входы 1 устройства. Запись кодов измерительной информации в регистры коммутатора 2 осуществляется по сигналам, поступающим с выходов блока 3 выбора каналов на входы коммутатора 2. Блок 4 опроса каналов в определенной последовательности опрашивает входные регистры коммутатора 2. При наличии информации блок 4 опроса каналов осуществляет считывание ее, и с информационного выхода коммутатора 2 цифровой код поступает на входы формирователя 14 кодов. Цифровой код на выходе коммутатора 2 сопровождается синхросигналом, по которому в формирователе 5 адресов каналов формируется адрес канала, из которого произведено считывание информации.

Блок 16 вьщеления строк с первого, второго и пятого выходов выдает сигналы, управляющие работой блока 21, блока 22 памяти, блока 23 управления и блока 24 сравнения. Сравнение ко- 55 дов адресов, формируеьонцс в формирователе 5, с кодами адресов чисел, фор-« мируемымн/в блоке 21 и стробируемыми информацией из блока 22 памяти, начинается с первой строки кадра изме0

50

рительнс й информации. (; начп ;. ; передачи каждг с.псдуюни ч строки ; ,;г.-;а в счетчик ЧР строк бппка 21 приоав- ляется единица, 1. г;тг| ггередакл r-vio BHFia кадра, то проиг.ходит и ;|.неиие режима работы считчика 98 6.;iO:: i 2 на р(-.перси иый, и с на-мпом пррелггчи к;1и- д,ой спедуилцей строгсп с-. Цержи - jc его уменьшается ил едшшду, riocjn; ric редачи пос.пе.диен строки рслдр, ; ин;10р- мации п счетчике 98 бдо ка 2; содержится нул1, вследствие чего лиг нялом с второго выхода блока 23 упрлплпиия рехим работы счетчика 98 блока 21 изменяется на прямой, и т.д.

В остальном работа fi; o::on предлагаемого устройства ипогта в ЭВМ кадров H3MeptyTp-p ; ич4юрма- 1У1И происходит анал г-,ь, 10 о- м)те блоков в режиме ввода адрес1 Г)Г о кадра. Прекращается ввод кадров из ;с:ритель- Н(1Й информйпии по С ЛИ иалу окоичсИ ия 1чвода с вьосода емрнта : , поступающему в ЭВМ - у1:ря ля|п. 1(г1 п да 26 устройства. Сигнал oKoH4a)f;in ввода формируется либо дегилфратором 6 при обнаружени;; г ослр;и им коца окончания ПВОД6 л поток; к.л ijt ; -(Гтельной ннфо; ма И 1 с нфсг малиоп- ного выхода комг- у атора 2, .njitjr; бл;:- ком 24 сравн . лия njin фиксиро , : r:t:r подряд HeKOTOi cru наперед я.п..ииго о Ч-Чсла сбоев. Но этому ссгр-ллу прек1)ар:.:1ет вяод и усрит ;ль ;Гг Hu.j. i p-- мадии и залрещающим с1-;Г1;ало ил. управляющем 25 усгройства лсрй- РОДИТ еги Е и-;ход ое г остояние.

Н частном случае, когда коэффициенты деления опорной частот.-. г ..,о- га одинаковы во весу :;лзл :К, г, t. сигналы упразле1гил гчапигь.- - .о гкодные регистры KONfi iyTaTCva 2 каналов форм-г- руются блоком 3 рыборя. кял апов с одинаковой частотой, кал,р ииформа,ип состоит из ОДНО г.тпоки, содержая ей рар.чое кт. И1(ест с: Kaifa.noB количество чисел. тако. кадре с заранее известной структурой СВОЙС1 вг) симметрии вы- рождаетс .я. В этом частном для оОеспечення работоспособности предлагаемого устройства в счетчикг. 118/ блока 23 улрав; ения, в ко.ором пос .78 оконч.чн.;я nepiioi ) рс .тимя рабг, ;ы уст- poi CTTia содоржт .чтя ко.п О..,0, при- нудчте.льно формярур .ся ко.; П...011, -1 далее работ,-, стрс-.йсткш пр;-л.олж ае;, ™ с:-: так, i,4s опргг-ко, В такой ситуацш )теред; а ;1ьформ;,1ШИ в Э1 ;М г ;1-:: 1 одит0

5

0

,

О

Ь

0

5

ся Kri.up. uiH, г остояиугмтт из нескольких I n цаннс м с:1учае из трех) элементар- iibix однострочных кадров.

Запись D память ЭВМ адресных кадров и кадров измерит(:1аьной и)1форма -ЧИН производится по одинаковой программе. После ввода в память ЭВМ кадров измерительной инф.:1р.апии, последняя сортируется по принадлежности соответствую1то1м источникам (каналам) с помощью введенного в память ЭВМ проверенного на достоверность адресного кадра. В процессе сортировки производится анализ измерительной ин- формащ™ с целью обнаружения кодов сбоя. При обнаружении кода сбоя последующая сортировка от места сбоя производится с начала кадра. При необходимости кадры со сбоями можно исключить из дальнейшей обработки, Номера таких кадров определяются как ближайшее большее целое число от числа D/d, где D - порядковый номер кода сбоя от начала массива измерительной информации, d - длина кадра.

Таким образом, контроль правиль- :ос1Ч1 ал,рГ Г.нот о кадра, основанн .гй на |.р.оГи:тти ого с имметрии, и проверка струт.туры перс,.иаом1 х в ЭВМ кадров и ельиоГ информации повьпиают ;т,о.;ток- 1:)Ность вводимой с помоп1ью гт11. ai- ioro устройства информации . Г ycipofi -.Tpe сбсйиые ситуа1у1и диаг- )остиру1отся, места сбоев в вводимом массиве помечаются кодами сбоев, а части кадров после обнаружения в них сбоев в ЭВМ не вводятся. Последующая сортировка дает правштьное разделение информации по каналам. При необходимости неполные кадры, полученные из-за сбоев, можно исключить из дальнейшей обработки.

Формула изобретения

2413

стартего ря-чряпа выходов группы бпока опроса кяналор соелинен с первым входом Рлокч каналов, выход блока опр ic a каналов г,оединен с первым вхо- дгм формирователя адреса канала, ингЬормационние выходы коммутатора соелинены с входами де т1фратора и Г холами первой группы ключей первой группы, выход дешифратора соединен с первым входом первого ключа, стро- бирующпй выход коммутатора соединен с втопым входом формирователя адреса кл нала, отличающееся тем, что, с целью повышения надежности устройства, в него введены элемент И, элемент ИЛИ, элемент ИСКЛГО- ЧЛЩЕЕ ИЛИ, второй ключ, вторая группа ключей, формирователь кодов, формирователь границы кадра, блок вьще- леяия строк, два триггера, два элемента задержки, блок формирования адреса, блок памяти, блок управления, блок сравнения, выход блока выбора

каналов соединен с первым входом эле- 25 входом памяти, первый выход

liCHra И, выход которого соединен со .торым входом первого ключа, выход которого подключен к первому входу -л-- м нгл , выход которого являет- л-,,.-.;г,: ВЬКОДОМ УСТРОЙСТВО,

Г плы ф р 1 чяБл-гч ля адреса канала : -. с гхпдами первой группы ,. - ггчрй -п п-рой rfiynaM, выходы ключей г опой ; руппь гог-днкеиы с ркодами

I 1 OpvlH nvnnh :-, Г: : ГГ:Й ПерВОЙ ГрУППЫ

.1 ,.xoA -iMi I ервои группы блока срав- чения, Bb.:KGj:,fc. ключяй первой группы ../единены с входами группы формиро- рягапя , .В1--гчоды которого являют ..ч ичформс 11монньг и Бпкодам; устройсг й |. aei:Bbri-; РЛ:ОД зломентд И -К-ШОЧАЮ- 1гК :&i ГР :.:лд второго ключа являютс :т 1ра 1ляющим ьход м устроистиа, выход .).(та ИСК, :р/ , ШШ подключен k р- : )аму 1;.-.оду фoг ipoвaтeлк адре- , Kpjici.ri3, 1-1- ОДУ блока о/фоса кана- .ПО:, ;;тот):ч-)у ..)ду блока выбора кано. -1--.И и второму нходу блока формирова- ;iH4 i; ;peca. прямой ВЫУ.ОД первого грг-;;-т чра с.о: ;ди1 ел с первьм входом :;riKii фо -ИрованиЕ адреса и через nt.i9 ..3l s;7CMPHT задержки с входами и горой гру. ключей второй группы jf -гг.-.С Ым входом элемента И, выход .т.- псгс.го разряда выходов группы блока ciapoca К Тналок соедин 2Я с входом форм роря reji.q грани11Ь кадра, вторым пходом блока выделения строк и пятым вкодогл Слока у1 раяле1шк, групп

24

30

формирователя границы кадра соединены с выходами группы блока выбора каналов, выход формирователя границы кадра подключен к входу установки в 1 irepBoro триггера, вход установки в О которого, вход установки в 1 Е:торого триггера и седьмой вход блока управления соединены с выходом второго ключа, инверсный выход первого триггера соединен с шестым входом бло ка управления, вход установки в О второго триггера соединен с первым выходом блока управления, выход второго триггера соединей к первому входу блока управления, входу чтения- записи блока памяти и первому входу блока выделения строк, третий вход которого соединен с выходом младшего разряда выходов группы блока опроса каналов, стробирующий выход коммутатора соединен с четвертым входом блока выделения строк, и через второй элемент задержки - с информационным

0

5

0

5

блока выделения строк соединен с четвертым входом блока управления, третий вход которого и пятый вход блока формирования адреса соединены с третьим выходом блока вьдрления строк, второй вход блока управления и шестой нход блока формирования адреса coL-лдлнены с четвертым выходом блока вьщелтения строк, второй выход которого соединен со стробирующим входом Злок.а памяти, выходы второй группы блока формирования адреса соединены г входами группы блока управления и адресными входами первой группы блока памяти, второй и третий выходы блока упр авления подключены соответственно к седьмому и восьмому входам блока формирования адреса, четвертый вход которого подключен к пятому выходу блока выделения строк, третий вход лока формирования адреса подключен к выходу блока опроса каналов, выходы первой группы блока формирования адреса соединены с адресньми входами второй группы блока памяти и входами вторг:й rpyrsynj блока сравнения, выход блока памяти соединен с первым входом блока сравнеютя, второй и третий входи -которого соединены соответственно : fйертьм и пятым выходами блока -Тф--рления, четвертый вход блока сравнения соединен с выходом блока каналов, первый яыход блока сряане1тия подключен к второму входу

элемента ИЛИ, второй выход - i пгиро- му входу элемента H C;KJII04AR)r(j-;R или ,и первому Р ..оду формироваткля кодов, третий вьгхо/; - к i3 ; i :ioi y лхопу форгги- рователя кодов.

11СКЛЮЧЛН)|11КК ИЛИ грушг, вторые вхолы третьего и четвертого элементор И и четвертого элемента И. ПТ-ИЕ яапяются естым ;:,х/том блока, г ьгход второго элемента И С(1олимен г первым входом пятого элемент;) И, выход которого соединен с входом сметного тригтера, выход которого является третьттм вьг- ления содержит регистр, триггер, эле- Q ходом блока, выход триг геу а является

5

ЧТО

о т л : бпок vripan-мент задержки, элемент Ш01, триггер, элемент НЕ, пять элементов И, четыре элемента ШП1-НЕ, счетчик, две группы элементов ИСКЛЮЧЛ 01:;ЕЕ 1Ш1, информационные входы регистра, входы первого элемента ИЛИ-ИЕ и входы первой группы элементов ИСКЛЮЧАЮЩЕЕ ШШ первой групп(1 являются пxoдa r группы блока, выходы регистра соединены с вxoдa rи первой группь ; -ieiip-HTOB ИСКЛЮЧАЮЩЕЕ ИЛИ второй гпу,:,1Ь, выходы которых соединен.г с входами второго элемента ИЛИ-НЕ, выход которого соединен с входом установки в t триггера и яв.г яет1-.я первым ;1ьгходом блока, выход первого элемеи.та iL IH-iiE соединен с входом установки О триггера и является четвертым вькодом (тока, выходы олементо;) lICK iOiiAKiriEL-; ИЛИ nepBoi группы соьлннечы с i :oдa ч- третьего элемента IL IH-iih, выход которого соединен с псрв1; и рходаки первого и второго ,И, вход элемента I-LTTi является noiJBvn- входог- Олока, второй Г(Х 1Д эиемймта ИЛИ соединен с вь хо;гом первого элемента. И, первые ВХС1ДЫ третьего if четвертого эпe eнтoв И являются соответственно вторым и третьим входам блока, -вьтход третьего элемента И сгн ди- иен с сум -гируюпптм входом счптчнка, вьтход четвертого элемента И гоединен с вычитающим входом сч(,, вьосод которого соединен с входом элемента НЕ и вторЬ; - входом орого элемента И, выход элемент,- НК соедиг ен с вторым входом перчзсго элемента И и пер- входом четвертого элемента вьЕКод которого соединен с яа- писи счетчигсл, вхо;; н;1чально;г установки .го подключен к ипп р логической единиц), выходы -rpynni T счетчика соединень с Еходаш; грлдтпы тетпертого элемента ИЛИ-НЕ и соответствуюшпш

входагда второй группы элсмэнтовpj. является вторьг вьосодом блока.

вторым выходом блока, второй вход пятого элемента И и третий вход элемента И.ПИ является четвертым входом блока, выход элемента ИЛИ является пятым

выходом блока, вход сброса счетчика является (ым входом блока, вход элемента задержки является пятым входом блока, выход элемента задержки соединен с входом записи регистра,

3, Устройство по П.1, отличающееся тем, что блок выделения строк содержит элемент задержки, элемент IE, элемент ИЛИ, два триггера, пять элементов И, первые входы

первого и второго элементов И, элемента ИЛИ и вход, элемента НЕ являются перпыг-1 входом блока, выход элемента iiE соединен с первыми входами третьего и четвертогг) элементов И, вход

установки п (V первого триггера и вход установки в Г второго тригге- ::а являются четвертым входом блока, пход установки в 1 первого триггера и второй вход BTopoi o элемента И являнтгся третьим входом б.чока, выход второго элемента И является четвертым вькодом блока, выход пепвого триггера соединен с первым входом пятого элемента И, выход которого соединен с

Бторьм входом первого элемента И,

вьгход которого является третьим выходом блока, вход элемента задержки является вторым входом блока, выход элемента задержки соединен с вторым

входом пятого элемента И и входом установки в О второго триггера, прямой и инверсный выходы которого соединены соответственно с вторыми входами третьего и четвертого элемснтов И, выход четвертого элемента И является первым вьжодом блока, выход третьего элемента И соединен с вторым входом элемента 5-ШИ и являетсл пятым Еькодом блока, вьгход элемента НЯИ

II.N

9ut.i

Ось симметрии

Ось симттрии

фиг 8

139792/,

С18 Пп Ш 4f О О О О

liZ.il

(рцгЮ

Фаъ.12

(Pu2.il

| Многоканальное устройство для ввода информации | 1984 |

|

SU1265783A1 |

Авторы

Даты

1988-05-23—Публикация

1986-10-01—Подача