./

Изобретение относится к цветному телевидению, в частности к декодирующим устройствам с дафровой обработкой сигнала.

Цель изобретения - повышение устойчивости работы частотного детектора за счет исключения сбоев.

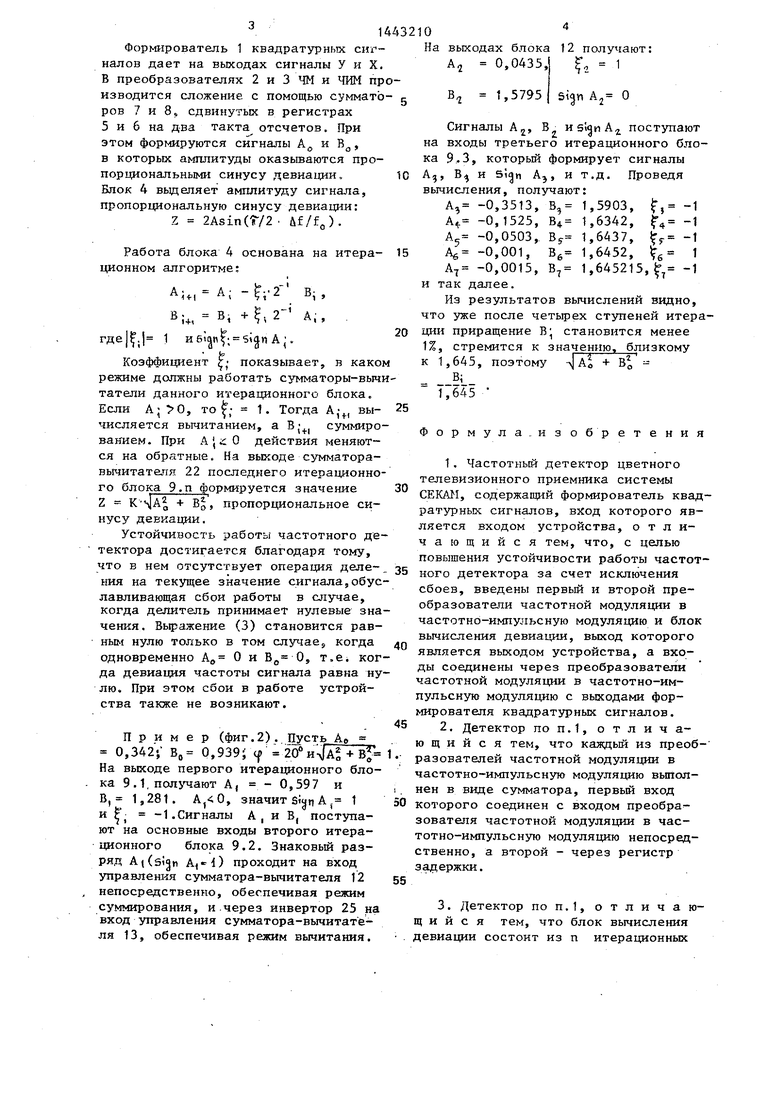

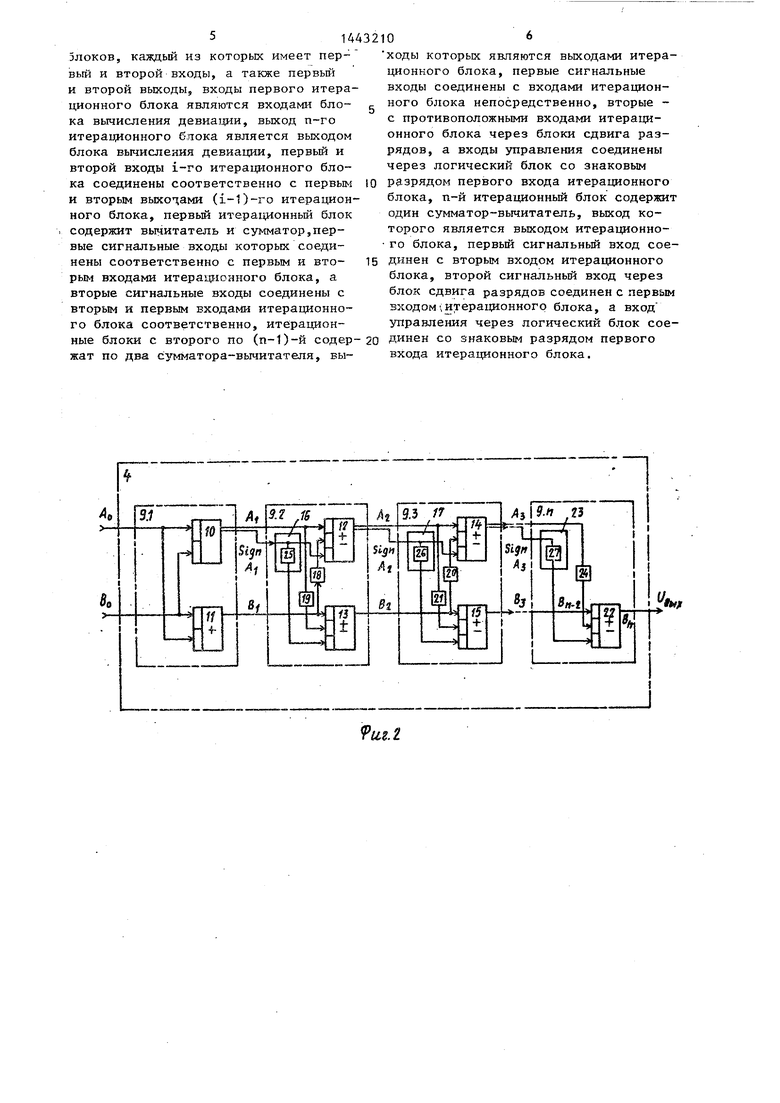

На фиг,1 представлена структурная электрическая схема частотного да- тектора цветного телевизионного приемника системы СЕКАМ; на фиг.2 - схема блока вычисления девиацииJ на фиг.З - АЧХ предлагаемого устройства

Частотньй детектор цветного теле- визионного приемника системы СЕКАМ содержит (фиг.1) формирователь 1 квадратурных сигналов, первый преобразователь 2 частотной модуляции (ЧМ) в частотно-импульсную модуля- цию (ЧИМ), второй преобразователь 3 ЧМ и ЧИМ, блок 4 вычисления девиа- 1ХИИ. Преобразователи 2 и 3 ЧМ в ЧИМ содержат регистры 5 и 6 задержки и сумматоры 7 и 8. Формирователь 1 квадратурных сигналов может быть выполнен в виде двух последовательно соединенных регистров задержки на такт и вычитателя, входы которого со .единены с входом первого регистра и выходом второго регистра, соединение регистров является первым выходом формирователя квадратурных сигналов, а выход вычитателя - вторьм выходом.

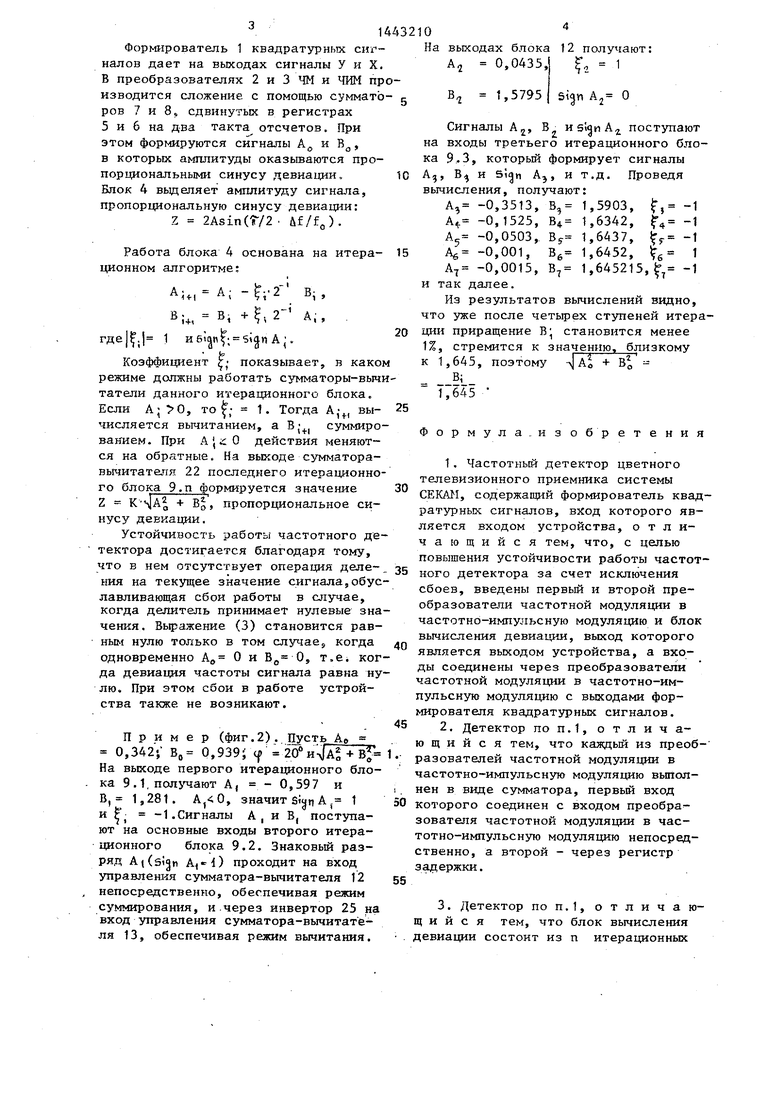

Формирователь 1 квадратурных сигналов может быть также вьтолнен в ви де нерекурсивного фильтра, содержащего п последовательно соединенных регистров задержки на такт и два сумматора, выходы которых являются, выхо дами формирователя. Входы первого сумматора соединены через формирователи весовых коэффициентов (умножители) с выходами нечетных регистров задержки, а выходы второго сумматора - через формирователи весовых коэффи- циентов с выходами четных регистров задержки Блок 4 вычисления девиации может быть выполнен в виде двух квадраторов, сумматора и вычислителя квадратного корня. При этом в качестве квадраторов и вычислителя квадратного корня могут использоваться постоянные запоминающие устройства (ПЗУ). Лучшие результаты дает итерационный блок (фиг.2), который содержит п итерационных блоков 9.1...9.п. В состав первого блока входят вычи- татель 10 и сумматор 11. Блоки со

второго по (п-1)-й содержат по два сумматора-вычит теля 12, 13 и 14, 15, логические блоки 16 и 17 и блоки 18-21 сдвига разрядов. Последний п-и блок содержит только один сум- матор-вьпштатель 22, логический блок 23 и блок 24 сдвига разрядов. Блоки 18 - 21, 24 осуществляют сдвиг данных в ту или иную сторону на заданное число разрядов. Выполнение логических блоков зависит от особенностей применяемых сумматоров-вьмита- телей в части входов управления режимом работы (суммирование или вычитание) . В простейшем случае блоки 16, 17 и 23 содержат по одному инвертору 25, 26 и 27.

Частотный детектор работает следующим образом.

Для пояснения работы устройства рассмотрим дискретизированные ЧМ синусоидальный (У) и косинусоидаль- ньм (X) сигналы. В каждом из сигналов вьщеляют по два отсчета с интервалом в два такта

yi(2)-Asin 2ir(fo +uf)(t:Ft)l, Х1(2),-Асо5Г2 и-( +uf)(t-),

где о 1/4f д - период тактового сигнала.

Находят выражения для сумм этих отсчетов: АО У1 + У2, В XI + Х2. После преобразований получают: АО(ВО) i2Asin(cos)27(fo+ &)tisin(fr/2 л Модуль этого выражения пропорционален синусу от девиации и с учетом того, что в системе CEKAI-I uf f

Z Л|АО + Bt 2Asin(r/2.)

AiTuf/f,

(1)

или

if fo /Air -J AO+ B

(2)

Таким образом, вычисление + Bg соответствует демодуляции цифрового ЧМ сигнала. На фиг.З дано поле допуска 1-1 для АЧХ аналогового частотного детектора СЕКАМ. График II фиг.З соответствует выражению (3).Он с большим запасом укладывается в поле допуска. Если необходима более высокая линейность АЧХ, то после определения модуля производится вычисление функции F arcsin(Z/2A) с помощью ПЗУ. Тогда АЧХ становится строго линейной (график III фиг.З).

Формирователь 1 квадратурных сигналов дает на выходах сигналы У и X. В преобразователях 2 и 3 ЧМ и ЧИМ производится сложение с помощью суммато- ров 7 к 8, сдвинутых в регистрах 5 и 6 на два такта отсчетов. При этом формируются сигналы А и В, в которых амплитуды оказьшаются пропорциональными синусу девиации, Блок 4 выделяет амплитуду сигнала, пропорциональную синусу девиации: Z 2Asin(ir/2

&f/fo).

Работа блока 4 основана на итерационном алгоритме;

1 I

В

15

U(

-ГГ2- В;, В, -f , 2- Ai,

ГДе|.| 1 А; .

Коэффициент - показывает, в каком режиме должны работать сумматоры-вычи- татели данного итерационного блока. Если А; 0, то ; 1. Тогда А числяется вычитанием, а В нанием. При

20

А, -0,3513, В, 1,5903, f, -1 А. -0,1525, 8 1,6342, -1 А -0,0503, В5- 1,6437, ;- -1 Аб -0,001, Вб 1,6452, lf-g 1 A-j -0,0015, В 1,645215, -1 и так далее.

Из результатов вычислений видно, что уже после четырех ступеней итерации приращение В становится менее 1%, стремится к значению, близкому

к 1,645, поэтому

5 1,645

лГл

R - BO

,Ч. sbi- 25 ;, суммиро- действия меняютФормула изобретения

ся на обратные. На выходе сумматора- вычитателя 22 последнего итерационного блока 9.П формируется значение 30 Z + BO, пропорциональное синусу девиации.

Устойчивость работы частотного детектора достигается благодаря тому.

t. Частотньй детектор цветного телевизионного приемника системы СЕКАМ, содержащий формирователь квадратурных сигналов, вход которого является входом устройства, отличающийся тем, что, с целью повышения устойчивости работы частот- что в нем отсутствует операция деле-, 35 ного детектора за счет исключения

сбоев, введены первый и второй преобразователи частотной модуляции в частотно-импульсную модуляцию и блок вычисления девиации, выход которого является выходом устройства, а входы соединены через преобразователи частотной модуляции в частотно-имния на текущее значение сигнала,обуславливающая сбои работы в случае, когда делитель принимает нулевые значения. Выражение (3) становится равным нулю только в том случаеJ когда 40 одновременно АО О и 5 О, т,е. когда девиация частоты сигнала равна нулю. При этом сбои в работе устройства также не возникают,

45

Пример (фиг.2). Пусть АО

0,342, Вд 0,939J cj 20 + 1. разователей частотной модуляции в На выходе первого итерационного блока 9.1, пол1 чают А, - 0,597 и В, 1,281. А,0, значит А , 1 и -1.Сигналы А , и В, поступают на основные входы второго итерационного блока 9.2. Знаковый разряд А ((sign ) проходит на вход управления сумматора-вьиитателя 12 непосредственно, обеспечивая режим суммирования, и.через инвертор 25 на вход управления сумматора-вычитате- ля 13, обеспечивая режим вычитания.

пульсную модуляцию с выходами формирователя квадратурных сигналов.

2. Детектор по п.1, отличающийся тем, что каищый из преобчастотно-импульсную модуляцию выпол- I . нен в виде сумматора, первый вход 50 которого соединен с входом преобра зователя частотной модуляции в частотно-импульсную модуляцию непосредственно, а второй - через регистр задержки.

55

3. Детектор по п.1, отличающийся тем, что блок вычисления девиации состоит из п итерационных

На выходах блока 12 получают:

А 0,0435,

1

В.

,5795

А

, О

Сигналы Aj, В. и51ЧпА, поступают на входы третьего итерационного блока 9.3, который формирует сигналы

А,, B,j и

Э

И т.д.

Проведя

gC

5

0

вычисления, получают:

А, -0,3513, В, 1,5903, f, -1 А. -0,1525, 8 1,6342, -1 А -0,0503, В5- 1,6437, ;- -1 Аб -0,001, Вб 1,6452, lf-g 1 A-j -0,0015, В 1,645215, -1 и так далее.

Из результатов вычислений видно, что уже после четырех ступеней итерации приращение В становится менее 1%, стремится к значению, близкому

к 1,645, поэтому

5 1,645

лГл

R - BO Формула изобретения

разователей частотной модуляции в

пульсную модуляцию с выходами формирователя квадратурных сигналов.

2. Детектор по п.1, отличающийся тем, что каищый из преобразователей частотной модуляции в

частотно-импульсную модуляцию выпол- нен в виде сумматора, первый вход которого соединен с входом преобра зователя частотной модуляции в частотно-импульсную модуляцию непосредственно, а второй - через регистр задержки.

.

55

разователей частотной модуляции в

3. Детектор по п.1, отличающийся тем, что блок вычисления девиации состоит из п итерационных

Злоков, каждый из которых имеет первый и второй входы, а также первый и второй выходы, входы первого итерационного блока являются входами бло- ка вычисления девиации, выход п-го итерационного блока является выходом блока вычисления девиации, первый и второй входы i-ro итерационного блока соединены соответственно с первым и вторым (i-l)-ro итерационного блока, первый итерационньш блок содержит вычитатель и сумматор,первые сигнальные входы которых соединены соответственно с первым и вто- рым входами итерационного блока, а вторые сигнальные входы соединены с вторым и первым входами итерационного блока соответственно, итерационные блоки с второго по (п-1)-й содер жат по два сумматора-вычитателя, вы ходы которых являются выходами итерационного блока, первые сигнальные входы соединены с входами итерационного блока непосредственно, вторые - с противоположными входами итерационного блока через блоки сдвига разрядов, а входы управления соединены через логический блок со знаковым разрядом первого входа итерационного блока, п-й итерационный блок содержит один сумматор-вычитатель, выход которого является вькодом итерационно го блока, первый сигнальный вход соединен с вторым входом итерационного блока, второй сигнальньй вход через блок сдвига разрядов соединен с первым вход ОМ , итерационного блока, а вход управления через логический блок соединен со знаковым разрядом первого входа итерационного блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотный детектор | 1988 |

|

SU1580523A1 |

| Частотный детектор | 1988 |

|

SU1663780A1 |

| ЦИФРОВОЙ ДЕМОДУЛЯТОР СИГНАЛОВ С ЧАСТОТНОЙ МОДУЛЯЦИЕЙ | 2012 |

|

RU2522039C1 |

| Частотный детектор декодера СЕКАМ | 1985 |

|

SU1317692A1 |

| Цифровой фазовый детектор | 2018 |

|

RU2723445C2 |

| Цифровой частотный детектор приемника СЕКАМ | 1983 |

|

SU1238270A1 |

| ЦИФРОВОЕ УСТРОЙСТВО РАЗДЕЛЕНИЯ СИГНАЛОВ ЯРКОСТИ И ЦВЕТНОСТИ В ДЕКОДЕРЕ СИСТЕМЫ СЕКАМ | 1991 |

|

RU2014755C1 |

| ЦИФРОВОЕ УСТРОЙСТВО РАЗДЕЛЕНИЯ СИГНАЛОВ ЯРКОСТИ И ЦВЕТНОСТИ В ДЕКОДЕРЕ СИСТЕМЫ СЕКАМ | 1991 |

|

RU2012163C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ СИГНАЛОВ С ДВУХКРАТНОЙ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 1991 |

|

RU2007886C1 |

| УСТРОЙСТВО РАЗДЕЛЕНИЯ СИГНАЛОВ ЯРКОСТИ И ЦВЕТНОСТИ В ДЕКОДЕРЕ СИСТЕМЫ СЕКАМ | 1991 |

|

RU2012164C1 |

Изобретение относится к цветному телевидению. Цель изобретения - по- вьшение устойчивости работы частотного детектора за счет исключения сбоев. Устр-во содержит формирователь 1 квадратурных сигналов, преобразователи 2 и 3 частотной модуляции в частотно-импульсную модуляцию и блок вычисления (БВ) 4 девиации. Из квадратурных сигналов формирователя 1 преобразователи 2 и 3 формируют сигиалы, в которых амгоштуды оказываются про- пор19 ональными синусу девиации. Затем БВ 4, работа кбторого основана на итерационном алгоритме, вьщеляет зту амплитуду. Устойчивость работы устр- ва достигается тем, что в нем отсутствует операция деле(шя на текущее значение сигнала, обусловливаннцая сбой работы в случае, когда делитель принимает нулевые значения. 2 з.п. ф-лы, 3 ил.S

1ПА

Н

250ff60

е.З

f.

| АСТА ELECTPONICA, 1984, № 3-4, р | |||

| ПЕЧНОЙ ЖЕЛЕЗНЫЙ РУКАВ (ТРУБА) | 1920 |

|

SU199A1 |

Авторы

Даты

1988-12-07—Публикация

1986-06-19—Подача