Изобретение относится к цветному телевидению, в частности к декодирующим устройствам СЕКАМ с цифровой обработкой сигнала.,

Целью изобретения является уменьшение искажений выходного сигнала частотного детектора и расширение функциональных возможностей для сиг- налов с девиацией выше стандартной. JQ

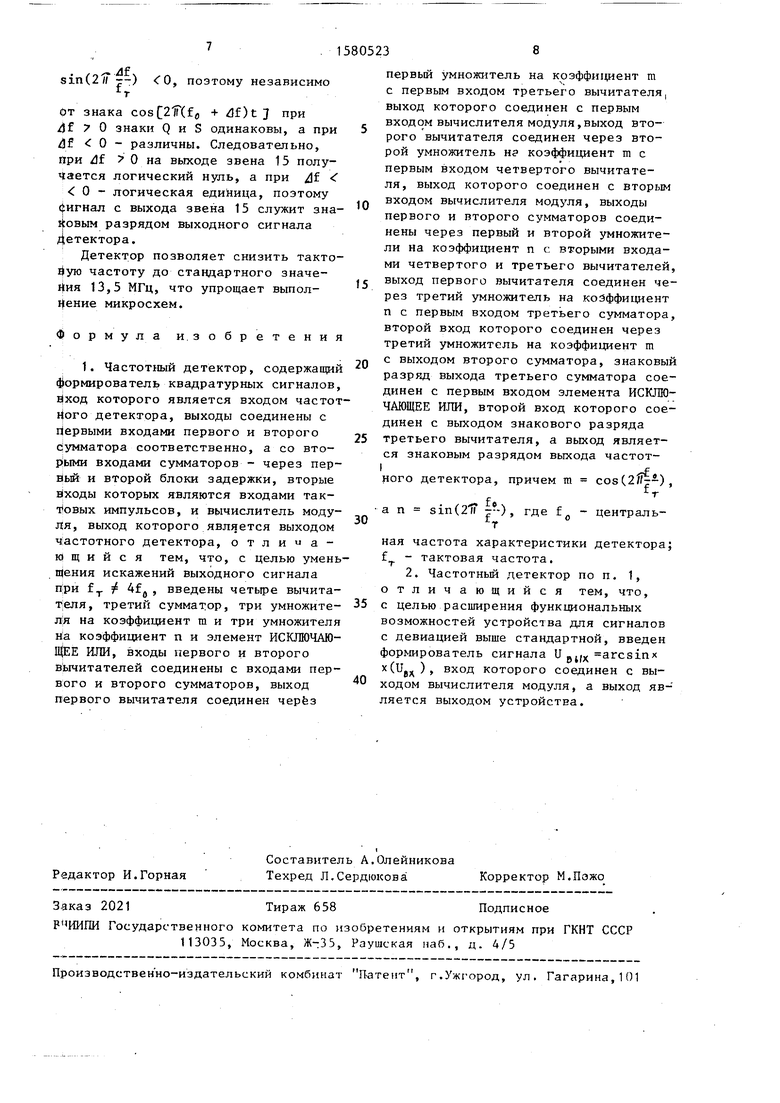

На чертеже представлена электрическая структурная схема частотного ;детектора.

Детектор содержит формирователь 1 квадратурных сигналов, первый 2 и j второй 3 блоки задержки, первый 4 и второй 5 сумматоры, вычислитель 6 модуля, умножитель 7 на коэффициент п, вычитатель 8, умножитель 9 на коэффициент п, вычитатель 10, умножи- 20 тель 11 на коэффициент ms вычитатель 12, умножитель 13 на коэффициент т, вычитатель 14, логическое звено ИСКЛЮЧАЮЩЕЕ ИЛИ 15, сумматор 16, умножитель 17 на коэффициент п, умно- 25 житель 18 на коэффициент m и блок 19 линеаризации.

Детектор работает следующим образом.

На вход детектора поступает цифро- ™ вой ЧМ сигнал U 8 Asin 21Г (f 0 + + /df)t , где f девиация частоты. С помощью формирователя 1 из ЧМ сигнала получают его ортогональные .составляющие Y и Х. При идентичности сигнала Y входному сигнал

35

X

Acos 2 Tf(f + f)tj

40

Блоки 2 и 3 задерживают сигналы YЈ и X 2 на два периода тактовой частоты f T ТУ Задержанные и незадержанные сигналы Y t; Y г и X ,; X г складываются и вычитаются в сумматорах .с 4 и 5 и вычитателях 12 и 14, образуя сигналы

С Y, + D X ,+ X t; Е ,;

F - X,- Хг

Вычитатели 8 и 10 определяют разности R m-F - n-С и S mE - nD, где т - коэффициенты умножителей 11 и 13, an- коэффициент умножителей 7 и 9.

Вычислитель 6 определяет модуль сигналов S и R:

U

2 + R4

,

JQ

j 20 25

™

35

40

.с

50

Сумматор 16 вычисляет сигнал Q m-D + п Е. Знаковый разряд сигнала Q(singQ) и знаковый разряд сигнала S(singS) поступают на входы логического звена ИСКЛЮЧАЮЩЕЕ ИЛИ 15. Выходной сигнал этого звена является знаковым разрядом выхода частотного детектора. Если частотный детектор применяется в декодере СЕКАМ, где девиация частоты относительно невелика, выходной сигнал снимается с выхода вычислителя 6.

В случае двух применений, когда девиация частоты велика, между выходом вычислителя 6 и выходом устройства включен блок 19 линеаризации в видп ПЗУ (ROM), запрограммированный на функцию U Arc sin (U flx ) .

Детектор демодулирует ЧМ сигнал без искажений при произвольном выборе значения тактовой частоты Јт.

На входе и выходе блока 2 выделяются сигналы, сдвинутые на два такта:

Y1 Asin 2 fT(f, + /Jf)(t - 5) ; Y2 Asin 2 1T(f ft + df)(t + ) .

На выходе сумматора 4 выделяется сигнал

С Y, + Y2 2Asin С27Г (f0 + + 4f)t J cos f 2 (f0 + 4f)J 2Asin 2 (f0 + jf)(2T«

) cos(2f)-sin() sin (2(4-) ,

гт гт тт tr

На выходе вычитателя 12 формируется сигнал F Xt - X2 2A-sin 21Г (f0 +

+ jf)tj sin 2 (f fl + ЛО 2Asiu 2 (f0 + /jf)t J tsin (

)cos(21f ) + cos ().

M

xsin (21Г |-)J .

t-r

-тi

На входы вычитателя 8 поступают сиг,

налы ra F и п-С. Пусть m соз(21Г--))

т

a n sin(2 ). Тогда

т

R mF - nC 2A (f e + df)t

df,

, df,

mncos(2lT Si) + m2 sin(2 -)J - тЈT

- 2A siit 27Г (f e + d f)tj - mncosx

x(2jT|-) - (2lT)J 2A tTrT

sin 2 IT (f 0 + df)t (m2 + n2)

sin(2f4Ј).

rr

3f,

Составляющие cos(21T---), нарушаю r

щие работу частотного детектора, компенсировались. -Аналогично находим сигнал S на выходе вычитателя 10, который равен

S mE - nD 2A.COS 2fT(fe +

+ 4f)t (m2 + n2)sin().

гт

f Вычислитель 6 определяет модуль сигналов S и R:

и «их Vs2 + R2- 2А (m2 + n2)x х sin() .

Детектор может работать при разных значениях Јт, при этом коэффициенты умножителей 7, 9, 11 и 13 долж30

ны соответствовать условиям

m cos(); n sin( § -) . t .14

Тем самым при произвольном значении

При Јт 13,5 МГц и К 1 га

тактовой частоты Јт выходной сигнал 35 n 0,91. частотного детектора пропорционален Сигнал на выходе звена 15 опреде- синусу девиации Jf и не содержит чле- ляется девиацией частоты входного

сигнала. На входы сумматора 16 посту- нов cos (2f--), создающих искажения. пают сигналы пЕ и mD. Результирующий

40 сигнал Q равен

Для декодера СЕКАМ замена аргумента его синусом не создает недопустимой погрешности. Максимальная девиация частоты 4f в сигнале СЕКАМ составляет 280 кГц. Пусть Јт 13,5 МГц. Тогда аргумент синуса

О 28 (/. 2 у 0,13031 рад. Значе50

x sin(2IT --) гт

ние sin (f sin(0,135) 0,12994. Отличие синуса от его аргумента составляет

(n inii n 900/ nnпоступают на входы логического звеi2ilЈ2Јl I 2ilfZZ2L:122 о, 28%. на ИСКЛЮЧАЮЩЕЕ ИЛИ 15. При af 0

U & I j J-j 1

55

Известно, что допустимая нелинейность демодуляционной характеристики частотного детектора СЕКАМ для девиа15805236

ции +280 кГц не должна превышать t5%. Предлагаемый детектор создает нелинейные искажения в 17 раз меньше допустимых, поэтому блок 19 линеаризации для декодера СЕКАМ не требуется и с достаточной точностью можно принять

10

,df

URb(x YS2 + R2 ЛА(Г()-К

или

Jf

fr 4A f(m2 + n2) К

S2

R2.

Если девиация частоты велика, на выходе вычислителя 6 модуля включают линеаризирующее ПЗУ. Тогда

. ,0 dfs + R2

8in(2. f- 5Х(-г --гу;

0-4f . . Г VS2 + R

j it -.- А ч т n I ------------- I

Z fr Arcsin 2A (ra2 + n2)J

t. fT , . Г Vs2 + R2 1 jf -.ArcSln --- -;--rTJ.

Детектор может работать при разных значениях Јт, при этом коэффициенты умножителей 7, 9, 11 и 13 долж

ны соответствовать условиям

m cos(); n sin( § -) . t .14

40 сигнал Q равен

Q пЕ + mD 4A(m2 + n2) cos 21Г

(fe + 4f)t Jcos (2). 45Т

Знаковый разряд сигнала Q, а также знаковый разряд сигнала

50

S 4A(ms + n2) cos 2(f0 +4f)tjx

x sin(2IT --) гт

cos() OHsin() 0, тт

при 4f 0 cos(.) 0 и

т

8in(2lT) r

0, поэтому независимо

от знака cosЈ2lT(fe + 4f)t J при /}f 7 0 знаки Q и S одинаковы, а при дЈ 0 - различны. Следовательно, при 4f О на выходе звена 15 получается логический нуль, а при Af. Г

0 - логическая единица, поэтому Сигнал с выхода звена 15 служит зна- йовым разрядом выходного сигнала детектора.

Детектор позволяет снизить такто- Йую частоту до стандартного значения 13,5 МГц, что упрощает выполнение микросхем.

Формула изобретения

1. Частотный детектор, содержащий формирователь квадратурных сигналов, вход которого является входом частот rtoro детектора, выходы соединены с Первыми входами первого и второго сумматора соответственно, а со вторыми входами сумматоров - через первый и второй блоки задержки, вторые йходы которых являются входами тактовых импульсов, и вычислитель моду- Ля, выход которого является выходом частотного детектора, отличающийся тем, что, с целью уменьшения искажений выходного сигнала при fr 4fft, введены четыре вычита- теля, третий сумматор, три умножителя на коэффициент m и три умножителя на коэффициент п и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, входы первого и второго вычитателей соединены с входами первого и второго сумматоров, выход первого вычитателя соединен через

5

0

5

0

5

0

первый умножитель на коэффициент m с первым входом третьего вычитателя, выход которого соединен с первым входом вычислителя модуля,выход второго вычитателя соединен через второй умножитель н коэффициент m с первым входом четвертого вычитателя, выход которого соединен с вторым входом вычислителя модуля, выходы первого и второго сумматоров соединены через первый и второй умножители на коэффициент п с вторыми входами четвертого и третьего вычитателей, выход первого вычитателя соединен через третий умножитель на коэффициент п с первым входом третьего сумматора, второй вход которого соединен через третий умножитель на коэффициент m с выходом второго сумматора, знаковый разряд выхода третьего сумматора соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом знакового разряда третьего вычитателя, а выход является знаковым разрядом выхода частотного детектора, причем m cos(2//--),

т

a n sin(2Tr 7), где f - централь- т

ная частота характеристики детектора; f - тактовая частота.

2. Частотный детектор по п. 1, отличающийся тем, что, с целью расширения функциональных возможностей устройства для сигналов с девиацией выше стандартной, введен формирователь сигнала U pt(x arcsinx x(UBX), вход которого соединен с выходом вычислителя модуля, а выход является выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотный детектор | 1988 |

|

SU1663780A1 |

| Частотный детектор цветного телевизионного приемника системы СЕКАМ | 1986 |

|

SU1443210A1 |

| Частотный детектор декодера СЕКАМ | 1985 |

|

SU1317692A1 |

| Устройство для детектирования частотно-модулированного сигнала | 1985 |

|

SU1261080A1 |

| Цифровой фазовый детектор | 1986 |

|

SU1467785A1 |

| ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР | 2013 |

|

RU2541147C1 |

| МНОГОЧАСТОТНЫЙ ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР | 2013 |

|

RU2534938C1 |

| Устройство для измерения отношения сигнал/шум | 1988 |

|

SU1575138A1 |

| Цифровой частотный детектор приемника СЕКАМ | 1983 |

|

SU1238270A1 |

| Индикаторное устройство | 1990 |

|

SU1744471A1 |

Изобретение относится к технике цветного телевидения. Цель изобретения уменьшение искажений выходного сигнала частотного детектора и расширение функциональных возможностей для сигналов с девиацией выше стандартной. Детектор содержит формирователь 1 квадратурных сигналов, блоки задержки 2 и 3, сумматоры 4 и 5, вычислитель 6 модуля, умножитель 7 на коэффициент N, вычитатель 8, умножитель 9 на коэффициент N, вычитатель 10, умножитель 11 на коэффициент M, вычитатель 12, умножитель 13 на коэффициент M, вычитатель 14, логическое звено 15 ИСКЛЮЧАЮЩЕЕ ИЛИ, сумматор 16, умножитель 17 на коэффициент N, умножитель 18 на коэффициент M и блок линеаризации 19. С помощью формирователя 1 из частотно-модулированного сигнала получают его ортогональные составляющие, а посредством сумматоров 4 и 5 и вычитателей 12 и 14 - сигналы, представляющие собой суммы и разности ортогональных составляющих. Вычитатели 8 и 10 формируют разности полученных сигналов, причем каждый вводится с некоторым коэффициентом. Вычислитель 6 определяет модуль, пропорциональный синусу девиации. Знаковый разряд выходного сигнала определяется суммированием в звене 15 по модулю двух знаковых разрядов соответствующих сигналов. Выбор соответствующих значений коэффициентов умножителей обеспечивает уменьшение искажений выходного сигнала. Для повышения линейности используется блок линеаризации 19, запрограммированный на функцию ARCSIN, что расширяет область применения частотного детектора для сигналов с большой девиацией. 1 з.п. ф-лы, 1 ил.

| Устройство для детектирования частотно-модулированного сигнала | 1985 |

|

SU1261080A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-07-23—Публикация

1988-05-13—Подача