e/off

13

ВыхЛ

4ib

00 Од

;о

00

Изобретение относится к иьшульс- ной технике и может быть использова- во в устройствах обработки информации в частности в измерительной технике.

Цель изобретения - расширение функхшональных возможностей за счет задания длительностью входного импульса длительности и частоты следования импульсов выходной последовательности.

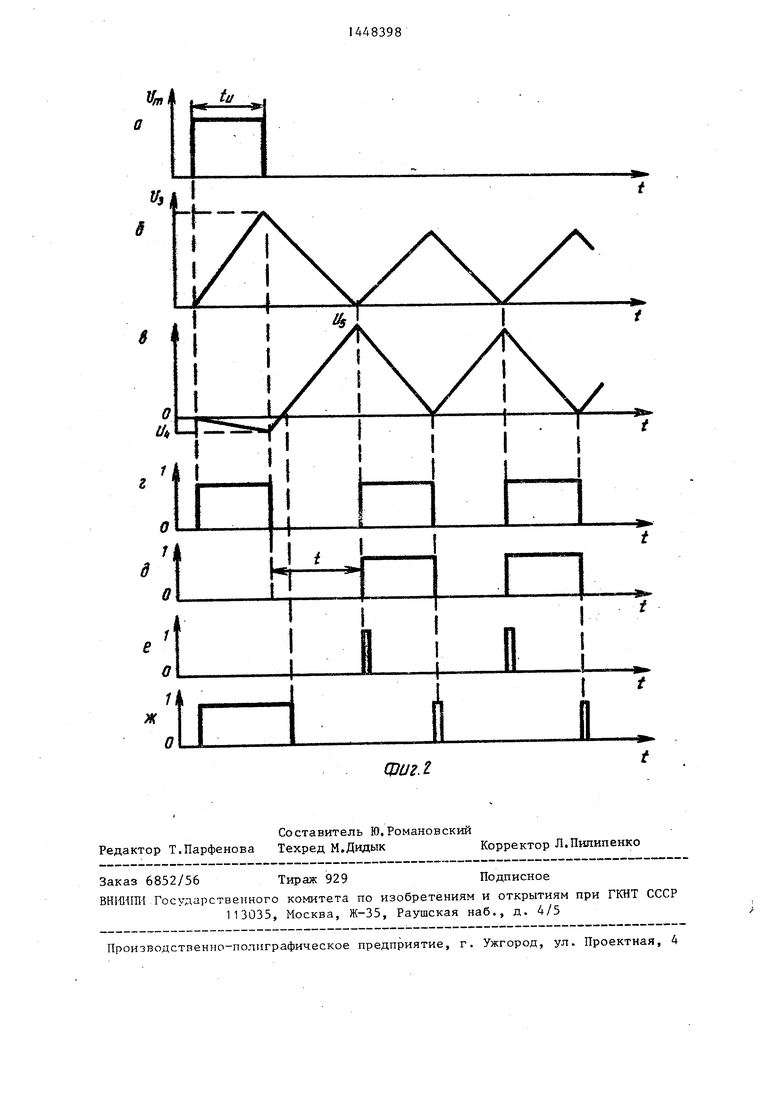

; На фиг.1 представлена функциональ- Йая схема предлагаемого генератора;

первого 3 и второго 17 компараторов, неинвертируилцие входы которых соединены с общей шиной. Выход первого компаратора 3 соединен с вторым входом логического элемента ИЛИ I1 и с установочным входом второго триггера 13. Выход второго компаратора 17 соединен с прямым входом логического элемента ЗАПРЕТ 9 и со сбрасывающим входом триггера 13.

Синхронизированный генератор работает следующим образом.

Пусть в произвольный момент време

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь экстремумов периодического сигнала в постоянное напряжение | 1989 |

|

SU1674002A1 |

| Преобразователь амплитуды импульсов в постоянное напряжение "ГАЛС | 1985 |

|

SU1401389A2 |

| Преобразователь экстремумов периодического сигнала в постоянное напряжение "Галс-7 | 1987 |

|

SU1442926A1 |

| Устройство для измерения температуры | 1978 |

|

SU771485A1 |

| Адаптивный дельта-модулятор со слоговым компандированием | 1991 |

|

SU1785078A1 |

| Аналого-цифровой преобразователь | 1982 |

|

SU1056452A1 |

| Синхронизированный генератор | 1979 |

|

SU851756A1 |

| Устройство для автоматической компенсации емкостного тока однофазного замыкания на землю | 1982 |

|

SU1107214A1 |

| Система передачи и приема дискретной информации | 1983 |

|

SU1119184A1 |

| Преобразователь амплитуды импульсов в постоянное напряжение "Галс | 1984 |

|

SU1413540A2 |

Изобретение может быть использовано в устройствах обработки информации, в частности в измерительной технике. Цель изобретения - расширение функциональных возможностей - достигается за счет того, что длительность и частота следования выходных импульсов задаются длительностью входного импульса. Генератор содержит сумматоры 1 и 15, компараторы 3 и 17, интеграторы 2 и 16, ключи 5-8 и 14, элемент ЗАПРЕТ 9, источник 10 опорного напряжения, злемент ИЛИ 11, триггеры 12 и 13, дифференцирующий элемент 4, входную шину 18. Введение сумматора 15, интегратора 16, компа-. ратора 17, триггеров 12 и 13, ключа 14 в генератор позволяет получить длительность импульсов, равную длительности входного импульса ty, а п е- риод следования импульсов, равный 2 t|. 2 ил. . СЛ

на фиг.2 - временные диаграммы, пояс-is ни на входную шину 18 поступает импульс амплитудой и и длительностью.

кяющие его работу.

Генератор содержит первый сумма- Top I, первый интегратор 2, первый Компаратор 3,дифференциру«нда1й эле- 1ент 4, первый 5, второй 6, третий 7,20 кающий первый 5 и второй 6 ключи. При четвертый 8 ключи, логический элемент этом первый 2 и второй 16 интеграто- SAIffET 9, источник 10 опорного напряжения, а также логический элемент ИЛИ 1, первый 12 и второй 13 тригге| ы, пятый ключ 14, второй сумматор 25 гический элемент ИЛИ 11, поступает на 15, второй интегратор 6, второй ком- устанавливающий вход первого тригге- паратор 17. Первый вход логического элемента ИЛИ И, запрещающий вход логического элемента ЗАПРЕТ 9, вход дифференцирующего элемента 4, первые 30 Входы первого 1 и второго 15 сумматоров подключены к входной шине 18.

Выходы логического элемента ИЛИ 1I - и логического элемента ЗАПРЕТ 9 подключены соответственно к устанорочно- 35 коэффициент передачи первого сумму и сбрасывающему входам первого матора 1, равным плюс I. Четвертьй триггера 12. Прямой и инверсный выхо- ключ 8 остается разомкнутым, а коэф- да первого триггера 12 соединены с управляющими входами третьего 7 и четвертого 8 ключей соответственно. 40 Второй вход первого сумматора 1 непосредственно, а второй вход второго сумматора 15 через пятый ключ 14 соединены с выходом источника 10 опорного напряжения. Управляющие входы пер-45 яого I и второго 15 сумматоров соответственно через третий 7 и четвертый 8 ключи соединены с общей шиной.

ty (фиг.2а). С переднего фронта входного импульса на дифференцирующем элементе 4 форм1фуется сигнал, замыры устанавливаются в нулевое начальное состояние (2б,в).

Входной и шyльc, проходя через лора 12. В то же время входной импульс запрещает прохождение сигнала через логический элемент ЗАПРЕТ 9 к сбрасывающему входу первого триггера 12. Первый триггер 12 устанавливается в единичное состояние (фиг.2г).Сигнал с его прямого выхода замыкает TpeTiril ключ 7, который устанавливает тем сафициент передачи второго сумматора 5 при этом равен минус 1. Во время действия входного импульса пятый ключ 14 размыкается. В итоге на выходе первого сумматора 1 напряжение U равно

и,

Е + и

ь

где Е - напряжение на выходе источника 10 опорного напряжения. Напряжение на выходе второго сумматора 15 и равно

Выходы первого I и второго 15 сумматоров подключены к входам первого 2 и второго 16 интеграторов, установочные входы которых соответственно через первый 5 и второй 6 ключи соединены с общей шиной. Управляющие входы первого 5 и второго 6 ключей под- ключены к выходу дифференцирующего элемента 4. Выходы первого 2 и второго 16 интеграторов подключены соответственно к инвертирукщим входам

кающий первый 5 и второй 6 ключи. При этом первый 2 и второй 16 интеграто-

ty (фиг.2а). С переднего фронта входного импульса на дифференцирующем элементе 4 форм1фуется сигнал, замыкающий первый 5 и второй 6 ключи. При этом первый 2 и второй 16 интеграто-

ры устанавливаются в нулевое начальное состояние (2б,в).

Входной и шyльc, проходя через логический элемент ИЛИ 11, поступает на устанавливающий вход первого тригге-

коэффициент передачи первого сумматора 1, равным плюс I. Четвертьй ключ 8 остается разомкнутым, а коэф-

ра 12. В то же время входной импульс запрещает прохождение сигнала через логический элемент ЗАПРЕТ 9 к сбрасывающему входу первого триггера 12. Первый триггер 12 устанавливается в единичное состояние (фиг.2г).Сигнал с его прямого выхода замыкает TpeTiril ключ 7, который устанавливает тем коэффициент передачи первого сумматора 1, равным плюс I. Четвертьй ключ 8 остается разомкнутым, а коэф-

фициент передачи второго сумматора 5 при этом равен минус 1. Во время действия входного импульса пятый ключ 14 размыкается. В итоге на выходе первого сумматора 1 напряжение U равно

коэффициент ора 1, равным ч 8 остается

и,

Е + и

ь

коэффициент передачи первого сумматора 1, равным плюс I. Четвертьй ключ 8 остается разомкнутым, а коэф-

где Е - напряжение на выходе источника 10 опорного напряжения. Напряжение на выходе второго сумматора 15 и равно

Ul -Un,.

Таким образом, в течение времени действия входного импульса первый интегратор 2 интегрирует напряжение U (фиг.26), а второй интегратор 16 - напряжение (фиг.2в). На выходе первого компаратора 3 напряжение при, этом соответствует О (фиг.2е), а на выходе второго компаратора 17 . 31448398

(фиг.2ж). Второй триггер 13 сбро 1

шен, сигнал на выходе генератора соответствует О (фиг.2д).

К моменту окончания входного импульса на выходе первого интегратора 2 напряжение достигает значения U

и,

и,- t4 Е + ,

t

ы

где

-Л постоянная времени первого интегратора 2.

Напряжение на выходе второго интегратора 16 достигает значения U

Ul-t4.

-и.

D,

2

- А-где

1, - постоянная времени второго интегратора 16.

После окончания входного импульса сигнал с выхода второго компаратора 17 проходит через логический элемент ЗАПРЕТ 9 и сбрасывает первый триггер 12. При этом третий ключ 7 размыкается, а четвертый ключ 8 замыкается. Соответственно изменяются на противоположные коэффициенты передачи первого 1 и второго 15 сумматоров. Пятый ключ 14 замыкается. В итоге напряжение на выходе первого сумматора 1 равно минус Е, а на выходе второго сумматора 15 - плюс, Е. Таким образом, напряжение на выходах первого 2 и второго 16 интеграторов после окончания входного импульса начинают меняться в противоположных к предьщу- пщм напряжениям (фиг.26, в).

Время, за которое напряжение на выходе первого интегратора 2 уменьшается до нуля, определяется из услоВИЯ

и.

1;Г

0.

Подставив в выражение (3) выражение (1), получаем

Е + и,

E-t

7

О,

отсюда

t t , + t

Urn

За это время напряжение на выходе второго интегратора 16 возрастает до значения Uj

E-t

и,

и, +

(5)

10

15

,

20

25

30

35

40

45

50

55

Подставив в выражение (5) выражения (2) и (4), получаем

г. b l

и.

U,,,.t4

(6)

,,,- 4.

1 1.

После перехода напряжения на выходе первого интегратора 2 через нуль на выходе первого компаратора 3 появляется сигнал, соответствую1ций 1 (фиг.2е). Этот сигнал устанавливает первый 2 и второй 13 триггеры в единичное состояние (фиг.2 г,д). Соответственно на противоположные меняются коэффициенты передачи первого 1 и второго 15 сумматоров. Напряжения на выходах первого 2 и второго 16 интеграторов начинают меняться в противоположных и предыдущем направлениях (фиг.2б,в).

Дпительность этого состояния генератора продолжается до тех пор, пока напряжение на выходе второго интегратора 16 не достигнет нуля (фиг.2ж). Это время определяется из условия

и 5 - -Ц Q (7 ч

Подставив в выражение (7) выражение (6), получаем

t ty.

За это время напряжение на выходе первого интегратора 2 достигает значения

т, ,

- е - ,

Далее происходит сброс первого 12 и второго 13 триггеров, изменяются на противоположные коэффициенты передачи первого 1- и второго 15 сумматоров. Таким образом генератор переходит в автоколебательный режим. При этом длительность импульсов на выходе генератора равна длительности входного импульса t, а период следования равен 2ti,.

Анализ выражения (4) показывает, что при постоянной длительности входных импульсов задержка выходной последовательности линейно зависит от амплитуды входных импульсов.

Таким образом, длительность и частоту следования импульсов выходной последовательности генератора можно задать длительностью одиночного входного импульса. Так как длительность импульсов выходной последовательноети равна длительности входного импульса, генератор можно использовать как устройство задержки одиночного импульса с возможностью периодического его повторения. Все это достигается за -счет введения в генератор логического элемента ИЛИ, двух триггеров, ключа, сумматора, интегратора и компаратора и новых связей. В ре- зультате функциональные возможности синхронизированного генератора по сравнению с прототипом расширяются.

Формула изобретения

Генератор импульсной последовательности, содержащий первый сумматор, первый интегратор, первый компаратор, четыре ключа, логический элемент ЗАПРЕТ и источник опорного на- пряжения, причем вход дифференцирующего элемента и первый вход первого сумматора подключены к входной шине, а второй вход первого сумматора подключен к выходу источника опорного напряжения, управляющие входы первог и второго ключей подключены к выходу дифференцирующего элемента, один вывод первого ключа соединен с установочным входом первого интегратора, отличающийся тем, что, с целью расширения функциональных возможностей за счет задания дпительнос тью входного импульса длительности и частоты следования импульсов выход- ной последовательности, в него введены логический элемент ИЛИ, первый и второй триггеры, пятый ключ, второй сумматор, второй интегратор и

5

0 5 0 g

второй компаратор, причем первый и второй сумматоры выполнены со знако- . переменным коэффициентом передачи, управляющие входы которых соответственно через третий и четвертьй ключи соединены с общей шиной, первый вход второго сумматора, управляющий вход пятого ключа, первый вход логического элемента ИЛИ и запрещающий вход логического элемента ЗАПРЕТ подключены к входной шине, второй вход второго сумматора через пятый ключ соединен с выходом источника опорного напряжения, один вывод второго ключа соединен с установочным входом второго интегратора, а вторые выводы первого и второго ключей и неинверти- рующие входы первого и второго компаf

раторов подключены к общей шине, выходы логических элементов ИЛИ и ЗАПРЕТ подключены соответственно к установочному и сбрасывающему входам первого триггера, прямой и инверсньш выходы которого подключены соответственно к управляющим входам третьего и четвертого ключей, выход первого компаратора соединен с вторым входом логического элемента ИЛИ и с установочным входом второго триггера, выход второго компаратора соединен с прямым входом логического элемента ЗАПРЕТ и со сбрасывающим входом второго триггера, выход которого одновременно является выходом генератора, выходы первого и второго сумматоров соединены с инвертирующими входами первого и второго компараторов через первый и второй интеграторы соответственно.

V/я

| Устройство задержки импульсов | 1981 |

|

SU970665A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Синхронизированный генератор | 1979 |

|

SU851756A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1988-12-30—Публикация

1987-04-23—Подача