Изобретение относится к импульсной технике и может использоваться для измерения амплитуды сигналов, максимального и минимального значения напряжения од- нополярных периодических сигналов любой полярности, минимального и максимального значения напряжения двухполярных периодических сигналов.

Цель изобретения - повышение точности преобразования при малых уровнях входного сигнала.

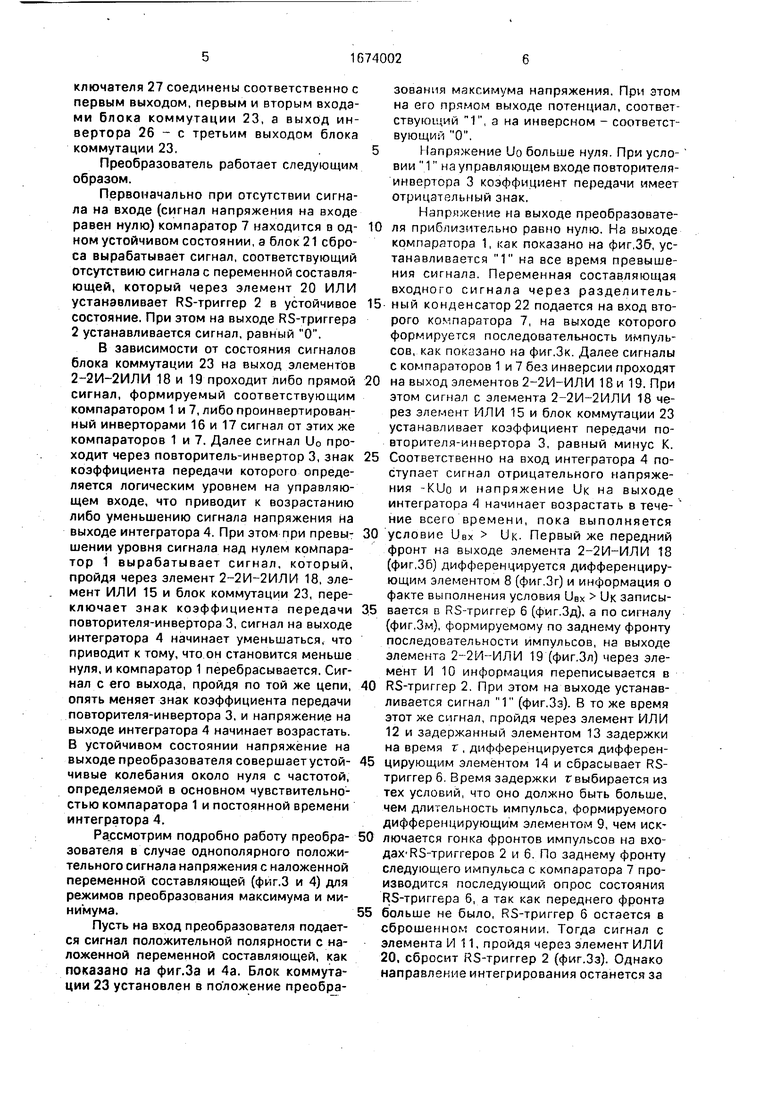

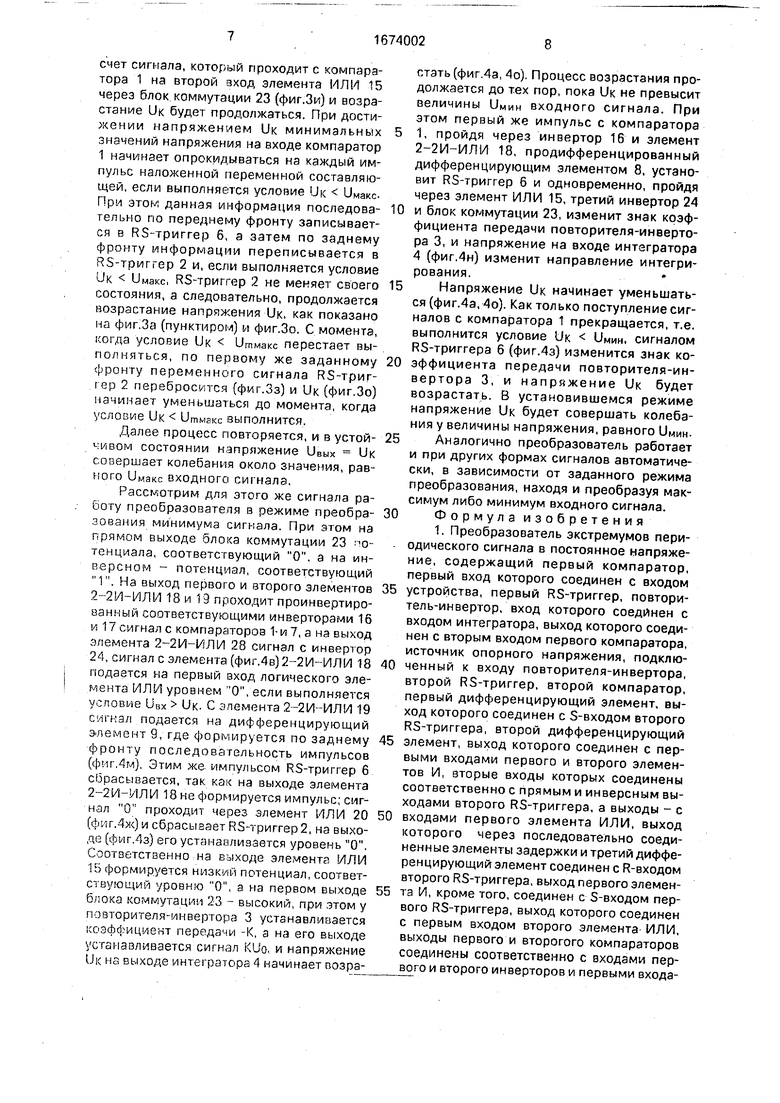

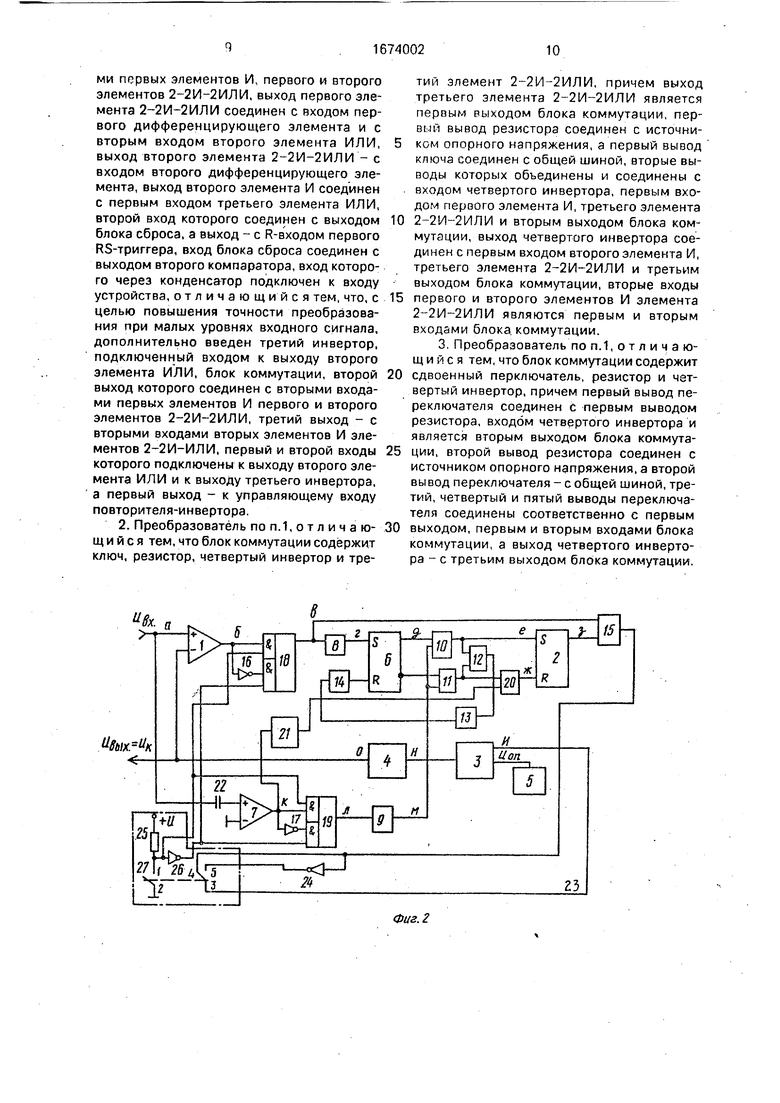

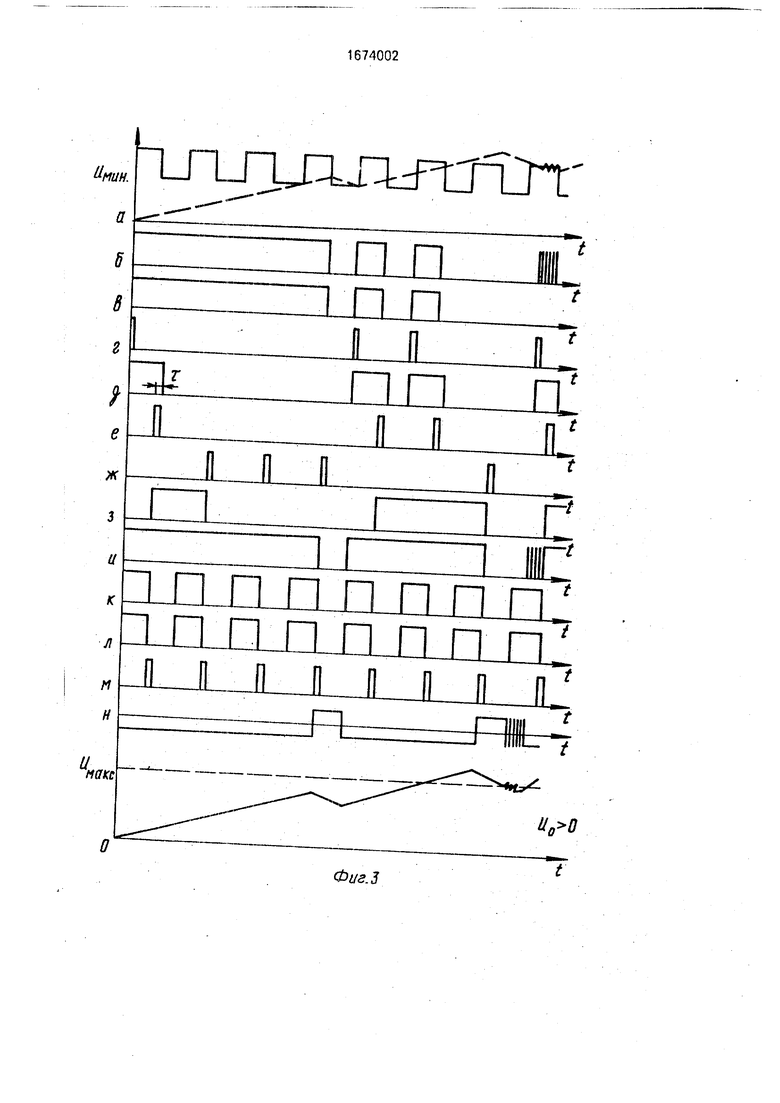

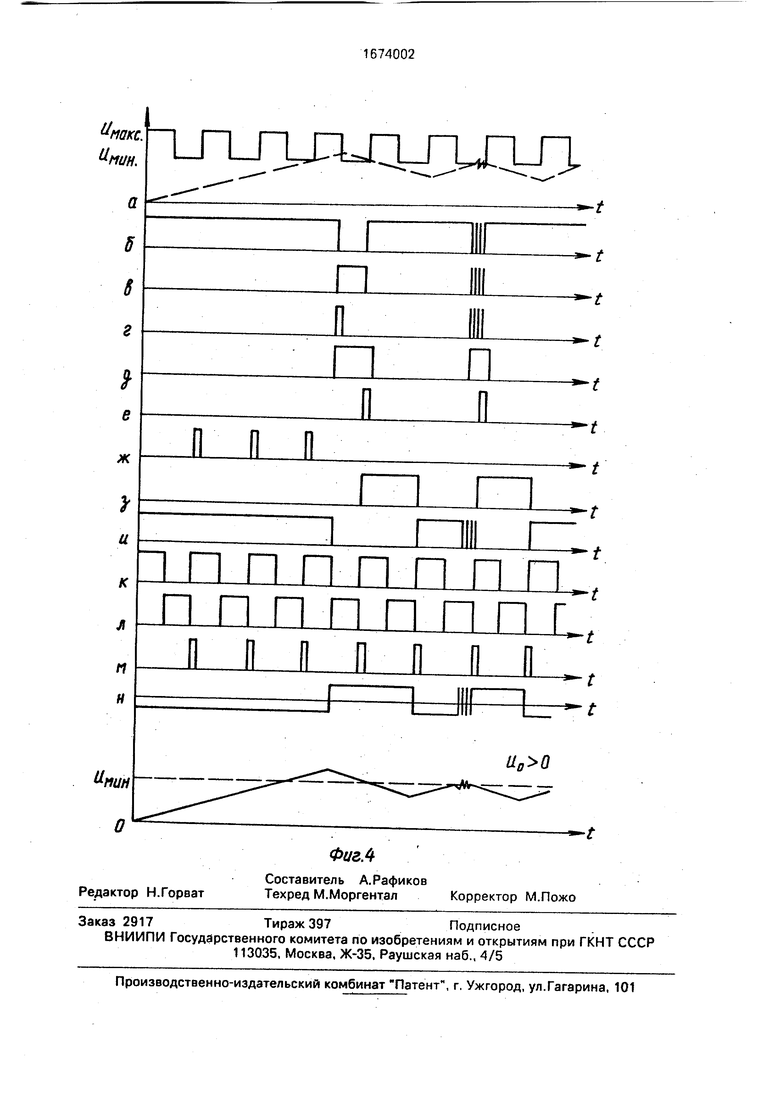

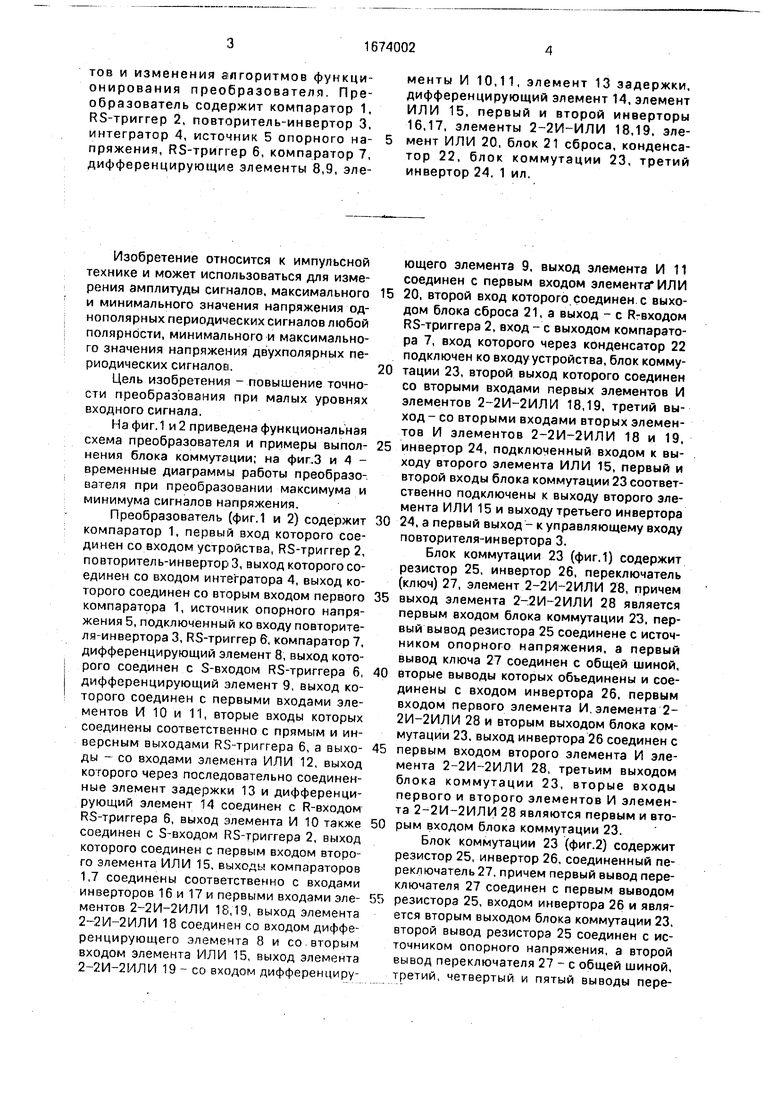

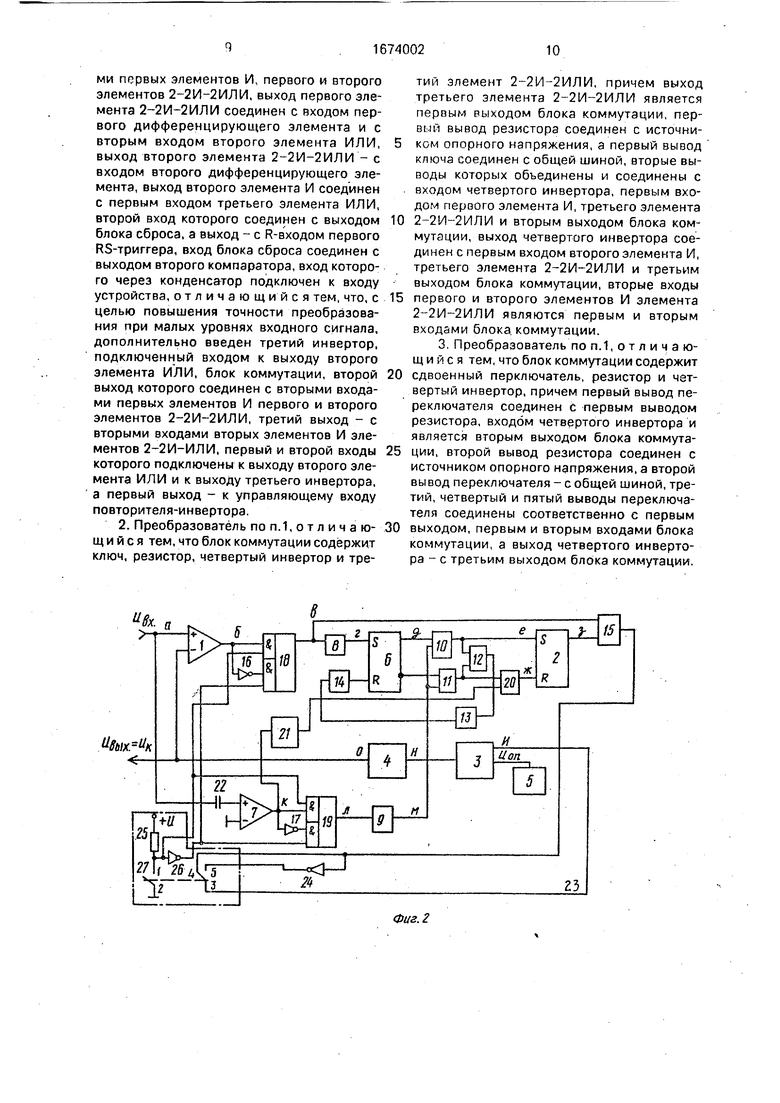

На фиг. 1 и 2 приведена функциональная схема преобразователя и примеры выполнения блока коммутации; на фиг.З и 4 - временные диаграммы работы преобразователя при преобразовании максимума и минимума сигналов напряжения.

Преобразователь (фиг.1 и 2) содержит компаратор 1, первый вход которого соединен со входом устройства, RS-триггер 2, повторитель-инвертор 3, выход которого соединен со входом интегратора 4, выход которого соединен со вторым входом первого компаратора 1, источник опорного напряжения 5, подключенный ко входу повторителя-инвертора 3, RS-триггер 6, компаратор 7, дифференцирующий элемент 8, выход которого соединен с S-входом RS-триггера б, дифференцирующий элемент 9, выход которого соединен с первыми входами элементов И 10 и 11, вторые входы которых соединены соответственно с прямым и инверсным выходами RS-триггера 6, а выходы - со входами элемента ИЛИ 12, выход которого через последовательно соединенные элемент задержки 13 и дифференцирующий элемент 14 соединен с R-входом RS-триггера 6, выход элемента И 10 также соединен с S-входом RS-триггера 2, выход которого соединен с первым входом второго элемента ИЛИ 15, выходы компараторов 1,7 соединены соответственно с входами инверторов 16 и 17 и первыми входами элементов 2-2И-2ИЛИ 18,19, выход элемента 2-2И-2ИЛИ 18 соединен со входом дифференцирующего элемента 8 и со вторым входом элемента ИЛИ 15, выход элемента 2-2И-2ИЛИ 19 - со входом дифференцирующего элемента 9, выход элемента И 11 соединен с первым входом элемента ИЛИ

20, второй вход которого соединен с выходом блока сброса 21, а выход - с R-входом RS-триггерэ 2, вход - с выходом компаратора 7, вход которого через конденсатор 22 подключен ко входу устройства, блок коммутации 23, второй выход которого соединен со вторыми входами первых элементов И элементов 2-2И-2ИЛИ 18,19, третий выход - со вторыми входами вторых элементов И элементов 2-2И-2ИЛИ 18 и 19,

инвертор 24, подключенный входом к выходу второго элемента ИЛИ 15, первый и второй входы блока коммутации 23 соответственно подключены к выходу второго элемента ИЛИ 15 и выходу третьего инвертора

24, а первый выход - к управляющему входу повторителя-инвертора 3.

Блок коммутации 23 (фиг.1) содержит резистор 25, инвертор 26, переключатель (ключ) 27, элемент 2-2И-2ИЛИ 28, причем

выход элемента 2-2И-2ИЛИ 28 является первым входом блока коммутации 23, первый вывод резистора 25 соединене с источником опорного напряжения, а первый вывод ключа 27 соединен с общей шиной.

вторые выводы которых объединены и соединены с входом инвертора 26, первым входом первого элемента И. элемента 2- 2И-2ИЛИ 28 и вторым выходом блока коммутации 23, выход инвертора 26 соединен с

первым входом второго элемента И элемента 2-2И-2ИЛИ 28, третьим выходом блока коммутации 23, вторые входы первого и второго элементов И элемента 2-2И-2ИЛИ 28 являются первым и вто0 рым входом блока коммутации 23.

Блок коммутации 23 (фиг.2) содержит резистор 25, инвертор 26, соединенный переключатель 27, причем первый вывод переключателя 27 соединен с первым выводом

Г резистора 25. входом инвертора 26 и является вторым выходом блока коммутации 23, второй вывод резистора 25 соединен с источником опорного напряжения, а второй вывод переключателя 27 - с общей шиной, третий, четвертый и пятый выводы переключателя 27 соединены соответственно с первым выходом, первым и вторым входами блока коммутации 23, а выход инвертора 26 - с третьим выходом блока коммутации 23.

Преобразователь работает следующим образом.

Первоначально при отсутствии сигнала на входе (сигнал напряжения на входе равен нулю) компаратор 7 находится в одном устойчивом состоянии, а блок 21 сброса вырабатывает сигнал, соответствующий отсутствию сигнала с переменной составляющей, который через элемент 20 ИЛИ устанавливает RS-триггер 2 в устойчивое состояние. При этом на выходе RS-триггера 2 устанавливается сигнал, равный О.

В зависимости от состояния сигналов блока коммутации 23 на выход элементов 2-2И-2ИЛИ 18 и 19 проходит либо прямой сигнал, формируемый соответствующим компаратором 1 и 7, либо проинвертирован- ный инверторами 16 и 17 сигнал от этих же компараторов 1 и 7. Далее сигнал U0 проходит через повторитель-инвертор 3, знак коэффициента передачи которого определяется логическим уровнем на управляющем входе, что приводит к возрастанию либо уменьшению сигнала напряжения на выходе интегратора 4. При этом при превышении уровня сигнала над нулем компаратор 1 вырабатывает сигнал, который, пройдя через элемент 2-2И-2ИЛИ 18, элемент ИЛИ 15 и блок коммутации 23, переключает знак коэффициента передачи повторителя-инвертора 3, сигнал на выходе интегратора 4 начинает уменьшаться, что приводит к гому, что он становится меньше нуля, и компаратор 1 перебрасывается. Сигнал с его выхода, пройдя по той же цепи, опять меняет знак коэффициента передачи повторителя-инвертора 3, и напряжение на выходе интегратора 4 начинает возрастать В устойчивом состоянии напряжение на выходе преобразователя совершает устойчивые колебания около нуля с частотой, определяемой в основном чувствительностью компаратора 1 и постоянной времени интегратора 4.

Рассмотрим подробно работу преобразователя в случае однополярного положительного сигнала напряжения с наложенной переменной составляющей (фиг.З и 4) для режимов преобразования максимума и минимума.

Пусть на вход преобразователя подается сигнал положительной полярности с наложенной переменной составляющей, как показано на фиг.За и 4а. Блок коммутации 23 установлен в положение преобразования максимума напряжения При этом на его прямом выходе потенциал, соответ ствующий 1 а на инверсном - соответст вующий О.

5I (апряжение Do болите нуля При услопии 1 на управляющем входе повторитепя- ииоертора 3 коэффициент передачи имеет отрицательный знак.

Напряжение на выходе преобразовате0 ля приблизительно равно нулю. На ныходе компаратора 1, как показано на фиг 36, устанавливается 1 на все время превышения сигнала, Переменная составляющая входного сигнала через разделитель5 ный конденсатор 22 подается на вход второго компаратора 7, на выходе которого формируется последовательность импульсов, как показано на фиг Зк Далее сигналы с компараторов 1 и 7 без инверсии проходят

0 на выход элементов 2-2И-ИЛИ 18 и 19. При этом сигнал с элемента 2 2И-2ИЛИ 18 через элемент ИЛИ 15 и блок коммутации 23 устанавливает коэффициент передачи по- вторителя-инвертора 3, равный минус К.

5 Соответственно на вход интегратора 4 поступает сигнал отрицательного напряжения -KUo и напряжение UK на выходе интегратора 4 начинает возрастать в течение всего времени, пока выполняется

0 условие UBx UK Первый же передний фронт на выходе элемента 2-2И-ИЛИ 18 (фиг.36) дифференцируется дифференцирующим элементом 8 (фиг Зг) и информация о факте выполнения услоьия UBX UK записы5 вается в RS-триггер б (фиг Зд), а по CHI налу (фиг Зм), формируемому по заднему фронту последовательности импульсов, на выходе элемента 2-2И- ИЛИ 19 (фиг Зл) через элемент И 10 информация переписывается в

0 RS-триггер 2. При этом на выходе устанавливается сигнал 1 (фиг.Зз). В то же время этот хе сигнал, пройдя через элемент ИЛИ 12 и задержанный элементом 13 задержки на время г , дифференцируется дифферен5 цирующим элементом 14 и сбрасывает RS- триггер б Время задержки г выбирается из тех условий, что оно должно быть больше, чем длительность импульса, формируемого дифференцирующим элементом 9, чем иск0 лючается гонка фронтов импульсов на входах RS-триггеров 2 и 6 По заднему фронту следующего импульса с компаратора 7 производится последующий опрос состояния RS-триггера 6, а так как переднего фронта

5 больше не было, RS-триггер 6 остается в сброшенном состоянии. Тогда сигнал с элемента И 11, пройдя через элемент ИЛИ 20, сбросит RS-триггер 2 (фиг Зз). Однако направление интегрирования останется за

счет сигнала, который проходит с компаратора 1 на второй вход элемента ИЛИ 15 через блок коммутации 23 (фиг.Зи) и возрастание UK будет продолжаться. При достижении напряжением UK минимальных значений напряжения на входе компаратор 1 начинает опрокидываться на каждый импульс наложенной переменной составляющей, если выполняется условие UK Unanc. При этом данная информация последовательно по переднему фронту записывается в RS-триггер б, а затем по заднему фронту информации переписывается в RS-триггер 2 и, если выполняется условие UK иМакс, RS-триггер 2 не меняет своего состояния, а следовательно, продолжается возрастание напряжения UK, как показано на фиг.За (пунктиром) и фиг.Зо. С момента, когда условие UK итмакс перестает выполняться, по первому же заданному фронту переменного сигнала RS-триггер 2 перебросится (фиг.Зз) и UK (фиг.Зо) начинает уменьшаться до момента, когда

уСЛОВИе UK UmMflKC ВЫПОЛНИТСЯ.

Далее процесс повторяется, и в устойчивом состоянии напряжение UBUX UK совершает колебания около значения, равного имакс входного сигнала.

Рассмотрим для этого же сигнала работу преобразователя в режиме преобразования минимума сигнала. При этом на прямом выходе блока коммутации 23 о- тснциала, соответствующий О, а на инверсном - потенциал, соответствующий 1. На выход первого и второго элементов 2-2И-ИЛИ 18 и 19 проходит проинвертиро- ванный соответствующими инверторами 16 и 17 сигнал с компараторов 1- и 7, а на выход элемента 2-2И-ИЛИ 28 сигнал с инвертор 24, сигнал с элемента (фиг.4в)2-2И- ИЛИ 18 подается на первый вход логического элемента ИЛИ уровнем О, если выполняется условие UBX UK. С элемента 2-2И--ИЛИ 19 сигнал подается на дифференцирующий элемент 9. где формируется по заднему фронту последовательность импульсов (фиг,4м), Этим же импульсом RS-триггер б сбрасывается, так как на выходе элемента 2-2И-ИЛИ 18 не формируется импульс; сигнал О проходит через элемент ИЛИ 20 (фпг.4ж) и сбрасывает RS-триггер 2, на выходе (фиг 4з) его устанавливается уровень О. Соответственно на выходе элемента ИЛИ 15 формируется низкий потенциал, соответствующий уровню О, а на первом выходе б юка коммутации 23 - высокий, при этом у повторителя-инвертора 3 устанавливается коэффициент передачи -К. а на его выходе устанавливается сигнал KUo, и напряжение UK на выходе интегратора 4 начинает возрастать (фиг.4а, 4о). Процесс возрастания продолжается до тех пор, пока UK не превысит величины имин входного сигнала. При этом первый же импульс с компаратора

1, пройдя через инвертор 16 и элемент 2-2И-ИЛИ 18, продифференцированный дифференцирующим элементом 8, установит RS-триггер 6 и одновременно, пройдя через элемент ИЛИ 15, третий инвертор 24

0 и блок коммутации 23, изменит знак коэффициента передачи повторителя-инвертора 3, и напряжение на входе интегратора 4 (фиг.4н) изменит направление интегрирования.

5Напряжение UK начинает уменьшаться (фиг.4а, 4о). Как только поступление сигналов с компаратора 1 прекращается, т.е. выполнится условие UK UMMH, сигналом RS-триггера 6 (фиг.4з) изменится знак ко0 эффициента передачи повторителя-инвертора 3, и напряжение UK будет возрастать. В установившемся режиме напряжение UK будет совершать колебания у величины напряжения, равного UMMH.

5 Аналогично преобразователь работает и при других формах сигналов автоматически, в зависимости от заданного режима преобразования, находя и преобразуя максимум либо минимум входного сигнала.

0 Формула изобретения

1. Преобразователь экстремумов периодического сигнала в постоянное напряжение, содержащий первый компаратор, первый вход которого соединен с входом

5 устройства, первый RS-триггер, повторитель-инвертор, вход которого соединен с входом интегратора, выход которого соединен с вторым входом первого компаратора, источник опорного напряжения, подклю0 ченный к входу повторителя-инвертора, второй RS-триггер, второй компаратор, первый дифференцирующий элемент, выход которого соединен с S-входом второго RS-триггера, второй дифференцирующий

5 элемент, выход которого соединен с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с прямым и инверсным выходами второго RS-триггера, а выходы - с

0 входами первого элемента ИЛИ, выход которого через последовательно соединенные элементы задержки и третий дифференцирующий элемент соединен с R-входом второго RS-триггера, выход первого элемен5 та И, кроме того, соединен с S-входом первого RS-триггера, выход которого соединен с первым входом второго элемента ИЛИ, выходы первого и второгого компараторов соединены соответственно с входами первого и второго инверторов и первыми входами пгрвых элементов И первого и оторого элементов 2-2И-2ИЛИ, выход первого элемента 2-2И-2ИЛИ соединен с входом первого дифференцирующего элемента и с вторым входом второго элемента ИЛИ, выход второго элемента 2-2И-2ИЛИ - с входом второго дифференцирующего элемента, выход второго элемента И соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом блока сброса, а выход - с R-входом первого RS-триггера, вход блока сброса соединен с выходом второго компаратора, вход которого через конденсатор подключен к входу устройства, отличающийся тем, что, с целью повышения точности преобразования при малых уровнях входного сигнала, дополнительно введен третий инвертор, подключенный входом к выходу второго элемента ИЛИ, блок коммутации, второй выход которого соединен с вторыми входами первых элементов И первого и второго элементов 2-2И-2ИЛИ, третий выход - с вторыми входами вторых элементов И элементов 2-2И-ИЛИ, первый и второй входы которого подключены к выходу второго элемента ИЛИ и к выходу третьего инвертора, а первый выход - к управляющему входу повторителя-инвертора.

2. Преобразователь по п. 1, о т л и ч а ю- щ и и с я тем, что блок коммутации содержит ключ, резистор, четвертый инвертор и тре

2-

тий элемент 2-2И-2ИЛИ. причем выход третьего элемента 2-2И-2ИЛИ является первым РЫХОДОМ блока коммутации, пер- вий вывод резисгора соединен с источником опорного напряжения, а первый ньтод ключа соединен с общей шиной, вторые вы- поды которых объединены и соединены с входом четвертого инвертора, первым входом первого элемента И, третьего элемента 22И-2ИЛИ и вторым выходом блока коммутации, выход четверюго инвертора соединен с первым входом второго элемента И, третьего элемента 2-2И-2ИЛИ и третьим выходом блока коммутации, вторые входы первого и второго элементов И элемента 2-2И-2ИЛИ являются первым и вторым входами блока коммутации.

3. Преобразователь по п. 1, о т л и ч а ю- щ и и с я тем. что блок коммутации содержит сдвоенный перключатель, резистор и четвертый инвертор, причем первый вывод переключателя соединен с первым выводом резистора, входом четвертого инвертора и является вторым выходом блока коммутации, второй вывод резистора соединен с источником опорного напряжения, а второй вывод переключателя - с общей шиной, третий, четвертый и пятый выводы переключателя соединены соответственно с первым выходом, первым и вторым входами блока коммутации, а выход четвертого инвертора - с третьим выходом блока коммутации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь экстремумов периодического сигнала в постоянное напряжение "Галс-7 | 1987 |

|

SU1442926A1 |

| Преобразователь амплитуды импульсов в постоянное напряжение | 1987 |

|

SU1509752A1 |

| Преобразователь амплитуды импульсов в постоянное напряжение | 1987 |

|

SU1506371A1 |

| Устройство для моделирования вентильного электродвигателя | 1988 |

|

SU1596357A1 |

| Измерительный преобразователь активной мощности | 1989 |

|

SU1659890A1 |

| Устройство для разбраковки полупроводниковых диодов | 1983 |

|

SU1164636A1 |

| Устройство для моделирования вентильного преобразователя | 1981 |

|

SU968829A1 |

| Преобразователь амплитуды импульсов в постоянное напряжение "Галс-4 | 1987 |

|

SU1511697A1 |

| Частотно-регулируемый асинхронный электропривод | 1985 |

|

SU1309247A1 |

| Преобразователь амплитуды импульсов в постоянное напряжение "Галс-В | 1984 |

|

SU1288615A1 |

Изобретение относится к импульсной технике и может быть использовано для измерения амплитуды сигналов, максимального и минимального напряжений однополярных периодических сигналов любой полярности, максимального и минимального значений двухполярных периодических сигналов. Цель изобретения - повышение точности преобразования при малых уровнях входного сигнала. Полученный эффект достигается за счет введения в преобразователь дополнительных элементов и изменения алгоритмов функционирования преобразователя. Преобразователь содержит компаратор 1, RS-триггер 2, повторитель-инвертор 3, интегратор 4, источник 5 опорного напряжения, RS-триггер 6, компаратор 7, дифференцирующие элементы 8, 9, элементы И 10, 11, элемент 13 задержки, дифференцирующий элемент 14, элемент ИЛИ 15, первый и второй инверторы 16, 17, элементы 2-2И-ИЛИ 18, 19, элемент ИЛИ 20, блок 21 сброса, конденсатор 22, блок коммутации 23, третий инвертор 24. 4 ил.

Лг. а

UMUH.

8

/

I

ж

II О И

ц

П

П П П fl П О П П

ffifcr-J

и

мак

О

JL

л;

c

JIT

Фиг.З

UflQKC.

UHUH. a

.4

S г

1

e ж

У и

D

и н

JLJLJLJL П И О

а,

пин

W --.,

П

О

- f

О

Ь

fl

| Преобразователь амплитуды импульсов в постоянное напряжение "Галс | 1983 |

|

SU1233056A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь экстремумов периодического сигнала в постоянное напряжение "Галс-7 | 1987 |

|

SU1442926A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-08-30—Публикация

1989-04-25—Подача