Вход

(Л

4:

И

и

со

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1985 |

|

SU1288902A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Регистр сдвига | 1982 |

|

SU1111207A1 |

| Устройство для ввода информации | 1984 |

|

SU1200274A2 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ПОВЫШЕННОЙ ТОЧНОСТИ (ВАРИАНТЫ) | 2008 |

|

RU2376625C1 |

| Формирователь длительности импульсов | 1986 |

|

SU1411942A1 |

| Голографическое постоянное запоминающее устройство | 1990 |

|

SU1725258A1 |

| Цифровой регулятор угловой скорости дугостаторного асинхронного двигателя | 1984 |

|

SU1203481A1 |

| ЦИФРОВОЕ ПЯТИКАНАЛЬНОЕ РЕЛЕ С ФУНКЦИЕЙ САМОДИАГНОСТИКИ | 2017 |

|

RU2671545C1 |

| ПАРАЛЛЕЛЬНЫЙ ИДЕНТИФИКАТОР КРИТИЧЕСКИХ ВЫБРОСОВ И ПРОВАЛОВ ПРИ СТАЦИОНАРНОМ И НЕСТАЦИОНАРНОМ НАПРЯЖЕНИИ СЕТИ | 2001 |

|

RU2191427C1 |

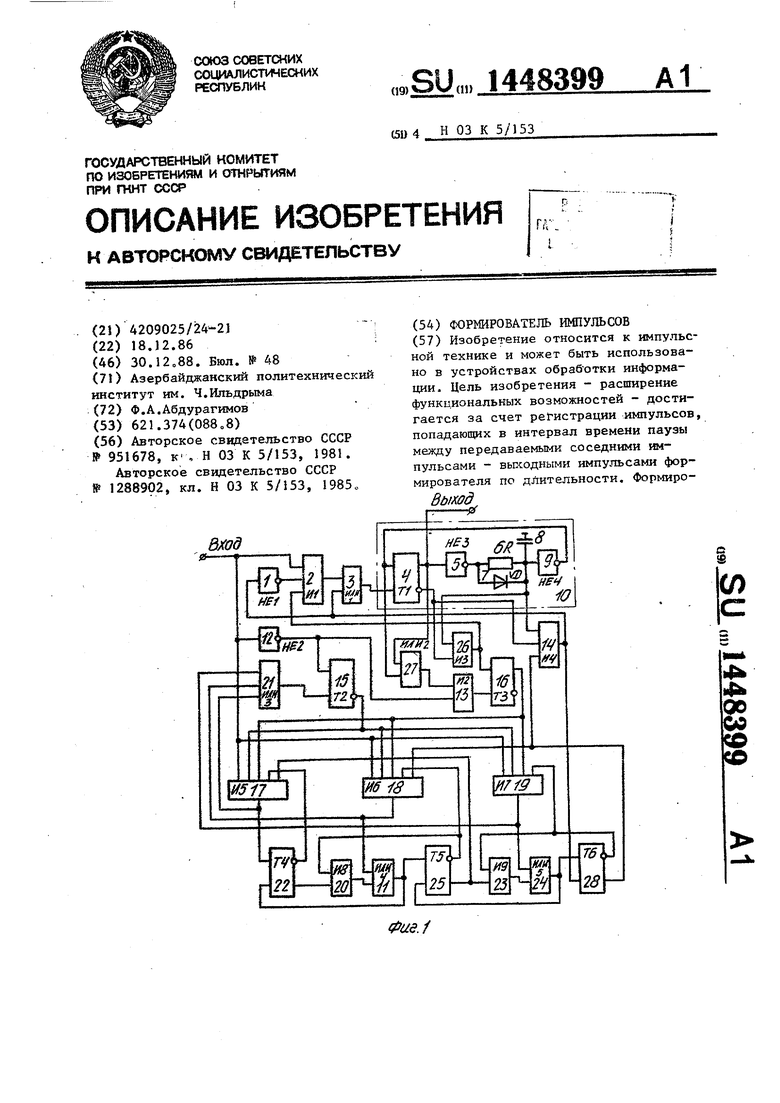

Изобретение относится к импульсной технике и может быть использовано в устройствах обраб отки информации. Цель изобретения - расширение функциональных возможностей - достигается за счет регистрации импульсов, попадаюпщх в интервал времени паузы между передаваемыми соседними импульсами - выходными импульсами формирователя ПС длительности. ФормироBbixod

Фие.1

ватель импульсов содержит элементы НЕ 1, 5, 9 и 12, элементы И 2, 13, 14, 17 - 20, элементы ИЛИ 3, 11, 21, 24 и 27, триггеры 4, 15, 16, 22, 25 и 28, резистор 6, диод 7, конденсатор 8, формирователь 10 импульсов. Элемент НЕ 1 исключает совпадение входного и записанного импульсов при передаче последнего на вход формирователя. С поступлением первого входного импульса через элементы И 2 и ИЛИ 3 запускается формирователь 10 и фор1

Изобретение относится к импульсной технике и может быть использовано в устройствах обработки информации.

Целью изобретения является расширение функциональной возможности за счет регистрации импульсов, попадающих в интервал времени паузы между передаваемыми, соседними импульсами (выходными импульсами формирователя по длительности).

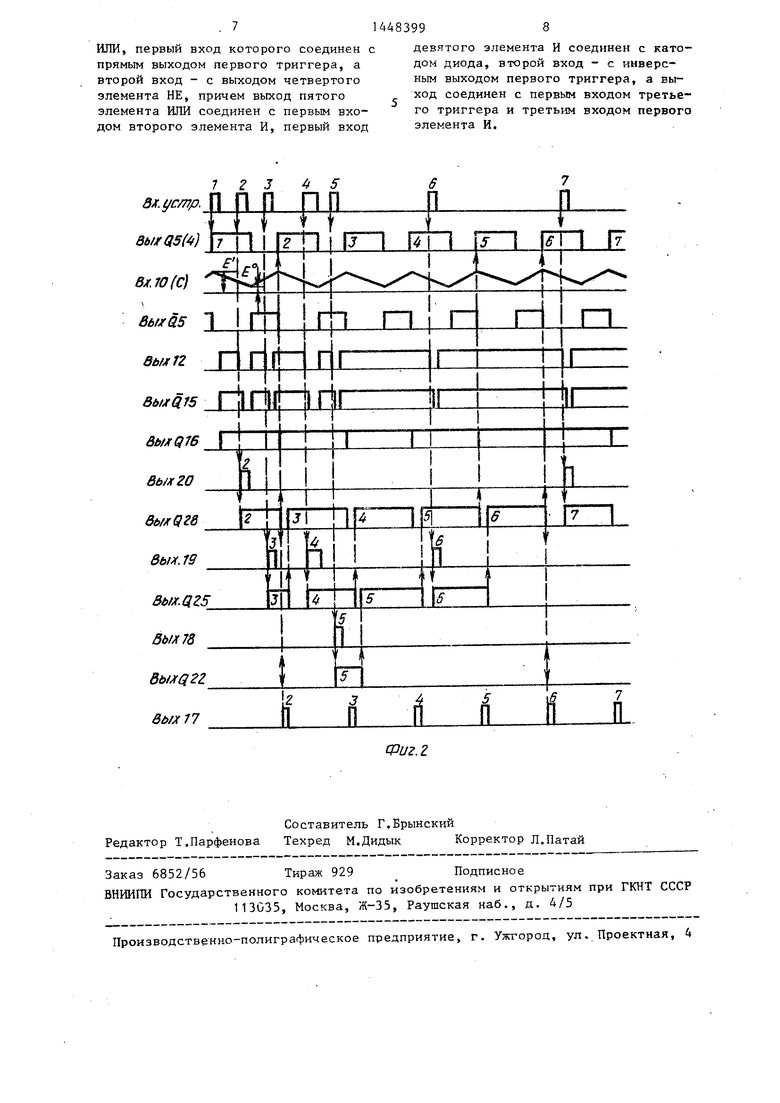

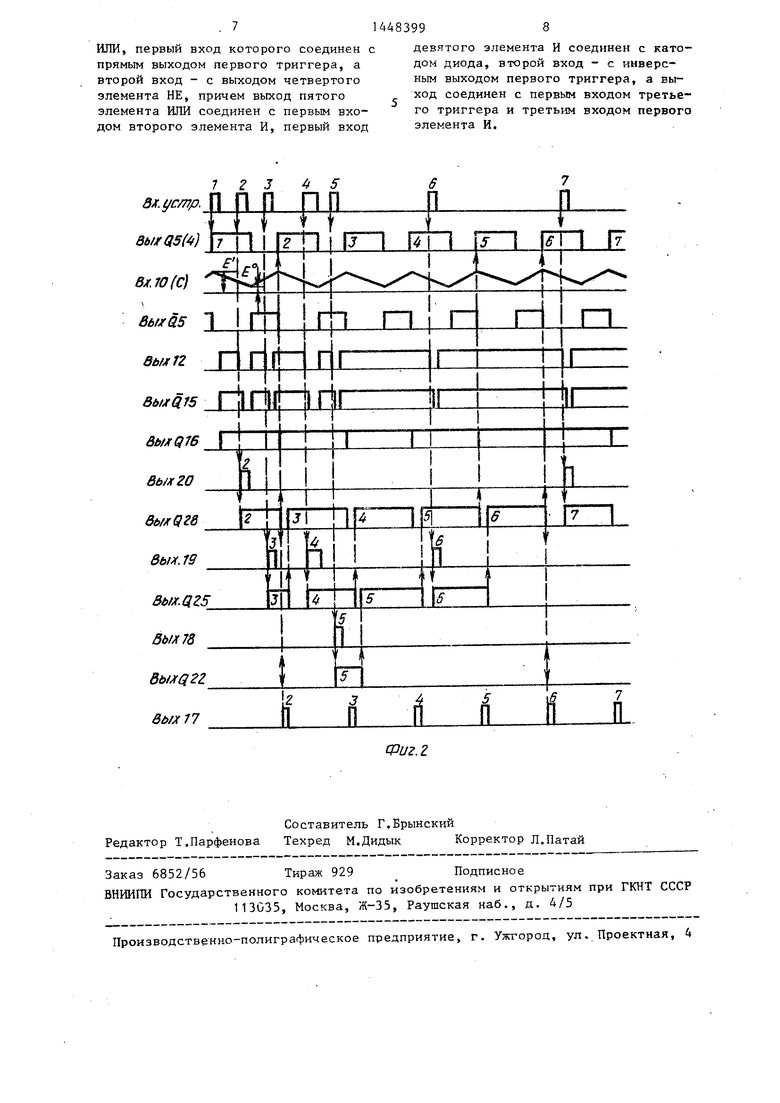

На фиг.1 представлена функциональная схема предлагаемого формирователя импульсов; на фиг,2 - временная диаграмма работы устройства (в - нулевое логическое состояние; Е - единичное логическое состояние).

Формирователь импульсов содержит элемент НЕ i, первый элемент И 2, первый элемент ШШ 3, первый триггер

4,которьй совместно с элементов НЕ

5,резистором 6, диодом 7, конденсатором 8 и элементом НЕ 9 вьшолняет функции формирователя 10 юшульсов, второй элемент ИЛИ 11, второй элемент НЕ 12, второй элемент И 13, третий элемент И 14, второй триггер 15, третий триггер 16, четвертьй элемент 17, пятый 18, шестой 19 и седьмой 20 элементы И, третий элемент ИЛИ 21, четвертый триггер 22, восьмой элемент И 23, четвертый элемент ИЛИ 24, пятый триггер 25, девятый элемент И 26, пятый элемент ИЛИ 27 и шестой триггер. 28. Между прямьм выходом первого триггера 4, являющимся выходом устройства, и его первым входом включены третий элемент НЕ 5 последовательно

мирует импульс, длительность которо равна времени разряда конденсатора Задним фронтом выходного импульса формирователя 10 происходит заряд конденсатора 8 до единичного логического уровня элемента НЕ 9, обеспечивающего иаузы между выходными импульсами. Работа всех элементов устройства поясняется по временным диаграммам, приведенным в описании изобретения. 2 ил.

с параллельно соединенными резистором 6 и диодом 7, анод которого подключен к выходу элемента НЕ 5, а катод через конденсатор 8 соединен с

5 общей шиной, и четвертый элемент НЕ 9, причем катод диода 7 соединен с первым входом третьего элемента И 14 второй вход второго соединен с инвер выходом первого триггера 4, а

10 выход через первый элемент НЕ 1 - со вторым входом первого элемента И 2, первый вход которого является входом устройства. Вход первого элемента НЕ 1 соединен с вторым входом пер 5 вого элемента ШШ 3, первый вход которого соединен с выходом первого элемента И 2, а выход - со вторым входом первого триггера 4, прямой выход которого соединен с первым дом пятого элемента ШШ 27, второй вход которого соединен с первым входом первого триггера 4, выход пятого

элемента ШШ 27 соединен с первым входом второго элемента И 13, второй вход которого через второй элемент НЕ 12 соединен с входом устройства, а выход - с вторым входом третьего триггера 16, первый вход которого соединен с выходом девятого элемента И 26, первый вход которого соединен с первым входом третьего элемента И 14, второй вход - с инверсным выходом первого триггера 4, а выход - с третьим входом первого элемента

35 И 2. Выходы четвертого 17, пятого 18 и шестого 19 элементов И соединены с первыми входами четвертого триггера

25

30

3

22, второго 11 и четвертого 24 элементов ИЛИ соответственно, а также с входами третьего элемента ИЛИ 21, выход которого соединен с вторьгн входом второго триггера 15, первый вход которого соединен с выходом втрого элемента НЕ 12, а инверсньш выход - с вторыми входа ш элементов И 17 - 19, первые входы которых соединены с входом устройства, третьи входы - с прямым выходом третьего триггера 16, четвертые - с инверсными выходами четвертого 22, пятого 2 и шестого 28 триггеров соответственно, а пятые входы элементов И 17 и 18 соединены с прямыми выходами тригеров 25 и 28 соответственно, приче второй вход четвертого триггера 22 соединен с выходом элемента ИЛИ 11, а прямой выход - с вторым входом седьмого элемента И 20, первый вход которого соединен с инверсным выходом пятого триггера 25, а выход - с вторым входом второго элемента ИЛИ 11, выход которого соединен с первы входом пятого триггера 25, второй вход которого соединен с выходом чевертого элемента ИЛИ 24, а прямой выход - с вторым входом восьмого элмента И 23, первый вход которого содинен с инверсным выходом шестого триггера 28, а выход - с вторым входом четвертого элемента ИЛИ 24, вых которого соединен с первым входом шестого триггера 28, второй вход которого соединен с выходом третьего элемента И 13, третий вход которого соединен с прямым выходом шестого триггера 28.

Устройство работает следующим образом.

С поступлением первого входного импульса через последовательно соединенные элементы И 2 и ИЛИ 3 запускается формирователь 10 и формируется импульс, длительность которого равна времени разряда конденсатора 8. При спаде первог.о входного импульса срабатьшает элемент НЕ 12 и через элемент И 13, подготовленный выходным сигналом триггера 4 формирователя 10 через элемент ИЛИ 27, триггер

При регистрации импульса в одиом разряде регистра исключается возможность регистрации этого импульса в других разрядах с помощью элемента

16, переброшенный в единичное состоя- jg щ 21 и триггера 15. Для это- ние сигналом с выхода элемента И 13, го выходной сигнал соответствующего а также через триггер 15, установлен- элемента И и (17-19) опрокидьшает ньщ в нулевое состояние, подготавли- триггер 14 в единичное со стояние и Ёает входы элементов И 17 - 19. -тем самым снимает разрешающий сигнал

0

0

5

Если во время формирования первого импульса на вход устройства поступает следукяций импульс, .то этот импульс не просчитьшается, а вццеляет- ся с .помощью элемента И 19 и через элемент ИЛИ 24 запоминается триггером 28. В это время входы элементов И 17 и 18 блокированы сигналами с единичного выхода триггеров 25 и 28. С запоминанием импульса триггером 28 блокируется вход элемента И 19 и подготавливается вход элемента И 17 для регистрации третьего импульса, кото5 рый запоминается триггером 22 через элемент И 17.

Задним фронтом выходного импульса формирователя 10 происходит заряд конденсатора 8 до единичного логического уровня элемента НЕ 9, обеспечивающего паузы между выходными импульсами формирователя 10о Высокий уровень потенциала с выхода элемента НЕ 9 через элемент ИЛИ 27 при отсутствии входного импульса не позволяет опрокидывания триггера 16 в нулевое состояние и условие для записи входных импульсов в регистре не исключается, т.е. при поступлении входных импульсов во время паузы между выходными импульсами формирователя осуществляется их запись в -регистр. При этом вход элемента И 26 подготовлен сигналом с инверсного выхода триггера

35 5, При заряде конденсатора до единичного логического уровня высокий потенш ал снимается с выхода элемента И 26, и, следовательно, с- входа триггера 16. Одновременно срабатьша-

40 ет заранее подготовленный элемент И 26 и опрокидьшает триггер 16 в исходное состояние, и условие для записи входных и fflyльcoв в регистре исчезает о Этот момент остается до пос45 тупления на выход триггера 4 входного и записанного импульсов, и с поступлением одного из них триггер 16 опрокидывается в рабочее состояние, так как восстанавливается условие для

50 записи импульсов.

При регистрации импульса в одиом разряде регистра исключается возможность регистрации этого импульса в других разрядах с помощью элемента

0

jg щ 21 и триггера 15. Для это- го выходной сигнал соответствующего элемента И и (17-19) опрокидьшает триггер 14 в единичное со стояние и -тем самым снимает разрешающий сигнал

514

с выходов элементов К 17 - 19-, Элемент НЕ I исключает совпадение входного и записанного имт-ульсов при передаче последнего на вяо;.- формирова - теля,

При отсутствии импульса з,атисаннь й в посладкем разряде регистра тлпулъс череэ элемекты И 14 и ИЛИ 3 после заряда конденсатора 8 . до логического уровня эле-цента НЕ 9 обеспечиваюпдего navsu -между выходными импульсами шот-1мяоовн е.ля 10, поступает 1 про- ИСХОДИТ . ИМТГ /ЛЪса Переднем Фронтом вьжодного импульса эххемент И 14 опрсх-сидьгаает триггер 28 в кскодное состояниеj и происходит автоматический сдвиг импульса со второго разряда регистра через элемента И 23 и ИЖ 24 в последний разряд. Второй разряд уста- навл шаетск в исход.ое состояние сигналом с выхода эл : мента ИЛИ 24 и про

исходит автог-шткческий сдвиг -5Мпуль- 25 кьй выход которого соединен с вторыми

са с третьего разряда рет лстра через элементь; И 20 и ИЛИ 1 во второй разряд. Третий разряд -устанавливается в исходное состояние сигналом с выхода элемента ЫМ 11,,При формировании очаре АНого им- пуль са nocT;nici;c :i:v/a Злоднь е импульсь -регистрируются s регистре. В слу да.е незаполнекпого регистра л при снятии блокировки входа :-.;:е-- еь.та И 2 сигналом с выхода з)е -;снта Fi 26 очерадной входной кмпульс поступРет нег;осред :СТвенно ка вход фЬу1-.:трС - ;-ателя iO,,

о р м у л а

о я

н и я

Формирователь импул: сов« соггержа- щий первьй; второй и третий триггерь з причем между гфямым ккходон перзого

триггера. являющимся яыходом формиро- з Дом пятого и первым входом шестого

вателя и его иер:зь м входов; третий элемеН л НЕ по следователт:ЧО с парал. соэднкенньп та рс;зкстс)ром и диодом, анод коч Орот С иодклочен к

: r. ivl.7:-;p ;4-Г . - Г .-Г . 1 -. - : ;

ВЫХОДУ этого s-K через конденсат;: живой,, и 4eTBep j:- jf злеман : которого соединен с катодом диода„ а выкод - с первым аксдоу пзрвого триггера,, дкода соединен с первым входом третьего элемен-- та И: второй Бход JcoToporo Соединен с инверсиык ,зх1ходом первого триггера а выход чепез зтчрзы-й элемент НЕ - - с

0

вторым входом первого элемента И, первый вход которого является входой устройства, причем вход первого элемента НЕ соединен с вторым входом первого элемента ИЛИ, первый вход которого соединен с выходом первого элемента И, а выход - с вторым вхо- док первого триггера, первый вход второго триггера соединен через второй элемент НЕ с входом устройства, а также вторым входом второго элемента И, выход которого соединен с вторым входом третьего триггера, пря- 5 мой выход которого соединен с- третьими входами четвертого, пятого и шестого элементов И, первые входы которых соединены с входом устройства, а выходы - с первыми входами четвертого триггера, второго и четвертого элементов ИЛИ соответственно, а также с входами третьего элемента ИЛИ, выход которого соединен с вто- входом второго триггера, инверс

0

входами четвертого, пятого и шестого элементов И, четвертые входы которых соединены с инверсными выходами четвертого, пятого и шестого триггеров

соответственно, причем прямой выход четвертого триггера соединен с вто- jpbM входом седьмого элемента И, пер- вьй вход которого соединен с инверс- ным вькодом пятого триггера, а выход с вторым входом второго элемента ИЛИ, выход которого соединен со Ьторым входом четвертого и с первым входом пятого триггеров, прямой выход пятого триггера соединен с пятым

входом четвертого элемента И, а так- |же с вторым входом восьмого, элемента И, выход которого соединен со вторым входом четвертого элемента ИЛИ, выход которого соединен с вторым вхотриггеров, причем второй вход шестого триггера соединен с выходом третьего элемента И, третий вход которого соединен с пятьм входом пятого элемента И и с -прямым выходом шестого триггера, инверсньш выход которого соединен с первым входом восьмого элемента И, отличающийся тем что, с целью расширения функциональньк возможностей путем обеспечения регистрации импульсов, попадающих в интервал времени паузы между вьтходн,ь1ми импульсами, в него введены девятьй элемент И и пятый элемент

. 714483998

ИЛИ, первый вход которого соединен с девятого элемента И соединен с катопрямым выходом первого триггера, а второй вход - с выходом четвертого элемента НЕ, причем выход пятого элемента ИЛИ соединен с первым входом второго элемента И, первый вход

дом диода, второй вход - с инверсным выходом первого триггера, а выход соединен с первым входом третьего триггера и третьим входом первого элемента И.

7 2 J 5

Ы

ГП} |ТП

rh п

rj

t±

4UJi

BbtxQIB

вь/хго

BbfxQZe

Вы. Г9

&ых.щг5 ВЫХ78

вь/х 77

дом диода, второй вход - с инверсным выходом первого триггера, а выход соединен с первым входом третьего триггера и третьим входом первого элемента И.

f

F

rd

П

НЕ

LI

1

ориг.г

| Формирователь импульсов | 1981 |

|

SU951678A1 |

| Формирователь импульсов | 1985 |

|

SU1288902A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-12-30—Публикация

1986-12-18—Подача