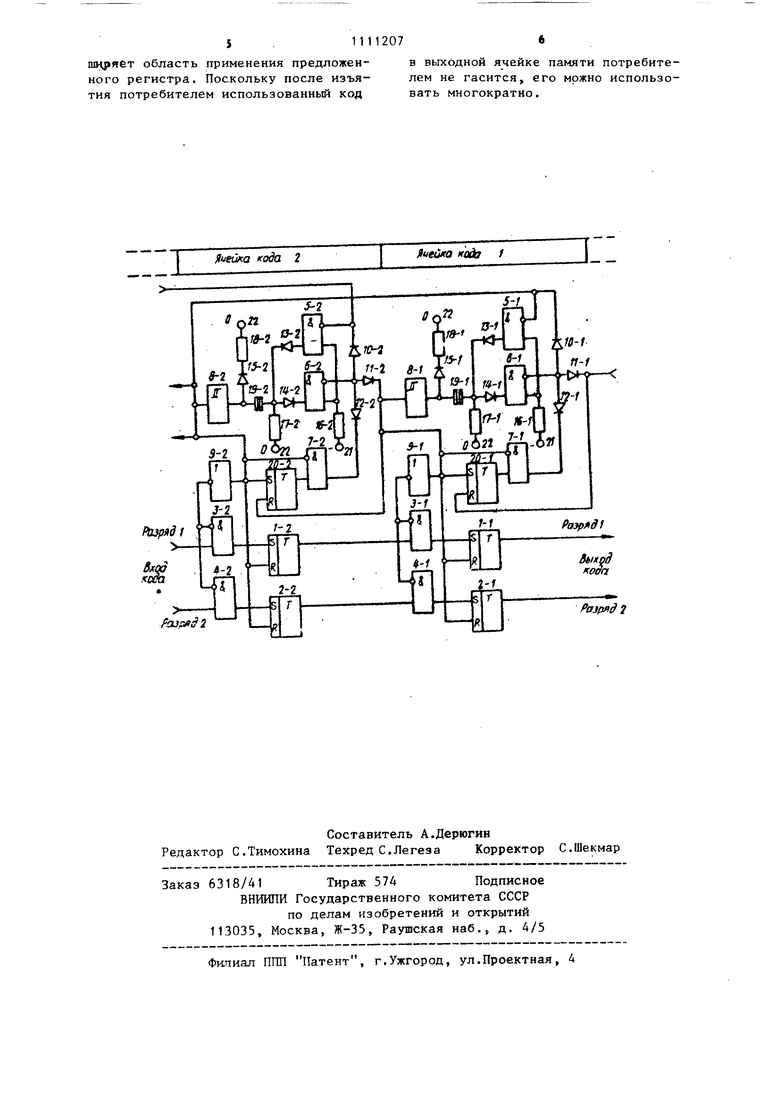

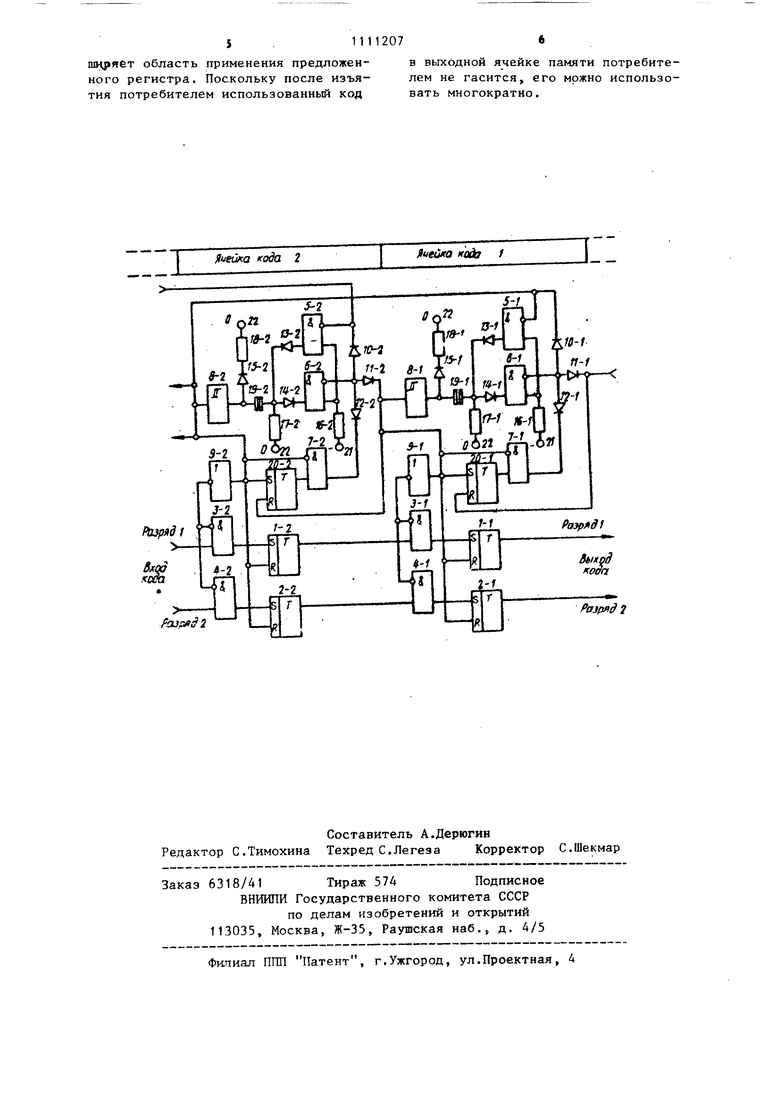

Изобретение относится к автомати ке и вычислительной технике и может быть использовано при построении устройств управления и хранения информации, , Известен регистр сдвига, состоящи из нескольких одинаковых ячеек памя ти, поразрядно соединенньк между со бой через элементы ЗАПРЕТ l . Наиболее близким к предлагаемому по технической сущности является регистр сдвига, содержащий в каждом разряде ячейки памяти, каждая из ко торых- состоит из RS-триггера и элемента ЗАПРЕТ, и формирователь импульсов сдвига, состоящий из трех элементов ЗАПРЕТ, порогового элемен та , элемента НЕ, разделительных диодов, согласующих резисторов и конден сатора 2J . Недостатком известных регистров является ограниченная область применения, так как они не позволяют обслуживать нулевые кодовые комбинации и не сохраняют записанньй в ячейку код после его считывания потребителем. Цель изобретения - расширение области применения путем обеспечения возможности сдвига любых кодовых ком бинаций . Поставленная цель достигается тем что регистр сдвига, содержащий в каждом разряде ячейки памяти, каждая из которых состоит из RS-триггера и элемента ЗАПРЕТ, и формирователь импульсов сдвига, состоящий из трех элементов ЗАПРЕТ, шести разделительных элементов ня диодах, трех согласующих элементов на резисторах и накопительного элемента на конденсаторе, выход элемента ЗАПРЕТ каждой ячейки памяти соединен с S-входом RS-триггера данной ячейки памяти, прямой выход которого соединен .с прямым входом элемента ЗАПРЕТ соответствующей ячейки памяти последующего разряда, инверсные входм элементов ЗАПРЕТ ячеек памяти каждого разряда соединены с выходом элемента НЕ формирователя импульсов сдвига разряда, в формирователе импульсов сдвига каждого разряда инверсньй вход первого элемента ЗАПРЕТ соединен с катодом первого диода и с выходом порогового зле мента формирователя импульсов сдвига предыдущего разряда, аноды первого, второго и третьего диодов соединены с инверсньм входом второго элемента ЗАПРЕТ, прямые входы второго и третьего элементов ЗАПРЕТ через первьй резистор подключены к шине питания, катод второго диода соединен с выходом порогового элемента формирователя импульсов сдвига последующего разряда, катод третьего диода соединен с выходом третьего элемента ЗАПРЕТ, инверсньй вход которого соединен с выходом порогового элемента и с входом элемента НЕ формирователя импульсов сдвига данного разряда, выход первого элемента ЗАПРЕТ соединен с анодом четвертого диода, выход второго элемента ЗАПРЕТ соединен с катодом пятого диода, катод четвертого и анод пятого диодов через второй резистор соединен с шиной нулевого потенциала и с первым выводом конденсатора, второй вывод которого соединен с входом порогового элемента и анодом шестого диода, катод которого через третий резистор подключен к шине нулевого потенциала, в каждом разряде содержит дополнительньй RS-триггер, прямой выход которого соединен с прямым входом третьего элемента ЗАПРЕТ, R-вход с катодом второго диода, S-вход с входом элемента НЕ и с R-входами RS-триггеров ячеек памяти данного разряда. На чертеже представлена электрическая схема предлагаемого регистра сдвига (только два разряда). Регистр сдвига содержит первые RS-триггеры ячеек памяти 1-1, , вторые RS-триггеры ячеек памяти 2-1 , 2-2, первые элементы ЗАПРЕТ ячеек памяти 3-1, 3-2, вторые элементы ЗАПРЕТ ячеек памяти 4-1, 4-2, первые, элементы ЗАПРЕТ формирователей импульсов 5-1, 5-2, вторые элементы ЗАПРЕТ формирователей импульсов 6-1, 6-2, третьи элементы ЗАПРЕТ формирователей импульсов 7-1, 7-2, пороговые элементы 8-1, 8-2, элементы НЕ 9-1, 9-2, разделительные элементы на первых диодах 10-1, 10-2, вторых диодах 11-1, , третьих диодах 12-1, 12-2, четвертых диодах 13-1, 13-2, пятых диодах 14-1, 14-2, шестых диодах 15-1, 15-2, согласующие элементы на первых резисторах 16-1, 16-2, вторых резисторах 17-1, U-lj третьих резисторах 18-1, 18-2.,

31

накоп}1тельные элементы на конденсаторах 19-1, 19-2, дополнительные RS-триггеры 20-1, 20-2, шину питания 21, шину нулевого потенциала.22.

Регистр сдвига работает следующим образом.

Перед началом работы регистр сдвига подключен к источнику питания, затем на R-вход RS-триггера 20-1 подают кратковременный сигнал гашения.

В исходном состоянии конденсаторы 19-1, 19-2 заряжены, на выходах инверторов 9-1, 9-2 - единичные сигналы, элементы ЗАПРЕТ 3-1, 3-2 и 4-1 4-2 закрыты. Состояние RS-триггеров 1-1, 1-2 и 2-1, 2-2 может быть любым.

Лри поступлении первого кода навходных шинах появляется кодовая комбинация сигналов в виде единиц и нулей. При записи этой комбинации в ячейках предьщущего, третьего разряда (не показаны) на инверсный вход элемента 5-2 подается кратковременньй импульс, на его выходе появляется нулевой сигнал и через низкоомный резистор 18-2 и элемент 5-2 конденсатор 19-2 быстро разряжается. В момент исчезновения импульсного сигнала от зарядного тока конденсатора 19-2, протекакяцего через элемент 6-2, появляется импульсньй сигнал на выходе элемента 8-2, который одновременно подается на вход инвертора 9-2, инверсный вход элемента 7-2, S-вход и R-входы RS-триггеров 20-2 и 1-2, 2-2. Сигнал на выходе инвертора исчезает, и единицы кода с входных шин проходят на S-входы триггеров 1-2, 2-2, которые, однако, переключиться не могут, поскольку есть сигналы на их R-входах.

В момент завершения заряда конденсатора элемент 8-2 резко гасится, в результате чего на R-входах триггеров 1-2, 2-2 сигнал исчезает, а на S-входах - задерживается на время возбуждения инвертора 9-2 и гашения элементов 3-2, 4-2. Поэтому кодовая .комбинация с входных шин записывает;ся в триггеры 1-2, 2-2, причем вид этой комбинации может быть любым, ig частности комбинация может быть нулевой. В возбужденном состоянии оказывается и триггер 20-2, сигнализируя о наличии кода во втором разряде.

074

Выходной импульсньй сигнал элемен тов 8-2 поступает также на вход элемента 5-1, вследствие чего разряжается конденсатор 19-1. После исчезновения импульса такой же импульс формирует пороговый элемент 8-1, под действием которого уже рассмотренным образом кодовая комбинация, записанная во втором разряде, сдвигается

в первьй разряд, гасится триггер 20-2, возбуждается триггер 20-1, сигнализируя о наличии кода в первом разряде регистра сдвига.

Аналогично второй код записывается во второй разряд, при этом возбуждается триггер 20-2, сигнализируя о наличии второго кода во втором разряде регистра сдвига, причем конденсаторы 19-1, 19-2 оказьшаются разряженными. Сигнал с выхода элемента 8-1 сигнализирует о возможности съема первого кода потребителю.

,После изъятия первого кода потребителем (роль потребителя может

играть нулевой разряд того же вида) его сигналом, поданным на R-вход, триггер 20-1 гасится. В результате на инверсном входе элемента 6-1 сигнал запрета исчезает и конденсатор 19-1 заряжается. Элемент 8-1 формирует сигнал сдвига, действием которого второй код сдвигается из второго разряда в первьй, стано-. вясь теперь уже первым, т.е. готовым к изъятию потребителем. Этот же сигнал действует на R-вход триггера 20-2 и гасит его.

После завершения этого импульса элемент 8-2 формирует очередной импульс и третий код сдвигается из третьего разряда (не показан) во второй, становясь теперь уже вторым. При этом вновь возбуждается триггер 20-2 и те из триггеров 1-2, 2-1,

которым соответствует единица во входной кодовой комбинации.

В зависимости от порядка поступления и изъятия кодов возможны самые разнообразные варианты заполнения

регистра любыми кодами, включая нулевой; и в любом случае взаимодействие .элементов регистра в принципе остается тем, что указано вьш1е.

Способность регистра обслуживать коды с любыми комбинациями единиц и нулей, включая чисто нулевую комбина цию, обеспечиваемая наличием в разряде дополнительного RS-триггера, расшнряет область применения предложенного регистра. Поскольку после изъятия потребителем использованный код

в выходной ячейке памяти потребителем не гасится, его можно использовать многократно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Регистр сдвига | 1978 |

|

SU809383A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Устройство ассоциативного распознавания образов | 1985 |

|

SU1330644A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2012 |

|

RU2506598C1 |

| УСТРОЙСТВО КОДИРОВАНИЯ, ПРИЕМА И ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ ПО ДВУХПРОВОДНОЙ ЛИНИИ СВЯЗИ | 1996 |

|

RU2115240C1 |

| Система контурного управления промышленного робота | 1986 |

|

SU1430256A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ПЕРЕДАЧИ ПОСЛЕДОВАТЕЛЬНОСТИ СИГНАЛОВ | 2005 |

|

RU2299474C2 |

| Устройство для приема относительного биимпульсного сигнала | 1987 |

|

SU1425863A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ ЗАМКОМ | 2002 |

|

RU2209909C1 |

| УСТРОЙСТВО ПРОГРАММНОГО УПРАВЛЕНИЯ | 2004 |

|

RU2261470C1 |

РЕГИСТР СДВИГА, содержащий в каждом разряде ячейки памяти, каждая из которых состоит из R5-триггера и элемента ЗАПРЕТ, и формирователь импульсов сдвига, состоящий из трех элементов ЗАПРЕТ, порогового элемента, элемента НЕ, шести разделительных элементов на диодах, трех согласующих элементов на резисторах и накопительного элемента на конденсаторе, выход элемента ЗАПРЕТ каждой ячейки памяти соединен с 5 -входом R5-триггера данной ячейки памяти, прямой выход которого соединен с прямым входом элемента ЗАПРЕТ соответствующей ячейки памяти последующего разряда, инверсные входы элементов ЗАПРЕТ ячеек памяти каждого разряда соединены с выходом элемента НЕ формирователя импульсов сдвига данного разряда, в формирователе импульсов сдвига каждого разряда инверсный вход первого элемента ЗАПРЕТ соединен с катодом первого диода и с выходом порогового элемента формирователя импульсов сдвига предьщущего разряда, аноды первого, второго и третьего диодов соединены с инверсным входом второго элемента ЗАПРЕТ, прямые входы второго и третьего элементов ЗАПРЕТ через первый резистор подключены к шине питания, катод второго диода соединен с выходом порогового элемента формирователя импульсов сдвига последующего разряда, катод третьего диода соединен с выходом третьего элемента ЗАПРЕТ, инверсный вход которого соединен с выходом порогового элемента и с входом элемента НЕ формирователЯ импульсов сдвига данного г разряда, выход первого элемента ЗАПРЕТ соединен с анодом четвертого диода, выход второго элемента ЗАПРЕТ соединен с катодом пятого диода, катод четвертого и анод пятого диодов через второй резистор соединены с шиS е ной нулевого потенциала и с первым выводом конденсатора, второй вывод которого соединен с входом порогового элемента и анодом шестого диода, катод которого через третий резис д тор подключен к шине нулевого потенО циала, отличающийся v| тем, что, с целью расширения области применения регистра путем обеспечения возможности сдвига любых кодовых комбинаций, каждый разряд регистра содержит дополнительный RS -триггер, прямой выход которого соединен с прямым входом третьего элемента ЗАПРЕТ, R-вход - с катодом второго диода, 5-вход - с входом элемента НЕ и с R-входами R5 -триггеров ячеек памяти данного разряда.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Насос | 1917 |

|

SU13A1 |

Авторы

Даты

1984-08-30—Публикация

1982-03-11—Подача