Предлагаемое изобретение относится к области информационно-измерительной и вычислительной техники и может быть использовано в электроэнергетике для регистрации параметров переходных процессов изменения напряжения и тока в электрических сетях при авариях.

Известно устройство для сбора, преобразования и передачи результатов измерения параметров физической среды (Патент 2081452 РФ, МПК G06F 17/40. Устройство для сбора, преобразования и передачи результатов измерения параметров физической среды / Т.Г.Самхарадзе (РФ). - 1997, Бюл. №16), содержащее аналоговые измерительные датчики, блок управления с адресно-информационной и командной магистралью, генератор тактовых импульсов, коммутатор, блок управления коммутатором, канал управления опросом датчиков, аналого-цифровой преобразователь, буферное запоминающее устройство, блок регистров результата, формирователь передаваемой информации, узел передачи данных и канал ввода-вывода.

Недостатком указанного аналога являются его узкие функциональные возможности - аналог предназначен для наблюдения за процессом изменения параметров контролируемых величин, но не может быть использован для регистрации параметров переходных процессов изменения напряжения и тока в электрических сетях при авариях, а также на интервалах времени, предшествующих аварийной ситуации.

Наиболее близким техническим решением к предлагаемому является устройство для сбора, обработки и пакетной передачи результатов измерения параметров физической среды (Патент 2079881 РФ, МПК G06F 17/40. Устройство для сбора, обработки и пакетной передачи результатов измерения параметров физической среды / Т.Г.Самхарадзе (РФ). - 1997, Бюл. №14), содержащее первую и вторую группы аналоговых измерительных датчиков, первую и вторую группы аналого-цифровых преобразователей, блоки обработки данных первой группы и блоки обработки данных второй группы, первый и второй коммутаторы, первый и второй блоки управления коммутаторами, четыре оперативных запоминающих устройства, два буферных запоминающих устройства, два формирователя передаваемой информации, два узла передачи данных, канал ввода-вывода и управляющий вычислительный комплекс с адресно-информационной и командной магистралью.

Недостатком прототипа также являются узкие функциональные возможности - прототип предназначен для наблюдения за процессом изменения параметров контролируемых величин, но не может быть использован для регистрации параметров переходных процессов изменения напряжения и тока в электрических сетях при авариях, а также на интервалах времени, предшествующих аварийной ситуации.

Технические задачи, решаемые изобретением - расширение функциональных возможностей устройства за счет обеспечения возможности регистрации параметров переходных процессов изменения напряжения и тока в электрических сетях при авариях, а также на интервалах времени, предшествующих аварийной ситуации.

Указанные технические задачи (в первом варианте реализации предлагаемого технического решения) решаются тем, что в устройство для сбора, обработки и пакетной передачи результатов измерения параметров физической среды, содержащее микроконтроллер, первое, второе и третье оперативные запоминающие устройства, первый счетчик, первый и второй многоканальные коммутаторы, аналого-цифровой преобразователь, группу аналоговых датчиков, генератор тактовых импульсов, выходы которого соединены: третий - с тактовым входом первого счетчика, первый - с тактовым входом микроконтроллера, адресная шина которого соединена с объединенными адресными входами второго и третьего оперативных запоминающих устройств, входы управления записью которых подключены к шине управления микроконтроллера, к которой также подключен вход управления состоянием выходов выходных регистров третьего оперативного запоминающего устройства, информационный выход первого счетчика соединен с управляющим входом первого многоканального коммутатора, информационные входы которого подключены к выходам группы аналоговых датчиков, дополнительно введены постоянное запоминающее устройство, числовой компаратор, таймер, регистр, второй - пятый счетчики, первый - третий триггеры, формирователь модуля, нуль-орган, источник опорных напряжений, дешифратор, первый - четвертый одноканальные аналоговые коммутаторы, первый и второй аналоговые компараторы, элемент И-НЕ, первый - пятый элементы И, первый - четвертый элементы ИЛИ, первый - шестнадцатый одновибраторы, группа цифровых датчиков, выходы которых соединены с информационными входами второго многоканального коммутатора, управляющий вход которого объединен с первым входом числового компаратора, информационным входом регистра и группой старших разрядов адресного входа первого оперативного запоминающего устройства и подключен к информационному выходу первого счетчика, третий выход генератора тактовых импульсов соединен с объединенными первым входом четвертого элемента ИЛИ и инверсным входом первого одновибратора, выход которого соединен с объединенными управляющим входом четвертого одноканального аналогового коммутатора и инверсным входом двенадцатого одновибратора, выход которого соединен со входом запуска аналого-цифрового преобразователя, информационный вход которого подключен к выходу формирователя модуля, тактовый вход подключен ко второму выходу генератора тактовых импульсов, а информационный выход соединен с группой младших разрядов информационного входа первого оперативного запоминающего устройства, вход управления записью которого объединен с входом установки нуля пятого счетчика и входом второго одновибратора и подключен к выходу окончания цикла преобразования аналого-цифрового преобразователя, выход второго одновибратора соединен с объединенными третьим входом первого элемента И и инверсным входом третьего одновибратора, выходы которого соединены: прямой - с первым входом первого элемента ИЛИ, а инверсный - через четвертый одновибратор с первым входом элемента И-НЕ, второй вход которого подключен к выходу второго многоканального коммутатора, соединенному через пятый одновибратор со входом управления записью регистра, вход управления состоянием выхода которого подключен к шине управления микроконтроллера, выход регистра соединен с шиной данных микроконтроллера и вторым входом числового компаратора, выход которого «А=В» (где А и В - соответственно коды чисел на первом и втором входах числового компаратора) соединен с объединенными первыми входами первого, второго и третьего элементов И, выход элемента И-НЕ соединен со входом установки единицы первого триггера, прямой выход которого соединен с объединенными вторыми входами первого и четвертого элементов И и входом шестого одновибратора, инверсный выход которого соединен со входом первого вектора прерываний микроконтроллера и через седьмой одновибратор - со входом установки единицы второго триггера, прямой выход которого через пятый элемент И соединен с тактовым входом третьего триггера, выходы которого соединены соответственно через восьмой и девятый одновибраторы со вторыми входами второго и третьего элементов И, выход которого соединен с тактовым входом второго счетчика и вторыми входами второго и первого элементов ИЛИ, выход которого соединен с тактовым входом третьего счетчика и через четвертый элемент И с первым входом второго элемента ИЛИ, выход которого соединен с тактовым входом четвертого счетчика, информационный выход которого соединен с адресной шиной микроконтроллера, вход управления состоянием информационного выхода подключен к шине управления микроконтроллера, а выход переноса соединен со входом десятого одновибратора, выходы которого соединены: прямой - со входом второго вектора прерываний микроконтроллера и входом установки нуля четвертого счетчика, инверсный - со входом установки нуля первого триггера, выход переноса второго счетчика соединен со входом одиннадцатого одновибратора, выходы которого соединены: прямой - со входом установки нуля второго счетчика, инверсный - со входами установки нуля второго и третьего триггеров, информационный выход третьего счетчика соединен с группой младших разрядов адресного входа первого оперативного запоминающего устройства, информационный выход которого соединен с информационным входом второго оперативного запоминающего устройства, информационный выход которого соединен с информационным входом третьего оперативного запоминающего устройства, информационный выход которого соединен с шиной данных микроконтроллера, соединенной с информационным входом постоянного запоминающего устройства, адресный вход которого подключен к адресной шине микроконтроллера, а вход управления записью подключен к шине управления микроконтроллера, выход первого элемента И через третий элемент ИЛИ соединен со входом управления записью второго оперативного запоминающего устройства, тактовый вход таймера объединен с вторым входом пятого элемента И и подключен к первому выходу генератора тактовых импульсов, вход захвата и вход управления состоянием выходов выходных регистров таймера подключены к шине управления микроконтроллера, а информационный выход таймера соединен с шиной данных микроконтроллера, выход первого многоканального коммутатора соединен с объединенными информационными входами нуль-органа и формирователя модуля, выход которого через четвертый одноканальный аналоговый коммутатор соединен с объединенными вторыми входами первого и второго аналоговых компараторов, первые входы которых подключены соответственно ко второму и первому выходам источника опорных напряжений, первый - третий выходы которого соединены соответственно с информационными входами первого - третьего одноканальных аналоговых коммутаторов, выходы которых объединены и соединены со входом опорного напряжения аналого-цифрового преобразователя, а управляющие входы первого - третьего одноканальных аналоговых коммутаторов подключены соответственно к первому - третьему выходам дешифратора, выходы первого и второго аналоговых компараторов через последовательно соединенные попарно тринадцатый и четырнадцатый, а также пятнадцатый и шестнадцатый одновибраторы связаны соответственно со вторым и третьим входами четвертого элемента ИЛИ, выход которого соединен с тактовым входом пятого счетчика, выход которого соединен с объединенными входом дешифратора и группой средних разрядов информационного входа первого оперативного запоминающего устройства, старший разряд которого объединен с первым управляющим входом формирователя модуля и подключен к прямому выходу нуль-органа, инверсный выход которого соединен со вторым управляющим входом формирователя модуля.

Указанные технические задачи (во втором варианте реализации предлагаемого технического решения) решаются тем, что в устройство для сбора, обработки и пакетной передачи результатов измерения параметров физической среды, содержащее микроконтроллер, первое, второе и третье оперативные запоминающие устройства, первый счетчик, первый и второй многоканальные коммутаторы, аналого-цифровой преобразователь, группу аналоговых датчиков, генератор тактовых импульсов, выходы которого соединены: третий - с тактовым входом первого счетчика, первый - с тактовым входом микроконтроллера, адресная шина которого соединена с объединенными адресными входами второго и третьего оперативных запоминающих устройств, входы управления записью которых подключены к шине управления микроконтроллера, к которой также подключен вход управления состоянием выходов выходных регистров третьего оперативного запоминающего устройства, информационный выход первого счетчика соединен с управляющим входом первого многоканального коммутатора, информационные входы которого подключены к выходам группы аналоговых датчиков, дополнительно введены постоянное запоминающее устройство, источник опорных напряжений, первый - третий одноканальные аналоговые коммутаторы, первый и второй числовые компараторы, второй - пятый счетчики, первый - третий триггеры, формирователь модуля, нуль-орган, таймер, регистр, дешифратор, элемент И-НЕ, первый - шестой элементы И, первый - пятый элементы ИЛИ, первый - двенадцатый одновибраторы, блок задания кода границы, группа цифровых датчиков, выходы которых соединены с информационными входами второго многоканального коммутатора, управляющий вход которого объединен с первым входом первого числового компаратора, информационным входом регистра и группой старших разрядов адресного входа первого оперативного запоминающего устройства и подключен к информационному выходу первого счетчика, третий выход генератора тактовых импульсов соединен с первым входом четвертого элемента ИЛИ, выход которого соединен с тактовым входом пятого счетчика и через первый одновибратор - с входом запуска аналого-цифрового преобразователя, информационный вход которого подключен к выходу формирователя модуля, тактовый вход подключен ко второму выходу генератора тактовых импульсов, а информационный выход соединен с объединенными вторым входом второго числового компаратора и группой младших разрядов информационного входа первого оперативного запоминающего устройства, вход управления записью которого объединен с входом установки нуля пятого счетчика и входом второго одновибратора и через шестой элемент И подключен к выходу окончания цикла преобразования аналого-цифрового преобразователя, выход второго одновибратора соединен с объединенными третьим входом первого элемента И и инверсным входом третьего одновибратора, выходы которого соединены: прямой - с объединенными входом установки нуля аналого-цифрового преобразователя и первым входом первого элемента ИЛИ, а инверсный - через четвертый одновибратор с первым входом элемента И-НЕ, второй вход которого подключен к выходу второго многоканального коммутатора, соединенному через пятый одновибратор со входом управления записью регистра, вход управления состоянием выхода которого подключен к шине управления микроконтроллера, выход регистра соединен с шиной данных микроконтроллера и вторым входом первого числового компаратора, выход которого «А=В» (где А и В - соответственно коды чисел на первом и втором входах первого и второго числовых компараторов) соединен с объединенными первыми входами первого, второго и третьего элементов И, выход элемента И-НЕ соединен со входом установки единицы первого триггера, прямой выход которого соединен с объединенными вторыми входами первого и четвертого элементов И и входом шестого одновибратора, инверсный выход которого соединен со входом первого вектора прерываний микроконтроллера и через седьмой одновибратор - со входом установки единицы второго триггера, прямой выход которого через пятый элемент И соединен с тактовым входом третьего триггера, выходы которого соединены соответственно через восьмой и девятый одновибраторы со вторыми входами второго и третьего элементов И, выход которого соединен с тактовым входом второго счетчика и вторыми входами второго и первого элементов ИЛИ, выход которого соединен с тактовым входом третьего счетчика и через четвертый элемент И с первым входом второго элемента ИЛИ, выход которого соединен с тактовым входом четвертого счетчика, информационный выход которого соединен с адресной шиной микроконтроллера, вход управления состоянием информационного выхода подключен к шине управления микроконтроллера, а выход переноса соединен со входом десятого одновибратора, выходы которого соединены: прямой - со входом второго вектора прерываний микроконтроллера и входом установки нуля четвертого счетчика, инверсный - со входом установки нуля первого триггера, выход переноса второго счетчика соединен со входом одиннадцатого одновибратора, выходы которого соединены: прямой - со входом установки нуля второго счетчика, инверсный - со входами установки нуля второго и третьего триггеров, информационный выход третьего счетчика соединен с группой младших разрядов адресного входа первого оперативного запоминающего устройства, информационный выход которого соединен с информационным входом второго оперативного запоминающего устройства, информационный выход которого соединен с информационным входом третьего оперативного запоминающего устройства, информационный выход которого соединен с шиной данных микроконтроллера, соединенной с информационным входом постоянного запоминающего устройства, адресный вход которого подключен к адресной шине микроконтроллера, а вход управления записью подключен к шине управления микроконтроллера, выход первого элемента И через третий элемент ИЛИ соединен со входом управления записью второго оперативного запоминающего устройства, тактовый вход таймера объединен с вторым входом пятого элемента И и подключен к первому выходу генератора тактовых импульсов, вход захвата и вход управления состоянием выходов выходных регистров таймера подключены к шине управления микроконтроллера, а информационный выход таймера соединен с шиной данных микроконтроллера, выход пятого счетчика соединен с объединенными входом дешифратора и группой средних разрядов информационного входа первого оперативного запоминающего устройства, старший разряд которого объединен с первым управляющим входом формирователя модуля и подключен к прямому выходу нуль-органа, инверсный выход которого соединен со вторым управляющим входом формирователя модуля, информационный вход которого объединен с входом нуль-органа и подключен к выходу первого многоканального коммутатора, первый - третий выходы источника опорных напряжений соединены соответственно с информационными входами первого - третьего одноканальных аналоговых коммутаторов, выходы которых объединены и соединены со входом опорного напряжения аналого-цифрового преобразователя, а управляющие входы первого - третьего одноканальных аналоговых коммутаторов подключены соответственно к первому - третьему выходам дешифратора, выход блока задания кода границы соединен с первым входом второго числового компаратора, выходы которого соединены: «А<В» - через двенадцатый одновибратор со вторым входом четвертого элемента ИЛИ, «А=В» и «А>В» - со вторым и третьим входами пятого элемента ИЛИ, первый вход которого подключен к первому выходу дешифратора, а выход пятого элемента ИЛИ соединен со вторым входом шестого элемента И.

Формирователь модуля содержит инвертор, четвертый и пятый одноканальные аналоговые коммутаторы, выходы которых объединены и соединены с выходом формирователя модуля, информационный вход которого соединен с объединенными входами четвертого одноканального аналогового коммутатора и инвертора, выход которого соединен со входом пятого одноканального аналогового коммутатора, первый и второй управляющие входы формирователя модуля соединены соответственно с управляющими входами четвертого и пятого одноканальных аналоговых коммутаторов.

Существенным отличием предлагаемого технического решения в различных вариантах его реализации является введение дополнительных элементов:

1) постоянного запоминающего устройства, формирователя модуля, нуль-органа, источника опорных напряжений, дешифратора, цифровых датчиков, первого - третьего одноканальных аналоговых коммутаторов, первого и второго аналоговых компараторов, таймера, регистра, числового компаратора, второго - пятого счетчиков, первого - третьего триггеров, элемента И-НЕ, первого - пятого элементов И, первого - четвертого элементов ИЛИ, первого - шестнадцатого одновибраторов;

2) постоянного запоминающего устройства, формирователя модуля, нуль-органа, источника опорных напряжений, дешифратора, цифровых датчиков, первого - третьего одноканальных аналоговых коммутаторов, таймера, регистра, первого и второго числовых компараторов, второго - пятого счетчиков, первого - третьего триггеров, элемента И-НЕ, первого - шестого элементов И, первого - пятого элементов ИЛИ, блока задания кода границы, первого - одиннадцатого одновибраторов.

К существенным отличиям предлагаемого технического решения также относятся организация его новой структуры и введение новых связей между элементами. Совокупность элементов и связей между ними обеспечивает достижение положительного эффекта - расширения функциональных возможностей за счет обеспечения возможности регистрации параметров переходных процессов изменения напряжения и тока в электрических сетях при авариях, а также на интервалах времени, предшествующих аварийной ситуации.

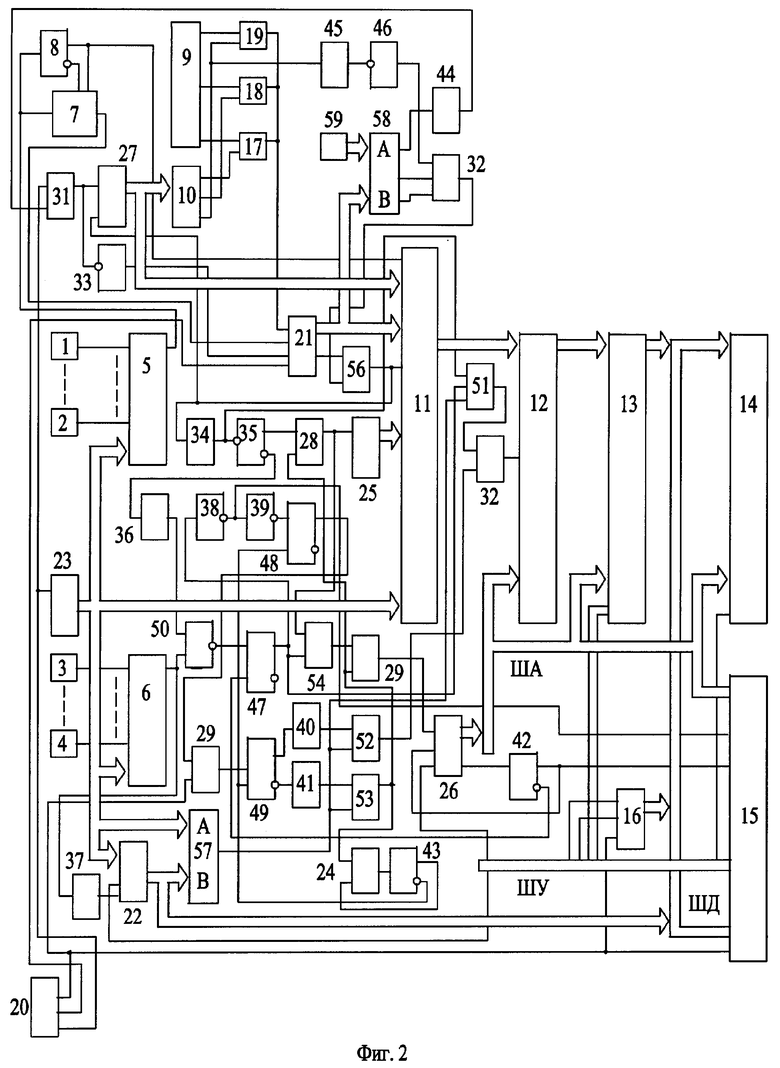

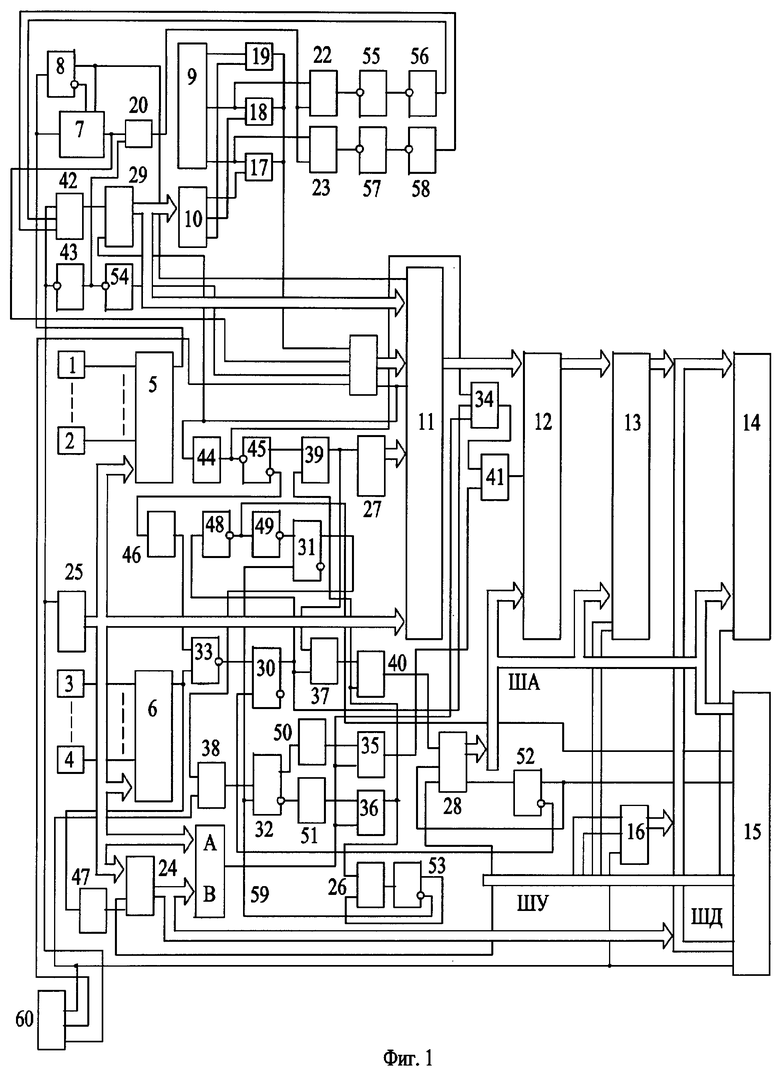

Схемы вариантов реализации регистратора параметров аварийных ситуаций в электрических сетях повышенной точности представлены: на фиг.1 - первого варианта, на фиг.2 - второго варианта; на фиг.3 приведен один из вариантов реализации формирователя модуля 7.

Схема первого варианта реализации регистратора (фиг.1) содержит группу аналоговых датчиков (АД) 1-2, группу цифровых датчиков (ЦД) 3-4, многоканальные первый аналоговый 5 (МАК) и второй цифровой 6 (МЦК) коммутаторы, формирователь 7 модуля (ФМ), нуль-орган (НО) 8, источник 9 опорных напряжений (ИОН), дешифратор 10, первое 11, второе 12 и третье 13 оперативные запоминающие устройства (ОЗУ), постоянное запоминающее устройство (ПЗУ) 14, микроконтроллер (МК) 15, таймер 16, первый - четвертый одноканальные аналоговые коммутаторы (OAK) 17-20, аналого-цифровой преобразователь (АЦП) 21, первый 22 и второй 23 аналоговые компараторы (АК), регистр 24, первый - пятый счетчики 25-29, первый -третий триггеры 30-32, элемент И-НЕ 33, первый - пятый элементы И 34-38, первый - четвертый элементы ИЛИ 39-42, первый - шестнадцатый одновибраторы

43-58, числовой компаратор (ЧК) 59, генератор 60 тактовых импульсов (ГТИ).

Выходы группы аналоговых датчиков 1-2 соединены с информационными входами первого многоканального коммутатора 5, выход которого соединен с объединенными информационными входами нуль-органа 8 и формирователя 7 модуля, выход которого через аналого-цифровой преобразователь 21 соединен с группой младших разрядов информационного входа первого оперативного запоминающего устройства 11, информационный выход которого соединен с информационным входом второго оперативного запоминающего устройства 12, информационный выход которого соединен с информационным входом третьего оперативного запоминающего устройства 13, информационный выход которого соединен с шиной данных микроконтроллера 15, соединенной с информационным входом постоянного запоминающего устройства 14, вход управления записью которого подключен к шине управления микроконтроллера 15, соединенной также со входами управления состоянием выходов регистра 24, таймера 16, четвертого счетчика 28 и выходных регистров третьего оперативного запоминающего устройства 13, входами управления записью третьего оперативного запоминающего устройств 13 и постоянного запоминающего устройства 14, а также со входом захвата таймера 16, информационный выход которого соединен с шиной данных микроконтроллера 15, а тактовый вход объединен с тактовым входом микроконтроллера 15 и вторым входом пятого элемента И 38 и подключен к первому выходу генератора 60 тактовых импульсов, второй выход которого соединен с тактовым входом аналого-цифрового преобразователя 21, а третий выход соединен с объединенными первым входом четвертого элемента ИЛИ 42, инверсным входом первого одновибратора 43 и тактовым входом первого счетчика 25, информационный выход которого соединен с управляющими входами первого 5 и второго 6 многоканальных коммутаторов, с группой старших разрядов адресного входа первого оперативного запоминающего устройства 11, первым входом числового компаратора 59 и информационным входом регистра 24, выход которого соединен с шиной данных микроконтроллера 15 и вторым входом числового компаратора 59, выход которого «А=В» (где А и В - соответственно коды чисел на первом и втором входах числового компаратора 59) соединен с объединенными первыми входами первого 34, второго 35 и третьего 36 элементов И, выходы группы цифровых датчиков 3-4 соединены с информационными входами второго многоканального коммутатора 6, выход которого соединен со вторым входом элемента И-НЕ 33 и через пятый одновибратор 47 со входом управления записью регистра 24, выход элемента И-НЕ 33 соединен со входом установки единицы первого триггера 30, прямой выход которого соединен с объединенными вторыми входами первого 34 и четвертого 37 элементов И и входом шестого одновибратора 48, инверсный выход которого соединен со входом первого вектора прерываний микроконтроллера 15 и через седьмой одновибратор 49 - со входом установки единицы второго триггера 31, прямой выход которого через пятый элемент И 38 соединен с тактовым входом третьего триггера 32, выходы которого соединены соответственно через восьмой 50 и девятый 51 одновибраторы со вторыми входами второго 35 и третьего 36 элементов И, выход которого соединен с тактовым входом второго счетчика 26 и вторыми входами второго 40 и первого 39 элементов ИЛИ, выход которого соединен с тактовым входом третьего счетчика 27 и через четвертый элемент И 37 с первым входом второго элемента ИЛИ 40, выход которого соединен с тактовым входом четвертого счетчика 28, информационный выход которого соединен с адресной шиной микроконтроллера 15, а выход переноса соединен со входом десятого одновибратора 52, выходы которого соединены: прямой - со входом второго вектора прерываний микроконтроллера 15 и входом установки нуля четвертого счетчика 28, инверсный - со входом установки нуля первого триггера 30, выход переноса второго счетчика 26 соединен со входом одиннадцатого одновибратора 53, выходы которого соединены: прямой - со входом установки нуля второго счетчика 26, инверсный - со входами установки нуля второго 31 и третьего 32 триггеров, информационный выход третьего счетчика 27 соединен с группой младших разрядов адресного входа первого оперативного запоминающего устройства 11, выход первого одновибратора 43 соединен с объединенными управляющим входом четвертого одноканального аналогового коммутатора 20 и инверсным входом двенадцатого одновибратора 54, выход которого соединен со входом запуска аналого-цифрового преобразователя 21, выход окончания цикла преобразования которого соединен с объединенными входом управления записью первого оперативного запоминающего устройства 11, входом установки нуля пятого счетчика 29 и входом второго одновибратор 44, выход которого соединен с объединенными третьим входом первого элемента И 34 и инверсным входом третьего одновибратора 45, выходы которого соединены: прямой - с первым входом первого элемента ИЛИ 39, а инверсный - через четвертый одновибратор 46 с первым входом элемента И-НЕ 33, выход четвертого элемента ИЛИ 42 соединен с тактовым входом пятого счетчика 29, выход которого соединен с объединенными входом дешифратора 10 и группой средних разрядов информационного входа первого оперативного запоминающего устройства 11, старший разряд которого объединен с первым управляющим входом формирователя 7 модуля и подключен к прямому выходу нуль-органа 8, инверсный выход которого соединен со вторым управляющим входом формирователя 7 модуля, выход которого через четвертый одноканальный аналоговый коммутатор 20 соединен с объединенными вторыми входами первого 22 и второго 23 аналоговых компараторов, первые входы которых подключены соответственно ко второму и первому выходам источника 9 опорных напряжений, первый - третий выходы которого соединены соответственно с информационными входами первого - третьего одноканальных аналоговых коммутаторов 17-19, выходы которых объединены и соединены со входом опорного напряжения аналого-цифрового преобразователя 21, а управляющие входы первого - третьего одноканальных аналоговых коммутаторов 17 - 19 подключены соответственно к первому - третьему выходам дешифратора 10, выходы первого 22 и второго 23 аналоговых компараторов через последовательно соединенные попарно тринадцатый 55 и четырнадцатый 56, а также пятнадцатый 57 и шестнадцатый 58 одновибраторы связаны соответственно со вторым и третьим входами четвертого элемента ИЛИ 42, выход первого элемента И 34 через третий элемент ИЛИ 41 соединен со входом управления записью второго оперативного запоминающего устройства 12, адресная шина микроконтроллера 15 соединена с объединенными адресными входами второго 12 и третьего 13 оперативных запоминающих устройств и постоянного запоминающего устройства 14.

Схема второго варианта реализации регистратора (фиг.2) содержит группу аналоговых датчиков (АД) 1-2, группу цифровых датчиков (ЦД) 3-4, многоканальные первый аналоговый 5 (МАК) и второй цифровой 6 (МЦК) коммутаторы, формирователь 7 модуля (ФМ), нуль-орган (НО) 8, источник 9 опорных напряжений (ИОН), дешифратор 10, первое 11, второе 12 и третье 13 оперативные запоминающие устройства (ОЗУ), постоянное запоминающее устройство (ПЗУ) 14, микроконтроллер (МК) 15, таймер 16, первый - третий одноканальные аналоговые коммутаторы (OAK) 17-19, генератор 20 тактовых импульсов (ГТИ), аналого-цифровой преобразователь (АЦП) 21, регистр 22, первый - пятый счетчики 23 - 27, первый - пятый элементы ИЛИ 28-32, первый - четырнадцатый одновибраторы 33-46, первый - третий триггеры 47-49, элемент И-НЕ 50, первый - шестой элементы И 51-56, первый 57 и второй 58 числовые компараторы (ЧК), блок 59 задания кода границы (БЗКГ).

Выходы группы аналоговых датчиков 1-2 соединены с информационными входами первого многоканального коммутатора 5, выход которого соединен с объединенными информационными входами нуль-органа 8 и формирователя 7 модуля, выход которого через аналого-цифровой преобразователь 21 соединен с объединенными вторым входом второго числового компаратора 58 и группой младших разрядов информационного входа первого оперативного запоминающего устройства 11, информационный выход которого соединен с информационным входом второго оперативного запоминающего устройства 12, информационный выход которого соединен с информационным входом третьего оперативного запоминающего устройства 13, информационный выход которого соединен с шиной данных микроконтроллера 15, соединенной с информационным входом постоянного запоминающего устройства 14, вход управления записью которого подключен к шине управления микроконтроллера 15, соединенной также со входами управления состоянием выходов регистра 22, таймера 16, четвертого счетчика 26 и выходных регистров третьего оперативного запоминающего устройства 13, входами управления записью третьего оперативного запоминающего устройств 13 и постоянного запоминающего устройства 14, а также со входом захвата таймера 16, информационный выход которого соединен с шиной данных микроконтроллера 15, а тактовый вход объединен с тактовым входом микроконтроллера 15 и вторым входом пятого элемента И 55 и подключен к первому выходу генератора 20 тактовых импульсов, второй выход которого соединен с тактовым входом аналого-цифрового преобразователя 21, а третий выход соединен с объединенными первым входом четвертого элемента ИЛИ 31 и тактовым входом первого счетчика 23, информационный выход которого соединен с управляющими входами первого 5 и второго 6 многоканальных коммутаторов, с группой старших разрядов адресного входа первого оперативного запоминающего устройства 11, первым входом первого числового компаратора 57 и информационным входом регистра 22, выход которого соединен с шиной данных микроконтроллера 15 и вторым входом первого числового компаратора 57, выход которого «А=В» (где А и В - соответственно коды чисел на первом и втором входах первого и второго числовых компараторов 57 и 58) соединен с объединенными первыми входами первого 51, второго 52 и третьего 53 элементов И, выходы группы цифровых датчиков 3-4 соединены с информационными входами второго многоканального коммутатора 6, выход которого соединен со вторым входом элемента И-НЕ 50 и через пятый одновибратор 37 со входом управления записью регистра 22, выход элемента И-НЕ 50 соединен со входом установки единицы первого триггера 44, прямой выход которого соединен с объединенными вторыми входами первого 51 и четвертого 54 элементов И и входом шестого одновибратора 38, инверсный выход которого соединен со входом первого вектора прерываний микроконтроллера 15 и через седьмой одновибратор 39 - со входом установки единицы второго триггера 48, прямой выход которого через пятый элемент И 55 соединен с тактовым входом третьего триггера 49, выходы которого соединены соответственно через восьмой 40 и девятый 41 одновибраторы со вторыми входами второго 52 и третьего 53 элементов И, выход которого соединен с тактовым входом второго счетчика 24 и вторыми входами второго 29 и первого 28 элементов ИЛИ, выход которого соединен с тактовым входом третьего счетчика 25 и через четвертый элемент И 54 с первым входом второго элемента ИЛИ 29, выход которого соединен с тактовым входом четвертого счетчика 26, информационный выход которого соединен с адресной шиной микроконтроллера 15, а выход переноса соединен со входом десятого одновибратора 42, выходы которого соединены: прямой - со входом второго вектора прерываний микроконтроллера 15 и входом установки нуля четвертого счетчика 26, инверсный - со входом установки нуля первого триггера 47, выход переноса второго счетчика 24 соединен со входом одиннадцатого одновибратора 43, выходы которого соединены: прямой - со входом установки нуля второго счетчика 24, инверсный - со входами установки нуля второго 48 и третьего 49 триггеров, информационный выход третьего счетчика 25 соединен с группой младших разрядов адресного входа первого оперативного запоминающего устройства 11, выход четвертого элемента ИЛИ 31 соединен с объединенными тактовым входом пятого счетчика 27 и инверсным входом первого одновибратора 33, выход которого соединен со входом запуска аналого-цифрового преобразователя 21, выход окончания цикла преобразования которого соединен с первым входом шестого элемента И 56, выход которого соединен с объединенными входом управления записью первого оперативного запоминающего устройства 11, входом установки нуля пятого счетчика 27 и входом второго одновибратор 34, выход которого соединен с объединенными третьим входом первого элемента И 51 и инверсным входом третьего одновибратора 35, выходы которого соединены: прямой - с объединенными первым входом первого элемента ИЛИ 28 и входом установки нуля аналого-цифрового преобразователя 21, а инверсный - через четвертый одновибратор 36 с первым входом элемента И-НЕ 50, выход четвертого элемента ИЛИ 31 соединен с тактовым входом пятого счетчика 27, выход которого соединен с объединенными входом дешифратора 10 и группой средних разрядов информационного входа первого оперативного запоминающего устройства 11, старший разряд которого объединен с первым управляющим входом формирователя 7 модуля и подключен к прямому выходу нуль-органа 8, инверсный выход которого соединен со вторым управляющим входом формирователя 7 модуля, первый - третий выходы источника 9 опорных напряжений соединены соответственно с информационными входами первого - третьего одноканальных аналоговых коммутаторов 17-19, выходы которых объединены и соединены со входом опорного напряжения аналого-цифрового преобразователя 21, а управляющие входы первого - третьего одноканальных аналоговых коммутаторов 17-19 подключены соответственно к первому - третьему выходам дешифратора 10, выход блока 59 задания кода границы соединен с первым входом второго числового компаратора 58, выходы которого соединены: «А<В» - через двенадцатый одновибратор 44 со вторым входом четвертого элемента ИЛИ 31, «А=В» и «А>В» - со вторым и третьим входами пятого элемента ИЛИ 32, первый вход которого через последовательно соединенные тринадцатый 45 и четырнадцатый 46 одновибраторы подключен к третьему выходу дешифратора 10, а выход пятого элемента ИЛИ 32 соединен со вторым входом шестого элемента И 56, выход первого элемента И 34 через третий элемент ИЛИ 30 соединен со входом управления записью второго оперативного запоминающего устройства 12, адресная шина микроконтроллера 15 соединена с объединенными адресными входами второго 12 и третьего 13 оперативных запоминающих устройств и постоянного запоминающего устройства 14.

Схема формирователя 7 модуля (фиг.3) содержит инвертор 61, четвертый 62 и пятый 63 одноканальные аналоговые коммутаторы, выходы которых объединены и соединены с выходом формирователя 7 модуля, информационный вход которого соединен с объединенными входами четвертого одноканального аналогового коммутатора 62 и инвертора 61, выход которого соединен со входом пятого одноканального аналогового коммутатора 63, первый и второй управляющие входы формирователя 7 модуля соединены соответственно с управляющими входами четвертого 62 и пятого 63 одноканальных аналоговых коммутаторов.

Генератор 60 выполнен кварцевым, его частота равняется 1-20 МГц (в зависимости от необходимой точности). Частота импульсов на первом выходе ГТИ 60 является максимальной, на втором она ниже, не третьем еще ниже. Частоты могут отличаться на несколько порядков. Счетчики 26 и 27 имеют одинаковую емкость, которая равна числу выборок предаварийного процесса. Емкость счетчика 28 равняется числу выборок, получаемых за суммарное время аварийного и предаварийного процессов.

Таймер 16, представляющий собой часы реального времени, предназначен для регистрации астрономического времени аварии с точностью до секунд, он позволяет зафиксировать год, месяц, дату, часы, минуты и секунды начала аварии.

На выходах ИОН 9 задаются напряжения (например): на первом (нижнем) - 0,1023 В, на втором - 1,023 В, на третьем - 10,23 В. Соотношение этих напряжений 1:10:100.

Аналоговые компараторы 22 и 23 имеют соответственно неинвертирующие и инвертирующие входы.

Первый вариант регистратора (фиг.1) работает следующим образом.

Информация непрерывно поступает от аналоговых датчиков 1-2, представляющих собой измерительные трансформаторы тока и напряжения. Выходы АД 1-2 поочередно подключаются через последовательно соединенные МАК 5 и ФМ 7 ко входу АЦП 21 в зависимости от кода на выходе счетчика 25. Например, при коде 0000 на выходе счетчика 25 (соответствующем контролю информации в первом канале с датчиками АД 1 и ЦД 3) ко входу АЦП 21 подключен выход АД 1.

С выхода МАК 5 на вход ФМ 7 и НО 8 поступают положительные и отрицательные полуволны синусоидальных сигналов. При положительной полуволне на прямом выходе НО 8 присутствует единица, на инверсном - ноль. Единичное напряжение с прямого выхода НО 8 прикладывается к управляющему входу коммутатора 62 (фиг.3) и открывает его - входное положительное напряжение после прохождения через коммутатор 62 без изменений появляется на выходе ФМ 7.

При отрицательной полуволне, наоборот, на прямом выходе НО 8 присутствует ноль, на инверсном - единица. В этом случае коммутатор 62 закрывается, а коммутатор 63 открывается и пропускает на выход ФМ 7 инвертированное инвертором 61 входное напряжение - в результате на выходе ФМ 7 также присутствует положительное напряжение.

По заднему фронту очередного импульса с третьего выхода ГТИ 60 запускается одновибратор 43, который задним фронтом своего выходного импульсом запускает одновибратор 54, а последний приводит в действие АЦП 21. Однако, учитывая достаточно большую длительность выходного импульса одновибратора 43 (которая превышает суммарную длительность выходных импульсов одновибраторов 55 - 58), до запуска АЦП 21 предварительно происходит выбор масштаба преобразования, который осуществляется следующим образом.

Выходной единичный импульс одновибратора 43 воздействует на управляющий вход коммутатора 20 и открывает его - в результате напряжение с выхода ФМ 7 прикладывается ко вторым входам компараторов 22 и 23, которые до этого момента находились в сработавшем состоянии - на их выходах присутствовали единичные напряжения.

По заднему фронту очередного импульса со второго выхода ГТИ 60 без задержки срабатывает счетчик 29, на выходе которого появляется код 01. При этом входном коде дешифратор 10 вырабатывает на первом выходе управляющее единичное напряжение, которое открывает коммутатор 17 - ко входу опорного напряжения АЦП 21 прикладывается напряжение 0,1023 В.

Если модуль входного сигнала при этом больше 1,023 В, то оба компаратора 22 и 23 отпускают - сигналы на их выходах переходят из единичных в нулевые, запуская цепи одновибраторов 55-56 и 57-58. Длительность выходного импульса одновибратора 55 с запасом превышает суммарную длительность выходных импульсов одновибраторов 57 и 58, поэтому счетчик 29 срабатывает дважды и его выходной код становится равным 11. При этом входном коде дешифратор 10 вырабатывает на третьем выходе управляющее единичное напряжение, которое открывает коммутатор 19 - ко входу опорного напряжения АЦП 21 прикладывается напряжение 10,23 В. В этом случае АЦП 21 запускается при максимальном масштабе 100, код которого 11 задается на выходе счетчика 29.

В том случае если модуль входного сигнала 1,023>/Uвх/>0,1023 В, то отпускает компаратор 23, запуская цепь одновибраторов 57-58. Выходной импульс последнего переводит счетчик 29 из состояния 01 в состояние 10, при котором управляющее единичное напряжение появляется на втором выходе дешифратора 10 - открывается коммутатор 18 - ко входу опорного напряжения АЦП 21 прикладывается напряжение 1,023 В. В этом случае масштаб преобразования равен 10.

В том случае если /Uвх/<0,1023 В, то оба компаратора 22 и 23 остаются в единичном состоянии, цепи одновибраторов 55-56 и 57-58 не запускаются, счетчик 29 не срабатывает и его выходной код остается равным 01. Ко входу опорного напряжения АЦП 21 через коммутатор 19 приложено напряжение 0,1023 В - в этом случае масштаб преобразования равен 1.

После окончания операции выбора масштаба АЦП 21 запускается импульсом одновибратора 54.

Импульсом с выхода окончания цикла преобразования АЦП 21 двоичный код очередной выборки процесса с выхода АД 1 (старший разряд информационного кода формируется на прямом выходе НО 8, группа средних разрядов кода задается на выходе счетчика 29, группу младших разрядов кода представляет непосредственно информационный код на выходе АЦП 21) записывается в ячейку ОЗУ 11 по адресу, формируемому счетчиками 25 и 27, например, 00000010 (старшая часть адресного кода 0000 формируется счетчиком 25, а младшая часть 0010 - счетчиком 27).

Импульс с выхода окончания цикла преобразования АЦП 21 также обнуляет содержимое счетчика 29 (приводя схему выбора масштаба преобразования в исходное состояние) и запускает одновибратор 44. По заднему фронту выходного импульса последнего запускается одновибратор 45, выходной импульс которого, после прохождения через элемент ИЛИ 39, увеличивает на единицу содержимое счетчика 27 (оно становится равным 0011), подготавливая к записи информации ячейку ОЗУ 11 с адресом 00000011 при следующей выборке процесса с выхода АД 1.

По заднему фронту импульса с инверсного выхода одновибратора 45 запускается одновибратор 46, выходной импульс которого поступает на первый вход элемента И-НЕ 33.

При отсутствии аварии в первом канале с датчиком АД 1 соответствующий ему цифровой датчик ЦД 3 имеет на выходе нулевое напряжение. Это напряжение через коммутатор 6 прикладывается ко второму входу элемента И-НЕ 33 и блокирует его для прохождения импульсов с выхода одновибратора 46.

В случае аварии в первом канале на выходе ЦД 3 появляется единичное напряжение, которое прикладывается ко второму входу элемента И-НЕ 33 и запускает одновибратор 47. Последний записывает код 0000 с выхода счетчика 25 в регистр 24, выходной код которого поступает на ШД коммутатора 15 и прикладывается ко второму входу ЧК 59, к первому входу которого также приложен код 0000 с выхода счетчика 25.

Поскольку коды на первом и втором входах ЧК 59 выравниваются, то на его выходе «А=В» появляется единичное напряжение, которое прикладывается ко вторым входам элементов И 34-36.

В случае аварии импульс с выхода одновибратора 46 проходит через элемент И-НЕ 33 и переводит в единичное состояние триггер 30, напряжение с выхода которого запускает одновибратор 48, выходной импульс которого, после прохождения через одновибратор 49, переводит в единичное состояние триггер 31 и поступает на вход первого вектора прерываний микроконтроллера 15.

По первому вектору прерываний микроконтроллер 15 переходит на выполнение первого программного блока, который осуществляет запись номера канала (0000) и времени начала аварии в этом канале (код времени с выхода таймера 16) в области памяти ПЗУ 14, отведенной для регистрации данных по одной аварии. Выполнение программы в МК 15 осуществляется параллельно с работой аппаратной части регистратора. При этом, в первую очередь, путем воздействия на вход захвата таймера 16 импульсом из ШУ МК 15 время аварии заносится в выходные регистры таймера 16. Затем номер канала 0000, в котором произошла авария, записывается из регистра 17 в ПЗУ 14, после чего выходы регистра 17 переходят в пассивное (так называемое третье) состояние. Далее выходы выходных регистров таймера 16 поочередно переходят (в зависимости от выбранного формата данных в ПЗУ 14) в активное состояние и время аварии фиксируется в ПЗУ 14 с точностью до секунды.

Учитывая, что емкость счетчика 27 равна числу выборок предаварийного процесса, его код 0011, сформировавшийся для записи информации при следующей выборке процесса с выхода АД 1, одновременно является младшей частью адреса ячейки ОЗУ 11, в которой находится код выборки начала предаварийного процесса. В связи с этим, начиная с адреса 00000011, из ОЗУ 11 в ОЗУ 12 начинают переписываться выборки предаварийного процесса. Происходит это следующим образом.

После перехода в единичное состояние триггера 31 напряжение с его выхода прикладывается к первому входу элемента И 38, на второй вход которого поступают импульсы максимальной частоты с первого выхода ГТИ 60. Выходные импульсы элемента И 38 с такой же частотой начинают переключать триггер 32, напряжения выходов которого поочередно запускают одновибраторы 50 и 51.

После прохождения выходного импульса одновибратора 50 через элемент И 35 и элемент ИЛИ 41 код выборки начала предаварийного процесса переписывается из ячейки с адресом 00000011 ОЗУ 11 в ячейку с адресом 000000 ОЗУ 12.

После прохождения выходного импульса одновибратора 51 через элемент И 36 на единицу увеличивается содержимое счетчика 26 (оно становится равным 0001), а после прохождения импульса через элемент ИЛИ 39 на единицу увеличивается содержимое счетчика 27 (оно становится равным 0100), а после прохождения импульса через элемент ИЛИ 40 на единицу увеличивается содержимое счетчика 28 (оно становится равным 000001).

В следующем такте работы триггера 32 содержимое счетчиков становится равным: 26 - 0010, 27 - 0101, 28 - 000010 и т.д.

После полной перезаписи информации о предаварийном процессе из ОЗУ 11 в ОЗУ 12 содержимое счетчиков равно: 26 - 1111, 27 - 0011, 28 - 001111.

При этом на выходе переноса счетчика 26 появляется единичное напряжение, запускающее одновибратор 53, выходные импульсы которого устанавливают в нулевое состояние счетчик 26, а также триггеры 31 и 32.

После этого в ОЗУ 11 и 12 продолжается запись аварийного процесса в масштабе реального времени.

При очередной выборке аварийного процесса в первом канале импульс с выхода окончания цикла преобразования АЦП 21 записывает код выборки в ячейку ОЗУ 11 с адресом 0011, а импульс с выхода одновибратора 44 (после прохождения через элемент И 34 и элемент ИЛИ 41) записывает этот же код с выхода ОЗУ 11 в ячейку ОЗУ 12 с адресом 001111.

После этого импульс одновибратора 45 после прохождения через элемент ИЛИ 39 увеличивает на единицу содержимое счетчика 27 (оно становится равным 0100), а после прохождения еще и через элемент И 37 и элемент ИЛИ 40 увеличивает на единицу содержимое счетчика 28 (оно становится равным 010000).

Таким образом, продолжается накопление информации в ОЗУ 11 и 12 до полного окончания аварийного процесса, длительность которого контролируется счетчиком 28.

При переполнении счетчика 28 на его выходе переноса появляется импульс, запускающий одновибратор 52, выходные импульсы которого устанавливают в нулевое состояние счетчик 28 и триггер 30, а также один из импульсов поступает на вход второго вектора прерываний МК 15.

По второму вектору прерываний МК 15 переходит на выполнение второго программного блока, который переписывает данные об аварийном и предаварийном процессах из ОЗУ 12 в ОЗУ 13. После этого полученные данные об аварии переписываются из ОЗУ 13 в ПЗУ 14 и размещаются в области памяти, отведенной для регистрации данных по первой аварии.

При следующих авариях регистратор работает аналогично.

Данные о предаварийных процессах всех каналов регистратора непрерывно накапливаются в ячейках ОЗУ 11. Наличие дополнительного ОЗУ 13 позволяет применять ПЗУ 14 любого быстродействия. Таймер 16, ГТИ 60, ОЗУ 11-13 и ПЗУ 14 могут быть встроенными в микроконтроллер 15.

Второй вариант регистратора (фиг.2) работает следующим образом.

Основная (нижняя) часть второго варианта схемы регистратора (фиг.2), содержащая элементы 1-6, 20-26, 28-30, 34-55, 57, работает так же, как и у первого варианта схемы регистратора.

Рассмотрим работу верхней части схемы второго варианта регистратора, содержащую элементы 7-19, 27, 31-33, 44-46, 56, 58, 59, которая осуществляет операцию выбора масштаба АЦП 21.

По заднему фронту очередного импульса с третьего выхода ГТИ 20 срабатывает счетчик 27 (его содержимое становится равным 01), а также запускается одновибратор 33, который своим выходным импульсом приводит в действие АЦП 21. При входном коде 01 дешифратор 10 вырабатывает на первом выходе управляющее единичное напряжение, которое открывает коммутатор 17 - ко входу опорного напряжения АЦП 21 прикладывается напряжение 0,1023 В с первого выхода ИОН 9. В этом случае масштаб преобразования равен 1.

Выходной код АЦП 21 с помощью ЧК 58 сравнивается с кодом границы 0011001112=10310 (число 103 чуть больше числа 1024:10=102,3), задаваемым БЗКГ 59.

Если граница 001100111 превышена (т.е. А<В), то на выходе «А<В» ЧК 58 появляется единичное напряжение, запускающее одновибратор 44. Выходной импульс последнего засчитывается счетчиком 27, содержимое которого становится равным 10, - управляющее напряжение появляется на втором выходе дешифратора 10, открывая коммутатор 18, который пропускает напряжение 1,023 В со второго выхода ИОН 9 на вход опорного напряжения АЦП 21. В этом случае масштаб преобразования равен 10.

Если и в этом случае граница 001100111 оказывается превышенной, то содержимое счетчика 27 становится равным 11, управляющее напряжение появляется на третьем выходе дешифратора 10, открывается коммутатор 19, пропуская напряжение 10,23 В со второго выхода ИОН 9 на вход опорного напряжения АЦП 21. В этом случае масштаб преобразования равен 100.

Появляющееся на третьем выходе дешифратора 10 единичное напряжение запускает цепь одновибраторов 45-46, вносящих задержку появления единичного сигнала на втором входе элемента И 56, которая необходима для исключения ложной записи информации в ОЗУ 11 при третьем запуске АЦП 21.

Импульсом с выхода окончания цикла преобразования АЦП 21 двоичный код очередной выборки процесса с выхода АД 1 записывается в ОЗУ 11.

В том случае если граница 001100111 не превышена (т.е. «А=В» или «А>В»), то на одном из выходов «А=В» или «А>В» ЧК 58 появляется единичное напряжение, которое через элемент ИЛИ 32 прикладывается ко второму входу элемента И 56, - импульс с выхода окончания цикла преобразования АЦП 21 проходит через элемент И 56, что приводит к записи двоичного кода очередной выборки процесса с выхода АД 1 в ОЗУ 11.

Импульс с выхода окончания цикла преобразования АЦП 21, после прохождения через элемент И 56, обнуляет содержимое счетчика 27 (приводя схему выбора масштаба преобразования в исходное состояние), а также запускает одновибратор 34.

Выходной импульс одновибратора 34 запускает одновибратор 35, импульс с прямого выхода которого обнуляет содержимое выходного регистра АЦП 21, подготавливая АЦП 21 для дальнейшей работы.

Преимуществом предлагаемого регистратора по сравнению с известными является расширение функциональных возможностей устройства за счет обеспечения возможности регистрации параметров переходных процессов изменения напряжения и тока в электрических сетях повышенной точности при авариях, а также на интервалах времени, предшествующих аварийной ситуации.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ | 2008 |

|

RU2381549C2 |

| ЧАСТОТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ ЕРМАКОВА-ФЕДОРОВА (ВАРИАНТЫ) | 2007 |

|

RU2362175C2 |

| ЧАСТОТОМЕР ДЛЯ ЭНЕРГОСИСТЕМ И ЭЛЕКТРОСТАНЦИЙ ЕРМАКОВА-ФЕДОРОВА (ВАРИАНТЫ) | 2007 |

|

RU2362174C1 |

| РЕГИСТРАТОР АВАРИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ЭНЕРГОСИСТЕМ | 2009 |

|

RU2402067C1 |

| УСТРОЙСТВО ДЛЯ МОНИТОРИНГА ПЕРЕХОДНЫХ РЕЖИМОВ В ЭЛЕКТРИЧЕСКОЙ СИСТЕМЕ | 2014 |

|

RU2554513C1 |

| СПОСОБ МОНИТОРИНГА ПЕРЕХОДНЫХ РЕЖИМОВ В ЭЛЕКТРОЭНЕРГЕТИЧЕСКОЙ СИСТЕМЕ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2012 |

|

RU2513874C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕЦИЗИОННЫЙ ЧАСТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2333501C1 |

| Устройство для измерения характеристик сверхпроводящих образцов | 1989 |

|

SU1675789A1 |

| СПОСОБ ИЗМЕРЕНИЯ ЧАСТОТЫ (ВАРИАНТЫ) И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ (ВАРИАНТЫ) | 2008 |

|

RU2380716C1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ФУНКЦИИ МОМЕНТОВ ЕРМАКОВА В.Ф. | 1994 |

|

RU2092897C1 |

Изобретение относится к области информационно-измерительной и вычислительной техники и может быть использовано в электроэнергетике для регистрации параметров переходных процессов изменения напряжения и тока в электрических сетях при авариях. Техническим результатом является расширение функциональных возможностей устройства за счет обеспечения возможности регистрации параметров переходных процессов изменения напряжения и тока в электрических сетях при авариях, а также на интервалах времени, предшествующих аварийной ситуации. Технический результат достигается благодаря тому, что: 1) первый вариант реализации регистратора содержит группу аналоговых датчиков, группу цифровых датчиков, многоканальные первый аналоговый (МАК) и второй цифровой (МЦК) коммутаторы, формирователь модуля, нуль-орган (НО), источник опорных напряжений (ИОН), дешифратор, первое, второе и третье оперативные запоминающие устройства (ОЗУ), постоянное запоминающее устройство (ПЗУ), микроконтроллер, таймер, первый - четвертый одноканальные аналоговые коммутаторы, аналого-цифровой преобразователь (АЦП), первый и второй аналоговые компараторы (АК), регистр, первый - пятый счетчики, первый - третий триггеры, элемент И-НЕ, первый - пятый элементы И, первый - четвертый элементы ИЛИ, первый - шестнадцатый одновибраторы, числовой компаратор, генератор тактовых импульсов (ГТИ); 2) второй вариант реализации регистратора содержит группу аналоговых датчиков, группу цифровых датчиков, первый МАК и второй МЦК, формирователь модуля, НО, ИОН, дешифратор, первое, второе и третье ОЗУ, ПЗУ, микроконтроллер, таймер, первый - третий одноканальные аналоговые коммутаторы, ГТИ, АЦП, регистр, первый - пятый счетчики, первый - пятый элементы ИЛИ, первый - четырнадцатый одновибраторы, первый - третий триггеры, элемент И-НЕ, первый - шестой элементы И, первый и второй числовые компараторы, блок задания кода границы. 2 н. и 2 з.п. ф-лы, 3 ил.

1. Регистратор параметров аварийных ситуаций в электрических сетях повышенной точности, содержащий первый счетчик, первый и второй коммутаторы, первое, второе и третье оперативные запоминающие устройства, группу аналоговых датчиков, аналого-цифровой преобразователь, микроконтроллер, генератор тактовых импульсов, выходы которого соединены третий - с тактовым входом первого счетчика, первый - с тактовым входом микроконтроллера, адресная шина которого соединена с объединенными адресными входами второго и третьего оперативных запоминающих устройств, входы управления записью которых подключены к шине управления микроконтроллера, к которой также подключен вход управления состоянием выходов выходных регистров третьего оперативного запоминающего устройства, информационный выход первого счетчика соединен с управляющим входом первого коммутатора, информационные входы которого подключены к выходам группы аналоговых датчиков,

отличающийся тем, что в него дополнительно введены постоянное запоминающее устройство, числовой компаратор, таймер, регистр, второй - пятый счетчики, первый - третий триггеры, формирователь модуля, нуль-орган, источник опорных напряжений, дешифратор, первый - четвертый одноканальные аналоговые коммутаторы, первый и второй аналоговые компараторы, элемент И-НЕ, первый - пятый элементы И, первый - четвертый элементы ИЛИ, первый - шестнадцатый одновибраторы, группа цифровых датчиков, выходы которых соединены с информационными входами второго многоканального коммутатора, управляющий вход которого объединен с первым входом числового компаратора, информационным входом регистра и группой старших разрядов адресного входа первого оперативного запоминающего устройства и подключен к информационному выходу первого счетчика, третий выход генератора тактовых импульсов соединен с объединенными первым входом четвертого элемента ИЛИ и инверсным входом первого одновибратора, выход которого соединен с объединенными управляющим входом четвертого одноканального аналогового коммутатора и инверсным входом двенадцатого одновибратора, выход которого соединен со входом запуска аналого-цифрового преобразователя, информационный вход которого подключен к выходу формирователя модуля, тактовый вход подключен ко второму выходу генератора тактовых импульсов, а информационный выход соединен с группой младших разрядов информационного входа первого оперативного запоминающего устройства, вход управления записью которого объединен с входом установки нуля пятого счетчика и входом второго одновибратора и подключен к выходу окончания цикла преобразования аналого-цифрового преобразователя, выход второго одновибратора соединен с объединенными третьим входом первого элемента И и инверсным входом третьего одновибратора, выходы которого соединены прямой - с первым входом первого элемента ИЛИ, а инверсный - через четвертый одновибратор с первым входом элемента И-НЕ, второй вход которого подключен к выходу второго многоканального коммутатора, соединенному через пятый одновибратор со входом управления записью регистра, вход управления состоянием выхода которого подключен к шине управления микроконтроллера, выход регистра соединен с шиной данных микроконтроллера и вторым входом числового компаратора, выход которого «А=В» (где А и В - соответственно, коды чисел на первом и втором входах числового компаратора) соединен с объединенными первыми входами первого, второго и третьего элементов И, выход элемента И-НЕ соединен со входом установки единицы первого триггера, прямой выход которого соединен с объединенными вторыми входами первого и четвертого элементов И и входом шестого одновибратора, инверсный выход которого соединен со входом первого вектора прерываний микроконтроллера и через седьмой одновибратор - со входом установки единицы второго триггера, прямой выход которого через пятый элемент И соединен с тактовым входом третьего триггера, выходы которого соединены соответственно через восьмой и девятый одновибраторы со вторыми входами второго и третьего элементов И, выход которого соединен с тактовым входом второго счетчика и вторыми входами второго и первого элементов ИЛИ, выход которого соединен с тактовым входом третьего счетчика и через четвертый элемент И с первым входом второго элемента ИЛИ, выход которого соединен с тактовым входом четвертого счетчика, информационный выход которого соединен с адресной шиной микроконтроллера, вход управления состоянием информационного выхода подключен к шине управления микроконтроллера, а выход переноса соединен со входом десятого одновибратора, выходы которого соединены прямой - со входом второго вектора прерываний микроконтроллера и входом установки нуля четвертого счетчика, инверсный - со входом установки нуля первого триггера, выход переноса второго счетчика соединен со входом одиннадцатого одновибратора, выходы которого соединены прямой - со входом установки нуля второго счетчика, инверсный - со входами установки нуля второго и третьего триггеров, информационный выход третьего счетчика соединен с группой младших разрядов адресного входа первого оперативного запоминающего устройства, информационный выход которого соединен с информационным входом второго оперативного запоминающего устройства, информационный выход которого соединен с информационным входом третьего оперативного запоминающего устройства, информационный выход которого соединен с шиной данных микроконтроллера, соединенной с информационным входом постоянного запоминающего устройства, адресный вход которого подключен к адресной шине микроконтроллера, а вход управления записью подключен к шине управления микроконтроллера, выход первого элемента И через третий элемент ИЛИ соединен со входом управления записью второго оперативного запоминающего устройства, тактовый вход таймера объединен с вторым входом пятого элемента И и подключен к первому выходу генератора тактовых импульсов, вход захвата и вход управления состоянием выходов выходных регистров таймера подключены к шине управления микроконтроллера, а информационный выход таймера соединен с шиной данных микроконтроллера, выход первого многоканального коммутатора соединен с объединенными информационными входами нуль-органа и формирователя модуля, выход которого через четвертый одноканальный аналоговый коммутатор соединен с объединенными вторыми входами первого и второго аналоговых компараторов, первые входы которых подключены соответственно ко второму и первому выходам источника опорных напряжений, первый - третий выходы которого соединены соответственно с информационными входами первого -третьего одноканальных аналоговых коммутаторов, выходы которых объединены и соединены с входом опорного напряжения аналого-цифрового преобразователя, а управляющие входы первого - третьего одноканальных аналоговых коммутаторов подключены соответственно к первому - третьему выходам дешифратора, выходы первого и второго аналоговых компараторов через последовательно соединенные попарно тринадцатый и четырнадцатый, а также пятнадцатый и шестнадцатый одновибраторы связаны соответственно со вторым и третьим входами четвертого элемента ИЛИ, выход которого соединен с тактовым входом пятого счетчика, выход которого соединен с объединенными входом дешифратора и группой средних разрядов информационного входа первого оперативного запоминающего устройства, старший разряд которого объединен с первым управляющим входом формирователя модуля и подключен к прямому выходу нуль-органа, инверсный выход которого соединен со вторым управляющим входом формирователя модуля.

2. Регистратор параметров аварийных ситуаций в электрических сетях повышенной точности по п.1, отличающийся тем, что формирователь модуля содержит инвертор, четвертый и пятый одноканальные аналоговые коммутаторы, выходы которых объединены и соединены с выходом формирователя модуля, информационный вход которого соединен с объединенными входами четвертого одноканального аналогового коммутатора и инвертора, выход которого соединен со входом пятого одноканального аналогового коммутатора, первый и второй управляющие входы формирователя модуля соединены соответственно с управляющими входами четвертого и пятого одноканальных аналоговых коммутаторов.

3. Регистратор параметров аварийных ситуаций в электрических сетях повышенной точности, содержащий первый счетчик, первый и второй коммутаторы, первое, второе и третье оперативные запоминающие устройства, группу аналоговых датчиков, аналого-цифровой преобразователь, микроконтроллер, генератор тактовых импульсов, выходы которого соединены третий - с тактовым входом первого счетчика, первый - с тактовым входом микроконтроллера, адресная шина которого соединена с объединенными адресными входами второго и третьего оперативных запоминающих устройств, входы управления записью которых подключены к шине управления микроконтроллера, к которой также подключен вход управления состоянием выходов выходных регистров третьего оперативного запоминающего устройства, информационный выход первого счетчика соединен с управляющим входом первого коммутатора, информационные входы которого подключены к выходам группы аналоговых датчиков, отличающийся тем, что в него дополнительно введены постоянное запоминающее устройство, источник опорных напряжений, первый - третий одноканальные аналоговые коммутаторы, первый и второй числовые компараторы, второй - пятый счетчики, первый - третий триггеры, формирователь модуля, нуль-орган, таймер, регистр, дешифратор, элемент И-НЕ, первый -шестой элементы И, первый - пятый элементы ИЛИ, первый - четырнадцатый одновибраторы, блок задания кода границы, группа цифровых датчиков, выходы которых соединены с информационными входами второго многоканального коммутатора, управляющий вход которого объединен с первым входом первого числового компаратора, информационным входом регистра и группой старших разрядов адресного входа первого оперативного запоминающего устройства и подключен к информационному выходу первого счетчика, третий выход генератора тактовых импульсов соединен с первым входом четвертого элемента ИЛИ, выход которого соединен с тактовым входом пятого счетчика и через первый одновибратор - с входом запуска аналого-цифрового преобразователя, информационный вход которого подключен к выходу формирователя модуля, тактовый вход подключен ко второму выходу генератора тактовых импульсов, а информационный выход соединен с объединенными вторым входом второго числового компаратора и группой младших разрядов информационного входа первого оперативного запоминающего устройства, вход управления записью которого объединен с входом установки нуля пятого счетчика и входом второго одновибратора и через шестой элемент И подключен к выходу окончания цикла преобразования аналого-цифрового преобразователя, выход второго одновибратора соединен с объединенными третьим входом первого элемента И и инверсным входом третьего одновибратора, выходы которого соединены прямой - с объединенными входом установки нуля аналого-цифрового преобразователя и первым входом первого элемента ИЛИ, а инверсный - через четвертый одновибратор с первым входом элемента И-НЕ, второй вход которого подключен к выходу второго многоканального коммутатора, соединенному через пятый одновибратор со входом управления записью регистра, вход управления состоянием выхода которого подключен к шине управления микроконтроллера, выход регистра соединен с шиной данных микроконтроллера и вторым входом первого числового компаратора, выход которого «А=В» (где А и В -соответственно, коды чисел на первом и втором входах первого и второго числовых компараторов) соединен с объединенными первыми входами первого, второго и третьего элементов И, выход элемента И-НЕ соединен со входом установки единицы первого триггера, прямой выход которого соединен с объединенными вторыми входами первого и четвертого элементов И и входом шестого одновибратора, инверсный выход которого соединен со входом первого вектора прерываний микроконтроллера и через седьмой одновибратор - со входом установки единицы второго триггера, прямой выход которого через пятый элемент И соединен с тактовым входом третьего триггера, выходы которого соединены соответственно через восьмой и девятый одновибраторы со вторыми входами второго и третьего элементов И, выход которого соединен с тактовым входом второго счетчика и вторыми входами второго и первого элементов ИЛИ, выход которого соединен с тактовым входом третьего счетчика и через четвертый элемент И с первым входом второго элемента ИЛИ, выход которого соединен с тактовым входом четвертого счетчика, информационный выход которого соединен с адресной шиной микроконтроллера, вход управления состоянием информационного выхода подключен к шине управления микроконтроллера, а выход переноса соединен со входом десятого одновибратора, выходы которого соединены прямой - со входом второго вектора прерываний микроконтроллера и входом установки нуля четвертого счетчика, инверсный - со входом установки нуля первого триггера, выход переноса второго счетчика соединен со входом одиннадцатого одновибратора, выходы которого соединены прямой - со входом установки нуля второго счетчика, инверсный - со входами установки нуля второго и третьего триггеров, информационный выход третьего счетчика соединен с группой младших разрядов адресного входа первого оперативного запоминающего устройства, информационный выход которого соединен с информационным входом второго оперативного запоминающего устройства, информационный выход которого соединен с информационным входом третьего оперативного запоминающего устройства, информационный выход которого соединен с шиной данных микроконтроллера, соединенной с информационным входом постоянного запоминающего устройства, адресный вход которого подключен к адресной шине микроконтроллера, а вход управления записью подключен к шине управления микроконтроллера, выход первого элемента И через третий элемент ИЛИ соединен со входом управления записью второго оперативного запоминающего устройства, тактовый вход таймера объединен с вторым входом пятого элемента И и подключен к первому выходу генератора тактовых импульсов, вход захвата и вход управления состоянием выходов выходных регистров таймера подключены к шине управления микроконтроллера, а информационный выход таймера соединен с шиной данных микроконтроллера, выход пятого счетчика соединен с объединенными входом дешифратора и группой средних разрядов информационного входа первого оперативного запоминающего устройства, старший разряд которого объединен с первым управляющим входом формирователя модуля и подключен к прямому выходу нуль-органа, инверсный выход которого соединен со вторым управляющим входом формирователя модуля, информационный вход которого объединен с входом нуль-органа и подключен к выходу первого многоканального коммутатора, первый - третий выходы источника опорных напряжений соединены соответственно с информационными входами первого - третьего одноканальных аналоговых коммутаторов, выходы которых объединены и соединены со входом опорного напряжения аналого-цифрового преобразователя, а управляющие входы первого - третьего одноканальных аналоговых коммутаторов подключены соответственно к первому - третьему выходам дешифратора, выход блока задания кода границы соединен с первым входом второго числового компаратора, выходы которого соединены «А<В» - через двенадцатый одновибратор со вторым входом четвертого элемента ИЛИ, «А=В» и «А>В» - со вторым и третьим входами пятого элемента ИЛИ, первый вход которого через последовательно соединенные тринадцатый и четырнадцатый одновибраторы подключен к третьему выходу дешифратора, а выход пятого элемента ИЛИ соединен со вторым входом шестого элемента И.

4. Регистратор параметров аварийных ситуаций в электрических сетях повышенной точности по п.3, отличающийся тем, что формирователь модуля содержит инвертор, четвертый и пятый одноканальные аналоговые коммутаторы, выходы которых объединены и соединены с выходом формирователя модуля, информационный вход которого соединен с объединенными входами четвертого одноканального аналогового коммутатора и инвертора, выход которого соединен со входом пятого одноканального аналогового коммутатора, первый и второй управляющие входы формирователя модуля соединены соответственно с управляющими входами четвертого и пятого одноканальных аналоговых коммутаторов.

| УСТРОЙСТВО ДЛЯ СБОРА, ОБРАБОТКИ И ПАКЕТНОЙ ПЕРЕДАЧИ РЕЗУЛЬТАТОВ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ФИЗИЧЕСКОЙ СРЕДЫ | 1994 |

|

RU2079881C1 |

| УСТРОЙСТВО ДЛЯ СБОРА, ПРЕОБРАЗОВАНИЯ И ПЕРЕДАЧИ РЕЗУЛЬТАТОВ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ФИЗИЧЕСКОЙ СРЕДЫ | 1994 |

|

RU2081452C1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Аналого-цифровое устройство сбора информации | 1987 |

|

SU1443004A1 |

Авторы

Даты

2009-12-20—Публикация

2008-05-04—Подача