Изобретение относится к контрольно-измерительной технике и может быть использовано в автоматизированных устройствах контроля интегральных схем (ИС).

Известно устройство контактирования выводов ИС, содержащее контактную головку с парами контактов на каждый вывод ИС, источник питания импульсного трансформатора, генератор тактовых импульсов, источник сигналов разрешения, пороговый элемент и элементы И [1].

При подключении контактной головки с парами контактов к выводам испытуемой ИС вырабатывается сигнал разрешения проверки контактирования, генератор вырабатывает тактовые импульсы, которые вызывают протекание импульсного тока по первичной обмотке соответствующего импульсного трансформатора. При этом, если существует участок контактирования между соответствующей парой контактов и выводами испытуемой ИС, вторичная обмотка импульсного трансформатора будет замкнута. В результате на дополнительной обмотке уровень наведенного сигнала ниже порога срабатывания порогового элемента. Если на участке контактирования контакта нет, то вторичная обмотка соответствующего импульсного трансформатора шунтироваться не будет, и в дополнительной обмотке наведутся сигналы, по уровню превышающие порог срабатывания порогового элемента.

Основным недостатком данного устройства контактирования является наличие пары контактов для проверки одного вывода испытуемой ИС. Применение пары контактов, помноженной на количество выводов ИС, для проверки контактирования на плате электротермотренировки (ЭТТ) не только повышает стоимость платы загрузки, так как необходимо вводить дополнительные контакты из драгоценных металлов в конструкцию контактного устройства (КУ) для испытуемой ИС, но и занимает дополнительный конструктивный объем на плате ЭТТ, что снижает на 30% количество устанавливаемых КУ на плате, из-за чего резко падает производительность испытательного оборудования. Пара контактов на контактной головке снижает надежность работы всего контактирующего узла по сравнению с одинарным контактом. При наличии контакта между парами контактной головки для шунтирования обмотки импульсного трансформатора можно иметь сопротивление порядка единиц ом, не нарушающее работу данного устройства контроля. При этом устройство практически работоспособно только в зоне полного нарушения контакта. Однако на практике часто имеет место не полное нарушение зоны контакта, а повышенное его сопротивление из-за наличия окисных пленок, снижения упругих свойств контакторов КУ на плате ЭТТ, загрязнений и т. д. При этом данные отклонения в нарушениях переходного сопротивления контактов не будут зарегистрированы устройством проверки контактирования, что снижает достоверность контроля контактирования и режимов тренировки.

Наиболее близким является устройство контроля контактирования интегральных схем [2]. Оно содержит блоки опорных напряжений, компараторов, управляющие клеммы (блок управления и измерения), регистр, блок зондов, источник напряжения и датчик потенциала.

Устройство работает следующим образом. При отсутствии контактов между блоком зондов и выводами ИС датчики потенциала открыты, напряжение на инверсных входах компараторов превышает напряжение на прямых входах, поступающие с блока опорных напряжений, поэтому входы компараторов находятся в состоянии логического нуля. После опускания зондов на выводы ИС на вывод подключения питания ИС поступает потенциал источника напряжения, в результате этого на выводах ИС устанавливается потенциал, соответствующий источнику напряжения. При наличии контакта между зондами и выводами ИС под действием потенциала, поступающего на управляющие входы, датчики потенциала закрываются, компараторы напряжения переключаются и на их выходе устанавливается уровень логической единицы, сигнализирующей о наличии контакта между зондами блока зондов и выводами ИС.

Устройство не позволяет в полной мере использовать методы компарирования выходных сигналов с выводов проверяемой ИС. Оно позволяет фиксировать только наличие или отсутствие контакта между зондами или выводами ИС. Использование только одного вывода испытуемой ИС для подключения источника напряжения не позволяет достоверно оценить состояние переходных сопротивлений между выводами ИС и контактами контактирующего устройства на плате ЭТТ, так как входы датчиков потенциала подключены к одному опорному напряжению, что не позволяет зарегистрировать однозначно, между какими выводами ИС и зондом имеется нарушение контакта в силу различной внутренней структуры ИС, в особенности цифровых ИС, имеющих так называемые втекающие и вытекающие как входные, так и выходные токи.

Использование этого устройства контроля контактирования не позволит достоверно сработать датчикам потенциалов, что приведет к ложным сигналам с компараторов напряжений. Применение данного устройства контактирования требует подключения блока зондов ко всем выводам испытуемой ИС, при этом возрастет сложность узла блока зондов, большое количество зондов для контактирования в многовыводных ИС снижает надежность всего механического устройства, затрудняет групповое контактирование ряда ИС. При этом размеры блока зондов определяют громоздкость конструктивных решений платы загрузки ЭТТ и ведут к снижению производительности испытательного оборудования, так как снижается до 20% количество испытуемых ИС, размещенных на плате загрузки. Данное устройство не позволяет контролировать контактирование ИС в динамическом режиме.

Целью изобретения является расширение области применения путем испытания в динамическом режиме при групповых испытаниях с одновременным повышением достоверности контроля.

Это достигается тем, что в устройство контроля контактирования интегральных схем, содержащее блок контактирования, блок управления, блок компараторов, первый управляющий вход которого соединен с первым выходом блока опорных напряжений, источник напряжения, первый выход которого соединен с первым входом блока контактирования, введен формирователь импульсных сигналов, блок коммутации, блок анализа, информационные входы которого с первого по К-й соединены соответственно с выходами с первого по К-й блока компараторов, где К - число выходных выводов испытуемой интегральной схемы, первый, второй, третий и четвертый управляющие входы блока анализа соединены раздельно с первым, вторым, третьим и четвертым выходами блока управления, первый и второй входы которого соединены соответственно с первым и вторым выходами блока анализа, выходы блока коммутации с первого по К-й соединены соответственно с информационными входами с первого по К-й блока компараторов, второй управляющий вход которого соединен с вторым выходом блока опорных напряжений, управляющие входы формирователя импульсных сигналов источника напряжения и блока коммутации соединены соответственно с пятым, шестым и седьмым выходами блока управления, входы с первого по К-й каждой из Р групп входов блока коммутации соединены раздельно с одноименными входами одноименных групп выходов блока контактирования, входы которого с второго по (n + 1)-й соединены соответственно с выходами формирователя импульсных сигналов с первого по n-й, где Р - число испытуемых интегральных схем; n - число входов испытуемой интегральной схемы, на которые подаются импульсные сигналы, входы блока контактирования с (n + 2)-го по (n + m + 1)-й соединены соответственно с выходами источника напряжения с второго по (m + 1)-й, где m - число входов испытуемой интегральной схемы, на которые подаются статические сигналы.

Предлагаемое устройство позволяет расширить область его применения путем испытания в динамическом режиме при групповых испытаниях с одновременным повышением достоверности контроля, так как позволяет выявить недопустимые переходные сопротивления между ИС и КУ.

В предлагаемом устройстве контроля контактирования ИС для повышения надежности и достоверности контроля контактирования между выводами ИС и подключающими выводами контактирующего устройства в блоке контактирования испытуемая ИС разделяется по выводам на входную и выходную части согласно собственной схемотехнике. При этом на входах ИС устанавливаются электрические режимы согласно технологии испытаний, а к остальным выводам, нагруженным на RCD-компоненты, подключается с помощью блока коммутации блок компараторов, который выделяет для контроля полезный сигнал. При этом сокращается блок зондов блока коммутации на количество входных выводов ИС, а сигналы контроля компарируются непосредственно с выводов ИС. Установка заданных электрических режимов на входах ИС и двухуровневая система компарирования выходных сигналов ИС позволяют выявить недопустимые переходные сопротивления при загрузке испытуемых ИС в контактирующие устройства.

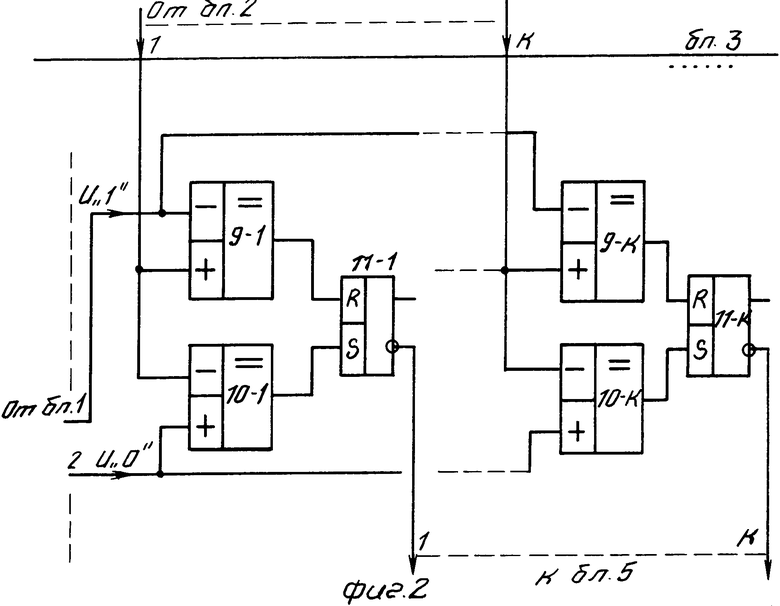

На фиг. 1 изображена структурная схема устройства контроля контактирования интегральных схем; на фиг. 2 - схема блока компараторов; на фиг. 3 - схема блока анализа; на фиг. 4 - временные диаграммы работы устройства.

Устройство контроля контактирования интегральных схем содержит блок 1 контактирования, блок 2 коммутации, блок 3 компараторов, блок 4 опорных напряжений, блок 5 анализа, блок 6 управления, формирователь 7 импульсных сигналов, источник 8 напряжения.

Блок 3 компараторов (см. фиг. 2) состоит из К устройств согласно количеству контрольных линий на входах 1-К блока, при этом каждое устройство содержит компаратор 9 уровня логической "1", компаратор 10 уровня логического "0", выходы которых подключены на RS-триггеры 11, которые на своем выходе формируют сигналы, совпадающие с формой сигналов на входе устройства. Опорные напряжения U уровней логической "1" и логического "0" задаются на устройства с блока 4 опорных напряжений.

Блок 5 анализа состоит (см. фиг. 3) из К устройств согласно количеству контрольных линий на входе блока, при этом каждое устройство содержит счетчик 12 импульсов, выходами подключенных через переключатели 13 на RS-триггеры 14, с выхода которых сигналы через ключи 15 поступают на схему 16 совпадения, с выхода которой сигнал контроля ИНФОРМ поступает на блок 6 управления, состоящий из устройств ввода-вывода с центральным процессором. Каждый счетчик 12 импульсов содержит счетный вход С, вход запрета счета СЕ, вход сброса R. Количество накопленных импульсов может устанавливаться по выходу с помощью переключателей 13. Схема 16 совпадения представляет собой логический элемент n И-НЕ, каждый n-вход которого состоит из элемента 2 ИЛИ и может управляться с помощью шины МАСКА. Запуск устройств осуществляется одновибратором 17.

Логические элементы ИСКЛЮЧАЮЩЕЕ ИЛИ (1-) 18, ключи 15 предназначены для подключения входов схемы 16 совпадения непосредственно к входам 1...n блока 5 анализа при наличии с контролируемого выхода ИС статического сигнала.

Источник 8 напряжения содержит (m + 1) стабилизаторов напряжения, выходами подключенных к входам испытуемых ИС и управляемых блоком 6 управления. Формирователь 7 импульсных сигналов содержит задающий генератор импульсов, формирователь периодов импульсов, подключенный к входам импульсных усилителей 1. ..n, при этом выходные сигналы импульсных усилителей регулируются по уровням напряжений логической "1" и логического "0" и подключены к входам испытуемых ИС.

Устройство контроля контактирования ИС работает следующим образом.

В исходном состоянии блок 6 управления переводит по шинам управления 5, 6 выходы источника 8 напряжения и формирователя 7 импульсных сигналов, подключенные в блоке 1 к контактным устройствам 1-Р для ИС, в высокоомное состояние. Устанавливаются с помощью блока 4 опорные напряжения логической "1" и логического "0" на входах блока 3 компараторов согласно типу проверяемой ИС. Устанавливается количество накапливаемых счетчиками 12 импульсов в блоке 5 анализа подключением входов RS-триггеров 14 к соответствующему выходу счетчика. При этом, если на входных линиях 1...К блока 5 анализа должен будет отсутствовать контролируемый сигнал с блока 3 компараторов, то соответствующий одноименный выход со счетчика 12 импульсов через его RS-триггер 14 и ключ 15 маскируется уровнем логической "1", устанавливаемой шиной МАСКА на спаренном входе элемента 2 ИЛИ схемы 16 совпадения. На остальных входах элементов 2 ИЛИ от шины МАСКА на схеме 16 совпадения устанавливаются уровни логического "0". Одновременно по шине СТАТИКА переключается соответствующий ключ 15, если на одноименном входе блока 5 анализа должен будет присутствовать статический сигнал с контролируемой ИС, а по шине ИНВЕРСИЯ на одном входе одноименного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (1-) 18, другим входом подключенного к входной линии блока 5 анализа, для статических сигналов установится уровень логической "1", для ожидаемого статического сигнала уровнем логического"0" или, наоборот, для ожидаемого статического сигнала уровнем логической "1" на шине ИНВЕРСИЯ для данного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (1-) 18 установится уровень логического "0".

Блок 6 управления по выходной шине 7 с помощью блока 2 коммутации непосредственно подключает контрольные входы блока 3 компараторов к сигналам на выводах контактирующего устройства с испытуемой ИС. При этом блок 6 управления включает источник 8 напряжения, импульсом запускает по линии (см. фиг. 3) ПУСК одновибратор 17 (см. фиг. 4), по срезу которого одновибратор вырабатывает короткий импульс СБРОС для обнуления счетчиков 12 импульсов и установки в блоке 5 анализа RS-триггеров в состояние, при котором на их выходах будут уровни логического "0".

По срезу импульса СБРОС одновибратор 17 дает строб РАЗРЕШЕНИЕ работы счетчика 12 импульсов и сигнал ЗАПУСК, по которому блок 6 управления включает формирователь 7 импульсных сигналов. При этом на входы испытуемых ИС подаются электрические режимы, параметры которых по уровням напряжений сигналов логического "0" и логической "1" строго заданы. На выходах испытуемой ИС появляются контрольные сигналы, которые поступают на входы блока 3 компараторов, где компарируются опорными напряжениями по уровням логического "0" и логической "1", и с выходов RS-триггеров 11 блок 3 вырабатывает синхронные сигналы, которые поступают для анализа в блок 5 (см. фиг. 2, 3). В течение строба РАЗРЕШЕНИЕ происходит накопление импульсов в счетчиках. После окончания работы одновибратор 17 в блоке 5 снимает строб РАЗРЕШЕНИЕ, при этом блокируется работа счетчиков 12 импульсов. Одновременно заканчивается строб ЗАПУСК, означающий готовность устройств к считыванию информации. Если на заданный промежуток времени счетчики 12, получив синхронные сигналы с выходов блока 3 компараторов, опрокинут RS-триггеры 14, последние установят на информационных входах элементов 2 ИЛИ схемы 16 совпадения логические "1", которые в сочетании с уже установленными уровнями логической "1" по шине МАСКА на входах элементов 2 ИЛИ с заведомо отсутствующими контрольными сигналами вызовут срабатывание схемы 16 совпадения, при этом на линии ИНФОРМ появится уровень логического "0", что соответствует наличию контакта между испытуемой ИС и выводами КУ. При отсутствии на каждом входном элементе 2 ИЛИ схемы 16 совпадения хотя бы одного уровня логической "1" на линии ИНФОРМ будет присутствовать уровень логической "1", что соответствует отсутствию контакта.

При отсутствии сигналов на входе испытуемой ИС, синхронных сигналов с выходов блока 3 компараторов или неправильном их количестве счетчики 12 не опрокинут соответствующие RS-триггеры 14, на информационных входах элементов 2 ИЛИ схемы совпадения будет присутствовать уровень логического "0". При этом, если на спаренном входе элемента 2 ИЛИ установить по линии МАСКА уровень логической "1", тогда простым перебором по шине МАСКА можно установить, какой информационный сигнал не поступил на вход элемента 2 ИЛИ, добиваясь срабатывания схемы 16 совпадения и получения на линии ИНФОРМ уровня логического "0". При наличии статического контролируемого сигнала с выхода испытуемой ИС блок 3 компараторов вырабатывает синхронный выходной статический сигнал (работа аналогично динамическому сигналу), который поступает на вход блока 5 анализа и через логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ (1-) 18 и соответствующий ключ 15 поступает на вход 2 ИЛИ схемы 16 совпадения. При этом блок 6 управления по шине ИНВЕРСИЯ в линии к элементу исключающее ИЛИ (1-) инвертирует контрольный сигнал через элемент исключающее ИЛИ (1-), установив логическую "1" на линию ИНВЕРСИЯ, если последний должен прийти уровнем логического "0", или контрольный сигнал не инвертируется, если он должен прийти уровнем логической "1". Тем самым выполняются условия работы схемы 16 совпадения.

После окончания цикла блок 6 управления выключает формирователи 7, блок 2 коммутации подключает следующую ИС, цикл повторяется.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для функционального контроля больших интегральных схем | 1990 |

|

SU1798743A1 |

| Устройство для функционального контроля больших интегральных схем | 1990 |

|

SU1809398A1 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО ИЗМЕРЕНИЯ ВРЕМЕННЫХ ПАРАМЕТРОВ | 1999 |

|

RU2180450C2 |

| Устройство для контроля контактирования логических блоков | 1989 |

|

SU1762281A1 |

| Устройство для управления шаговым двигателем | 1989 |

|

SU1686691A1 |

| Устройство контроля контактирования интегральных схем | 1986 |

|

SU1383231A1 |

| Устройство для контроля контатирования интегральных схем | 1982 |

|

SU1049912A1 |

| СПОСОБ КОНТРОЛЯ КОНТАКТИРОВАНИЯ КМОП-БИС И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2009518C1 |

| Способ обработки изделий в ультразвуковом поле и устройство для его осуществления | 1990 |

|

SU1752444A1 |

| Измеритель параметров комплексных сопротивлений | 1989 |

|

SU1751690A1 |

Изобретение может быть использовано в автоматизированных устройствах контроля интегральных схем (ИС) при проведении групповых испытаний. Устройство содержит блок 1 контактирования, блок 3 компараторов, блок 4 опорных напряжений, блок 6 управления, источник 8 напряжения. Введение в устройство блока 2 коммутации, блока 5 анализа и формирователя 7 импульсных сигналов позволяет использовать его для контроля контактирования ИС при проведении групповых испытаний (например, электротермотренировки) в динамическом режиме, при этом повышается достоверность контроля. 1 з.п.ф-лы, 4 ил.

| Устройство контроля контактирования интегральных схем | 1986 |

|

SU1383231A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1994-09-30—Публикация

1991-01-08—Подача