СП

О5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема частотно-фазовых сигналов | 1987 |

|

SU1543563A1 |

| Демодулятор фазоманипулированных сигналов | 1988 |

|

SU1518902A1 |

| УСТРОЙСТВО ДЛЯ ОПОВЕЩЕНИЯ О ПАВОДКЕ ИЛИ СЕЛЕ | 2003 |

|

RU2235364C1 |

| Система для передачи и приема сигналов с фазочастотной манипуляцией | 1986 |

|

SU1354427A1 |

| Приемник фазоманипулированных сигналов | 1982 |

|

SU1022330A1 |

| СИСТЕМА ДЛЯ ПРЕДУПРЕЖДЕНИЯ О ЗЕМЛЕТРЯСЕНИЯХ И ЦУНАМИ | 2007 |

|

RU2349939C1 |

| ЦИФРОВОЙ ДЕМОДУЛЯТОР СИГНАЛОВ С МНОГОПОЗИЦИОННОЙ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2021 |

|

RU2776968C1 |

| Устройство для демодуляции фазоманипулированного сигнала | 1982 |

|

SU1061286A1 |

| Формирователь опорного напряжения для демодулятора фазоманипулированных сигналов | 1988 |

|

SU1552391A1 |

| Устройство для передачи и приема сигналов с фазовой манипуляцией | 1989 |

|

SU1732486A2 |

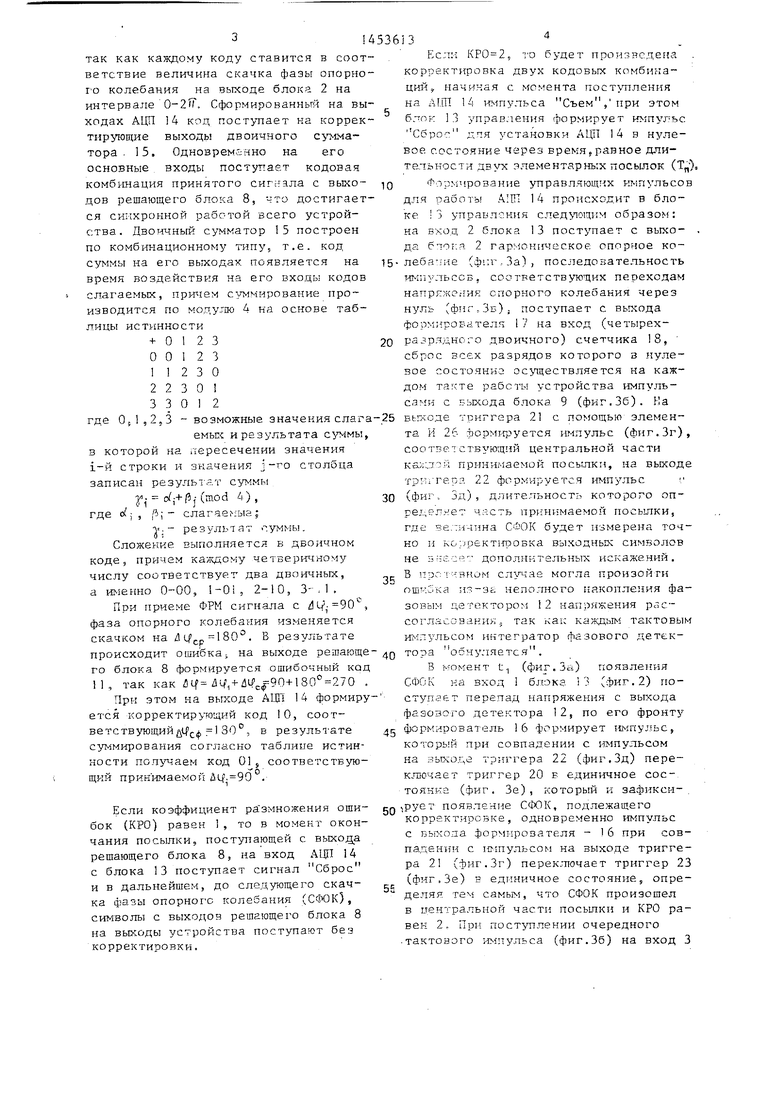

Изобретение относится к технике связи. Цель изобретения - повышение помехоустойчивости. Устр-во содержит : блок предварительной селекции, блок 2 формирования опорного колебания, фазовые детекторы 3, 4 и 12, фазовра- цатель 5, блоки 6, 7 и 1 задержки, решающий блок 8, блок 9 тактовой синхронизации, делитель 10 частоты, блок 13 управления (БУ), АЦП 14 и двоичный сумматор 15. В отсутствие скачка фазы оба принятых символа в квадратурном и синфазном подканалах пост т1ают на выходы сумматора 15 без изменен1гй. Если при приеме сигнала фазо эазностной модуляции изменилась скачком фаза опорного колебания, то произойдет ошибка и на выходе решающего блока 8 будет сформирован ошибочный код, который корректируется в сумматоре 15 с помощью кода, сформированного на выходе АЦП 14. 3 i-m.

0us.1

Изобретение относ итя к технкке связи и может использTFаться н системах передачи дамньк ij.-и на. 1,ч.мн с фазо разностной модуляцией (ФРМ) первсзго порядка,

Цель изобретения: - повышение поме X о у с то Гтч ив о с ти .

На фиг. 1 изображена структурная эдектрическая схема и оедлох енного

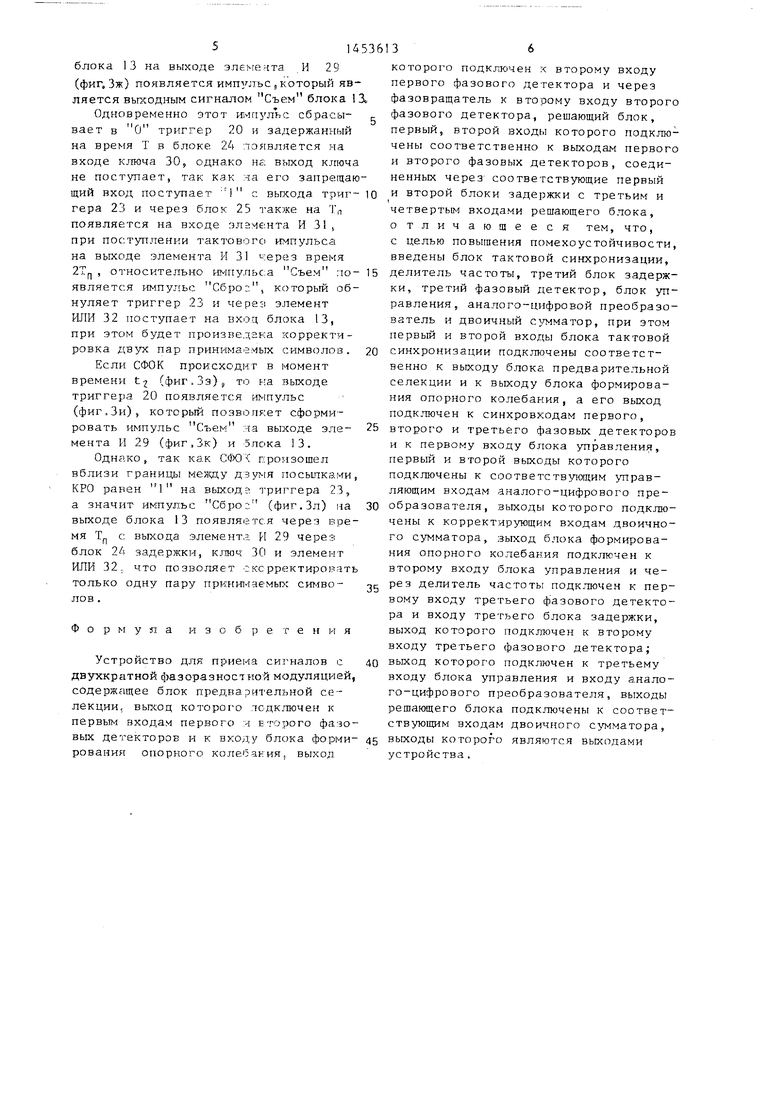

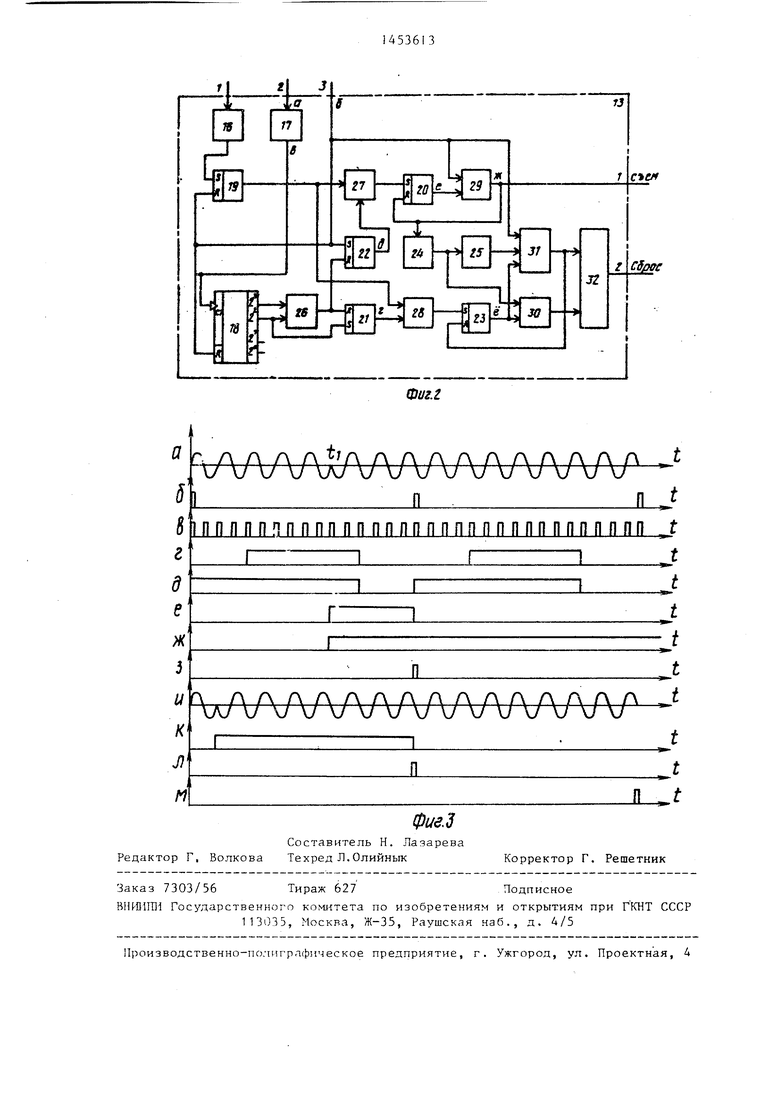

устройства; на фиг. 2 - структурная электрическая схема б.юка управления на фиг. 3 - временные л,иаграммы.

Устройство содер жит блок 1 предварительной селекции, блок 2 формирова ния онорно- о колебания , первьй 3, второй 4 фазовые детекторы, фазовра- |цатель 5, первый 6, второй 7 блоки задержки, решающий блс К 8, блок 9 тактовой синхронизацнн, делитель 10 частоты, третий блок М задержки, третий фаз(звый детек : ()р 12, блок 13 управления, аналого -цифровой преобразователь 14, ДВОИЧНЫ сумматор 15. Блок 13 управления содержит формиро- ватель 16 импз льсов, соормирователь 1 последовательности импульсов, счетчик 18, триггеры 19-23, блоки 24 и 25 задержки, элементы И 26-29, ключ 30,элемент И 31, элек&1 т ИЛИ 32,

Устройство работает :;ледуюшим образом .

Приним:аемый сигнал дву-ккратной ФРМ, прошедший блок 1 предварительно селекции, поступает на первые входы фазовых детекторов 3 и 4 синфазной и квадратурной ветвей, на вторые входы которы х подается спорное напряжение. С вькода блока 9 тактовой синх- ронизации поступают управляющие импульсы на синхровходы фазовых детекторов 3 и 4, на вьког.е которых формируются видеоимпульсы з соответствие с разностью фаз вхо1;ного сигнала и опорного колебания, формируемого блоком 2, Решающий блок 8 сравнивает принятые ст- мволы обоух подканалов с сиь(волами предыдущей посылки, которые запоминаются в бток.ах 6 и 7, формируя при атом на своих вькодах два символа, соответствукп .их принятой разности фаз, причем n -оо, , 80°-10, 270°-1 1 .

В отсутствие скачка фазы оба символа посттеают на вькоды двоичного сумматора 15 без и:эмене(ий. Если в момент времени : , происходит скачзк

фазы огюрног-о колебан 1я I/5 tf |- --- то

СФ Д

это приводит к ошибочному приему сигналов, на выходах решающего блока 8 появляется пара символов, соответствующая

(М ,,- Ч ;,,)+Зс/,,

где

величина скачка фазы опор

ного колебания; Lf, - фаза сигнала г-ринимаемой

посылки; if.- фаза сигнала предьщущей

посылки,

На выходе делителя 10 частоты а У. уменьогается з четыре раза. Такое из- мение масштаба фазовой плоскости опорного колебания позволяет измеритьЛ1;,на интервале О- | , получая

на выходе фазового детектора 12 напряжение рассогласования, пропордио- нальное йЦ, между напряжением опорного колебания

OK -)UOCOS(W t/4-f (

iiJ ct

)

MM 4

и опорным колебанием, задержанным на t|, с помощью блока I задержки

и

ок (t+t -p UpCosCuiCt+t )/4+ %) ,

где начальная фаза опорного колбания, положим равной О, тогда

Qлс

50

5

(0

и,

г f,,- W Uod Vct

Jo.-(t + tp- cos -.

Затем это напряжение с выхода фазового детектора 12 поступает на вход аналого-цифрового преобразователя (АЦ11) 14 и в блок 13 управления, где определяется момент скачка фазы, коэффигдаент размножения опгибок, который равен , если скачек произошел вблизи границ между двумя посьшками, т.е. искажена только 6,. посьпка, и равен 2, если скачек произошел в средней части посылки b ,--i , в этом ошибочно принимаются Ь; и Ь . , мосыл- ки и далее формируются с учетом этого коэффициента, управляющие импульсы для запуска и сбороса АЩ1 14.

При поступлении импульса Съем с выхода блока 13 на вход А1Д1 14 в последнем происходит преобразование , пропорционального Л Lfj.B двоичный код, при этом код 00 соответствуi1 на интерй фня интервале +45

вале 45-135

10

на

интервале 135225 ° и 01 на интервале 225-31 5 Здесь как раз и происходит обратное ггреоб- рачованис масштаба фазовой плоскости.

так как каждому коду ставится в соответствие величина фазы опорного колебания на выходе блока 2 на интервале О-2ГГ. Сформированный на выходах АЦП 14 код поступает на корректирующие выходы двоичного с мма- тора . 15. Одновремйнно на его основные входы поступает кодовая комбш ация принятого с выходов решающего блока 8, что достигается симхронной работой всего устройства. Двот-гчный сумматор 15 построен по комбинадионному типу, т.е. код суммы на его выходах появляется на время воздействия на его входы кодов слагаемых, причем суммирование производится по модулю 4 на основе табицы истинное + О 1 0012 1123 2230 3301

и

2 3 3 О

2

где О;1,2.3 - возможные значениясла

емьк и результата в которой на пересечении значения i-й строки и значения j-го столбда записан результат суммы

Т{ (5/i+P,-(n).od 4) , где ( , 6; - слагаемые;

Л .- результат суммы.

Сложение выполняется в двоичном коде, причем каждому четверичному числу соответствует два двоичных, а именно 0-00, -Oi, 2-10, 3- ,1 ,

При приеме Ф РМ сигнала с фаза опорного колебания изменяется скачком на . В результате происходит оши бка; на выходе решаю го блока 8 формируется ошибочный к 11, так как 54 Л,+ /5М с 90+180° 270

При этом на выходе АЦП 14 форми 0, соот

ется корректир то1дии код ветствуюш,ий(.ф 1 30°, в результате суммирования согласно таблице истиности получаем код 01j соответствующий прин имаемой Д1. 90 .

Если коэффидиент ра змножения ошибок (КРО) равен 1, то в момент окончания посылки, поступающей с выхода решающего блока 8, на вход АЦП 14 с блока 13 поступает сигнал Сброс и в дальнейшем, до следующего скачка фазы опорного колебания (СФОК), сш 5волы с выходов решающего блока 8 на вькоды устройства поступают без корректировки.

536J3

Есл:-: КРО 2, то будет произведена корректировка двух кодовых комбина- дни, начиная с момента постчтления на 14 импульса Съем, при этом блок 13 управ. тения формирует импульс Сброс дня установки АЩТ 14 в нулевое, состояние через времЯ}равное длительности двух элементарных посылок („). 1011 ор -1чрование управляющих га-шульсов

для работы А Ш 14 происходит в блоке 3 управлс:ния след пощим образоь : на вхо.о; 2 блока 13 поступает с выхо- . да 2 гар:-.1оническое опорное ко0

0

5 БЫЛ

5

5- леба ие (фиг , За) , последовательность иг 1пу льсоБ. соответствующих переходам напряжогшя спорного колебания через нуль (ФИГ,ЗБ); поступает с выхода форм;-;роБателя 17 на вход (четырехразрядного двоичного) счетчика 18, сброс всех разрядов которого з нулевое состояниз ос тцествляется на каждом такте работы устройства импуль- с выхода блока 9 (фиг. 36). На

де триггера 21 с помощью элемента И 26 эормргруется импульс (фиг.Зг), соответствующий центральной части ка;;;д 3-й принимаемой посььлкп, на вькоде трк; гера 22 форм лруется 1мпульсс

(фигч Зд), длительность которого оп- ределмет чясть принимаемой посылки, где зе;:ичнна будет измерена точно и ког ректировка выходньк символов не S - ecft-: дополнительных искажений. В прг: |. -нном могла произойти ошт. Зка из-зй неполного накопления фазовым детектором 12 напряжения рлс- согласованик 5 так как тактовым ш ьтульсом интегратор фазового детектора обну.чяется.

В момент t (фиг.Зй) появления СФОК на вход блока 13 (фиг.2) поступает перепад напряжения с выхода фазового детектора 12, по его фронту формирователь 16 формирует импу;дьс, которь Й при совпадении с импульсом на выходе триггера 22 (фиг.Зд) пере- клзочает триггер 20 в единичное состояние (фиг. Зе), который и эафиксм-.

рует появление СФОК, подлежащего корректировке, одновременно импульс с Бьо-юла формирователя - 1 6 при совпадении с импульсом на выходе триггера 2 (фиг.Зг) переключает триггер 23 (фиг.Зе) в единичное состояние, определяя тем самым, что СФОК произошел в иентральной части посьшки и КРО равен 2, При поступлении очередного

.тактового и пульса (фиг. 36) на вход 3

0

5

0

5

S14

блока 13 на выходе элемента И 29 (фиг, Зж) появляется импульс (Который является выходным сигнс1лом Съем блока

Одновременно этот И 1аульс сбрасы- вает в О триггер 20 и задержанный на время Т в блоке 24 оявляется на входе ключа 30, однако нг; выход к.ггюча не поступает, так как его запрещающий вход поступает М с выхода триг- гера 23 и через блок 25 также на Тп появляется на входе элэме:нта И 31 , при поступлении тактов эгс И чпульс.а на вькоде элемента И 31 1 :ерез время 2Т , относительно tMnyribcia Съем :ю- является импульс Сбро::, который обнуляет триггер 23 и чере;| элемент ИЛИ 32 поступает на вход блока 13, при этом будет произве.цгка корректировка двух пар принима-эмых символов.

Если СФОК происходн:т в момент времени t (фиг.Зз), то на выходе триггера 20 появляется импульс (фиг.Зи), который позв1:1ляет сформировать импульс Съем ла выходе эле- мента И 29 (фиг.Зк) и Злока 13.

Однако, так как произошел вблизи границы между д:эумя посьшками, КРО равен 1 на ВЫХОДЕ- триггера 23, а значит импульс Сбро:. (фиг. 3л) на выходе блока 13 появля12тс.я через время Т с выхода элемента И 29 через блок 24 задержки, к.гюч 30 и элемент ИЛИ 32, что позволяет Г.ксрректировать только одну пару прини1 1аемьпс симво- лов .

Формула изобретем и я

Устройство для приерьа сигналов с двухкратной фазоразностной модуляцией, содержащее блок предварительной селекции, выход которого подключен к первьм входам первого i второго фазовых детекторов и к вхол;у блока форми- рования опорного колебания,: выход

которого подключен к второму входу первого фазового детектора и через фазовращатель к второму входу второг фазового детектора, решающий блок, первый, второй входы которого подключены соответственно к выходам первог и второго фазовых детекторов, соединенных через соответствующие первый и второй блоки задержки с третьим и четвертым входами решающего блока, отличающееся тем, что, с целью повышения помехоустойчивости введены блок тактовой синхронизации, делитель частоты, третий блок задержки, третий фазовый детектор, блок управления, аналого-цифровой преобразователь и двоичный с лчматор, при этом первый и второй входы блока тактовой синхронизации подключены соответственно к выходу блока предварительной селекции и к выходу блока формирования опорного колебания, а его выход подключен к синхровходам первого, второго и третьего фазовых детекторов и к первому входу блока управления, первый и второй выходы которого подключены к соответствующим 5,т1рав- ляющим входам аналого-цифрового преобразователя, выходы которого подключены к корректирующим входам двоичного сумматора, выход блока формирования опорного колебания подключен к второму входу блока управления и через делитель частоты подключен к первому входу третьего фазового детектора и входу третьего блока задержки, выход которого подключен к второму входу третьего фазового детектора; выход которого подключен к третьему входу блока управления и входу аналого-цифрового преобразователя, выходы решающего блока подключены к соответствующим входам двоичного сумматора, вькоды которого являются выходами устройства.

Редактор Г, Волкова

Составитель Н. Лазарева Техред Л.Олийнык

фие.З

Корректор Г. Решетник

| Цифровое телевидение./Под ред | |||

| М.И | |||

| Кривошеева | |||

| М.: Связь, 1980, с.150. |

Авторы

Даты

1989-01-23—Публикация

1987-01-22—Подача