ел

Изобретение относится к технике связи и может быть использовано в системах передачи данных сигнала с фазовой манипуляцией.

Цель изобретения - повьппение помехоустойчивости .

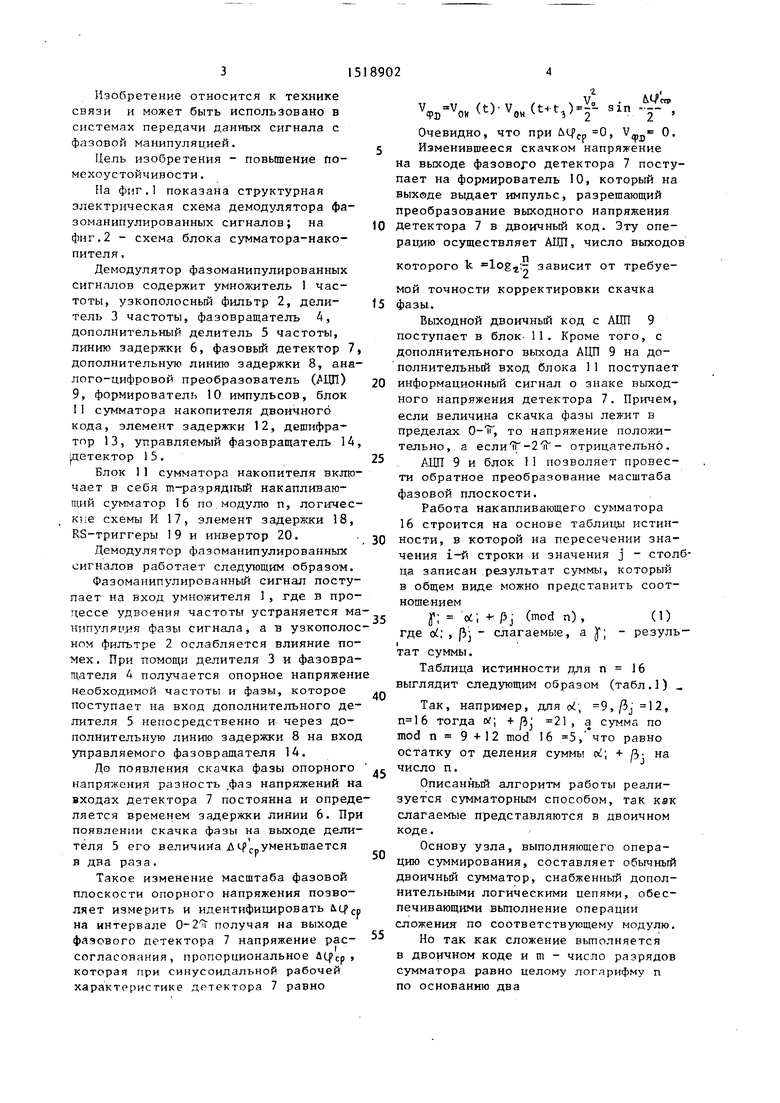

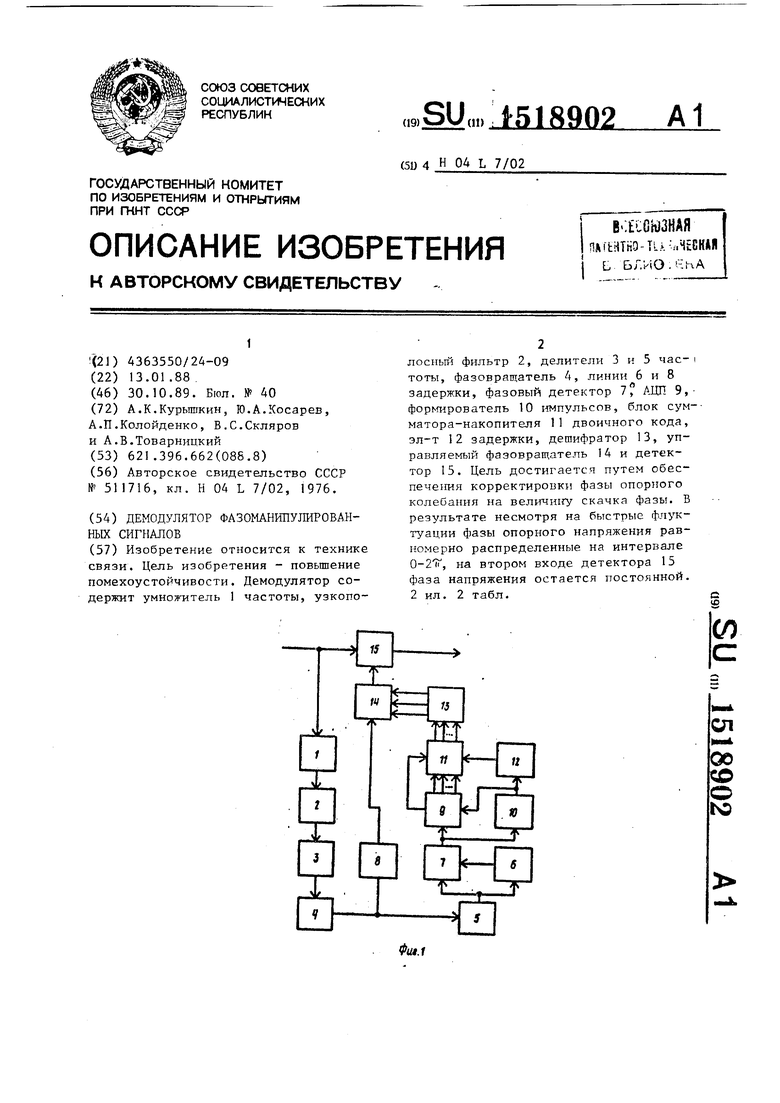

На фиг,1 показана структурная электрическая схема демодулятора фа- зоманипулированных сигналов; на фиг.2 - схема блока сумматора-накопителя .

Демодулятор фазоманипулированных Сигналов содержит умножитель 1 частоты, узкополосный фильтр 2, делитель 3 частоты, фазовращатель 4, дополнительный делитель 5 частоты, линию задержки 6, фазовый детектор 7, дополнительную линию задержки 8, аналого-цифровой преобразователь (1Щ) 9, формирователь 10 импульсов, блок I1 сумматора накопителя двоичного кода, элемент задержки 12, дешифратор 13, управляемый фазовращатель 14, |детектор 15.

Блок 11 сумматора накопителя включает в себя т-разрядный накапливающий сумматор 16 по.модулю п, логические схемы И 17, элемент задержки 18, RS-триггеры 19 и инвертор 20.

Демодулятор фазоманипулированных сигналов работает следующим образом.

Фазоманипулированный сигнал поступает на вход умножителя 3, где в процессе удвоения частоты устраняется манипуляция фазы сигнала, а в узкополосном фихгьтре 2 ослабляется влияние помех. При помощи делителя 3 и фазовращателя А получается опорное напряжени необходимой частоты и фазы, которое поступает на вход дополнительного делителя 5 непосредственно и через дополнительную линию задержки 8 на вход управляемого фазовращателя 14.

До появления скачка фазы опорного напряжения разность .фаз напряжений на входах детектора 7 постоянна и определяется временем задержки линии 6. При появлении скачка фазы на выходе делителя 5 его величина Д Lfj-pуменьшается в два раза.

Такое изменение масштаба фазовой плоскости опорного напряжения позволяет измерить и идентифицировать на интервале 0-20 получая на выходе фазового детектора 7 напряжение рассогласования, пропорциональное Дсрср которая при синусоидальной рабочей характеристике детектора 7 равно

V V

(t)-Vo(t.t)

sin , Г

0.

СРВ ОН - он -3 2 Очевидно, что приЛд (., V. Изменившееся скачком напряжение на выходе фазового детектора 7 поступает на формирователь 10, который на выходе выдает импульс, разрешающий преобразование выходного напряжения детектора 7 в двоичный код. Эту операцию осуществляет АЦП, число выходов

которого

п

зависит от требуе5

0

5

0

5

0

5

0

5

мой точности корректировки скачка фазы.

Вьпсодной двоичный код с АЦП 9 поступает в блок- 11. Кроме того, с дополнительного выхода АЦП 9 на дополнительный вход блока 11 поступает информационный сигнал о знаке выходного напряжения детектора 7. Причем, если величина скачка фазы лежит в пределах 0-Т, то напряжение положительно, а если Г-2 п - отрицательно.

АЦП 9 и блок I1 позволяет провести обратное преобразование масштаба фазовой плоскости.

Работа накапливающего сумматора 16 строится на основе таблицы истинности, в которой на пересечении значения i-ii строки и значения j - столбца записан результат суммы, который в общем виде можно представить соотношением

У; oi; /3j (mod n), (1) где , fi- - слагаемые, а - результат суммы.

Таблица истинности для п 16 выглядит следующим образом (табл.)

Так, например, для oi 9,/3j 12, тогда о;; 21, а сумма по mod п 9+12 mod 16 5, что равно остатку от деления суммы Ы; + - на число п.

Описанный алгоритм работы реализуется сумматорным способом, так как слагаемые представляются в двоичном коде.

Основу узла, выполняющего операцию суммирования, составляет обычный двоичный сумматор, снабженный дополнительными логическими цепями, обеспечивающими вьшолнение операции сложения по соответствующему модулю.

Но так как сложение вьтолняется в двоичном коде и m - число разрядов сумматора равно целому логарифму п по основанию два

m login,

TO двоичный накапливающий cywtaTOp 16 (при n 2 ) может быть реализован последовательным соединением m - чис ла двоичных разрядов сумматора без дополнительньк логических цепей и обратной связи.

Кроме накапливающего сумматора 16 в блок 11 конструктивно входит линейка из m - числа RS-триггеров 19, образующих вторую ступень памяти, элемент задержки 18 и m логических схем И 17, которые позволяют осуществить своевременную перезапись сформированного кода из накапливающего сумматора 16 во вторую ступень памяти RS-триггеров с помощью управляющего сигнала, поступающего после окончания переходных процессов в накапливающем сумматоре 16 и обнуления RS-триггеров 19.

Двоичный код поступает на соответствующие входы дешифратора 13. Выходной сигнал с дешифратора 13 поступает на один из управляющих входо фазовращателя 14, который обеспечивает корректировку фазы опорного колебания на величину скачка фазы.

Если с течением времени возникает следующий спонтанный скачок фазы опорного напряжения, то демодулятор определяет величину этого скачка, причем соответствующие ей двоичный код суммируется с хранящимся в блоке 11 кодом первичного скачка и переза- письшается во вторую ступень памяти блока 11. Далее новый скачок фазы скорректируется, как и первый. При последующих скачках фазы сумма их величин может превысить 27.

В этом случае накапливающий сумматор в блоке 11 позволяет учесть периодичность тригонометрических фунций, описьюающих опорный сигнал.

Работу демодулятора фазоманипули- рованных сигналов можно пояснить на конкретном примере.

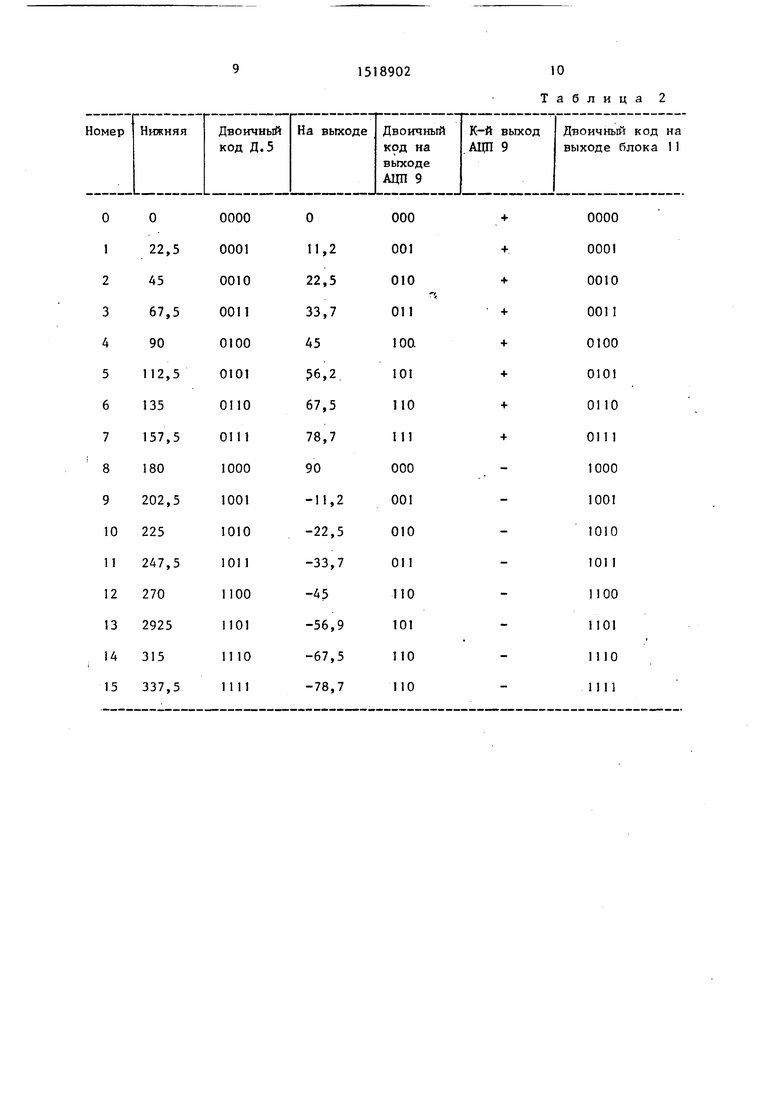

Пусть интервал 0-211 разбит на 16 подинтервалов () по 22,5.

Каждому значению угла соответствует 4-разрядный двоичный код (см. табл . 2) .

В общем случае n должно равняться целой степени числа 2 (8 по 45); (16 по 22,5°); (32 по 11,25°); (64

по 5,6 ) и т.д.

При п 16АЦП 9 должен иметь восемь точек отсчета и число выходов k-.l 3.

Четвертый (k-й) разряд, старший для блока 1I, формируется с помощью инвертора 5 на основании сигнала с дополнительного выхода АЦП 9, зависящего от полярности преобразован- Q ного в двоичный код напряжения. При положительной полярности это 1, при отрицательной О.

Тогда скачок фазы на выходе фазовращателя 4Atfc f 315 (-45°) на вы- 5 ход делителя 5 ДЧе -22,5 приведет к появлению на выходе фазового детектора 7 напряжения Уфд/ sin ЛМ счр Аид 9 к вьщает код - 010.

Однако такой же код был бы сформи- 0 ровен на выходе АЩ и в случае скачка фазы ЛС/ст 5 . Эту неоднозначность позволяет разрешить сигнал 6 дополнительного выхода АЦП, несущий ин- формапдю о знаке выходного напряже- 5 ния фазового детектора 7. Поэтому в рассматриваемом случае скачку фазы uQ crf, -43- соответствующий код 1010, а uq;c.( код 0010.

На выходе блока 11 сформируется 0 код 1010 при этом на соответствующем выходе дешифратора 13 появится сигнал, который и определит величину корректирующего сдвига фазы в управляемом фазовращателе 14 (-45°).

Таким образом, несмотря на быстрые флуктуации фазы опорного напряжения, равномерно распределенные на интервале 0-21, на втором входе детектора 15 фаза напряжения остается

Q ПОСТОЯНИОЙ.

5

Форм.ула изобретения

Демодулятор фазоманипулированиых сигналов, содержащий детектор и по5 следовательно соединенные умножитель частоты, узкополосный фильтр, делитель частоты и фазовращатель, последовательно соединенные линию задержки и фазовый, детектор, второй вход

0 которого соединен с входом линии задержки, объединенные первый вход детектора и вход умножителя частоты являются входом демодулятора, а выход детектора является выходом демо5 дулятора, отличающийся тем, что, с целью повышения помехоустойчивости, в него введены дополнительная линия задержки, дополнительный делитель частоты, аналоге7151

цифровой преобразователь (/Ш) и последовательно соединенные формирователь импульсов, элемент задержки, блок сумматора-накопителя, дешифратор и управляющий фазовращатель, выход которого подключен к второму входу детектора, а вход через дополнительную линию задержки - к объединенным выходу фазовращателя и входу дополнительного делителя частоты.

9028

выход которого подключен к объединенным входам линии задержки и фазового дете ктора, выход которого подключен к объединенным сигнальным входам АЦП и формирователя импульсов, выход которого через АЦП подключен к информационным входам блока сумматора-накопителя, к сигнальному входу которого подключен дополнительный выход АЦП.

10

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь опорного напряжения для демодулятора фазоманипулированных сигналов | 1988 |

|

SU1552391A1 |

| ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2008 |

|

RU2393641C1 |

| ИЗМЕРИТЕЛЬ ФАЗ ОСЦИЛЛОГРАФИЧЕСКИЙ | 2005 |

|

RU2314543C2 |

| Устройство для передачи и приема сигналов с фазовой манипуляцией | 1989 |

|

SU1732486A2 |

| ОДНОКАНАЛЬНАЯ МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОПРЕДЕЛЕНИЯ НАПРАВЛЕНИЯ НА ЦЕЛЬ | 1997 |

|

RU2108595C1 |

| Осциллографический фазометр | 1988 |

|

SU1550435A1 |

| Устройство для распознавания импульсных сигналов с внутриимпульсной модуляцией | 1988 |

|

SU1580569A2 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1322477A1 |

| Устройство для приема сигналов с двухкратной фазоразностной модуляцией | 1987 |

|

SU1453613A1 |

| ФАЗОВЫЙ СПОСОБ ПЕЛЕНГАЦИИ И ФАЗОВЫЙ ПЕЛЕНГАТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2012 |

|

RU2518428C2 |

Изобретение относится к технике связи. Цель изобретения - повышение помехоустойчивости. Демодулятор содержит умножитель 1 частоты, узкополосный фильтр 2, делители 3 и 5 частоты, фазовращатель 4, линии 6 и 8 задержки, фазовый детектор 7, АЦП 9, формирователь 10 импульсов, блок сумматора-накопителя 11 двоичного кода, элемент 12 задержки, дешифратор 13, управляемый фазовращатель 14 и детектор 15. Цель достигается путем обеспечения корректировки фазы опорного колебания на величину скачка фазы. В результате несмотря на быстрые флуктуации фазы опорного напряжения равномерно распределенные на интервале 0-2φ, на втором входе детектора 15 фаза напряжения остается постоянной. 2 ил.

Примечание: О, 1, 2, ..., 15- возможные значения слагаемых и результаты суммы.

Таблица 1

Таблица 2

фиг. 2

| Авторское свидетельство СССР № 511716, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-10-30—Публикация

1988-01-13—Подача