1

Изобретение относится к измерительной технике, связанной с измерением разности фаз двух электрических колебаний, и может быть использовано в информационно-измерительных и ра- диотехнических системах для измерения разности фаз в присутствии быстрых фазовых флюктуации.

Цель изобретения - повышение быстродействия получения достоверных результатов измерения разности фаз при ее флюктуациях.

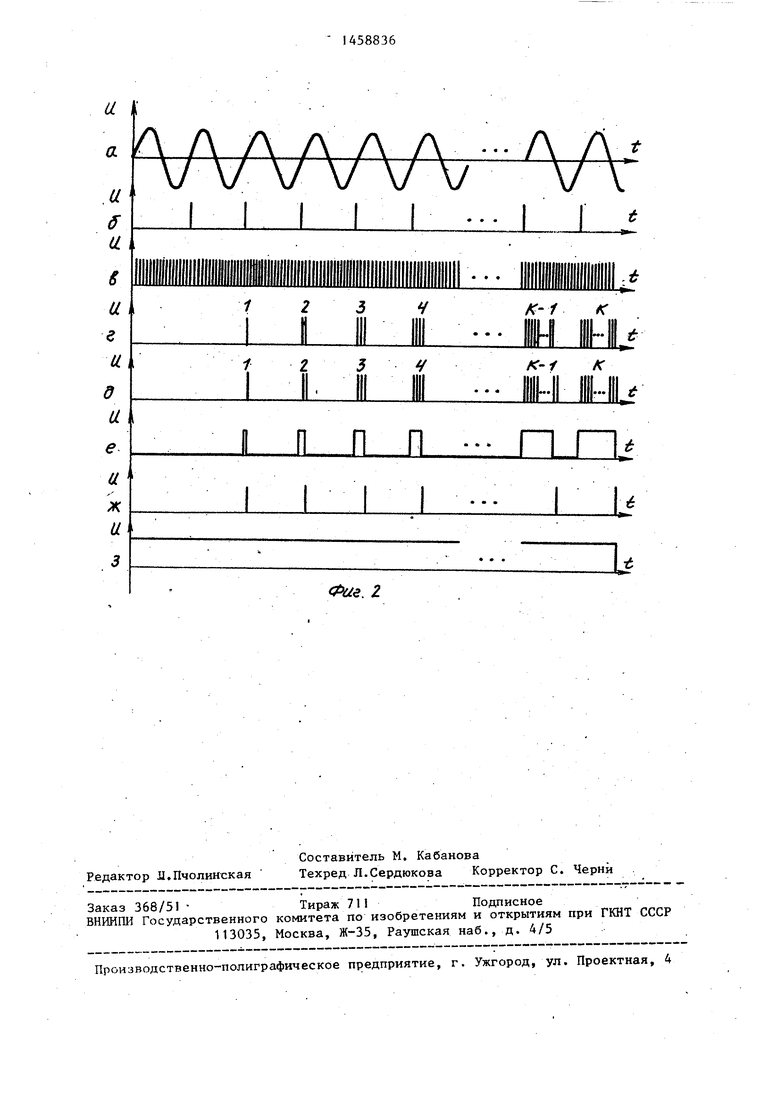

На фиг. 1 представлена функциональная схема устройства; на фиг. 2- временные диаграммы, поясняющие его работу.

Цифровой фазометр содержит -первый 1, второй 2 и третий 3 формирователи RS-триггер 4 и счетный триггер 5, первый 6, второй 7, третий 8 и четвертый 9 элементы И, элемент ИЛИ 10, реверсивный счетчик 11, клемму 12 генератора .счетных импульсов, первый 13 и второй .14 счетчики, последовательно соединенные первый делитель 15, первый р&гистр 1 6., блок 1 7 вычитания, квадратор 18, накапливающий сумматор 19, второй делитель 20, блоки 21 извлечения квадратного корня и первый компаратор 22, второй вход которого подключен к шине 23 записи, последовательно соединенные блок 24 дополнения- кода и второй компаратор 25, а также элемент 26 задержки, второй регистр 27, блок 28 памяти, блок 29 преобразования час- тоты, первый и второй выходы которого подключены соответственно к вхо дам формирователей 1 и 2 и клемму

5

0

5

0

5

43 измерительного временного интервала. Вход третьего формирователя 3 соединен с входом второго формирователя 2, входы реверсивного счетчика 11 соединены соответственно с выходами элементов И 6 и 7, первые входы которых соединены соответственно с прямым и инверсным выходами RS-триггера 4, вторые входы элементов И 6 и 7 соединены с клеммой 43 измерительного временного интервала, выходом первого компаратора 22 и управляющим входом второго регистра 27, третьи входы элементов И 6 и 7 соединены с клеммой 12 генератора счетных импульсов, а четвертые - с выходом счётного триггера 5, вход которого подключен к выходу элемента 10 ИЛИ. Цервый вхйд элемента ИЛИ 10 соединен с выходом первого формирователя 1 и с S-входом RS-триггера 4, а второй вход элемента ИЛИ 10 соединен с выходом второго формиро- вателя 2 и R-входом RS-триггера 4. Выход третьего формирователя 3 .соединен с С-входом первого счетчика 13, установочными R -входами второго счетчика 14 и накапливающего сумматора 19 и управляющими входом первого регистра 16. Выход второго к.омпа- Iратора 25 соединен с первым входом третьего элемента И 8, второй вход которого подключен к клемме 12 генератора счетных импульсов, а выход соединен с С-входом второго счетчика 14 и параллельно через элемент 26 задержки подключен к прямому входу четвертого элемента И 9 и первому управляющему, входу накапливающего сумматора 19. Второй управляющий

вход накапливающего сумматора 19 соединен с выходом четвертого элемента И 9, инверсный вход которого подключен к выходу второго компаратог ра 25.

Вход блрка 2в памяти соединен с выходом первого делителя 15, первьми входами подключенного к выходу реверсивного счетчика 11, а вторыми - к выходу первого счетчика 13, вторым входам второго делителя 20 и второго компаратора 25, а также к а дрес- ному входу записи блока 28 памяти, адресный вход считывания которого соединен с выходами второго счетчика 14 и входом блока 24 дополнения кода выход блока 28 памяти соединен с вторым входом блока 17 вычитания. Выходы первого регистра 16 подключены к входам второго регистра 27, выход ко торого является выходом цифрового фазометра , При этом первый и второй входы блока 29 преобразования частоты являются соответственно первым и вторым входами цифрового фазометра.

В состав блока 29 преобразования частоты входят последовательно соеди ненные первый смеситель 30, первый фильтр 31, второй смеситель 32 к первый УПЧ 33, последовательно соединенные третий смеситель 34, второй фильтр 35, четвертый смеситель 36 и второй УПЧ 37, последовательно соединенные усилитель 38, пятый смеситель 39 и третий фильтр 40, а также первь и второй гетеродины 41 и 42. Выход первого гетеродина 41 подключен к управляющим входам первого и третьего смесителей 30, 34, выход второго гетеродина 42 подключен к управляю- щему входу пятого смесителя 39, выхо третьего фильтра 40 подключен к управляющим входам второго и четвертого смесителей 32 и 36, а вход усилителя 38 соединен с выходом второго фильтра 35. Входы смесителей 30 и 34 являются соответственно первым и вторым входами блока 29 преобразования частоты, первым и вторым выходам которого являются соответственно выходы УПЧ 33 и 37.

0

5

Блок 29 путем двойного преобразования частоты -обеспечивает формирование на первом и втором выходах соответственно опорного и измеряемого сигналов промежуточной частоты, равной частоте второго гетеродина 42, которая не зависит от частоты входного сигнала. При этом разность -фаз сигналов на промежуточной частоте равна разности фаз между опорным и измеряемым входными сигналами. Этим обеспечивается возможность работы устройства в широком частотном диапазоне входных сигналов.

Опорный сигнал промежуточной частоты с первого выхода блока 29 посту- пает на вход формирователя 1. На входы формирователей 2 и 3 подается из- 0 меряемый сигнал (фиг. 2а) промежуточной частоты с второго выхода блока 29.

Формирователи 1 и 2, триггеры 4 и 5. элементы И 6 и 7 и элемент ИЛИ 10, 5 обеспечивают формирование временных интервалов, соответствующих разности фаз , измеряемого и опорного сигналов в каждом J-M периоде, и заполнение этих интервалов счетными импульсами, поступающими с клеммы 12 генератора счетных импульсов соответственно через элементы И 6 и 7 на вычитающий и суммирующий входы реверсивного счетчика II. С выхода реверсивного счетчика 11 цифровой код, соответствующий сумме значений фаз tpj , измеренных в каждом J-M периоде, поступает на первый выход делителя 15, где делится на количество периодов сих нала, которое определяется счетчиком 13 по числу импульсов, поступивших На его вход с выхода формирователя 3 (фиг. 2б), и в виде цифрового кода с выхода счетчика I3 подается на второй вход делителя 15. Импульсы с выхода формирователя 3 (фиг. 26) формируются по концу каждого j-ro периода сигнала.

0

5

0

5

50

Таким образом, определяется цифровой код среднего значения измеряемой фазы по окончании каждого j-ro периода сигнала (фиг. 2а)

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой одноканальный инфранизкочастотный фазометр | 1987 |

|

SU1472831A1 |

| Цифровой фазометр-частотомер | 1987 |

|

SU1471148A1 |

| Измерительный двухфазный генератор | 1987 |

|

SU1442931A1 |

| Устройство индикации пеленга | 1983 |

|

SU1167555A1 |

| Цифровой фазометр и его варианты | 1982 |

|

SU1020781A1 |

| Грозопеленгатор-дальномер | 1984 |

|

SU1187120A1 |

| Цифровой фазометр | 1985 |

|

SU1290197A1 |

| Устройство для измерения сдвига фаз | 1986 |

|

SU1381406A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Корреляционный измеритель фазовых соотношений узкополосных случайных процессов | 1990 |

|

SU1714616A1 |

Изобретение может быть использовано в информационно-измерительных системах и является усовершенствованием изобретения по авт.св. №1112309. Цель изобретения - получение досто- верньк результатов измерения разности фаз при ее флюктуациях. Постав ленная цель достигается введением в фазометр последовательно соединенных делителя 15, первого регистра 16 и второго регистра 27, а также после- .довательно соединенных блока 29 преобразования частоты, формирователя 3, счетчика 13, блока 28 памяти, блока 17 вычитания, квадратора 18, накапливающего сумматора 19, второго делителя 20, блока 21 извлечения квадратного корня и компаратора 22, последовательно соединенных компаратора 25, элемента И 8 и элемента 26 задержки, выход которого соединен с входами накопительного сумматора непосредственно и через элемент И 9, второй вход которого соединен с выходом компаратора 25, вход которого соединен с входом делителя 15, выходом счетчика 13 и вторым входом деi (Л

Устройство работает следующим образом.

На первый и второй входы блока 29. преобразования частоты поступают соответственно опорный и измеряемый сигналы.

55

j

tf, + Vi +... + q j

Полученное среднее значение фазы (| записывается в регистр 16 и в блок 28 памяти, на адресный вход записи которого с выхода счетчика 13 подается цифровой код, соотв-етствую- щий числу 3 периодов сигнала. Запись среднего значения фазы Cf в ре- гистр 16 осуществляется каждым импульсом с формирователя 3 (фиг, 26), поступающий на его управляющий

При этом в процессе измерений в блоке 28 памяти хранятся коды всех средних значений фаз tf, t Cfj , а регистр 16, обновляя инфор- . мадию после каждого j-ro периода, содержит только код среднего значения фазы (. , который поступает на вход регистра 27 и на первый вход блока 17 вычитани,я.

Считывание информации из блока 28 памяти осуществляется кодом, который поступает с выхода счетчика 14 на адресный вход считывания блока 28.

Код считывания формируется из последовательности счетных импульсов, поступающих с клеммы 12 (фиг. 2в) на второй вход элемента И 8, на первый вход которого подаются импульсы, сформированные компаратором 26 (фиг. 2е) путем сравнения кода с выхода счетчика 13 и кода с выхода счетчика 14, увеличенного на единицу блоком 24 дополнения кода. Импульсы, сформированные на выходе элемента И 8 (фиг. 2г), поступают на С-вход счетчика 14 и через элемент 26 за- держки на управляющий вход накаплива ющего сумматора 19. ,

Счетчик 14 и накапливающий сумматор 19 обнуляются после каждого j-ro периода измеряемого сигнала импульса ми, поступающими на их установочные Rg-входы с выхода формирователя 3 (фиг. 2б). Тем самым в течение каждого последующего (начиная с т ретьего) периода измеряемого сигнала (фиг.2а) обеспечивается последовательное поступление с выхода блока 28 памяти на второй вход блока 17 вычитания кодов средних значений фаз Cf, , i ,,., tf ;., измеренных за предыдущие (J-1) периодов сигнала.

На выходе устройства 17 вычитания формируется последовательность кодов (t, -tpj), (cpj-Cfj),..., (cfj.,-cpj) которая через квадратор 18 поступает на вход накапливающего сумматора 19. При поступлении на первый управляющий вход накапливающего сумматора 19 импульсов, задержанньо; элементом 26

задержки (фиг. 2д) относительно импульсов с выхода элемента И 8 (фиг.2 на время ut ,(где Т - период следования счетных импульсов (фиг.2в определяемое процессом получения по- слёдовательности кодов ( ц, - Cfj ) , ((г - j),..., (Cfj-, -q-j) на выходе квадратора 18, накапливающий сумматор 19 формирует сумму этих кодов, которая при поступлении на второй его управляющий вход импульса с выхода элемента И 9 (фиг. 2ж) передается на вход делителя 20.

Импульсы формируются на вькоде элемента И 9 при поступлении на его прямой вход импульсов с выхода элемента 26 задержки (фиг. 2д), а на инверсный вход - импульсов с выхода компаратора 25 (фиг. 2е).

На второй вход делителя 20 с выхода счетчика 13 подается цифровой код, соответствующий ко|1ичеству j периодов измеряемого сигнала (фиг.2а в KOTOpiaix произведено измерение фазы

Блок 21 извлечения квадратного корня формирует цифровой код средне- квадратического отклон1ения ( , среднего значения фазы (fj... Цифровой код G. , поступая на первый вход ксгмпаратора 22, сравнивается в нем с кодом заданной погрешности измерения U , поданной на второй вход компаратора 22 с шины 23 записи. При выполнении условия (jh. U компаратор 22 формирует отрицательный перепад (фиг. 2з), который поступает на клемму 43 измерительного временного интервала и на вторые входы элементов И 6 и 7, а также на управляющий вход регистра 27. При этом прекращается дальнейший процесс измерения и обеспечивается вывод среднего значения фазы сигнала с регистра 27 на вход устройства. Фазометры позволяют по сравнению с прототипом обеспечить заданную точность измерения разности фаз путем накапливания информации о флюктуирующей фазе сигнала с проверкой этой информации на достоверность в процессе измерений. Этим достигается возможность получения оптимального времени измерения разности фаз сигналов в зависимости от интенсивности фазовых флюктуации и заданной погрешности измерения.

Проверка на достоверность информации о флюктуирующей фазе сигнала

в процессе измерения позволяет повысить оперативность измерений.

Формула изобретения

Цифровой фазометр по авт. св. № 1I12309, отличающийся тем, что, с целью повьшения быстродействия полученных достоверных ре- зультатов измерения разности фаз при ее флюктуациях, в него введены блок преобразования частоты, первый и второй выходы которого подключены соответственно к входам первого и второго формирователей, последовательно соединенные третий формирователь и первый счетчик, причем вход третьего формирователя подключен к входу второго формирователя, после- довательно соединенные первый делитель, первый регистр, блок вычитания квадратор, накапливающий сумматор, второй делитель, блок извлечения квадратного корня и первый компара- тор, второй вход которого подключен к шине записи, а выход соединен с клеммой измерительного временного интервала, последовательно соединенные блок дополнения кода, второй компа- ратор, третий элемент И, элемент задержки, выход которого соединен с первым управляющим входом накапливающего сумматора, а также четвертый элемент И, выходом подключенный к второму управляющему входу накапливающего сумматора, прямым входом - к выходу элемента задержки, а инверсным входом - к выходу второго компаратора, второй счетчик, второй регистр и блок памяти, входы которого соединены с выходами Первого делтеля, первыми входами подключенного к выходам реверсивного счетчика , а вторыми - к выходам первого счетчик вторым входам второго делителя, второго компаратора и адресным входам записи блока памяти, адресные входы считывания которогЬ соединены.с выходами второго счетчика и входами блока дополнения кода, а выходы блока памяти соединены с вторыми входами блока йычитания, при этом второй вход третьего элемента И подключен к клемме генератора счетных импульсов, а выход - к счетному входу второго счетчика, установочный вход которого соединен с выходом третьего формирователя, управляющим входом первого регистра и установочным входом накапливающего сумматора, причем входы второго регистра соединены с выходами первого регистра, управляющий вход второго регистра подключен к выходу первого компаратора, а выход второго регистра соединен с выходами шины цифрового фазометра, первая и вторая входные клеммы которого соединены соответственно с первым и вторьгм входами блока преобразования частоты.

а о.

.а

ff и.

S

и е и

д а

е

а

ж. и

I I /

/г-у

л--/

п

us. Z

I I /

/г-у

л--/

п

| Цифровой фазометр | 1983 |

|

SU1112309A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-02-15—Публикация

1987-06-29—Подача