МИ -вместе первым разрядным входом .первого сумматора и разрядным входом дешифратора, выходы которого соединены с соответствующими выводами индикатора, причем вход перекоса первого сумматора первой разрядной ячейки сое динен собщей шиной, а в каждой последующей разрядной ячейке он COG JHнен с выходом переноса первого сум матора предыдущей разрядной ячейки вторые разрядные входы первых сумматоров всех разрядных ячеек соединены каждый со своим выходом установки констант блока управления, первый и второй входы которого являются соответственно первым и вторим входами блока отсчета результатов измерений, при этом счетные входы регистров памяти всех разрядных ячеек соединены с информационным выходом блока управления, а с его выходом установки нуля соединены объединенные входы установки нуля регистров памяти всех разрядных ячеек.

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент однородной вычислительной структуры | 1984 |

|

SU1211890A1 |

| Цифровой фазометр | 1972 |

|

SU438940A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УДЕЛЬНОЙ ЭЛЕКТРОПРОВОДИМОСТИ МОРСКОЙ ВОДЫ | 2007 |

|

RU2366937C2 |

| Преобразователь фаза-код | 1979 |

|

SU864542A1 |

| Цифровой фазометр | 1980 |

|

SU932423A1 |

| Цифровой компенсационный фазометр | 1980 |

|

SU920563A1 |

| Устройство для поверки фазометров | 1982 |

|

SU1057877A1 |

| Цифровой фазометр | 1986 |

|

SU1348744A1 |

| Цифровой компенсационный фазометр | 1980 |

|

SU924611A1 |

| Измерительный двухфазный генератор | 1987 |

|

SU1442931A1 |

1. ЦИФРОВОЙ ФАЗОМЕТР, содержащий фазовращатель, реверсив, ный счетчик, блок отсчета результатов измерений и фазочувствительный блок, причем выход фазовращателя соединен с первым входом фазочувствктельного блока, первый выход которого соединен с входом сложения, а второй - с входом вычитания реверсивного счетчика, отличающийся .тем, что, с целью расширения динамического диапазона измеряемых сигналов, повьпиения точности и сокращения времени измерения, в него введен умножитель частоты, а фазовращатель выполнен дискретным, фазочувствительный блок состоит из измерительного и опорного параметрических генераторов, модулятора, делителя частоты и двух фазовык различителей, причем входная клемма измеряемого .сигнала соединена со вторым входом фазочувствительного блока, при этом второй вход соединен с сигнальным входом измерительного параметрического генератора, прямой выход которого соединен с первыми входами первого и второго фазовых различителей, вторые входы которых соединены соответственно с прямым и инверсным выходами опорного параметрического генератора, а их выходы соединены с первой и второй выходными клеммами фазсУчувстви- , тельного блока, первый вход которого соединен непосредственно с входом иакачки опорного параметрического генератора и через модулятор с входом накачки измерительного параметрического генератора, третий вход фазочувствительного блока соединен через делитель частоты с входом управления Модулятора, причем выходы реверсивного счетчика соединены с соответствующими входами управления дискретного фазовращателя, а вход дискретного . фазовращателя и третий вход фазочувст вительного блока соединены через умножитель частоты со входнойклеммой опорного сигнала, при этом первый и второй входь блока отсчета результаО) тов измерения соединены соответствен но с первым и вторым выходами фазо:чувствительного блока. г.Фазометр .1, о т л,и ч а ю - g ,Щ и и с я тем, что.блок отсчета ре- j зультатов измерений содержит блок I управления и ц разрядных ячеек, каждая из которых включает первый и вто рой четырехразрядные полные сумматоры, регистр памяти, дешифратор, инди35 катор и инвертор, при этом разрядные выходы первого сумматора начиная с младшего разряда соединены с соответствующими первыми разрядными входами второго сумматора, вторые разрядные входы первого и третьего разрядов и вход переноса которого соединены между собой и соединены с общей шиной, а вторые разрядные входа второго и четвертого разрядов соединены между собой и соединены через инвертор с выходом переноса первого сумматора, разрядные выходы второго сумматора соединены с соответствующими разрядными входами регистра па-мяти, каждалй разрядный выход которого, начиная с младшего разряда, соединен с соответствующими соединенны

1

Изобретение- относится к радиотехнике и измерительной технике и может быть использовано для измерения разности фаз двух радиосигналов в разлн ных радиоэлектронных устройствах..

Известен фазометр, используемый для контроля и измерения фазового сдвига двух радиосигналов в радиоэлектронной аппаратуре и содержащий чувствительный элемент, счетчики, дискретный фазовращатель, делитель, частоты, блок коммутации, преобразователь, блок включения, блок анализа и индикатор Щ ,

Недостатком его является узкий динамический диапазон измеряемых сигналов, малая чувствительность и точность вследствие использования в чувствительном элемента усилителей я ограничителей.

Наиболее близким к предложенному по технической сущности является фазометр, состоящий из фазочувствительного блока и подключенных к нему последовательно соединенных фазовршаателя, цифроаналогового преобразователя и реверсивного счетчика, состояние которого,, пропорциональное измеренному фазовот сдвигу, отобрах ается в цифровой форме. Фазочувствительный блок содержит фазовый детектор, к одному входу которого подключен усилитель измеряемого сигнала, а к другому - компенсирующий фазовращатель и нуль-орган, к одному входу которого подключен выход фазового детектора, а к другому - генератор тактовых импульсов 2 ,

Недостатком этого устройства является узкий динамический диапазон измеряемых сигналов, низкая точность и большое время измерения,

Узкий динамический диапазон обусловлен применением усилителя в цепи измеряемого сигнала в фазочувствигел ном блоке. Наличие указанного усилк™ теля, имеющеТо конечную стабильность амплитудно-частотной и фазочастоткой

характеристики во времени и при дййствии дестабилизирующих факторов, а также наличие ифроаналоговрго преобразователя в цепи управления фазовращателя обусловливает низкую точность устройства.

Для изменения амплитуды измеряемых сигналов в ряде -случаев требуется использовать дополнительные аттенюаторы, или усилители, на подк.71ючение которых требуется дополнительное время. Кроме того, результаты измерения в известном устройстве отображаются в цифровой форме лишь в виде числа пропорционального измеренному .значению фазового сдвига и поэтому требуется дополнительное время на вычисление фазового сдвига в градусной мере,

Цель изобретения - расширение динамического диапазона измеряемых сигналов, повышение точности.и сокращение времени измерения.

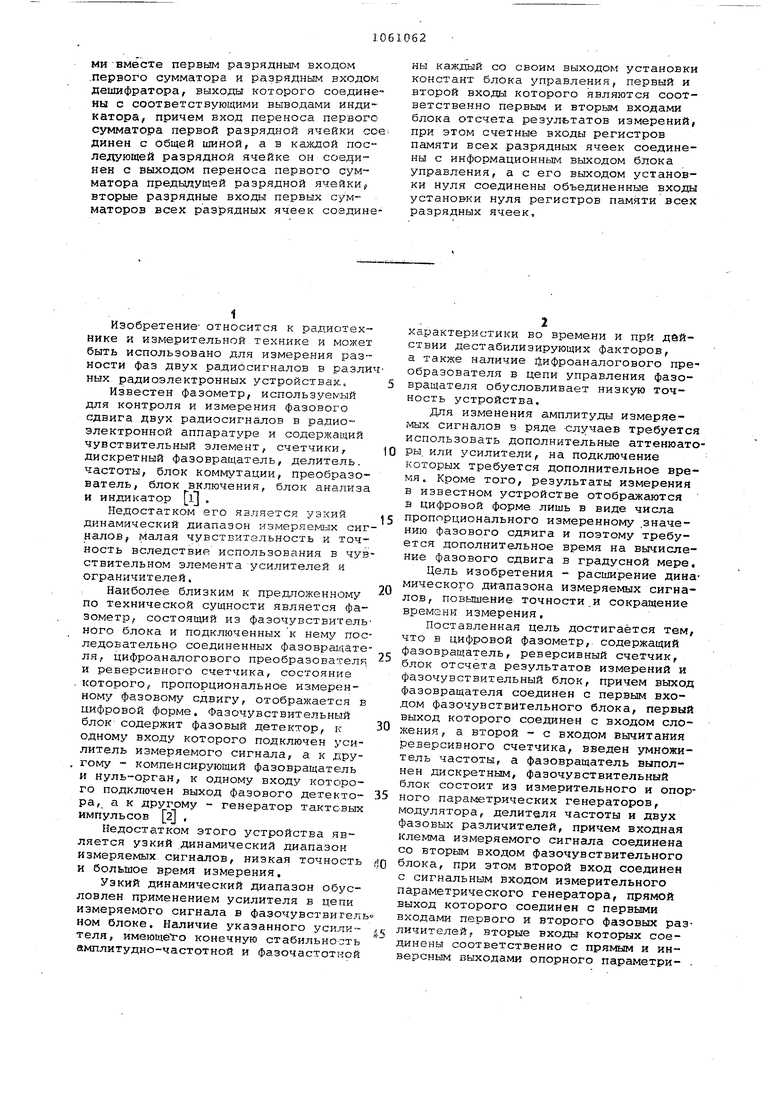

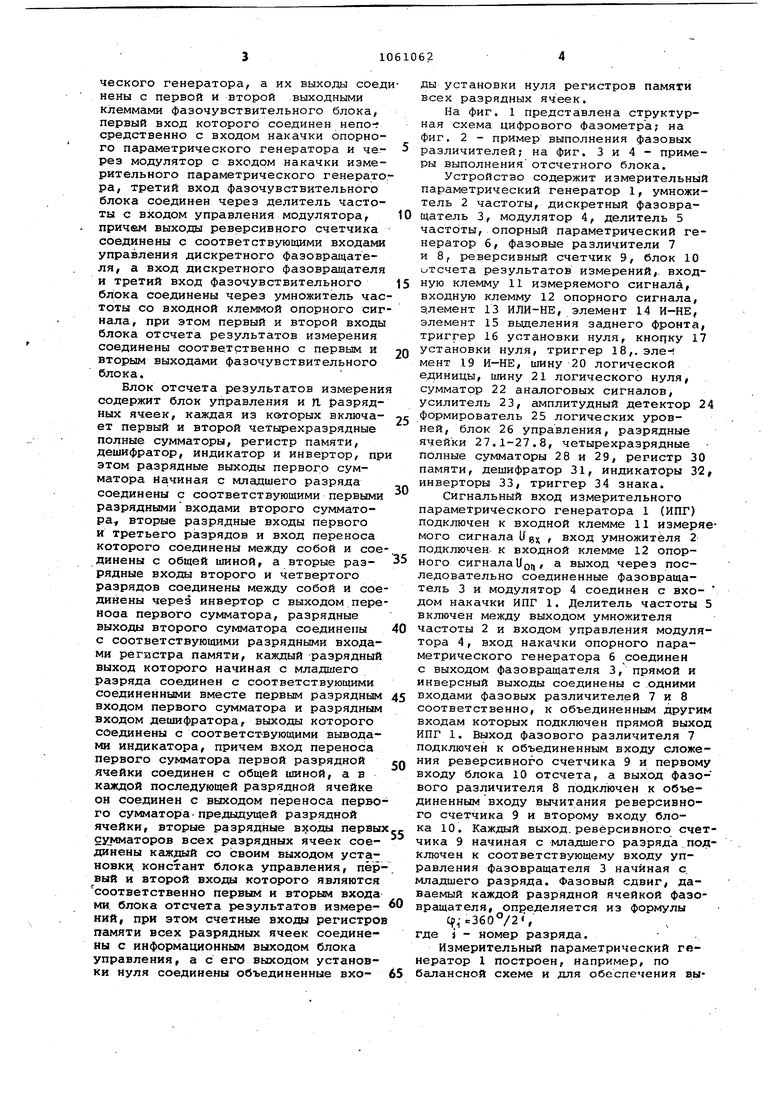

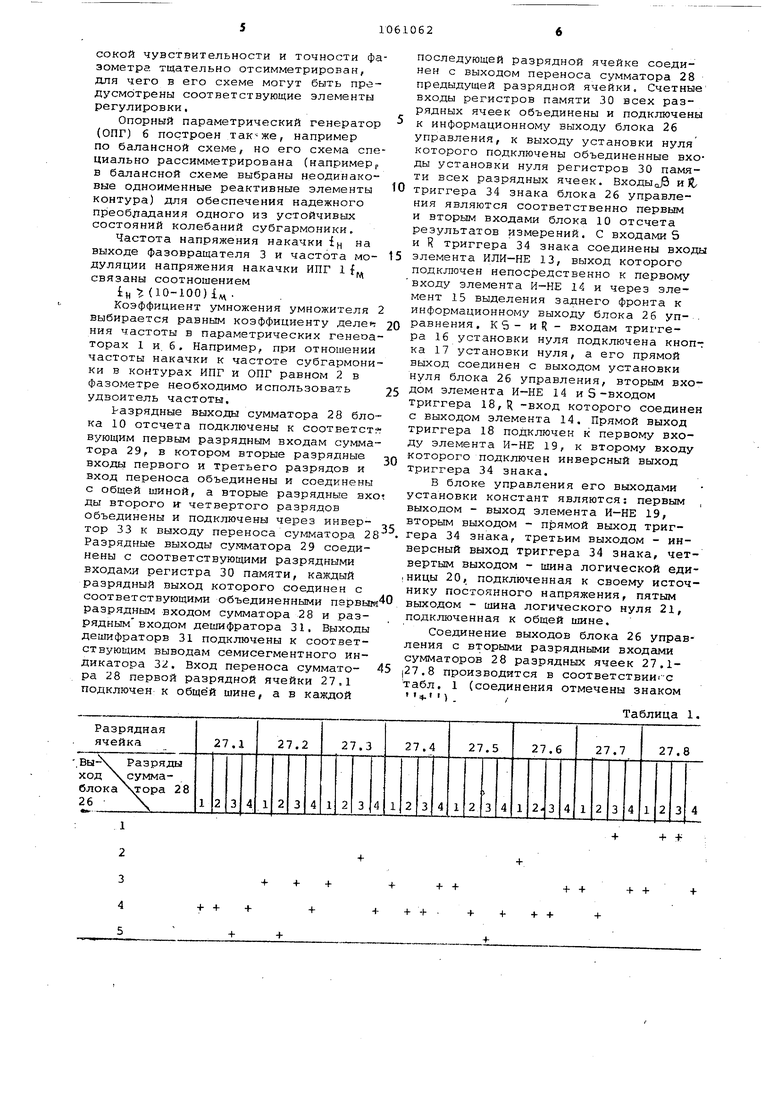

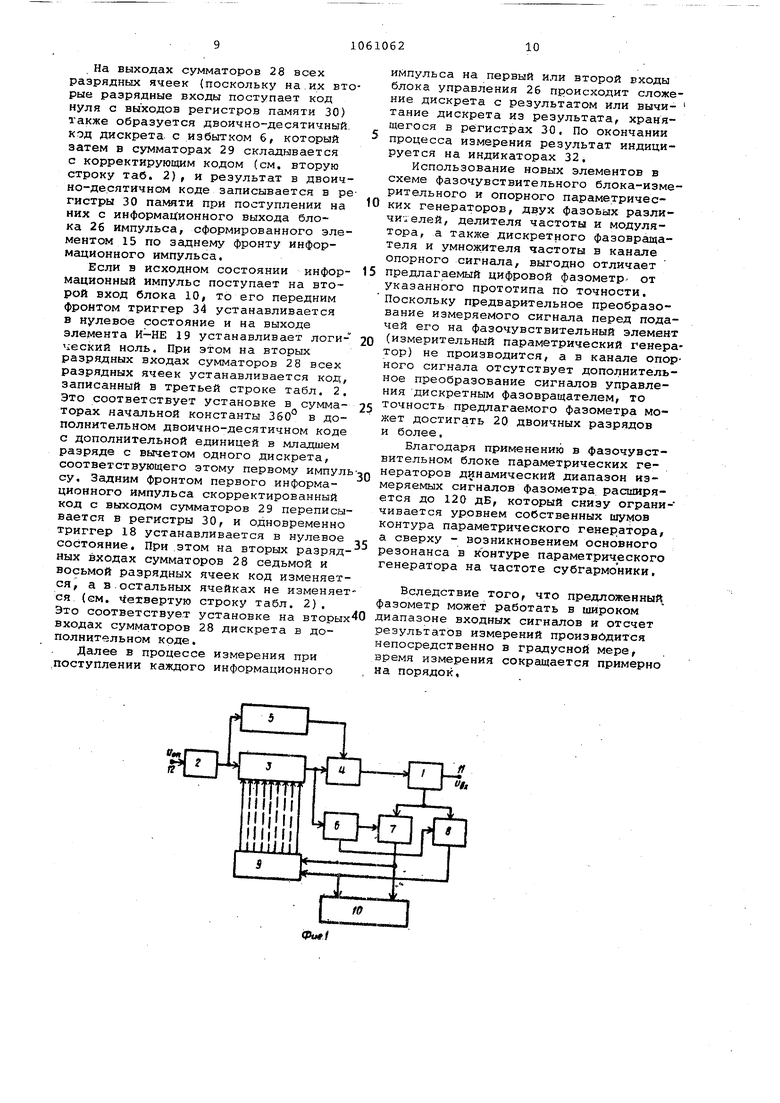

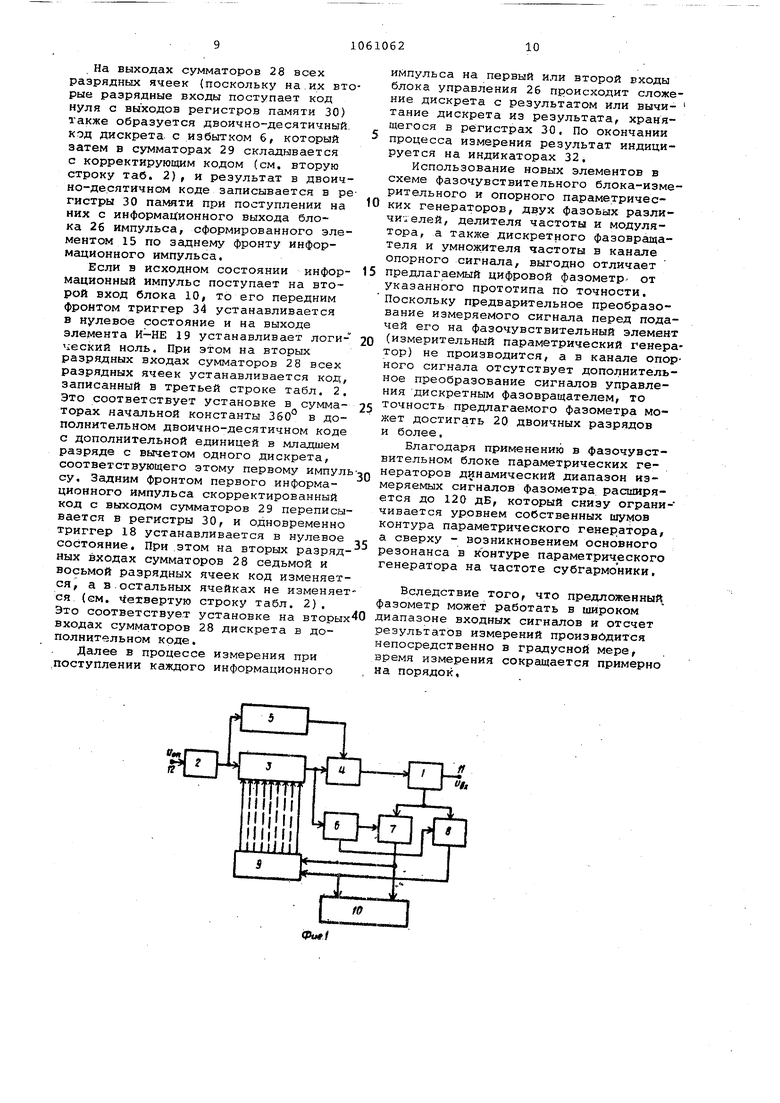

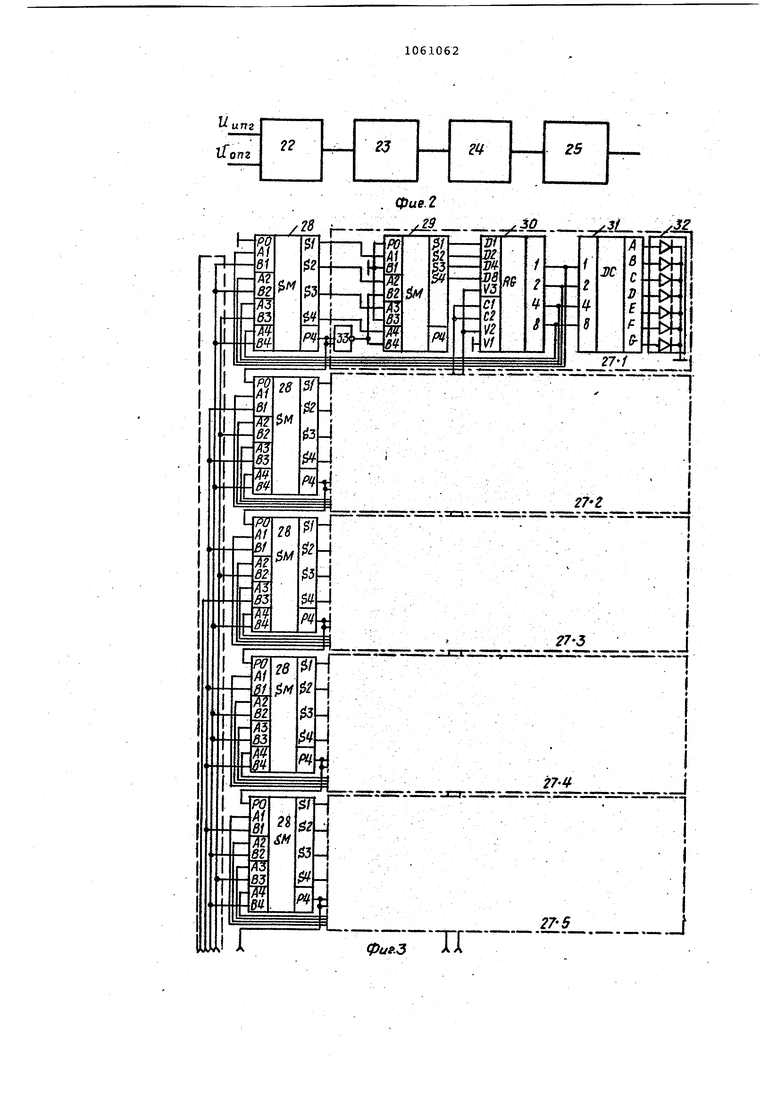

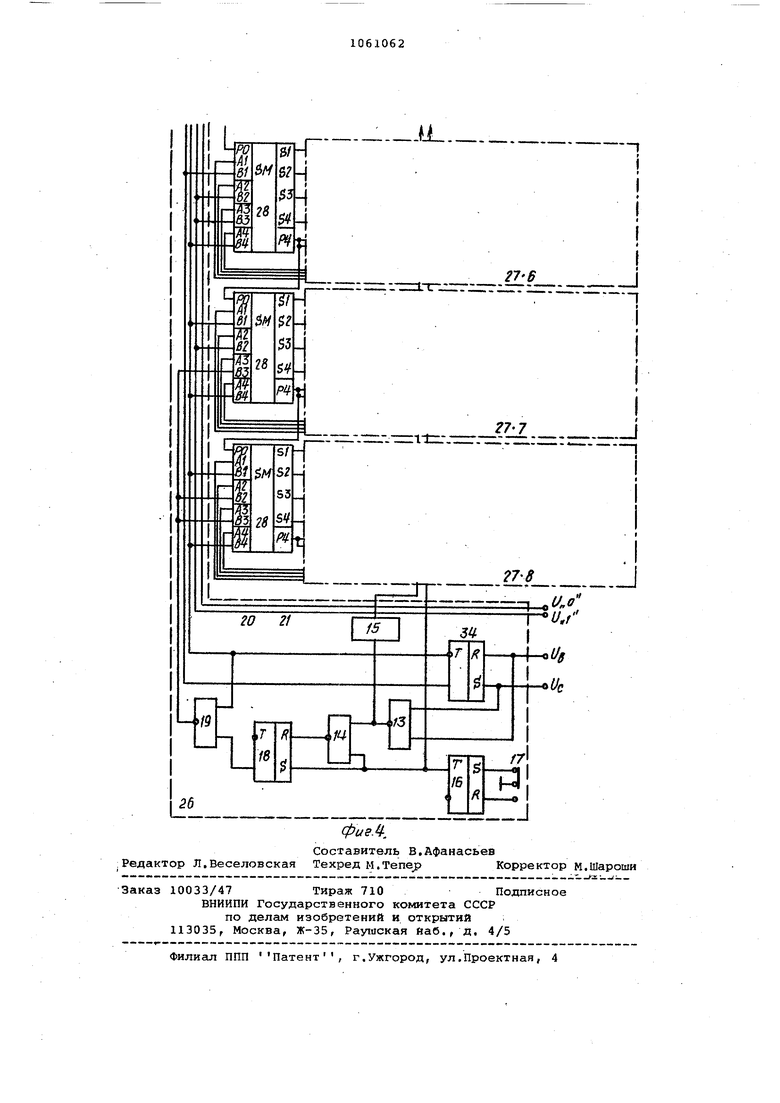

Поставленная цель достигается тем, что в цифровой фазометр, содержащий фазовращатель, реверсивный счетчик, блок отсчета результатов измерений и Фазочувствительный блок, причем выход фазовращателя сое.динен с первым входом фазочувствительного блока, первый выход которого соединен с входом сложения, а второй - с входом вычитания реверсивного счетчика, введен умножитель частоты, а фазовращатель выполнен дискретным, Фазочувствительный блок состоит из измерительного и опорного парагхгетрических генераторов, модулятора, делителя частоты и двух фазовых различителей, причем входная клемма измеряемого сигнала соединена со вторым входом фазочувствительного блока, при этом второй вход соединен с сигнальным входом измерительного параметрического генератора, прямой выход которого соединен с первыми входами первого и второго фазовых различителей, вторые входы которых соединены соответственно с прямым и инверсным выходами опорного параметрического генератора, а их выходы соед нены с первой и второй выходными клеммами фазочувствительного блока, первый вход которого соединен непог средственно с входом накачки опорного параметрического генератора и через модулятор с входом накачки измерительного параметрического генерато ра, третий вход фазочувствительного блока соединен через делитель частоты с входом управления модулятора, причем выходы реверсивного счетчика соединены с соответствующими входами управления дискретного фазовращателя, а вход дискретного фазовращателя и третий вход фазочувствительного блока соединены через умножитель час тоты со входной клеммой опорного сиг нала, при этом первый и второй входы блока отсчета результатов измерения соединены соответственно с первым и вторым выходами фазочувствительного блока. Блок отсчета результатов измерени содержит блок управления и л разрядных ячеек, каждая из которых включает первый и второй четырехразрядные полные сумматоры, регистр памяти, дешифратор, индикатор и инвертор, пр этом разрядные выходы первого сумматора Начиная с младшего разряда соединены с соответствующими первыми разряднымивходами второго сумматора вторые разрядные входы первого и третьего разрядов и вход переноса которого соединены между собой и сое динены с общей шиной, а вторые разрядные входы второго и четвертого разрядов соединены между собой и сое динены через инвертор с выходом пере носа первого сумматора, разрядные выходы второго сумматора соединены с соответствующими разрядными входами регистра памяти, каждый разрядный выход которого начиная с младшего разряда соединен с соответствующими соединенными вместе первым разрядным входом первого сумматора и разрядным входом дешифратора, выходы которого соединены с соответствующими выводами индикатора, причем вход переноса первого сумматора первой разрядной ячейки соединен с общей шиной, а в каждой последующей разрядной ячейке он соединен с выходом переноса перво го сумматора-предыдущей разрядной ячейки, вторые разрядные входы первы сумматоров всех разрядных ячеек соединены каждый со своим выходом установки констант блока управления, пёр вый и второй входы которого являются соответственно первым и вторым входа ми блока отсчета результатов измереНИИ, при этом счетные входы регистро памяти всех разрядных ячеек соединены с информационным выходом блока управления, а с его выходом установки нуля соединены объединенные входы установки нуля регистров памяти всех разрядных ячеек. На фиг. 1 представлена структурная схема цифрового фазометра; на фиг, 2 - пример выполнения фазовых различителей; на фиг. 3 и 4 - примеры выполнения отсчетного блока. Устройство содержит измерительный параметрический генератор 1, умножитель 2 частоты, дискретный фазовращатель 3, модулятор 4, делитель 5 частоты, опорный параметрический генератор 6, фазовые различители 7 и 8, реверсивный счетчик 9, блок 10 тсчета результатов измерений,, входную клемму 11 измеряемого сигнала, входную клемму 12 опорного сигнала, элемент 13 ИЛИ-НЕ, элемент 14 И-НЕ, элемент 15 вьщеления заднего фронта, триггер 16 установки нуля, кноцку 17 установки нуля, триггер 18,, элемент 19 И-НЕ, шину 20 логической единицы, шину 21 логического нуля, сумматор 22 аналоговых сигналов, усилитель 23, амплитудный детектор 24 формирователь 25 логических уровней, блок 26 управления, разрядные ячейки 27.1-27.8, четырехразрядные полные сумматоры 28 и 29, регистр 30 памяти, дешифратор 31, индикаторы 32, инверторы 33, триггер 34 знака. Сигнальный вход измерительного параметрического генератора 1 (ИПГ) подключен к входной клемме 11 измеряемого сигнала Uej , вход умножителя 2 подключен к входной клемме 12 опорного сигналаUQI,, а выход через последовательно соединенные фазовращатель 3 и модулятор 4 соединен с входом накачки ИПГ 1. Делитель частоты 5 включен между выходом умножителя частоты 2 и входом управления модулятора 4, вход накачки опорного параметрического генератора 6 соединен с выходом фазовращателя 3, прямой и инверсный выходы соединены с .одними входами фазовых различителей 7 и 8 соответственно, к объединенным другим входам которых подключен прямой вь1Ход ИПГ 1. Выход фазового различителя 7 подключен к объединенным входу сложения реверсивного счетчика 9 и первому входу блока 10 отсчета, а выход фазового различителя 8 подключен к объединенным входу вычитания реверсивного счетчика 9 и второму входу блока 10. Каждый выход, реверсивного счетчика 9 начиная с младшего разряда.подключен к соответствующему входу управления фазовращателя 3 начиная с, младшего разряда. Фазовый сдвиг, даваемый каждой разрядной ячейкой фазовргццателя, определяется из формулы q - 360°/2, где i - номер разряда. Измерительный параметрический генератор 1 построен, например, по балансной схеме и для обеспечения высокой чувствительности и точности фа зометра тщательно отсимметрирован, для чего в его схеме могут быть предусмотрены соответствующие элементы регулировки. Опорный параметрический генератор (ОПГ) б построен , например по балансной схеме, но его схема спе циально рассимметрирована (например,, в балансной схеме выбраны неодинаковые одноименные реактивные элементы контура) для обеспечения надежного преобладания одного из устойчивых состояний колебаний субгармоники. Частота напряжения накачки IH на выходе фазовращателя 3 и частота модуляции напряжения накачки ИПГ 1f связаны соотношением н г (10-100) i; . Коэффициент умножения умножителя выбирается равным коэффициенту ния частоты в параметрических генеоа торах 1 и, б. Например, при отношении частоты накачки к частоте субгармони ки в контурах ИПГ и ОПГ равном 2 в фазометре необходимо использовать удвоитель частоты, i-азрядные выходы сумматора 28 бло ка 10 отсчета подключены к соответст вующим первым разрядным входам сумма тора 29 f в котором вторые разрядные входы первого и третьего разрядов и вход переноса объединены и соединены с общей шиной, а вторые разрядные ax ды второго IT четвертого разрядов объединены и подключены через инвертор 33 к выходу переноса суг-лматора. 2 Разрядные выходы сумматора 29 соединены с соответствующими разрядными входами регистра 30 памяти, каждый разрядный выход которого соединен с соответствующими объединенными парвым разрядным входом сумматора 28 и разрядным входом дешифратора 31, Выходы дешифраторв 31 подключены к соответствующим выводам семисегментного индикатора 32, Вход переноса сумматора 28 первой разрядной ячейки 27,1 подключен к общей шине, а в каждой

+ + +

+ 4- + + + +

+ + +

+ +

+ + + + + + + + + + последующей разрядной ячейке соединен с выходом переноса сумматора 28 предыдущей разрядной ячейки. Счетные входы регистров памяти 30 всех разрядных ячеек объединены и подключены к информационному выходу блока 26 управления, к выходу установки нуля которого подключены объединенные входы установки нуля регистров 30 памяти всех разрядных ячеек. Входы В и ft триггера 34 знака блока 26 управления являются соответственно первым и вторым входами блока 10 отсчета результатов измерений, С входами 5 и R триггера 34 знака соединены входы элемента ИЛИ-НЕ 13, выход которого подключен непосредственно к первому входу элемента И-НЕ 14 и через элемент 15 выделения заднего фронта к информационному выходу блока 26 уп- . равнения, К 5 - и( - входам тригтера 16 установки нуля подключена кноп- ка 17 установки нуля, а его прямой выход соединен с выходом установки нуля блока 26 управления, вторым входом элемента И-НЕ 14 иS-входом триггера 18,R -вход которого соединен с выходом элемента 14, Прямой выход триггера 18 подключен к первому входу элемента И-НЕ 19, к второму входу которого подключен инверсный выход триггера 34 знака, В блоке управления его выходами установки констант являются: первым , выходом - выход элемента И-НЕ 19, вторым выходом - прямой выход триггера 34 знака, третьим выходом - инверсный выход триггера 34 знака, четвертым выходом - шина логической единицы 20, подключенная к своему источнику постоянного напряжения, пятым выходом - шина логического нуля 21, подключенная к общей шине, Соединение выходов блока 26 управ ления с вторыми разрядными входами сумматоров 28 разрядных ячеек 27.1|27,8 производится в соответствии-с табл. 1 (соединения отмечены знаком ). / Таблица 1. Устройство работает следующим образом. В исходном состоянии, когда на фа зометр не поданы входные сигналы, ре версивный счетчик 9 находится в нуле вом состоянии, предварительно устано Ленном, а дискретный фазовращатель 3 дает нулевой фазовый сдвиг. При подаче на входы фазометра опорного и измеряемого сигналов ОПГ 6 возбуждается в режиме непрерывных колебаний с заданной фазой, жестко привязанной к фазе опорного сигнала на выходе дискретного фазовращателя 3, а фаза суб армоники ИПГ 1 при поступлении на него с модулятора 4 каждого радио импульса накачки определяется фазой входного сигнала. На выходе фазового различителя 7 появляется видеоимпульс, который пос тупает на вход сложения реверсивного счетчика 9 и изменяет состояние его младшего разряда. При этом фаза напряжения накачки на выходе дискретно го фазовращателя 3 изменяется на величину одного дискрета ЛЧ 360°/2, где п - количество разрядов реверсив ного счетчика 9 (или дискретного фазовращателя). Напряжение накачки с измененной на л If фазой поступает на вход накачки ОПГ 6 и через модулятор в виде радиоимпульсов на вход накачки ИПГ Параметрические генераторы возбуждаются, но поскольку фаза напряжения накачки изменяется на- угол , то сепаратрисы ОПГ 6 и ИПГ 1 поворачиваются относительно вектора измеряемого сигнала (или своего исходного положения) на уголЛЦ /2. Если то ИПГ 1 опять возбуждается в фазе.с ОПГ 6 и на выходе фазового различителя 7 вновь появляется видеоимпульс, который поступает на вход сложения реверсивного счетчика 9 и вызывает изменение фазы накачки на выходе дискретного фазовращателя 3 еще на ДЦ) . Циклы изменения фазы диск ретного фазовращателя 3 повторяются до тех пор, пока сепаратрисы не повернутся относительно исходного положения на угол k---r- Q,, I2 В этом случае ИПГ 1 возбудится с фазой субгармоники противоположной фазе субгармоники ОПГ 6. Теперь виде

1011

1000

1010

1010 1011

1101

1101

1011

оно

оно

оно . 1010 0111

1010

1010

1010

1010

1010 1001 1011 1110 1011

1111

1110 - 1111

1111

1011

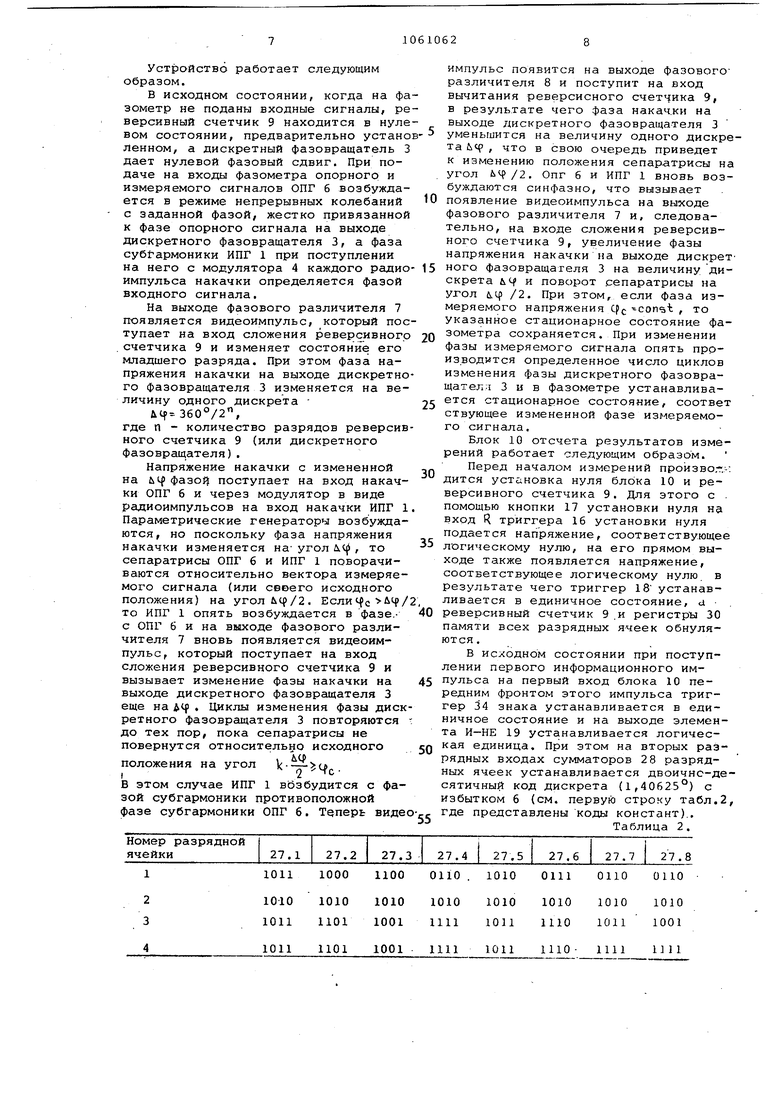

1001 1111 импульс появится на выходе фазового различителя 8 и поступит на вход вычитания реверсисного счетчика 9, в результате чего фаза накач.ки на выходе лискретного фазовращателя 3 уменьшится на величину одного дискрета frvcp , что в свою очередь приведет к изменению положения сепаратрисы на угол , Опг 6 и ИПГ 1 вновь возбуждаются синфазно, что вызывает появление видеоимпульса на выходе фазового различителя 7 и, следовательно, на входе сложения реверсивного счетчика 9, увеличение фазы напряжения накачки на выходе дискретного фазовращателя 3 на величину дискрета ьч и поворот сепаратрисы на угол й.ц) /2. При этом, если фаза измеряемого напряжения срс const , то указанное стационарное состояние фазометра сохраняется. При изменении фазы измеряемого сигнала опять производится определенное число циклов изменения фазы дискретного фазовращателп 3 и в фазометре устанавливается стационарное состояние, соответ ствующее измененной фазе измеряемого сигнала. Блок 10 отсчета результатов измерений работает следующим образом. Перед началом измерений произво-ч дится установка нуля блока 10 и реверсивного счетчика 9. Для этого с . помощью кнопки 17 установки нуля на вход R триггера 16 установки нуля подается напряжение, соответствующее логическому нулю, на его прямом выходе также появляется напряжение, соответствующее логическому нулю в результате чего триггер 18 устанавливается в единичное состояние, а . реверсивный счетчик 9.и регистры 30 памяти всех разрядных ячеек обнуляются. В исходном состоянии при поступлении первого информационного импульса на первый вход блока 10 передним фронтом этого импульса триггер 34 знака устанавливается в единичное состояние и на выходе элемента И-НЕ 19 устанавливается логическая единица. При этом на вторых разрядных входах сумматоров 28 разрядных ячеек устанавливается двоично-десятичный код дискрета (1,40625°) с избытком 6 (см. первую строку табл.2, где представлены коды констант).. Таблица 2. На выходах сумматоров 28 всех разрядных ячеек {поскольку на их вто рые разрядные входы поступает код нуля с выходов регистров памяти 30) также образуется двоично-десятичный. код дискрета с избытком 6, который затем в сумматорах 29 складывается с корректирующим кодом (см, вторую строку таб. 2), и результат в двоично-десятичном коде записывается в ре гистры 30 памяти при поступлении на них с информационного выхода блока 26 импульса, сформированного элементом 15 по заднему фронту информационного импульса. Если в исходном состоянии информационный импульс поступает на второй вход блока 10, то его передним фронтом триггер 34 устанавливается в нулевое состояние и на выходе элемента И-НЕ 19 устанавливает логи- ческий ноль. При этом на вторых разрядных входах сумматоров 28 всех разрядных ячеек устанавливается код, записанный в третьей строке табл, 2, Это соответствует установке в сумматорах начальной константы 360° в дополнительном двоично-десятичном коде с дополнительной единицей в младшем разряде с вычетом одного дискрета, соответствующего этому первому импул су. Задним фронтом первого информационного импульса скорректированный код с выходом сумматоров 29 переписы вается в регистры 30, и одновременно триггер 18 устанавливается в нулевое состояние. При этом на вторых разряд ных входах сумматоров 28 седьмой и восьмой разрядных ячеек код изменяет ся, а в.остальных ячейках не изменяе ся (см, «гетвертую строку табл, 2) , Это соответствует установке на вторы входах сумматоров 28 дискрета в дополнительном коде, Далее в процессе измерения при .поступлении каждого информационного импульса на первый или второй входы блока управления 26 происходит сложение дискрета с результатом или вычитание дискрета из результата, хранящегося в регистрах 30, По окончании процесса измерения результат индицируется на индикаторах 32, Использование новых элементов в схеме фазочувствитепьного блока-измерительного и опорного параметрических генераторов, двух фазовых различи- елей, делителя частоты и модулятора, а также дискретного фазовращателя и умножителя частоты в канале опорного сигнала, выгодно отличает предлагаемый цифровой фазометр от указанного прототипа по точности, Поскольку предварительное преобразование измеряемого сигнала перед подачей его на фазочувствительный элемент (измерительный параметрический генератор) не производится, а в канале опорного сигнала отсутствует дополнительное преобразование сигналов управления дискретным фазовращателем, то точность предлагаемого фазометра может достигать 20 двоичных разрядов и более. Благодаря применении) в фазочувствительном блоке параметрических генераторов динамический диапазон измеряемых сигналов фазометра расширяется до 120 дБ, который снизу ограничивается уровнем собственных myiyiOB контура параметрического генератора, а сверху - возникновением основного резонанса в контуре параметрического генератора на частоте субгармоники, Вследствие того, что предложенный фазометр может работать в широком диапазоне входных сигналов и отсчет результатов измерений производится непосредственно в градусной мере, время измерения сокращается примерно на порядок.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Адаптивный фазометр | 1974 |

|

SU499539A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для измерения сдвига фаз | 1973 |

|

SU464857A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-12-15—Публикация

1982-01-15—Подача