рой группы соединен с вторым входом соответствующего элемента И-НЕ, выходы каждых 32 элементов И-НЕ соединены с 32 входами соответствующего элемента И первой группы, выход которого соединен с установочным входом соответствующего счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования пачекиМпульСОВ | 1979 |

|

SU828384A1 |

| Грозопеленгатор-дальномер | 1984 |

|

SU1187120A1 |

| Устройство для контроля знаний обучаемых | 1990 |

|

SU1758658A1 |

| ПАССИВНАЯ СИСТЕМА ОПРЕДЕЛЕНИЯ КООРДИНАТ ИСТОЧНИКОВ ИЗЛУЧЕНИЯ | 1989 |

|

SU1841037A1 |

| Самонастраивающееся устройство управления | 1983 |

|

SU1130830A1 |

| Устройство для контроля радиоэлектронной аппаратуры | 1984 |

|

SU1182541A1 |

| СИСТЕМА СИНХРОНИЗАЦИИ ЧАСОВ ПО РАДИОКАНАЛУ | 1985 |

|

SU1840365A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ОШИБОК | 1998 |

|

RU2127943C1 |

| Устройство для контроля логических узлов | 1980 |

|

SU991430A1 |

УСТРОЙСТВО ИНДИКАЦИИ ПЕЛЕНГА, содержащее три ключа, первый источник постоянного опорного напряжения, выход которого соединен с входом третьего ключа, последовательно соединенные сумматор, фильтр, усилитель-ограничитель, первый элемент И, второй элемент И, одновибратор, элемент ИЛИ, декадный счетчик и регистр сдвига, последовательно соединенные генератор импульсов, счетЧик и дешифратор, а также делитель , третий элемент И и N индикаторов, причем выход генератора импульсов соединен с вторым входом первого элемента И и с входом делителя частоты, прямой выход которого соединен с управляющими входами первого и третьего ключей и третьим входом первого элемента И, а инверсный выход - с управляющим входом второго ключа, выходы первого, второго и третьего ключей соединены с входами сумматора, выход первого элемента И соединен через третий элемент И с вторым входом первого элемента ИЛИ, первый, второй, третий и четвертый выходы дешифратора соединены соответственно с вторым входом второго элемента И, вторым входом третьего элемента И, третьим входом первого элемента ИЛИ и управляющим входом записи регистра сдвига, при этом входы первого и второго ключей являются входами ортогональных составляющих пеленга цели устройства индикации пеленга, отличающееся тем, что, с целью повышения быстродействия, введены второй источник постоянного опорного напряжения, два компаратора, второй элемент ИЛИ, N. элементов памяти первой группы, N элементов памяти второй группы, N дешифраторов первой группы, N дешифраторов второй группы, 32 N элементов И-НЁ, N элементов И первой группы, N счетчиков, N триггеров, N элементов ИЛИ, N элементов И второй группы и N дешифраторов третьей группы, причем каждый i-й из N выходов регистра сдвига соединен с входами i-x элементов памяти первой и второй групп и первым входом i-ro элемента И Bi-орой группы, входы первого и второго ключей соединены с управляющими входами первого и второго компараторов, опорные в.ходы которых подключены к выходу второго источника постоянноi го напряжения, а входы стробирования соединены с восьмым выходом дешифратора, (Л причем выходы компараторов подключены соответственно к первому и второму входам второго элемента ИЛИ, выход которого соединен через N элементов ИЛИ с вторыми входами N элементов И второй группы, каждый из которых соединен через соответствующий дешифратор третьей группы с входом соответствующего индикатора, пятый выход дешифратора соединен с управляющими вхоО5 дами N элементов памяти второй группы и сд входами N счетчиков, выходы которых соединены через N триггеров с вторыми входаСП ми N элементов ИЛИ соответственно, шессд той выход дешифратора соединен с управляющими входами N элементов памяти первой группы, седьмой выход дешифратора соединен с установочными входами.N триггеров, каждый i-й и,з N элементов памяти первой группы соединен с входом i-ro дешифратора первой группы, а каждый 1-й из N элементов памяти второй группы соединен с входом i-ro дешифратора второй группы, каждый из 32 выходов дешифратора первой группы соединен с первым входом соответствующего элемента И-НЕ, а каждый из 32 выходов каждого дешифратора вто

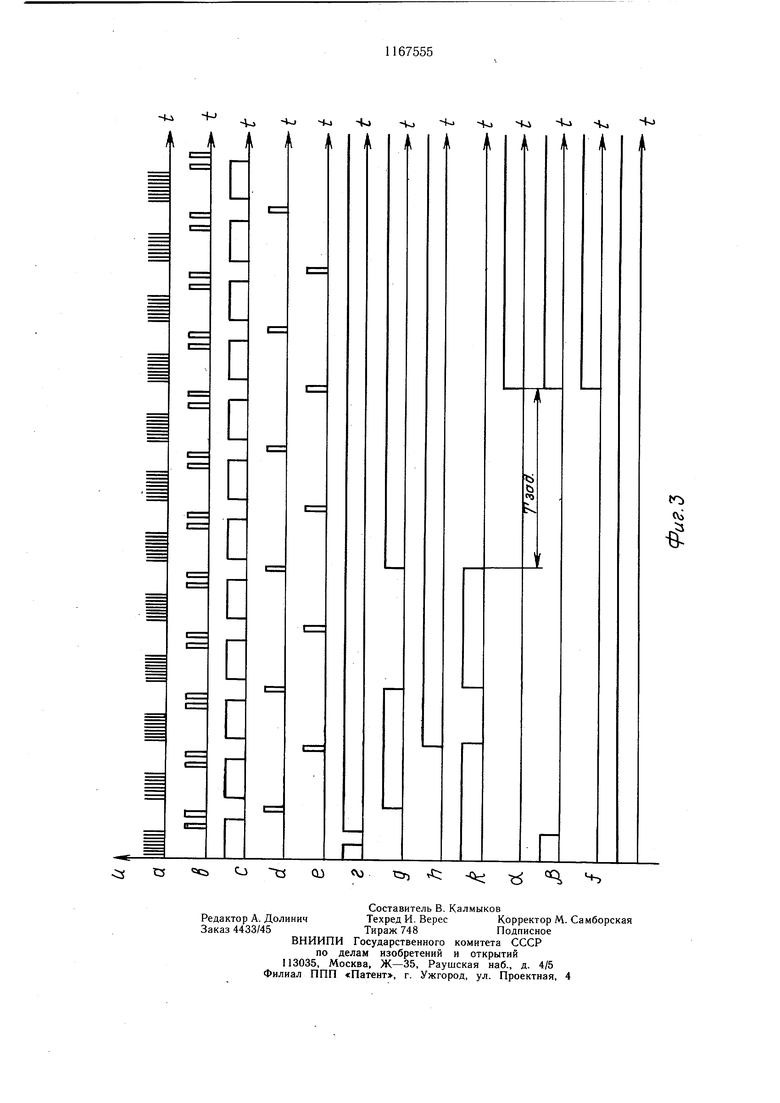

Изобретение относится к радиотехнике и может использоваться в индикаторах, индицирующих измеряемую величину, значение которой относительно истинного значения по закону нормального распределения с нулевым средним. Цель изобретения - повышение быстродействия. На фиг. 1 представлена структурная электрическая схема предложенного устройства; на фиг. 2, 3 - временные диаграммы, поясняющие его работу. Устройство содержит первый источник 1 постоянного опорного напряжения, три ключа 2, 3 и 4, сумматор 5, фильтр 6, усилитель-ограничитель 7, первый элемент И 8, второй элемент И 9, одновибратор 10, элемент ИЛИ 11, декадный счетчик 12, регистр 13 сдвига, генератор 14 импульсов, счетчик 15, дещифратор 16, делитель 17 частоты, третий элемент И 18, второй источник 19 постоянного опорного напряжения, компаратор 20, N элементов памяти 21 первой группы, N элементов памяти 22 второй группы, N дешифраторов 23 первой группы, N дешифраторов 24 второй группы, 32 N элементов И-НЕ 25, N элементов И 26, N счетчиков 27, N триггеров 28, N элементов ИЛИ 29, N элементов И 30 второй группы, N дешифраторов 31 третьей группы и N индикаторов 32, второй компаратор 33 и второй элемент ИЛИ 34. Устройство работает следующим образом. Входные напряжения Ux и Uy, пропорциональные синусу и косинусу пеленга (фиг. 2 а, б), поступают на входы ключей 2 и 3. Ключи 2 и 3 управляются напряжениями прямоугольной формы с фазой 0° (фиг. 2в) и 90° (фиг. 2г) соответственно. При этом на выходе ключей 2 и 3 формируются напряжения прямоугольной формы с амплитудами Ux и Uy и фазами 0° и 90 соответственно. Эти напряжения поступают на входы сумматора 5. После суммирования этих напряжений сумматором на выходе последнего формируется ступенчатое напряжение с фазой первой гармоники (фиг. 2д, е). Напряжение первой гармоники суммарного напряжения выделяется фильтром 6 и поступает на вход усилителя-ограничителя 7, с выхода которого поступает на вход формирователя фронтов (не показан), в результате чего оно преобразуется в напряжение прямоугольной формы (фиг. 2ж). Это напряжение поступает на первый вход элемента И 8, на второй вход которого поступает опорное напряжение 0°, на третий вход поступают с генератора 14 счетные импульсы, в результате чего на выходе элемента И 8 формируется пачка импульсов, соответствующая углу пеленгования (фиг. 2з). В качестве делителя 17, служащего для формирования опорных напряжений с фазой 0°, 45°, 90°, 180°, могут быть применены счетчики. Пачка импульсов поступает на коммутатор, предназначенный для управления устройством. По своей структуре он представляет собой распределитель импульсов, состоящий из генератора 14, счетчика 15, дещифратора 16, элементов И 9, 18 и элемента ИЛИ 11. Коммутатор коммутирует пачку импульсов либо на вход декадного счетчика 12, либо на вход одновибратора 10, предназначенного для деления пачки импульсов на два. После первых двух считываний информации в декадном счетчике 12 записывается информация (Qi -Ь -%) - которая переписывается в регистр ГЗ сдвига и сдвигается в сторону младших разрядов на разряд, что соответствует делению на два. Тогда Q, , где Q - действительные значения пеленга. Следующая пачка импульсов поступает в декадный счетчик 12 через одновибратор 10. Б результате все последующие отсчеты можно представить в виде Q;,P 9pPL + J9y + ,..., + om-K где Q - Ке значение Qycp. Однако это не единственный способ реализации данного устройства, в более общем виде устройство цифровой обработки осуществляет усреднение в виде

Qycp }

где п - 00

Элементы И 30 непосредственно управляет прохождением отсчетов пеленга на цифровое табло.

Причем каждый бит информации поступает на один вход элемента И 30, а на второй вход поступает управляющий потенциал устройства выделения смены состояний. Управляющие сигналы формируются им поразрядно.

Устройство выделения смены состояний предназначено для обнаружения флюктуации значений пеленга в устройстве цифровой обработки и включает в себя две группы N элементов памяти 21 и 22, предназначенные для поочередной записи с регистра 13 сдвига текущего значения пеленга и пред ставляющие собой набор регистров, обеспечивающих запись всех разрядов информации включающие по 4 бита каждый. Выходы в элементах памяти 21 и 22, соответствующие данному разряду, подключены ко входам дещифраторов 23 и 24 данного разряда и данной группы дещифраторов.

Дещифраторы 23 и 24 совместно с элементами И-НЕ 25 предназначены для сопоставления пеленгов, записанных в первую и вторую группу регистров.

Если информация, записанная в первый и второй регистр, по данному разряду совпадает, на один из элементов И-НЕ 25 данного разряда на оба входа поступают уровни логической «1, на выходе его формируется уровень логической «О, который поступает на один из входов элементов И 2&, предназначенных для управления режимом работы счетчиков. Причем, если на один из входов элементов И 26 поступает уровень логической «О, свидетельствующий о совпадении информации, записанной в элементах памяти 21 и 23 по данному разряду, на выходе их формируется уровень логического «О разрещающий счет.,

Счетчики 27 формируют задержку момента совпадения информации, записанной в регистры, на несколько периодов для исключения случайного совпадения ее до момента заверщения усреднения. Счетные импульсы на счетчики 27 поступают с коммутатора.

Триггеры 28 предназначены для запоминания момента совпадения информации.

Элементы ИЛИ 29 предназначены для формирования управляющих сигналов, разрещающих индикацию на цифровом табло либо с момента совпадения информации в данном разряде в элементах памяти 21 и 22 (что свидетельствует о том, что за промежуток времени между перезаписью с регистра 13 смены ее не произощло, а значение измеряемой величины установилось постоянно и не меняется в течение всего времени задержки формируемого счетчиками 27), либо по окончании сигнала в том случае, когда сигнпл на входе кратковременен, и усреднения не произошло. В этом случае индицируется значение, полученное в результате усреднения за промежуток времени присутствия сигнала. Управляет этим режимом компаратор 20, на один из входов которого поступает опорное напряжение, на другой вход UBX. Третий стробирующий вход подключен к выходу коммутатора для исключения вывода ложной информации до поступления UBX.

На фиг. 3 приведена временная диаграмма работы цифрового индикатора пеленга.

Пачка импульсов (фиг. За) поступает на вход декадного счетчика 12.

Полученный на счетчике код переписывается первым импульсом записи (фиг. За) в регистр 13 сдвига.

После смены сигнала на управляющем входе регистра 13 (фиг. 3с), после режима «Запись - параллельно устанавливается режим «Сдвиг.

Поступающий с коммутатора второй импульс (фиг. Зв) сдвигает информацию на один разряд, что соответствует делению на два.

Это значение устанавливается на входах первой и второй группы элементов памяти 21 и 22 устройства выделения смены состояний, и на первых входах элементов И 30.

Импульс, поступающий на вход синхронизации первой группы, переписывает полученное значение (фиг. 3d).

Последующие пачки импульсов поступают на вход декадного 12 счетчика через одновибратор 10, в результате чего в регистре 13 накапливается усредненное значение пеленга, которое импульсом записи (фиг. Зе) переписывается во вторую группу элементов памяти 22, после чего оба значения пеленга сравниваются поразрядно дещифраторами 23 и 24.

В случае совпадения кодов, совпадает и выходной уровень логической единицы на выходах дешифраторов 23 и 24. Диаграмма на фиг. 3 g и fi соответствует появлению уровней логической «1 на обоих входах элементов И-НЕ 25. Таким образом, на выходе элементов И 26 формируется уровень логического «О (фиг. 3R). В случае несовпадения уровней логических «1 на входах элементов И-НЕ 25 данного разряда, на выходе соответствующего элемента И-26 формируется уровень логической «1. В этом случае импульсы, поступающие на счетные входы счетчиков 27 (фиг. Зе), не считаются. В случае же совпадения информации записанной в регистры данного разряда, после каждого совпадения информации на вход счетчика 27 данного разряда поступает импульс. В результате счетчиком формируется задержка Тзад, после которой на вход триггера 28 данного разряда поступает управляющий период напряжения (фиг. 3л).

До начала работы на второй вход триггера 28 поступил импульс установки (фиг. Зг). В результате на выходе триггера устанавливается уровень логической единицы (фиг. 3.) который поступает на вход элемента ИЛИ 29 данного разряда и на управляющем входем элемента И данного разряда формируЦифра So и

фиг. 2

ется уровень логической «1, а информация,

записанная в регистре 1 сдвига по данному

разряду, индицируется на табло (фиг. 3f).

В случае если усреднение не произощло

до окончания сигнала, по окончании его компаратор 20 формирует на своем выходе уровень логической «1, поступающий на вторые входы элементов ИЛИ 29, в результате чего информация по всем разрядам через элементы И 30 выводится на цифровые

индикаторы 32. индикатор пяленга

| Цифровое индикаторное устройство | 1980 |

|

SU892310A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Труды Государственного научно-,исследовательского института гражд,анской авиации, вып | |||

| Способ получения камфоры | 1921 |

|

SU119A1 |

| Способ сопряжения брусьев в срубах | 1921 |

|

SU33A1 |

Авторы

Даты

1985-07-15—Публикация

1983-07-22—Подача