фазовращателей 1 и 2, третьего, четвертого, пятого, шестого и седьмого эапоминаюищх блоков 1 Гз - 19, 21, вычислителя 20 пазности фаз, второго вычитающего блока 22, второго блока II управл.ения, переключателя 15 режима работы и индикатора 23. Устройство содержит также два к.гпоча 3 и 4, первый блок 5 управления, сумматор 6,. детектор 7, коммутатор 8, первый вы

5808

читающий блок 12, первый и второй запоминающие блоки 9 и 10, блок 13 преобразования, измеритель 14 отно- 1чения. Используя периодическую вось- митактовую и пятитактовую коммутацию, формируют требуемый комплекс информации для точного измерения разности фаз сигналов в расширеннЬм диапазоне. 2 с.п. и 1 з.п. ф-лы, 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель полных сопротивлений | 1989 |

|

SU1693565A1 |

| Адаптивная оптическая система апертурного зондирования | 1990 |

|

SU1793219A1 |

| Квазикогерентный демодулятор фазоманипулированных сигналов | 1990 |

|

SU1758898A1 |

| Индикаторное устройство | 1991 |

|

SU1809307A1 |

| АНАЛИЗАТОР ХАРАКТЕРИСТИЧЕСКОЙ ФУНКЦИИ СИГНАЛА | 2002 |

|

RU2231798C2 |

| Двухканальный фазометр | 1989 |

|

SU1718140A2 |

| Способ обнаружения и высокоточного определения параметров морских ледовых полей и радиолокационная система для его реализации | 2019 |

|

RU2710030C1 |

| Цифровой измеритель мощности | 1982 |

|

SU1092422A2 |

| Устройство селекции движущихся целей для радиолокатора с вобуляцией периода повторения | 1984 |

|

SU1841287A1 |

| Вихретоковый структуроскоп | 1985 |

|

SU1307323A1 |

Изобретение может быть использовано в радиоизмерительной технике преимущественно в миллиметровом диапазоне волн. Целью изобретения является расширение диапазона однозначного измерения разности фаз и повышение точности. Цель достигается тем, что в дополнительные такты коммутации вводят приращение фазовых сдвигов в опорный и измерительный ка. налы, определяют значения косинусов собственной разности фаз измерителя, суммы собственной разности Фаз измерителя и измеряемой разности фаз, приращения по опорному каналу разности фаз, cyMvoJ собственной разности фаз измерителя и приращения по опорному каналу разности фаз, суммы собственной разности фаз измерителя и прира1чения по опорному и измерительному каналам, суммы собственной разности фаз измерителя и приращения по измерительному каналу разности фаз, вычисляют по полученным значениям косинусов значения синуса и косинуса приращения разности фаз по опорному каналу, вычисляют собствен - ную разность фаз измерителя и сумму собственной разности фаз и измеряемой разности фаз, а разность фаз определяют как разность суммы соб- ственной разности фаз измерителя и ; измеряемой разности фаз и собственной разности фаз измерителя. Также периодически коммутируют сигналы опорного и измерительного каналов, детектируют их и их сумму, определяют значения косинуса разности фаз входных СВЧ-сигналов, определяют значения косинуса суммы собственной разности фаз измерителя и измеряемой разности фаз. В устройстве цель достигается введением двух управляемых сл D1 03

1

Изобретение относится к радиоизмерительной технике и может быть ис- пользовано для измерения разности фаз СВЧ-сигналов преимущественно в миллиметровом диапазоне волн.

Цель изобретения - расширение диапазона однозначного измерения разности фаз и повьтение точности в миллиметровом диапазоне волн.

На фиг.) представлена схема устройства для осуществления способа; на фиг.2 - структурная схема вычислителя разности фаз.

Устройство содержит первый 1 и второй 2 управляемые фазовращатели, первый 3 и второй 4 ключи, первый блок 5 управления, сумматор 6, детектор 7, коммутатор 8, первый 9 и второй 10 запоминающие блоки, второй блок 11 управления, первый вычитающий блок 12, блок 13 преобразования функции, измеритель 14 отношения, переключатель 15 режима работы, третий 16, четвертый 17, пятый 18, 1честой 19 запоминающие блоки, вычислитель 20 разности фаз, седьмой запоминающий блок 21, второй вычитающий блок 22,и индикатор 23.

Вьтислитель 20 разности фаз состоит из первого 24 и второго 25 блоков преобразования арккосинуса, третьего вычитающего блока 26, фор- мирователя 27 напряжения, блока 2 вычисления синуса, блока 29 вычисления косинуса, второго сумматора 30, первого 31 и второй 32 перемножителей, блока 33 деления, четвертого вычитающего блока 34 и блока 35 преобразования арктангенса.. Выходы уп- равляем1,1х фазовращателей 1 и 2 сое

5

0

5

0

5

40

диненыс входами ключей 3 и 4, выходы которых подключены к соответ- ствующим входам сумматора 6, выход которого через детектор 7 соединен с коммутатором 8. Первый, второй и третий выходы коммутатора 8 соединены с информационными входами запоми-. нающих блоков 9 и Ю и входом вычитающего блока 12. Выходы запоминающих блоков 9 и 10 подключены к входам блока 13 функционального преобразования, а также к входам вычитающего блока 12.. Выходы вычитающего блока 12 и блока 13 преобразования ф-ункции связаны с входами измерителя 14 отнотения, выход которого соединен с информационными входами запоминающих блоков 16 - 19. Выходные сигналы запоминающих блоков 16 - 19 поступают на соответствующие входы вычислителя 20 разности фаз, выход которого соединен с запоминающим блоком 21 и с одним из входов вычитающего блока 22, второй вход которого.подключен к выходу запоминающего блока 21. Выход вычитающего блока 22 сое-- динен с входом индикатора 23. Вьпсоды блока 5 управления связаны с управляющими входами ключей 3 и 4, коммутатора В и запоминающих блоков 9 и 10. Выходы блока 11 управления соединены с управляющими входами фазовращателей 1 и 2, запоминающих блоков 16 и 17 непосредственно и запоминающих блоков 18,19 и 21 через переключатель 15 режима работы. Синхронизирующий выход блока 11 управления подключен к входу блока 5 управления, Вьгходы блоков 24 и 25 преобразования арккосинуса соединены с вы314

читающим блоком 26. Выход вычитающего блока 26 связан с входами блока 28 вычисления синуса и блока 29 вычисления косинуса. Формирователь 27 напряжения своим выходом подсоединен к одному из входов сумматора 30, другой вход которого подключен к выходу запоминающего блока 16. Входы перемножителя 31 соответственно сое- динены с выходом сумматора 30 и выходом блока 28, а входы перемножителя 32 - с въгходами блоков 29 и 16. Пе- ремнохители 31 и 32 осуществляют перемножение входных сигналов. Выход перемножителя 32 соединен с одним из входов вычитающего блока 34, другой вход которого подключен к запоминающему блоку 17. Выход вычитающего блока 34 соединен с одним из входов блока 33 деления, другой вход которого связан с выходом перемножителя 31,Выходной сигнал блока 33 деления поступает на вход блока 35 преобразования арктангенса.

Способ измерения разности фаз ос уществляется следующим образом.

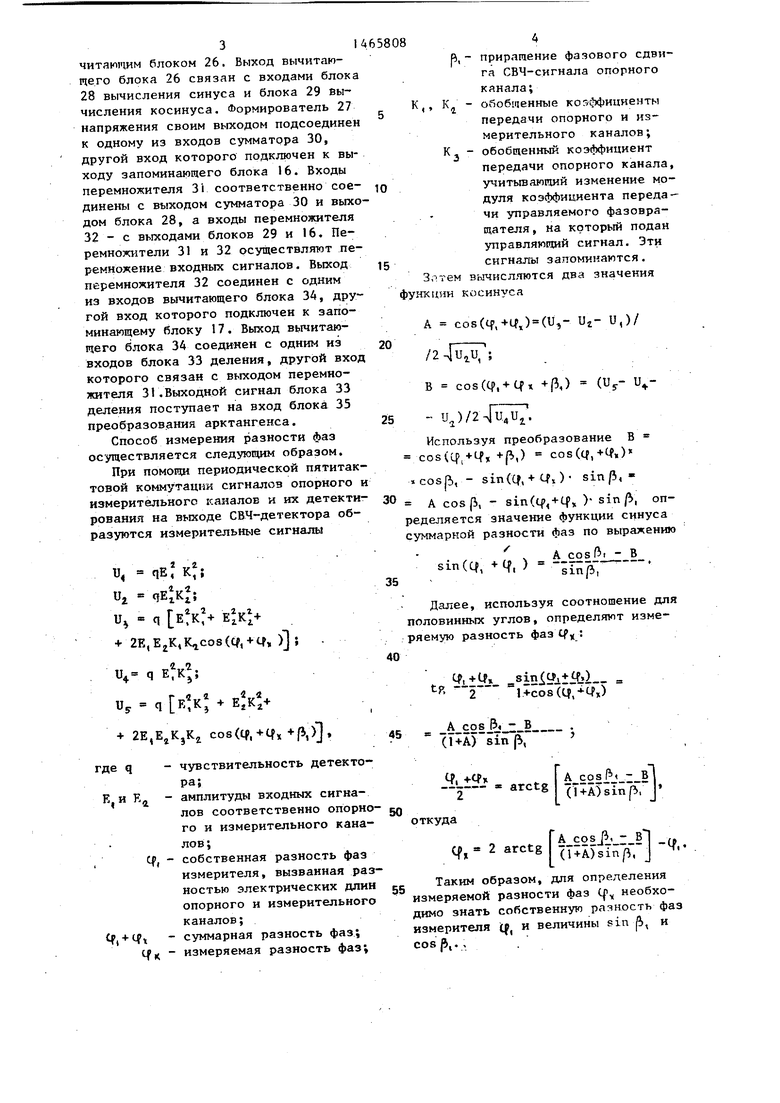

При помощи периодической пятитак- товой коммутации сигналов опорного и измерительного каналов и их детекти- рования на въкоде СВЧ-детектора образуются измерительные сигналы

i

«2

и.

qE J

- + ElKl

, , 2E,E2K,(tf,+Cf, );

и.

2 Ч q Е.к;;

- + Уг

45

де q

Е,иЕ

U.,

+ 2E,EjK,K2, cos(Cf,+Cf, +р,).

-чувствительность детектора;

-амплитуды входных сигналов соответственно опорно- gg го и измерительного каналов;

qi, - собственная разность фаз измерителя, вызванная разностью электрических длин gg опорного и измерительного каналов;

Су -i-tf - суммарная разность фаз; if - измеряемая разность фаз;

s

зо

0

25

В,- приращение фазового сдвига СВЧ-сигнала опорного канала;

К,, К - обобщенные коэффициенты передачи опорного и измерительного каналов; К - обобщенный коэффициент

передачи опорного канала, учитьшающий изменение модуля коэффициента передачи управляемого фазовращателя, на который подан управляющий сигнал. Эти сигналы запоминаются, Злтем вычисляются два значения функции косинуса

А cos(4,+l)(U,- иг- и,)/

в cos(({,+(|х +fi,) (Us-- и,)/24и7иГ.

В

35

2 - ч -ч 1

Используя преобразование cos(Cp -«-Lf, +р,) cos(c,,)

., - sin(C|,+ Cfx)- sin/i, A cosfi, - sin(q, + Cf, ) sin/i, определяется значение функции синуса суммарной разности фаз по выражению

. А cos3, - В sin(Q, -Kf, )

sinp,

Далее, используя соотношение для половинных углов, определяют измеряемую разность фаз tf :

Cf.+tf sin a iiifj)-- tp. -2 i;cos(4,tf,)

45

A cos . O+Ay sin (,

t, +CfK

откуда

Cf 2 arctg

A cosf I (T+Aysinp, J

Г A cosJi, I ()sin, J

Таким образом, для определения измеряемой разности фаз Cf необходимо знать собственную разность фаз измерителя if, и величины sin (., и

COSJlj,,

514658086

Величины sinp, , cosfi, и If, on- - го5((-В)

2 4UsK

ределяются на первом этапе измерения, когда на входы опорного и измерительного каналов подаются сигналы с одинаковыми фазами.

На этом этапе при помощи периодической во сьмитактовой коммутации сигналов опорного и измерительного каналов на выходе СВЧ-детектора образуются измерительные сигналы

5 Полученные значения запоминаются и используются для вычисления величин sinf),, cosfi, иМ , .

Величина i, определяется по выражению:

10

Р), arccos(F) - arccos(G).

q E,Kt;

q

4

E K 2B,E,,K,,cosq J ; a „2

и

4K

q Е;КЗ ;

USK q Ef.K; - E,K + H- 2E,,K,,cos(Cf, + /3, )

бк

9

qE.. К

-IK

74

V IK

.K

f 2E, .jK4 cosCcp.+p,-/ ) ;

и

8 к 5-2Е

t1 }40

Е,К, + Е„..К. -f-ч

,,К4

cos

(Q.-)

где р2 - приращение фазового сдвига СВЧ-сигнала измерительного канала;

К. - обобщенный коэффициент передачи измерительного канала, учитьгеающий изменение моду:- ля коэффициента передачи управляемого фазовращателя этого канала, на который подан управляющий сигнал; 4к амплитуды входных сигналэв

соответственйо опорного и 7 измерительного каналов.

Эти сигналы используются для вычисления четырех значений функций косинусов:

35

40

sinq. С tg 2 T+cosqi, (T+C)sin(b,

откуда

Гс cos f3t - D . 2 arctg by-) .

Вычисгленная величина Cf, запоминается и используется при дальнейших измерениях.

Устройство работает следующим

jg образом.

.Переключатель 15 режима работы устанавливается в положение 1. На входы опорного и измерительного каналов подаются сигналы с одинаковы- cQ ми фазами.

В первом такте открыт ключ 3, а к выходу детектора 7 через коммутатор 8 подключен запоминающий блок 9. При квадратичной хара:ктеристике детектора 7 с учетом обобщенного ко- эфЛициента передачи опорного канала

К (утгравляющий сигнал на фазовраща- F созСи +Р,{Ь ) отсутствует) запоминающий

2 |U6KU4K блок 9 фиксирует сигнал, пропорциоС сов tf,

yi). s.ii-llib -.

. г, D cos(Cf,+ fi, ) .-

2- |U4KU

13гк

Полученные значения запоминаются и используются для вычисления величин sinf),, cosfi, иМ , .

Величина i, определяется по выражению:

Р), arccos(F) - arccos(G).

вычисляются величины sin, и cos ft,, крторые запоминаются и ис- пользуются при дальнейших измерениях .

Для однозначного определения р, с высокой точностью его значение желательно устанавливать близким к ii /2. При этом величина выбирается из условия О «iCf,

. Используя преобразование D cosCcf, + f3, ) cos q), cos Р), - - sini, sin p., C cos - sinq;, sinp,, определяется значение синуса собственной разности фаз

,

sin/3,

sincj),

Используя соотношение половинных

35

40

углов, определяют собственную разность фаз ср, :

sinq. С tg 2 T+cosqi, (T+C)sin(b,

откуда

Гс cos f3t - D . 2 arctg by-) .

Вычисгленная величина Cf, запоминается и используется при дальнейши измерениях.

/

нальный квадрату амплитуды входного сигналя, т.е. U,, qF.K . Во втором такте открыт ключ 4 и к детектору 7 подключен запоминающий блок 10, который с учетом обобщенного коэффициента передачи измерительного канала К,, (управляющий сигнал на фазовращателе 2 отсутствует) фиксирует сигнал и,,, ПЕ,. В третьем такте открыты оба ключа 3 и 4, к выходу детектора 7 подключен вычитаю- .гщй блок 12, на который одновременно подаются сигналы с запоминающих блоков 9 и 10, а к выходу измерителя 14 отношения подключен запоминающий блок 16. Во время третьего такта при отсутствии управляющих сигналов на фазовращателях 1 и 2 на выходе детектора 7 в соответствии с теоремой косинусов формируется сигнал

и, ,к 2-4u5K Wcosq,. В вычитаДем блоке 12 происходит вычитание первых двух слагаемых, на его выходе формируется сигнал Uq 241Гк1 кСО.чЧ, . Одновременно сигналы и, и с запоминающих блоков 9 и 10 подаются на блок IJ

- . .г ffj mj r t-iri or

1465808

а , (М Л

10

нал и ,- . „ -t- р,) , из которого в вычитающем блоке 12 происходит вычитание сигналов и 1 и . На выходе вычитающего блока 12 формируется сигнал 2 -JIUK 4K- cos((f, ). Одновременно с этим на выходе блока 13 преобразования функикй образу ется выходной сигнал и„, 24V4K « лов.-постгпающих с запоминаюпг- х бло ков 9 и 10. Обработка сигналов D измерителе 14 отноиеник дает на выходе сигнап и,4к a,cos(L|, ). кото- рьш заносится в запоминак пий блок 1/ В шестом такте открыт ключ 4, на управляемый фазовращатель 2 подан управ лятий сигнал, а к выходу детекто 20 ра 7 подключен запоминающий блок 1U, который с учетом обобщенного коэффициента передачи измерительного кана- ла К, фиксирует сигнал В седьмом, такте открыты оба ключа 25 3 и 4, на управляемые фазовращатели и 2 поданы управляющие сигналы, к выходу детектора 7 подключен вычитаю щий блок 12, на которьш одновременно подаются сигналы с запо

п .. 1 П . п V H nronV

15

р: а:ов:н;: : --Рь осу- ЗО -а..их блоков 9 а к ществляет перемножение входных сигна- измерителя лов извлечение квадратного корня с последующим удвоением полученного

1п fmr ТТЛ1Т1Г ПМИТ5 V

последуил щм -

результата. На его выходе формирует- сигнал L . П

,, 9 JTl и, . Обработ- -.. ,.. ;; л ся сигнал Ь.. -

WK1 /. ,.«u/ tito-

измерителя ч отнишсп /. запоминающий блок 18. На выходе детектора 7 при этом фор шруется

Ь бк

СИГННЛ iJ-Yi, 4К °К 1

ся СИ1 па-1 АПв

ка сигналов в измерителе 14 отношения дает на выходе сигнал U,,

а cost , где а, - коэффициент про- ходе им1,г..:./«-.--.

пор1 иональности. Вьосодной сигнал из-,сов r,- (. - Рг Одновременно сигмерителя 14 отнощения заносится в за-40 „,, ;, „ и, „з запоминающих блок

поминающий блок 16. В -ер.ом так- .„-.одаются на блок 3 ФУ -o

4k bt ,, 9 Гг 11

ходе образуется сигнал 11,- А/ П .

nOMHrlclrJi J an i jiv- iv

те открыт ключ 3, в опорный канал введено приращение фазового сдвига СВЧ-сигнала путем подачи на фазо- йращатель 1 управляющего сигнала, . а к вьгходу детектора 7 подключен за-- поминающий блок 9, которьй с учетом обобщенного коэффициента передачи опорного канала К, фиксирует сигнал и прЛ Kt. В пятом такте откры- ™ оба Глюча 3 и 4, на управляемьй Фазовращатель 1 подан управляющий сигнал, к выходу детектора 7 подключен вычитающий блок 12, на кото-, рый одновременно подаются сигналы 1 и с запоминающих блоков У и ш, а к выходу измерителя 14 отношения подключен запоминающий блок 17. На выходе детектора 7 формируется сигблоко

Ги п дГтсГнГблок .3 функционального преобразования, на вьтходе которого формируется сигнал ь,, лс 2 л|и., U,J . Обработка сигналов и, .и и,, в измерителе 14 отношени дает на выходе сигнал 1:,-, а . +Р,- К), который заносится в запоминающий блок 18. В во 50 мом такте открыт ключ 3, управляю- щий сигнал на управляемом фазовращ теле 1 отсутствует, а к выходу дет тора 7 подключен запоминающий блок который фиксирует сигнал И, ее аР - В девятом такте открыты оба к лю а 3 и 4, на управляемый фа вращатель 2 подан управляющий сигн к выходу детектора 7 подключен вычитающий блок 12. на который одно

и

465808

а , (М Л

10

нал и ,- . „ -t- р,) , из которого в вычитающем блоке 12 происходит вычитание сигналов и 1 и . На выходе вычитающего блока 12 формируется сигнал 2 -JIUK 4K- cos((f, ). Одновременно с этим на выходе блока 13 преобразования функикй образу ется выходной сигнал и„, 24V4K « лов.-постгпающих с запоминаюпг- х бло ков 9 и 10. Обработка сигналов D измерителе 14 отноиеник дает на выходе сигнап и,4к a,cos(L|, ). кото- рьш заносится в запоминак пий блок 1/. В шестом такте открыт ключ 4, на управляемый фазовращатель 2 подан управ лятий сигнал, а к выходу детекто- 20 ра 7 подключен запоминающий блок 1U, который с учетом обобщенного коэффициента передачи измерительного кана- ла К, фиксирует сигнал В седьмом, такте открыты оба ключа 25 3 и 4, на управляемые фазовращатели и 2 поданы управляющие сигналы, к выходу детектора 7 подключен вычитающий блок 12, на которьш одновременно подаются сигналы с запо

п .. 1 П . п V H nronV

15

у- ЗО -а..их блоков 9 а к на- измерителя с

-а..их блоков 9 а к измерителя

измерителя ч отнишсп /. запоминающий блок 18. На выходе детектора 7 при этом фор шруется

О -а..их блоков 9 а к измерителя

сигнал L . П

-.. ,.. ;; л

Ь бк

СИГННЛ iJ-Yi, 4К °К 1

ходе им1,г..:./«-.--.

,сов r,- (. - Рг Одновременно сиг 4k bt ,, 9 Гг 11

ходе образуется сигнал 11,- П .

,сов r,- (. - Рг Одновременно сиг0 „,, ;, „ и, „з запоминающих блок

.„-.одаются на блок 3 ФУ -o

блоков

Ги п дГтсГнГблок .3 функционального преобразования, на вьтходе которого формируется сигнал ь,, лс 2 л|и., U,J . Обработка сигналов и, .и и,, в измерителе 14 отношения дает на выходе сигнал 1:,-, а . +Р,- К), который заносится в запоминающий блок 18. В вось- 50 мом такте открыт ключ 3, управляю- щий сигнал на управляемом фазовраща теле 1 отсутствует, а к выходу детектора 7 подключен запоминающий блок 9 который фиксирует сигнал И, ее аР - В девятом такте открыты оба к лю а 3 и 4, на управляемый фазовращатель 2 подан управляющий сигнал к выходу детектора 7 подключен вычитающий блок 12. на который одно

временно подаются сигналы U, , UJK. с запоминающих блоков 9 и 10, а к выходу измерителя 1А отношения подсоединен зaпo шнaющий блок 19. На выходе детектора формируется сигнал

вк бк- ,к бк«--оз()- В вьгчитающем блоке 12 происходит вычитаниенала и

сигнал

сигналов и и на его

.8 к 2и и.

из. сиг(К ЛХ

выходе образуется

UTfc- соз(с,-pi).

Одновременно из запоминающих блоков 9 и 10 поступают сигналы Ubv; на блок 13 преобразования функций на его выходе формируется сигнал

«Чк которьш одновременно с выходным сигналов вычитающего блока 12 поступает на измеритель 14 отношения. На выходе последнего образуется сигнал 2о ((,-(Ь ), который заносится в запоминающий блок 19. Выходные сигналы с запоминающих блоков 16 - 19 одновременно поступают на вычислитель 20 разности фаз, на выходе которого формируется сигнал 11, aiq, (где а - коэффициент пропорциональности), который заносится в запоминающий блок 21, Затем переключатель 15 режима работы устанавливается в положение На выходы опорного и измерительного каналов подаются сигналы с измеряемой разностью фаз. При этом устройство работает как и на протяженки первых пяти тактов .Поэтому на выходе детектора 7 за пять тактов коммутации Нормируются сигналы и,т Е,К,;

пк1

и,

и +

xcos(q,+q)); 11 q Е,

и, + IL + 2

СОЕ(О,.,).

Из этих сигналов формируются выходные сигналы измерителя 14 отношения и„ a,cos(q ,+(|,); U,, а, cos (if, + + Uf - p,} t которые заносятся в запоминающие блоки 16,17. Выходные сигнаUfj, с запоминающих

лы и,, ,11,4 блоков 16 - 19 одновременно поступают на .вычислитель 20 разности фаз, на выходе которого образуется сигнал и,, а,2(ср,+ lf) . Сигнал U, одновременно с нающего блока ющий блок 22,

выходным сигналом U, | запоми- 21 подаются на вычитана выходе которого фор-

мируется сигнал

1Ча

, (где а, коэффициент пропорциональности), пропорциональный измеряемой разнос-

146580810

ти фаз; этот сигнал фиксируется индикатором 23.

Вычислитель 20 разности фаз работает следующим образом.

При первом этапе измерения на входы блоков 24 и 25 преобразования арккосинуса одновременно подаются

5

сигналы a,cos(Q, + Р юц (Cf,- .) из запоминающих блоков 18 и 19. На выходах блоков 24 и 25 соответственно формирзпотся сигналы Ь г-ж. ,+ |5, -/5г ) t ( гРг г-де а - коэффициент пропорциональности, которые

поступают на вычитающий блок 26, На выходе последнего образуется сигнал

В,, пропорциональньш величине (где а - коэффициент пропорцио а5к

(

0

нальности) . Затем сигнал V ORKO- временно поступает на блок 28 вычисления синуса, и блок 29 вычисления косинуса, на их выходах соответственно формируются сигналы

5 а sin PI

и,

27 К

- а

cos

/, (где

- коэффициент пропорциональности).- . Одновременно с этим на сумматор 30 подаются два сигнала: сигнал единичного уровня, который вырабатывается

0 формирователем 27 напряжения, и сигнал хранящийся в запоминающем блоке 16. Выходной сигнал сумматора 30 a,(l+cosq ,) одновременно с сигналом 1L подается на перемножитель

,с 31 ,при этом на его выходе формируется сигнал aj (l+cosCf,) sin р (где а - коэффициент пропорциональности). Наряду с этим на перемножитель 32

поступают сигналы к «к 0 торые обеспечивают на его выходе сигнал ЭцСОБ Cf, cos, (где ag - коэф(Ъициент пропорциональное ти). Выходной сигнал Uj перемножителя 32 одновременно с сигналом хранящимся в запоминающем блоке 17, поступает на вычитающий блок 34. На его выходе образуется сигнал 1 з(к

, cos(i, - cos(C|,+fi, )J , который совместно с выходным сигна- лом перемножителя 31 подается на блок 33 деления. На выходе блока 33 деления формируется сигнал

fc, - «о tg 2

5

к

55

coscpj cQS,((,+P2l

te T-fcosq T)sin l3 . поступающий на блок 35 преобразования арктангенса. На выходе последнеи

1465808

1 2

10

-однознпчного измерения разности фаз и повышения точности, в миллиметровом диапазоне волн в дополнительные такты коммутации сигналов опорного и измерительного каналов вводят приращение фазовых сдвигов в опорньш и измерительный каналы, определяют значения косинусов собственной раз мости фаз измерителя, суммы собственной разности фаз измерителя и измеряемой разности фаз, приращения по опорному каналу разности фаз, суммы собственной разности фаз изме- ,. рителя и приращения по опорному кана лу разности фаз, суммы собственной разности фаз измерителя и приращения во опорному и измерительному каналам, суммы собственной разности фаз 20 измерителя и приращения по измерительному каналу разности фаз, вычис ляют по полученным значениям косину сов значения синуса и косинуса при ращения разности фаз по опорному ка- 25 налу, затем вычисляют собственную разность фаз измерителя и собственной разности фаз измерителя и измеряемой разности фаз, для чего используют тригонометрические со- 30 отношения для половинных углов, а искомую разность фаз-определяют как разность суммы собственной разности фаз измерителя и измеряемой разности . фаз и собственной разности фаз изме- рителя.

исследования, способ и , с.атора, а выход последнего соеди- позволяют создать автоматизированные 40 детектора, выход ко- микропроцессорные анализаторы епей, „,„,,ен к первому входу

коммутатора, второй вход которого соединен с первым выходом первого .. блока управления, управляющие входы - первого и второго ключей соединены соответственно с вторым и третьим выходами блока управления, четвертый выход которого подключен к управляюсь щим входам запоминающих блоков, ин- ° Лормационные входы которых соединены соответственно с первым и вторым выходами коммутатора, выходы первого и второго запоминающих блоков под - ключены соответственно к первому и . второму входам вычитающего блока и первому и второму входам блока преобразования, выход которою подключен к первому входу измерителя отного образуется сигнал 1,,- а,,, . пропорциональный собственной разности фаз. Коэффициенты а,.а,„ являются коэффициентами пропорциональности. При дальнейших измерениях работа вычислителя 20 разности фаз не отличается от описанной, однако вместо сигнала П„ используется сигнал и„ , который поступает на сумматор 30 и перемножитель 32, а вместо, сигнала . и , - сигнал , поступающий на вычитающий блок 34. При этом на выходе блока 35 формируется сигнал , д (qi + qi), пропорциональный суммарной разности фаз.

Таким образом, повышение точности измерения разности фаз достигается за счет исключения из результатов измерения собственной разности фаз измерителя и за счет увеличения крутизны преобразования, так как крутизна изменения тангенса в диа- пазоне измеряемых углов больше крутизны изменения косинуса при тех же значениях углов, а также за счет то-; го, что результат измерения не зависит от величины приращений фазовых сдвигов СВЧ-сигналов опорного и З- . мерительного каналов.

Расщирение диапазона однозначности измерения разности фаз достигается за счет использования при определении измеряемой разности фаз глав-; ных значений функции тангенса половинных углов, которые имеют диапазон однозначности от - ii до и

Как показали экспериментальные исследования, способ и устройство позволяют создать автоматизирован микропроцессорные анализаторы цеп которые могут быть использованы в миллиметровом и субмилл:иметровом диа пазонах.

Формула

зобретения

65808

1 2

-однознпчного измерен и повышения точности вом диапазоне волн в такты коммутации сиг и измерительного кан ращение фазовых сдви измерительный каналы значения косинусов мости фаз измерител венной разности фа измеряемой разности по опорному каналу суммы собственной р ,. рителя и приращения лу разности фаз, су разности фаз измери во опорному и измер лам, суммы собствен 20 измерителя и приращ тельному каналу раз ляют по полученным сов значения синуса ращения разности фа 25 налу, затем вычисл разность фаз измер ственной разности измеряемой разност используют тригон 30 отношения для поло искомую разность ф разность суммы соб фаз измерителя и и . фаз и собственной

гаения, второй вход которого соединен с выходом вычитающего блока, третий вход которого подключен к третьему выходу коммутатора, отличающееся тем, что, с целью расширения диапазона однозначного измерения разности Лаз и повышения точности в миллиметровом диапазоне волн.

оно снабжено двумя управляемыми фазо- Q тель разности фаз содержит первый и

вращателями, третьим, четвертым, пятым, щестым и седьмым запоминающими блоками, вычислителем разности фаз, вторым вычитающим блоком, вторым блоком управления, переключателем режима работы и индикатором, причем выход измерителя отношения соединен с информационными входами третьего, четвертого, пятого и шестого запо «1нающих блоков, выходы ко торых подключены соответственно к первому, второму, третьему и четвертому входам вычислителя разности фаз, выход которого соединен с информационным входом седьмого запо минающего блока и с первым входом , второго вьтитающего блока, выход которого подключен к входу индикатора, второй вход второго вычитающего блока соединен с выходом седьмого. запоминающего блока, управляющий вход которого подключен к третьему выходу переключателя режима работы, первый и второй выходы которого сое ди;нены с управляющими входами пятого и шестого запоминающих блоков, первый, второй и третий входы переключателя режима работы подключены к пятому, шестому и седьмому выходам второго блока управления, третий и четвертый выходы которого соединены соответственно с управляющими входами третьего и четвертого запоминающих блоков, первый и второй выходы второго блока управления соединены с управляющими входами первого и второго управляемых фазовращателей, выходы которых подключены к входам ключей, вход второго блока управления соединен с .пятым вьгходом первого блока управления.

5 перемножители, блок деления, второй сумматор, формирователь напряжения и блок преобразования арктангенса, причем выходы первого и второго блоков преобразования арккосинуса соедиQ нены соответственно с первым и вторым входами третьего вычитающего блока выход которого подключен к входам блоков вьтисления синуса и косинуса, первый вход вьшислителя

5 разности фаз соединен с первыг-щ вхо-; дами второго перемножителя и второго сумматора, а второй - с первым входом четвертого вычитающего блока, выход блока- вычисления косинуса через второй перемножитель подключен к второму входу четвертого вычитающего блока, выход которого подключен к перг, вому входу блока деления, выход формирователя напряжения соединен с вторым входом второго сумматора, выход которого. Через последовательйо соединенные первый перемножитель и блок деления соединен с входом блока преобразования арктангенса, при этом второй вход первого перемножителя соединен с выходом блока вычисления синуса, а третий и четвертый . входы вычислителя разности фаз соединены соответственно с входами первого и второго блоков преобразования

0

5

0

5

арккосинуса.

| Устройство для измерения разности фаз | 1979 |

|

SU783706A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

Авторы

Даты

1989-03-15—Публикация

1987-01-08—Подача