Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных вы числительных системах (ВС) с большой глубиной распараллеливания вычислительных процессов для оперативного контроля корректности распределения ресурсов.

Цель изобретения - увеличение глубины диагностирования о

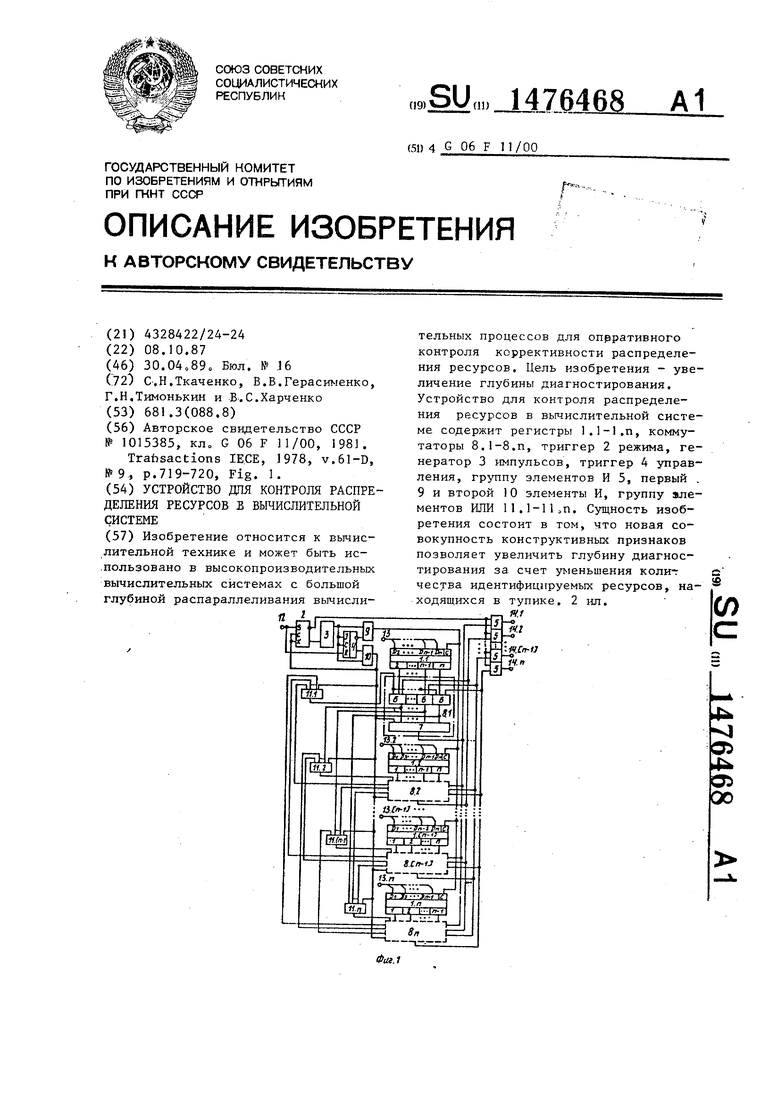

На фиг.1 представлена функциональная схема устройства для контроля распределения ресурсов вычислительной системы; на фиг.2 - график распределения ресурсов.

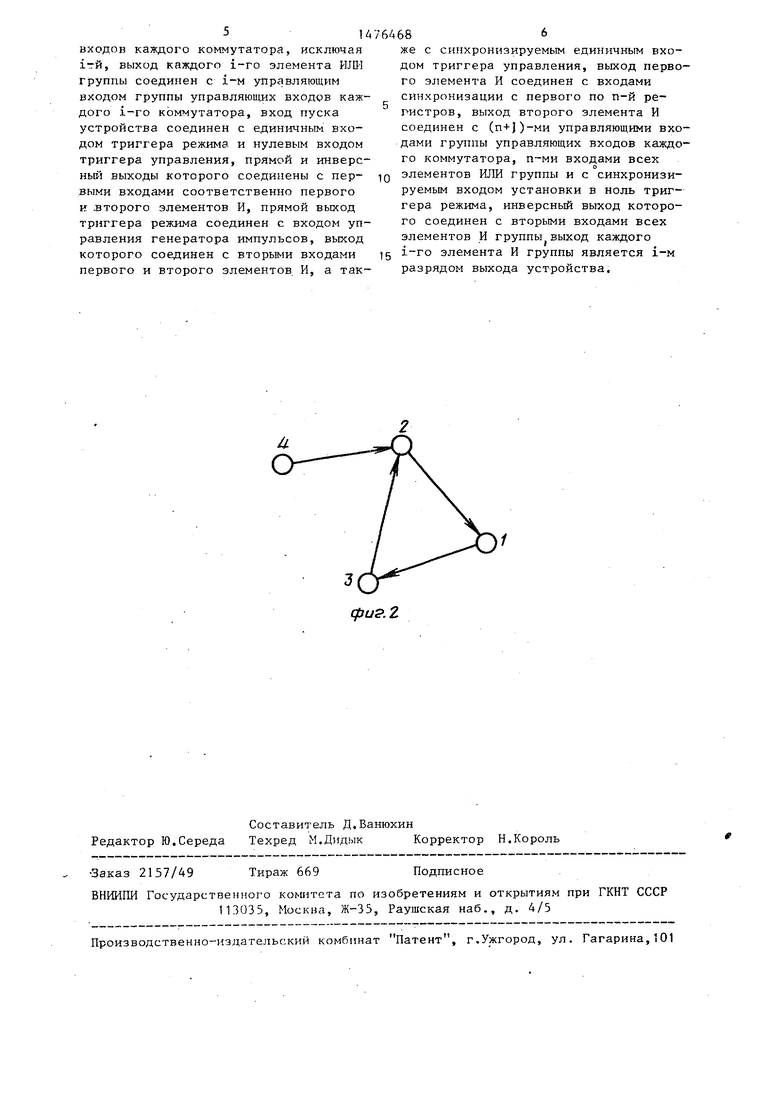

Устройство для контроля распределения ресурсов вычислительной системы содержит (фиг. 1) первый 1.1-п-й 1„п регистры (п - число типов ресурсов системы), триггер 2 режима, генератор 3 импульсов, триггер 4 управления, группу элементов И 5, группу элементов И 6 и элемент ИЛИ 7, входящие в состав каждого из коммутаторов 801-8„п, первый 9 и второй 0 элементы И, группу элементов ИЛИ 11, вход 12 пуска устройства, группы 13.1-13.П информационных входов устройства, разряды выхода 14 „1-14 устройства.

Регистры 1.1-1сп предназначены дл приема, хранения и выдачи информации о состоянии распределения ресурсов. Поскольку процесс, владеющий 1-м ресурсом R-, не может повторно его запрашивать, то 1-й разряд каждого регистра l.i не используется.

В остальные разряды 1-го регистра 1.1 информация записывается следующим образом. Если i-м ресурсом владеет какой-либо процесс (процессы) который, кроме того, запрашивает другой ресурс, например БЦ (или несколько ресурсов одновременно), то в j-й разряд 1-го регистра 1,1 записывается 1, а в остальные - О.

Если же i-м ресурсом только владеет один или несколько процессов и этот процесс (процессы) дополнительно никакие другие ресурсы не запра- шивает, то во все разряды 1-го регистра 1.1 записываются нули. Процессы, только запрашивающие какие-либо ресурсы, также не запоминаются в регистрах 1.1 (1 1,п).

Триггер 2 режима предназначен для задания режимов работы устройства: ожидания работы и анализа. Генера

76468 тор

10

15

20

3 импульсов предназначен для формирования последовательности импульсов. Триггер 4 управления предназначен для синхронизации работы устройства. Группа элементов И 5 предназначена для выдачи информации о состоянии ресурсов системы после того, как устройство закончит свою работу. Группа элементов И 6 предназначена для формирования соответствующих управляющих сигналов в зависимости от исходных информационных и управляющих на входе„ Элемент ИЛИ 7 предназначен для селектирования входных сигналов и выработки соответствующего выходного сигнала управления.

Коммутатор 8.1 предназначен для формирования сигналов управления в зависимости от входной и управляющей информации.

Элемент И 9 предназначен для инициирования импульсов приема исходной информации в регистры 1.1-1.п.

Элемент И 10 предназначен для выработки сигнала начала анализа

Элементы ИЛИ ПД (,п) группы элементов ИЛИ 11 предназначены для формирования сигналов управления ра- 30 ботой соответствующих коммутаторов. Выход 12 пуска предназначен для приема сигнала пуска устройства. Группа 13 информационных входов предназначена для приема информации в регистры 1.1-l.n о распределении ресурсов вычислительной системы0 Группа 14 выходов предназначена для выдачи информации о ресурсах, вовлеченных в туг пик, если такие имеются.

Работу устройства рассмотрим на примере процедуры контроля распределения ресурсов в системе, график распределения ресурсов которой представлен на фиг.2„

25

35

40

В исходном состоянии все элементы памяти хранят нулевые значения (входы установки в нуль на чертеже условно не показаны). По сигналу пуска с входа 12 пуска устройства триггер 2 режима устанавливается в единичное состояние, а триггер 4 управления (если это запуск повторный) - в нулевое.

Высоким потенциалом с прямого выхода триггера 2 режима запускается генератор 3 импульсов, а низким потенциалом с инверсного выхода закрывается группа элементов И5.

Первый импульс с выхода генератора 3 импульсов через открытый высоким потенциалом с инверсного выхода триггера 4 управления элемент И9 поступает на синхровходы всех регистров 1.1-l.n, разрешая тем самым прием информации о состоянии распределения ресурсов: в третий разряд первого регистра 1.1, в первый разряд второго регистра 1.2, во вторые разряды третьего 1.3 и четвертого 1.4 регистров запишутся единицы. В остальных разрядах всех регистров будут храниться нули.

По заднему фронту первого импульса триггер 4 управления устанавливается в единичное состояние. Элемент И9 низким потенциалом с инверсного выхода этого триггера закрывается, а вы- сокий потенциал с прямого выхода подается на вход элемента И10. Поэтому второй импульс с выхода генератора 3 импульсов открывает его. Сигнал, сформированный на выходе элемента И8, поступает на вторые управляющие входы всех коммутаторов, а также на n-е входы всех элементов группы ИЛИ

И.

После срабатывания элементов ИЛИ в группе и во всех коммутаторах на выходах всех коммутаторов формируются высокие потенциалы, поступающие на все (за исключением 1-х для 1-го, коммутатора) управляющие входы первой группы управляющих входов всех коммутаторов, а сигналы с выхода каждого элемента ИЛИ 11„i поступают на первые управляющие входы коммутатора 8.1.

После этого в каждом коммутаторе

срабатывают те элементы группы элементов И 6, на входах которых присутствуют высокие потенциалы, поступающие с выходов соответствующих разря- дов регистров 1.1-l.n. Для рассматриваемого примера такими элементами являются третий элемент И первого коммутатора 8,1, первый - второго коммутатора 8.2, вторые элементы И третьего 8.3 и четвертого 8.4 коммутато- . ров.

Высокие потенциалы с выходов этих элементов поступают на входы элементов И7 в каждом коммутаторе и на входы соответствующих элементов группы ИЛИ 11 элементов ИЛИ,

По окончании положительного импульса с выхода элемента И 10 на всех

0

5

5

0

0

5 g

0

5

входах элемента ИЛИ 11.4 присутствуют только низкие потенциалы и нулевой сигнал с его выхода запирает коммутатор 8.4, который также на своем выходе формирует нуль. Единичными сигналами с выходов остальных элементов И 11 коммутаторы 8.1-8.3 остаются открытыми. На их выходах формируются единичные сигналы.

По заднему фронту импульса с выхода элемента И 10 триггер 2 режима устанавливается в нулевое состояние. Низким потенциалом с его прямого выхода останавливается генератор 3 импульсов, а высоким потенциалом с инверсного выхода открывается блок 5 элементов И, Срабатывают первые три элементы И и выходные шины 14,1-14.3 группы выходов 14 устройства остаютт ся возбужденными. Таким образом, обнаруживается тупиковая ситуация по первому, второму и третьему ресурсам. Функционирование устройства на этом прекращается

Формула изобретения

Устройство для контроля распределения ресурсов в вычислительной системе, содержащее с первого по п-й регистры, где п - число типов ресурсов системы, с первого по n-й коммутаторы, причем с первого по (1-1)-й и с (i+l)-ro по n-й разряды каждой i-й группы (,п) информационных входов устройства соединены соответственно с первым (1-1)-м и (1+1)-м ...,п-м информационными входами i-ro регистра, выход каждого j-ro разряда группы выходов каждого 1-го регистра (i/j , j-l,n) соединен соответственно с информационными входами разрядов каждой j-й группы входов 1-го коммутатора, отличающееся тем, что, с целью увеличения глубины диагностирования, оно содержит триггер режима, генератор импульсов, триггер управления, группу элементов И, группу элементов ИЛИ, первый и второй элементы И, причем выход каждого j-ro разряда группы выходов каждого 1-го коммутатора соединен с соответствующим входом j-ro элемента ИЛИ группы, выход 1-го разряда группы выходов каждого i-ro ком- мутатора соединен с первым входом 1-го элемента И группы, с i-ми управляющими входами группы управляющих

514

входов каждого коммутатора, исключая i-й, выход каждого 1-го элемента ИШ1 группы соединен с i-м управляющим входом группы управляющих входрв каждого 1-го коммутатора, вход пуска устройства соединен с единичным входом триггера режима и нулевым входом триггера управления, прямой и инверсный выходы которого соединены с первыми входами соответственно первого и второго элементов И, прямой выход триггера режима соединен с входом управления генератора импульсов, выход которого соединен с вторыми входами первого и второго элементов И, а так64686

же с синхронизируемым единичным входом триггера управления, выход первого элемента И соединен с входами синхронизации с первого по n-й регистров, выход второго элемента И соединен с (п+)-ми управляющими входами группы управляющих входов каждого коммутатора, входами всех элементов ИЛИ группы и с синхронизируемым входом установки в ноль триггера режима, инверсный выход которого соединен с вторыми входами всех элементов И группы выход каждого 5 1-го элемента И группы является i-м разрядом выхода устройства.

5

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля распределения ресурсов | 1989 |

|

SU1702372A1 |

| Устройство для контроля распределения ресурсов в вычислительной системе | 1985 |

|

SU1312583A1 |

| Устройство для контроля распределения ресурсов | 1985 |

|

SU1297051A1 |

| Устройство для контроля распределения ресурсов | 1985 |

|

SU1297061A1 |

| Устройство для контроля распределения ресурсов | 1987 |

|

SU1509898A1 |

| Устройство для контроля распределения ресурсов в вычислительной системе | 1985 |

|

SU1269138A1 |

| Устройство обмена данными распределенной управляющей системы | 1990 |

|

SU1718226A1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1987 |

|

SU1462344A1 |

| Устройство для обмена данными | 1984 |

|

SU1278874A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1986 |

|

SU1388863A1 |

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных вычислительных системах с большой глубиной распараллеливания вычислительных процессов для оперативного контроля корректности распределения ресурсов. Цель изобретения - увеличение глубины диагностирования. Устройство для контроля распределения ресурсов в вычислительной системе содержит регистры 1.1-1.N, коммутаторы 8.1 - 8.N, триггер 2 режима, генератор 3 импульсов, триггер 4 управления, группу элементов И 5, первый 9 и второй 10 элементы И, группу элементов ИЛИ 11.1-11.N. Сущность изобретения состоит в том, что новая совокупность конструктивных признаков позволяет увеличить глубину диагностирования за счет уменьшения количества идентифицируемых ресурсов, находящихся в тупике. 2 ил.

С о с т ав ит ель Д.Банюхин Редактор Ю.Середа Техред М.Дидык Корректор Н.Король

Заказ 2157/49

Тираж 669

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 1П035, Москва, Ж-35, Раушская наб., д. 4/5

. - ---- - - - - - - -- - -.--,.- -- -..«..

Производственно-издательский комбинат Патент, г.Ужгород, ул. Гагарина,101

фиг. 2

Подписное

| Устройство контроля | 1981 |

|

SU1015385A1 |

| Transactions IECE, 1978, V.61-D, № 9, р.719-720, Fig | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-04-30—Публикация

1987-10-08—Подача