1

Изобретение относится к иычнслн-- телыюй технике и может быть использовано в качестве тчоммутггрующей сети ;у1я упраплелия и обмена данньп-гл в распределенных системах с контролем.

Целью изо6ретенг-1я является повышение производительпост - устройства

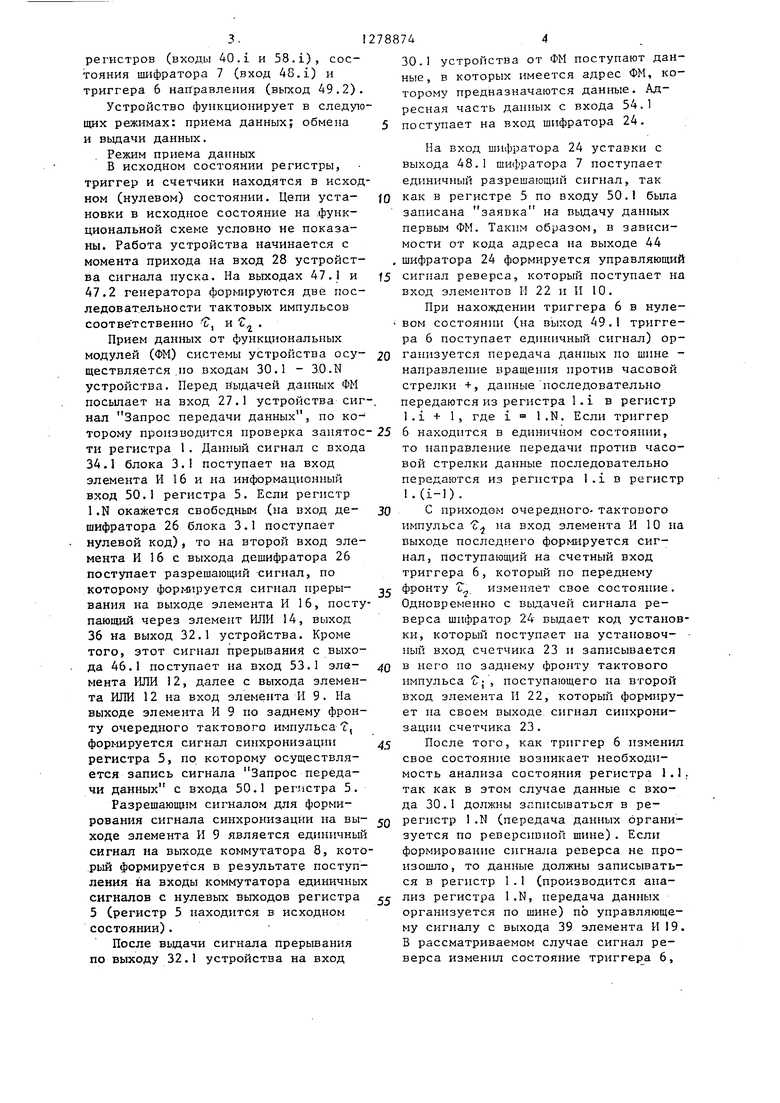

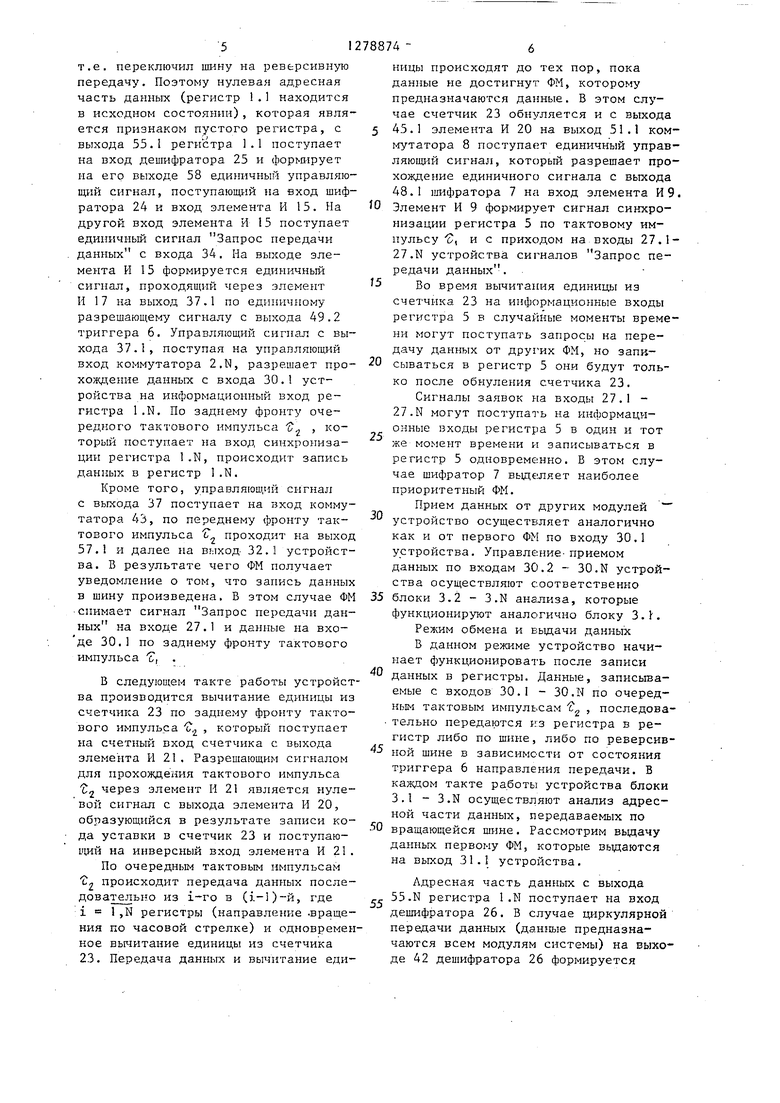

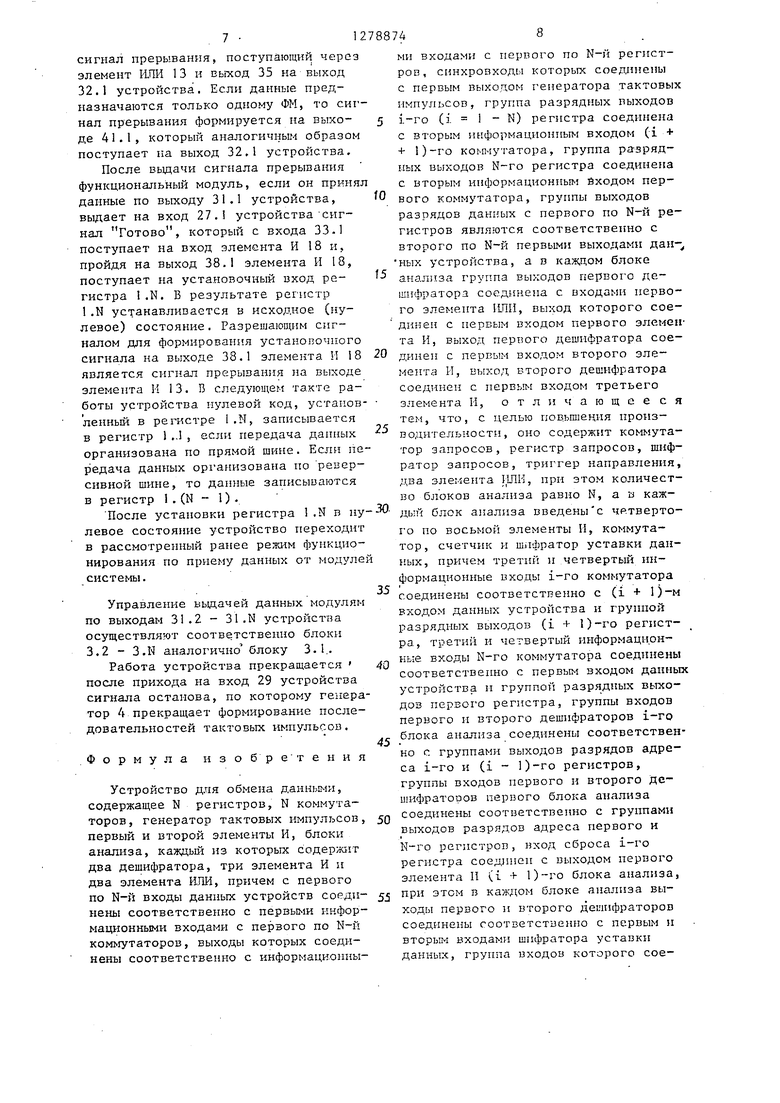

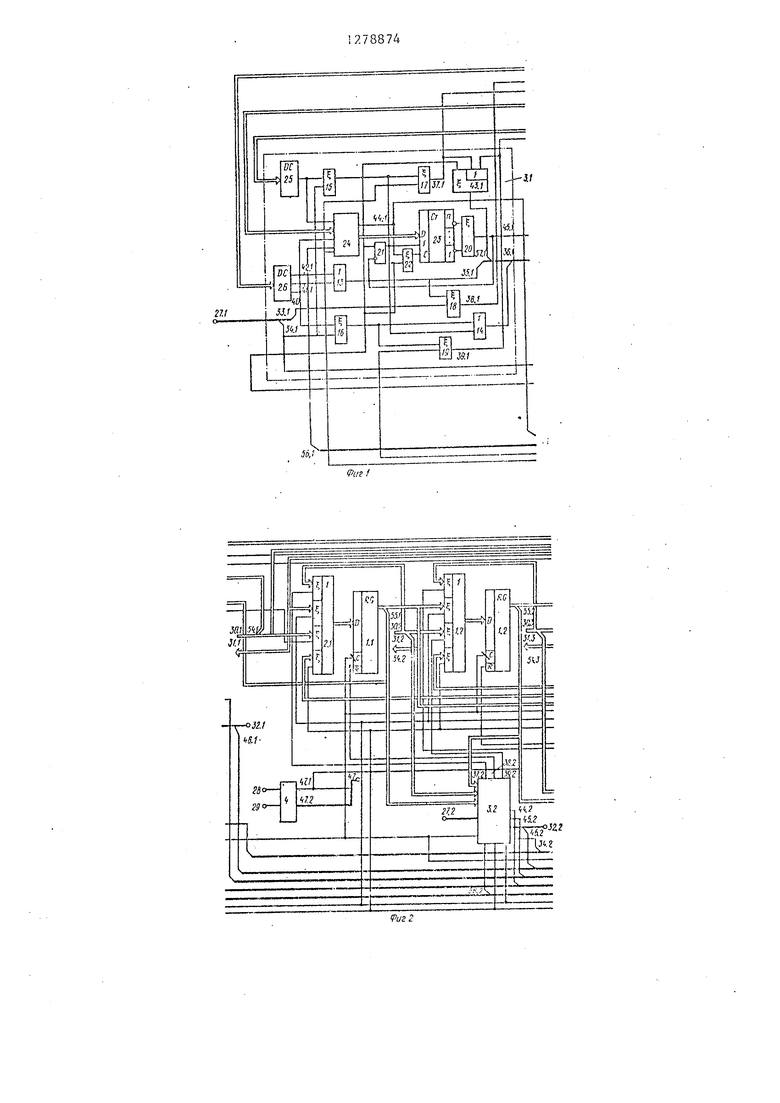

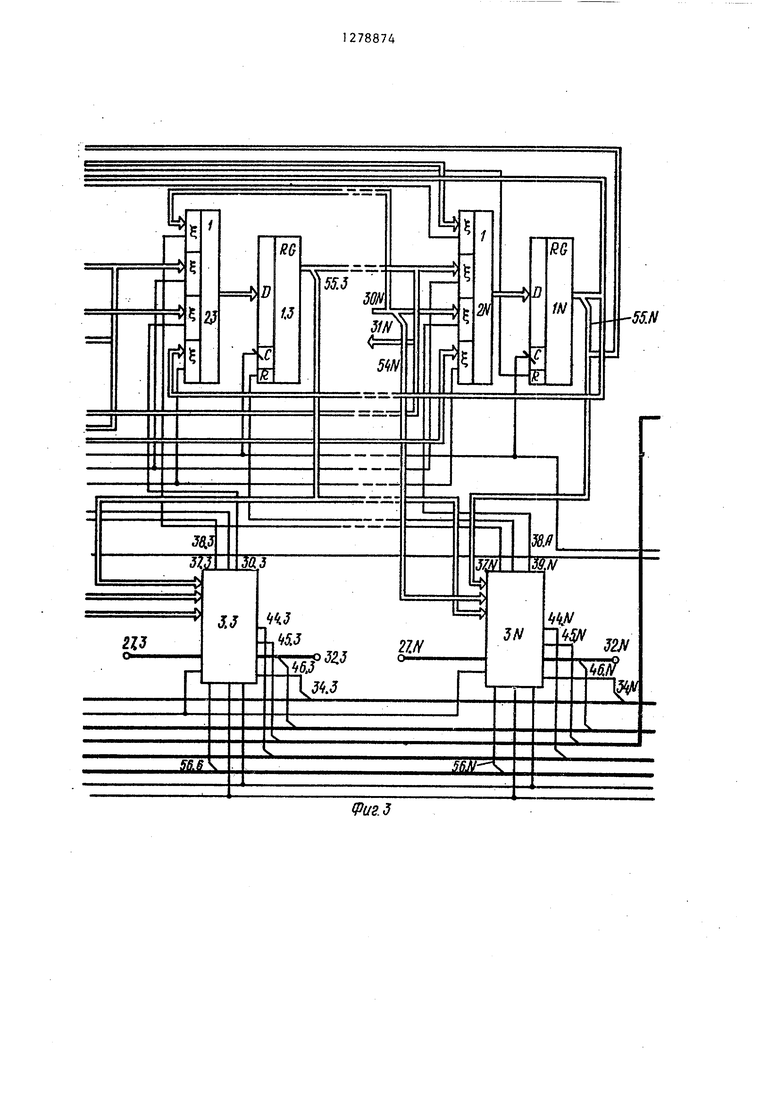

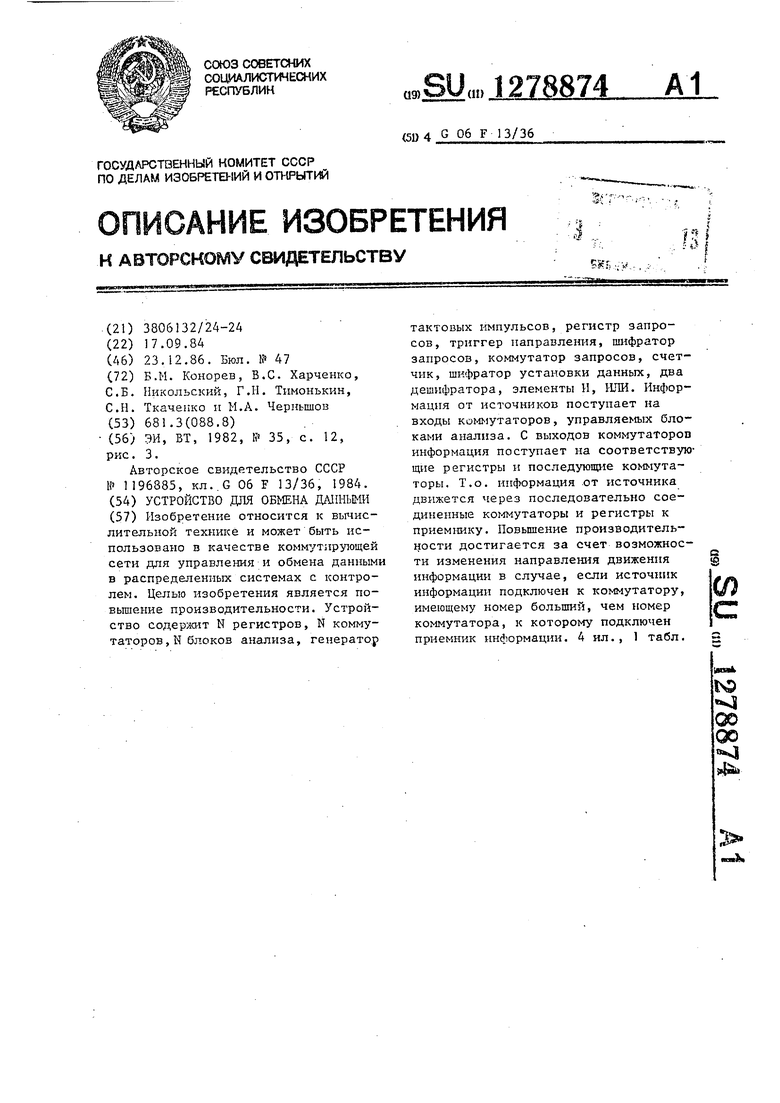

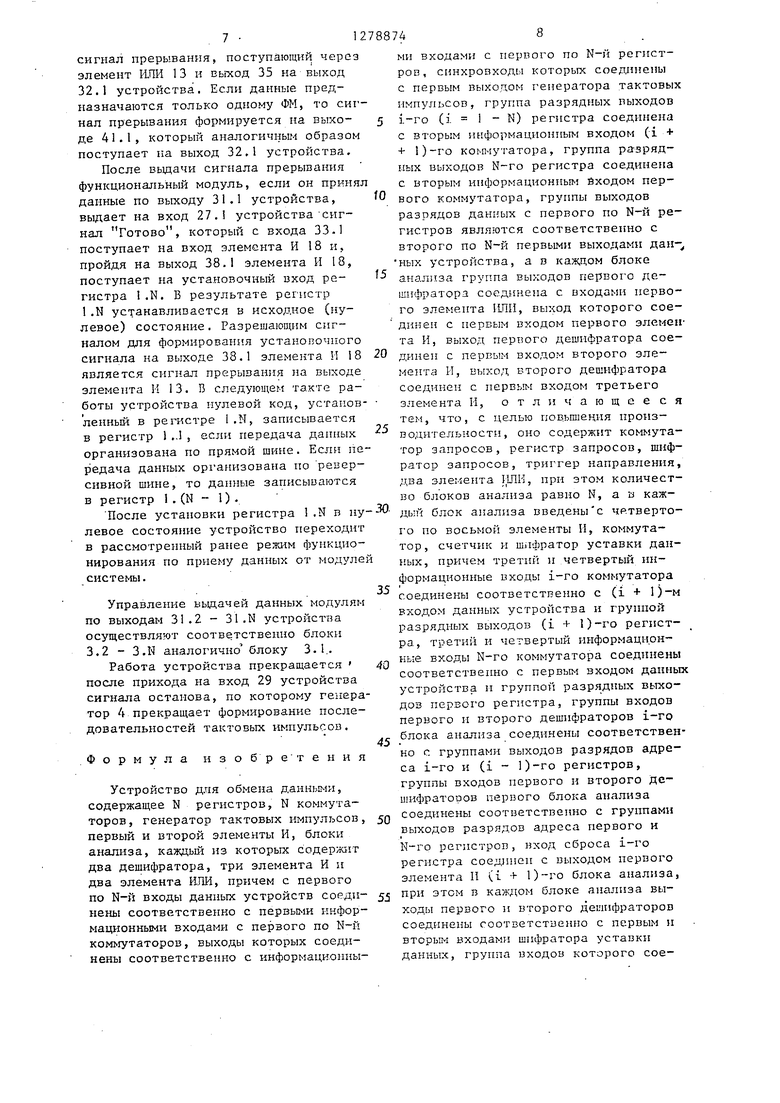

На фиг. 1-4 призеде а ,по1:ал ная схема устройства.

Устройство содепззшт ггерпые - Н-е регистры 1.1 I.NJ первые - N-e коммутаторы 2.1 - 2,N, первые - N-e блоки 3.1 3,N анализа, генератор 4 тактовых импульсов, регистр 5 за- просо, триггер 6 мап)авлеп1 я, шясЬ- ратор 7 запросов, коммутатор 8 запросов, второй элемент II 9, первый элемепт Я 10, второй олемепт ИЛИ 11 перхзый элспмепт ИЛН 12, первый элеме 1иШ 13, второй злемепт 1ШИ 14, третий элемент Г 15, BTOpoi-i элемепт 1 .16, пгггый эле;- епт И 17, первый элемент 18, шестой элег юпт И 19, четлерть й И 20, осьг-;ой элемент П 21, седь: ой элемепт Н 22, счетмик 23, шшЬратор 24 уставки дан iibiXs первый депшфратор 25, второй деши Ьратор 26, nepBbiii - входы 27,1 -- 27 .N запроса передачи дазпгых устройства, вход 28 пуска устройства, вход 29 oc i anoBa устройства, лервый - М-й входы 30.1 - 30.N двп- ных устройства, neiiBbul N-ii выходы 31.1 - 31.N даипы-х устройства, пер- вый выходы 32,1 - 32,N сигналов прерываний устгюйства, вход 33 си г-н ал а 1 отовпости функця опального модуля:, входы. 34 Л - 34, N сигнала

О

О

О

I

О о

П р я м е ч а и и е: х; - i-гзход схемы 7 анализа;

у, - i-й выход 48 i-й схемы анализа.

Ш Ифратор 24 п.ре;. назпачеп для

ла управления PBBGIJCOM шины да 44,1 в зависимости от зан

формирования уставки данп.ых и сигна

-

т

fO

15

278874, 2

запроса нередачи данных, выход 35 сигнала прерываний при приеме данных, выход, 36 сигнала нрерываний на выдачу данных, первый - N-й вглходы 5 37.1 - 37.N сигналов управления выдачи даннь х, первый - N-й выходы 38.1 - 38.N установочных сигналов, первый -- М-й выходы 39, 1 - 39 ,N сигналов управления выдачи данных, выход 40 пустых слогов, выходы 41 и 42 депгифратора 26, коммутатор 43, первый N-Й выходы 44.1 - 44,N управления реверсом, первый - N-й выходы 45,.N сигналов управления записью заявок в регистр 5 запросов, первый - N-й выходы 46.1 - 46.N управления записью заявок в регистр 5 запросов, выход 47 синхронизации устройства, выход 47.1 последовательности тактовых импульсов о , выход 47.2 последовательности тактовых импульсов , первый N-й выходы 48,1 - 48.N шифратора 7, нулевой и единичный выходы 49.1 - 49.2 триггера б направления, первый - N--ii информационные входы 50.1 - 50.N регистра 5, нервы; - N--й входы 51.1- 51.N коммутатора 8, первый - N-й входы 52,1 - 52.N элемента ИЛИ 1, первый - N-Й входы 53,1 - 53.N эле- .чепта 1 ШИ 12, нервый N-й входы 54.1- 54.N адреса, первый - N-й выходы 55.1 - 55,N разрядов адреса, первый - N- -й входы 56.1 - 56,N блоков 3.1 - 3,N, первый - N-й выходы 57.1 - 57,N коммутаторов 43.1 43.N и дешифратор 25.

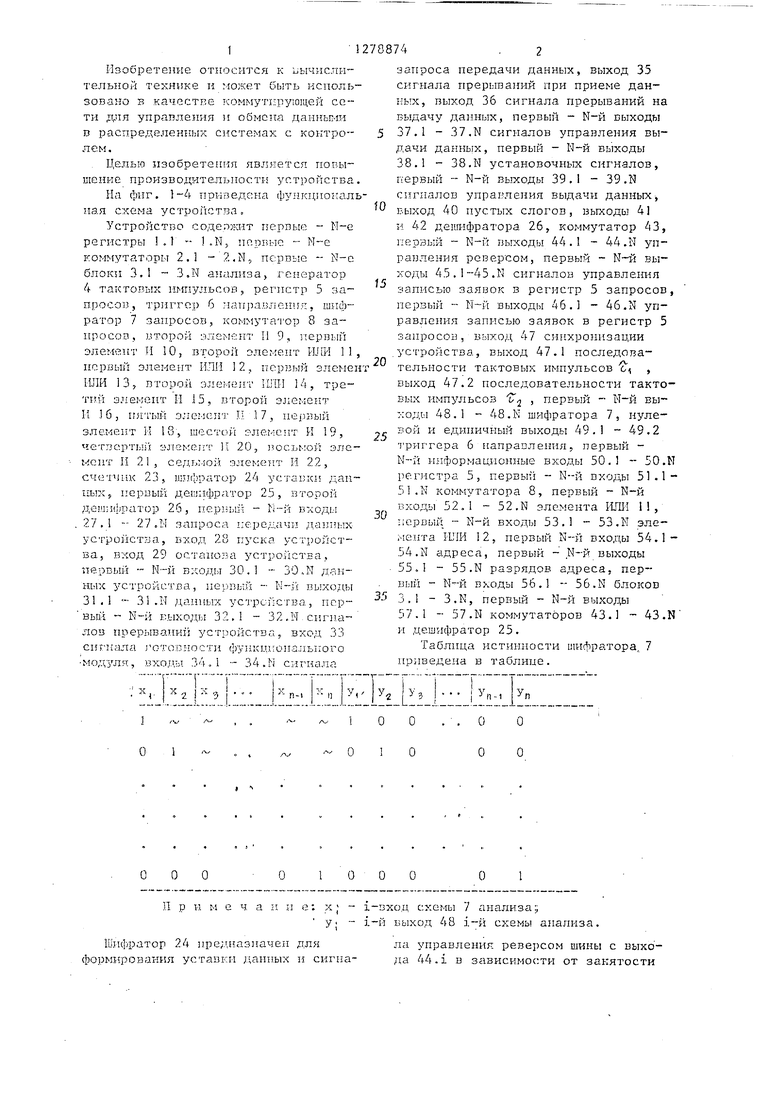

Таблица истинности шифратора, 7 приведена в таблние.

20

25

30

35

о

о

ла управления PBBGIJCOM шины с выхода 44,1 в зависимости от занятости

регистров (входы 40.i и 58.1), состояния шифратора 7 (вход 48.1) и триггера 6 нагГравления (выход 49.2),

Устройство функционирует в следующих режимах: приема данных; обмена и вьщачи данных.

Режим приема данных

В исходном состоянии регистры,

триггер и счетчики находятся в исходном (нулевом) состоянии. Цепи установки в исходное состояние на .функциональной схеме условно не показаны. Работа устройства начинается с момента прихода на вход 28 устройства сигнала пуска. На выходах 47.1 и 47.2 генератора формируются две последовательности тактовых импульсов соотве тственно , и С, .

Прием данных от функциональных модулей (ФМ) системы устройства осуществляется .по входам 30,1 - 3.0.N устройства. Перед выдачей данных ФМ посылает на вход 27.1 устройства сигнал Запрос передачи данных, по которому производится проверка занятости регистра 1. Данный сигнал с входа 34.1 блока 3,1 поступает на вход элемента И 16 и на информационный вход 50.1 регистра 5. Если регистр 1.N окажется свободным (на вход дешифратора 26 блока 3.1 поступает нулевой код), то на второй вход элемента И 16 с выхода дешифратора 26 поступает разрешающий сигнал, по которому форшфуется сигнал прерывания на выходе элемента И 16, поступающий через элемент ИЛИ 14, выход 36 на выход 32,1 устройства. Кроме того, этот сигнал прерывания с выхода 46.1 поступает на вход 53,1 элемента ИЛИ 12, далее с выхода элемента ИЛИ 12 на вход элемента И 9. Ыа выходе элемента И 9 по заднему фронту очередного тактового импульса t, формируется сигнал синхронизации регистра 5, по которому осуществляется запись сигнала Запрос передачи данных с входа 50.1 регистра 5.

Разрешающим сигналом для формирования сигнала синхронизации на выходе элемента И 9 является единичный сигнал на выходе коммутатора 8, который формируется в результате поступления на входы коммутатора единичных сигналов с нулевых выходов регистра 5 (регистр 5 находится в исходном состоянии),

После выдачи сигнала прерывания по выходу 32.1 устройства на вход

30.1 устройства от ФМ поступают данные, в которых имеется адрес ФМ, которому предназначаются данные. Адресная часть данных с входа 54.1 5 поступает на вход шифратора 24,

На вход шифратора 24 уставки с выхода 48,1 mH(J.ipaTopa 7 поступает единичный разрешающий сигнал, так

O как в регистре 5 по входу 50.1 была записана заявка на выдачу данных первым ФМ. Таким образом, в зависимости от кода адреса на выходе 44 , шифратора 24 формируется управляющий

5 сигнал реверса, который поступает на вход элементов И 22 и И 10,

При нахождении триггера 6 в нуле- вом состоянии (на выход 49,1 триггера 6 поступает единичный сигнал) ор0 ганизуется передача данных по шине - направлепие вращения против часовой стрелки +, данные последовательно передаются из регистра l.i в регистр 1,1 + 1, где 1 1,N, Если триггер

5 6 находится в единичном состоянии, то направлепие передачи против часовой стрелки данные последовательно передаются из регистра 1.1 в регистр 1.(1-).

0 С приходом очередного- тактового импульса с па вход элемента И 10 на выходе послед его формируется сигнал, поступающий на счетный вход триггера 6, который по переднему

фронту Т изменяет свое состояние. Одновременно с выдачей сигнала реверса шифратор 24 выдает код установки, который поступает на устаповоч- пый вход счетчика 23 и записывается

0 в него по заднему фронту тактового импульса с; , поступающего на второй вход элемента И 22, который формирует па своем выходе сигнал синхронизации счетчика 23.

5 После того, как триггер 6 изменил свое состояние возникает необходимость анализа состояния регистра 1,1. так как в этом случае данные с входа 30,1 должны записываться- в ре0 регистр 1,N (передача данных организуется по реверсивной шипе), Если формирование сигнала реверса не произошло, то данные должны записываться в регистр 1.1 (производится ана5 ЛИЗ регистра 1.N, передача данных организуется по шине) по управляющему сигналу с выхода 39 элемента И 19. В рассматриваемом случае сигнал реверса изменил состояние триггера 6,

т.е. переключил шину на реверсивную передачу. Поэтому нулевая адресная часть данных (регистр 1.1 находится в исходном состоянии), которая является признакам пустого регистра, с выхода 55.1 регистра 1.1 поступает на вход дешифратора 25 и формирует на его выходе 58 единичный управляющий сигнал, поступающий на вход шифратора 24 и вход элемента И 15. На другой вход элемента И 15 поступает единичный сигнал Запрос передачи данных с входа 34. На выходе элемента И 15 формируется единичный сигнал, проходящий через элемент И 17 на выход 37.1 по единичному разрешающему сигналу с выхода 49.2 триггера 6. Управляющий сигнал с выхода 37.1, поступая на управляющий вход коммутатора 2.N, разрешает прохождение данных с входа 30.1 устройства на информационный вход регистра 1.N. По заднему фронту очередного тактового импульса Z , который поступает на вход синхронизации регистра 1.N, происходит запись данных в регистр I.N.

Кроме того, управляюш,ий сигнал с выхода 37 поступает на вход коммутатора 43, по переднему фронту тактового импульса Г проходит на выход 57.1 и далее на выход 32.1 устройства. В результате чего ФМ получает уведомление о том, что запись данных в шину произведена. В этом случае ФМ снимает сигнал Запрос передачи данных на входе 27.1 и данные на вхо- де 30.1 по заднему фронту тактового импульса S l .

В следующем такте работы устройства производится вычитание единицы из счетчика 23 по заднему фронту тактового импульса С. , который поступает на счетный вход счетчика с выхода элемента И 21. Разрешающим сигналом для прохождения тактового импульса 1„ через элемент И 21 является нулевой сигнал с выхода элемента И 20, образующийся в результате записи кода уставки в счетчик 23 и поступаю- 11ЩЙ на инверсный вход элемента И 21

По очередн1)1м тактовым импульсам происходит передача данных после- довательно из i-ro в (5.-1)-й, где i 1,N регистры (направление .вращения по часовой стрелке) и одновременное вычитание единицы из счетчика 23. Передача данных и вычитание еди

5

0

5

ницы происходят до тех пор, пока данные не достигнут ФМ, которому предназначаются данные. В этом случае счетчик 23 обнуляется и с выхода 45.1 элемента И 20 на выход 51.1 коммутатора 8 поступает единичный управ- ляющIiй сигнал, который разрешает прохождение единичного сигнала с выхода 48.1 шифратора 7 на вход элемента И 9. Элемент И 9 формирует сигнал синхронизации регистра 5 по тактовому импульсу -С, и с приходом на.входы 27.1- 27.N устройства сигналов Запрос передачи данных.

Во время вычитания единицы из счетчика 23 на информационные входы регистра 5 в случайные моменты времени могут поступать запросы на передачу данных от других ФМ, но записываться в регистр 5 они будут только после обнуления счетчика 23.

Сигналы заявок на входы 27.1 - 27.N могут поступать на информационные входы регистра 5 в один и тот же момент времени и записываться в регистр 5 одновременно. В этом случае шифратор 7 выделяет наиболее приоритетный ФМ.

Прием данных от других модулей устройство осуществляет аналогично как и от первого ФМ по входу 30.1 устройства. Управление- приемом данных по входам 30.2 - 30.N устройства осуществляют соответственно 5 блоки 3.2 - 3.N анализа, которые функционируют аналогично блоку 3.К

Режим обмена и выдачи данных

В данном режиме устройство начинает функционировать после записи данных в регистры. Данные, записываемые с входов 30.1 - 30.N по очеред- ньот тактовым импульсам , последовательно передаются из регистра в регистр либо по шине, либо по реверсивной шине в зависимости от состояния триггера 6 направления передачи. В каждом такте работы устройства блоки 3.1 - 3.N осуществляют анализ адресной части данных, передаваемых по вращающейся шине. Рассмотрим выдачу данных первому ФМ, которые выдаются на выход 31.1 устройства.

Адресная часть данных с выхода 55.N регистра 1.N поступает на вход дешифратора 26. В случае циркулярной передачи данных (данные предназначаются всем модулям системы) на выходе 42 дешифратора 26 формируется

0

0

5

0

сигнал прерывания, поступающий через элемент ИПИ 13 и выход 35 на выход 32.1 устройства. Если данные предназначаются только одному ФМ, то сигнал прерывания формируется на выходе 41.1, который аналогичны - образом поступает иа выход 32.1 устройства. После вьздачи сигнала прерывания функциональный модуль, если он принял данные по выходу 31.1 устройства, выдает на вход 27.1 устройства сигнал Готово, который с входа 33.1 поступает на вход элемента И 18 и, пройдя на выход 38.1 элемента И 18, поступает на установочный вход регистра 1.N. В результате регистр 1.N устанавливается в исходное (нулевое) состояние. Разрешающим cisr- налом для формирования устанопочпого сигнала на выходе 38.1 элемента И 18 является сигнал прерывания на выходе элемента И 13. В следующем такте работы устройства нулевой код, установленный в регистре 1.N, записывается в регистр 1 .. , если передача данных организована по прямой шине. Если передача данных организована но реверсивной шине, то данные записываются

ров, синхровходы которых соединены с первым выходом генератора тактовых импульсов, группа разрядных выходов i.-го (i 1 - N) регистра соединена с вторым информационным входом (i + + )-го ком утатора, группа разрядных выходов N-ro регистра соединена с вторым информационньм йходом первого коммутатора, группы выходов разрядов данных с первого по N-й регистров являются соответственно с второго по N-й первььми выходами данпых устройства, а п каждом блоке анализа группа выходов первого дешифратора соединена с входами первого элемепта 1ШИ, выход которого соединен с первым входом первого элемеп та И, выход первого дешифратора соединен с первым входом второго элемента И, выход второго дешифратора соединен с первь м входом третьего элемента И, отличающееся тем, что, с целью повьгаения производительности, оно содержит коммутатор запросов, регистр запросов, шифратор запросов, триггер направления, два элемента 1ШИ, при этом количество блоков анализа равно N, а в кажв регистр 1.(N - 1).

После установки регистра 1 .N в дый блок анализа введены с чр.тверто- левое состояние устройство переходит о „Q восьмой элементы И, коммута- в рассмотренный ранее режим функционирования по приему данных от модулей системы.

35

Управление выдачей данных модулям по выходам 31.2 - 31.N устройства осуществляют соответственно блоки 3.2 - 3.N аналогично блоку 3.I..

Работа устройства прекращается 40 после прихода на вход 29 устройства сигнала останова, по которому генератор 4 прекращает формирование последовательностей тактовых импульсов.

45 Формула изобре тения

Устройство для обмена данными, содержащее N регистров, N коммутаторов, генератор тактовых импульсов, 50 первый и второй элементы И, блоки анализа, каждый из которых содержит два дешифратора, три элемента И и два элемента ИЛИ, причем с первого по N-й входы данных устройств соеди- 5j иены соответственно с первыми информационными входами с первого по N-й коммутаторов, выходы которых соединены соответственно с информациопнытор, счетч1И ; и ш 1фратор уставки дан- , причем третий и четвертый информационные входы 1-го коммутатора соединены соответственно с (i + 1)-м входом данных устройства и грунпой разрядных выходов (i + 1)-го регистра, третий и четвертый информационные входы N-ro коммутатора соединены соответственно с первым входом данных устройства и группой разрядных выходов первого регистра, группы входов первого и второго дешифраторов i-ro блока анализа соединены соответственно с группами выходов разрядов адреса i-ro и (i - 1)-го регистров, группы входов первого и второго дешифраторов первого блока анализа соединены соответственно с группами выходов разрядов адреса первого и N-ro регистров, вход сброса i-ro регистра соединеп с выходом первого элемента И (i + 1)--го блока анализа, при этом в каждом блоке анализа выходы первого и второго дешифраторов соединены соответственно с первым и вторым входами шифратора уставки данных, группа входов которого сое27887Д8

ми входами с первого по N-й регистO

5

0

5

ров, синхровходы которых соединены с первым выходом генератора тактовых импульсов, группа разрядных выходов i.-го (i 1 - N) регистра соединена с вторым информационным входом (i + + )-го ком утатора, группа разрядных выходов N-ro регистра соединена с вторым информационньм йходом первого коммутатора, группы выходов разрядов данных с первого по N-й регистров являются соответственно с второго по N-й первььми выходами дан пых устройства, а п каждом блоке анализа группа выходов первого дешифратора соединена с входами первого элемепта 1ШИ, выход которого соединен с первым входом первого элемепта И, выход первого дешифратора соединен с первым входом второго элемента И, выход второго дешифратора соединен с первь м входом третьего элемента И, отличающееся тем, что, с целью повьгаения производительности, оно содержит коммутатор запросов, регистр запросов, шифратор запросов, триггер направления, два элемента 1ШИ, при этом количество блоков анализа равно N, а в каж дый блок анализа введены с чр.тверто- о „Q восьмой элементы И, коммута-

дый блок анализа введены с чр.тверто- о „Q восьмой элементы И, коммута-

тор, счетч1И ; и ш 1фратор уставки дан- , причем третий и четвертый информационные входы 1-го коммутатора соединены соответственно с (i + 1)-м входом данных устройства и грунпой разрядных выходов (i + 1)-го регистра, третий и четвертый информационные входы N-ro коммутатора соединены соответственно с первым входом данны устройства и группой разрядных выходов первого регистра, группы входов первого и второго дешифраторов i-ro блока анализа соединены соответственно с группами выходов разрядов адреса i-ro и (i - 1)-го регистров, группы входов первого и второго дешифраторов первого блока анализа соединены соответственно с группами выходов разрядов адреса первого и N-ro регистров, вход сброса i-ro регистра соединеп с выходом первого элемента И (i + 1)--го блока анализа, при этом в каждом блоке анализа выходы первого и второго дешифраторов соединены соответственно с первым и вторым входами шифратора уставки данных, группа входов которого соединена с соответствующим входом данных устройства, а группа выходов - с группой установоч}1ых входов счетчика, группа инверсных разрядных выходов которого соединена с группой входов четвертого элемента И, выход третьего элемента И соединен с пер- вьм входом пятого элемента И, выход которого соединен с первым йходом коммутатора, второй вход которого соединен с выходом шестого элемента И, первый вход которого и первый вход второго элемента ИЛИ соединены с выходом второго элемента И, второй вход второго элемента I-iJlH соединен с вькодом третьего элемента И, выход шифратора уставки данных соедине с первым входом седьмого элемента И, выход которого соединен с синхровхо- 7ДОМ счетчика, в)1ход четвертого элемента И соединен с инверсным входом восьмого элемента И, выход которого соединен со счетным входом счетчика, i-й установочный вход регистра запросов, вторые входы первого, второго и третьего элементов И блока анализа образуют i-й вход запроса передачи данных устройства, первый выход генератора тактовых импульсов соединен с вторыми входами седьмых, восьмых элементов И и третьими входами коммутаторов.всех блоков анализа и первым входом первого элемента И, выход которого соединен со счетным входом триггера направления, единичный которого соединен с третьими входами шифраторов уст.авки данных и вторыми входами пятых: элементов И всех блоков анализа и первыми управляющими входами С первого по N-й коммутаторов, а нулевой выход соединен с вторыми входами шестых элементов И всех блоков анализа и

5

вторыми управляющими входами с первого по N-Й коммутаторов, группа выходов шифратора запросов соединена с первой группой входов коммутатора запросов и четвертьдми входами шифраторов уставки данных.соответствующих блоков анализа, выходы вторых элементов ИЛИ всех блоков анализа соединены .с входами первого элемента ИЛИ, выход которого соединен с первым входом второго элемента И, второй и третий входы и выход которого соединены соответственно с вторым выходом .генератора тактовых импульсов, выходом коммутатора запросов и ситсровходом регистра запросов, выходы первого и второго элементов 1-ШИ и коммутатора i-ro блока анализа образуют выход прерывания устройства, выходы четвертых элементов и всех блоков анализа соединены с второй группой входов коммутатора запросов, третья группа входов которого соединена с группой инверсных разрядных выходов регистра запросов, группа прямых разрядных выходов которого соединена с группой входов шифратора запросов, второй вход первого элемента И соединен с выходом второго элемента ИЛИ, входы которого соединены с выходами шифраторов уставки данных всех блоков анализа, первьш и второй выходы генератора тактовых импульсов образуют 5 С1 нхровыход устройства, третий управляющий вход i-ro коммутатора соединен с выходом пятого элемента И . Ci + 1)-го блока анализа, третий управляющий вход N-ro коммутатора соединен с выходом пятого элемента И первого блока анализа, четвертый управляющий вход i-ro коммутатора соединен с выходом шестого элемента И i-ro блока анализа.

0

5

0

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство для обмена данными | 1984 |

|

SU1196885A1 |

| Программируемый управляющий модуль | 1989 |

|

SU1649506A1 |

| Устройство для контроля распределения ресурсов | 1985 |

|

SU1297051A1 |

| Многоканальная микропрограммная управляющая система | 1985 |

|

SU1280628A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство для управления обменом управляющей информацией в распределенной системе | 1986 |

|

SU1325477A1 |

| Устройство для контроля распределения ресурсов | 1989 |

|

SU1702372A1 |

| Устройство для обслуживания запросов | 1988 |

|

SU1522205A1 |

| Многоканальное устройство управления вводом информации в микроЭВМ | 1984 |

|

SU1234844A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве коммутирующей сети для управления и обмена данными в распределенных системах с контролем. Целью изобретения является по- вьгаение производительности. Устройство содеряшт N регистров, N коммутаторов , Ы блоков анализа, генератор тактовых импульсов, регистр запросов, триггер направления, шифратор запросов, коммутатор запросов, счетчик, шифратор установки данных, два дешифратора, элементы И, I-LTH. Информация от источников поступает на входы коммутаторов, управляемых блоками анализа. С выходов коммутаторов информация поступает на соответствующие регистры и последующие коммутаторы. Т.о. информация от источника движется через последовательно соединенные ко1-1мутаторы и регистры к прием1шку. Повышение производитель™ цости достигается за счет возможности изменения направления движения информации в случае, если источник информации подключен к коммутатору, имеющему номер больший, чем номер коммутатора, к которому подключен приемник информации. 4 ил., 1 табл. С ю .«чЗ 00 «,.%.

т

3Si5 jyiTHO

3

4J

e

ь

5J

1Ш

J4.J

5W

ж

Ш ЖлГ

Us.

-v

ТЩ

JA/

Ш

Ш П

SSJI/

| ЗИ, ВТ, 1982, № 35, с | |||

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для обмена данными | 1984 |

|

SU1196885A1 |

Авторы

Даты

1986-12-23—Публикация

1984-09-17—Подача