ментов И, выход которого соединен с .первым входом четвертого элемента И, вторые входы первого и четвертого элементов И подключены к тактовому входу устройства, вход второго распределителя импульсов соединен с выходом четвертого элемента И первые выходы этого распределителя подключены к соответствующим первым входам второго мультиплексора, вторые входы которого соединены с выходами соответствующих регистров второго блока, а выход этого мультиплексора подключен к второму входу схемы сравнения, выход которой соединен с входом установки триггера совпадения, первый, второй и третий, входы пятого элемента И подключены к выходам соответственно первого и второго управляющих мультиплексоров и триггера ана.лиза, а выход этого элемента И соединен с входом установки триггера тупика, инверсный выход триггера совпадения под ключен к первому входу шестого элемента И, выход которого соединен с входом установки второго триггера управления и вторыми входами блоков элементов И первой группы, прямой и инверсный выходы второго триггера управления подключены к первым входам соответственно седьмого и восьмого элементов И, вторые входы которых соединены с вторым выходом первого распределителя импульсов, выход седь:мого.элемента И подключен к входу сброса второго триггера управления и третьему входу элемента ИЛИ, а выход восьмого элемента И соединен с входом установки триггера анализа, вход сброса которого подключен к управляющему входу устройства, а выход - к входу сброса триггера режима, причем второй выход второго распределителя импульсов соединен с вторым . входом шестого элемента И и четвертым входом элемента ИЛИ.

2. Устройство по П.1, от л ичающееся тем, что распределитель импульсов содержит счетчик и дешифратор, вход данных которого подключен к выходу счетчика, управляющий вход дешифратора и вход счетчика соединены с входом распределителя, а выходы дешифратора подключены к первым и вторым выходам распределителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля распределения ресурсов | 1986 |

|

SU1341642A1 |

| КОНТРОЛЛЕР РАСПРЕДЕЛЕНИЯ РЕСУРСОВ | 2013 |

|

RU2526762C1 |

| Устройство для контроля распределения ресурсов | 1984 |

|

SU1215112A1 |

| Устройство для контроля распределения ресурсов | 1985 |

|

SU1297051A1 |

| Устройство для контроля распределения ресурсов в вычислительной системе | 1985 |

|

SU1269138A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для моделирования дискретных систем | 1985 |

|

SU1295411A1 |

| Устройство для контроля распределения ресурсов | 1989 |

|

SU1702372A1 |

| Устройство для индикации | 1990 |

|

SU1795511A1 |

| Устройство для контроля распределения ресурсов в вычислительной системе | 1985 |

|

SU1312583A1 |

1o УСТРОЙСТВО КОНТРОЛЯ, coдёрж нцее два блока ре гистров, три группы блоков элемеитов И, триггер режима, элемент ИШ, два мультиплексора и триггё|э тупика, выход которого соединен с выходом у&тройства, выходы блоков элементов И первой и второй групп подключены еортветственнО К первым .входам установки и входам данных соответствующих р ёгистров первого блока, а выходы блоков элементов И третьей группы соединены с входами данных соответствующих регистров второго блока, первые входы блоков элементов И второй и третьей групп подключены соответстве «но к первому и второму входам данных устройства, а вторые входы этих блоков элементов И соединены с инверсным выходом триггера режима, вход установки которого подключен к управляю|щему входу устройства, первому входу элемента ИЛИ и входу сброса триггера тупика, пер-выё входы первого и второго мультиплексоров соединены с выходами соот.ветствующих регистров первого и второго блоков , отличающееся .тем, что, с целью расширения функцио-. наЛьных возможностей, оно содержит два упр авляющих мул ь ти пле ксо ра, два распределителя кмпульсов, два Tj irre ра управления, триггер совпадения, Триггер анализа, элемент ИЛИ-НЕ и восемь элементов И, при этом входы данных первого и второго управляющих Мультиплексоров подключены к выходам соответствукщйх регистров первого и второго блоков, управляющие входы эТих мультиплексоров соединены с инверсным выходом триггера режима, первые выходы первого и второго управляющих мультиплексоров подключены .соответственно к входам установки регистров второго блока и вторым входам установки регистров первого блока, вход установки первого триггера управления соединен с выходом элемента .ИЛИ, выход этого триггера подключен к первому входу первого элемента И, выход которого соединен с входом пер-, вого. распределителя импульсов, входами сброса первого триггера управления и триггера совпадения, первые выходы лервого распределителя имсл nyjibcoB подключены к первым входам 00 соответствующих блоков элементов И с первой группы, соответствующим вхоО1 дам элемента ИЛИ-Н и соответствующим первым входам первого мультиплексора, вторые входа которого соединены с выходами соответствующих регистров первого блока, выход первого мультиплексора подключен к первому входу схемы сравнения и первым входам второго элемента И, выход которого соединен с вторым входом элемента ИЛИ и первым входом третьего элемента И, выход элемента ИЛИ-НЕ подключен к ВТОРЫМ входам второго и третьего эле

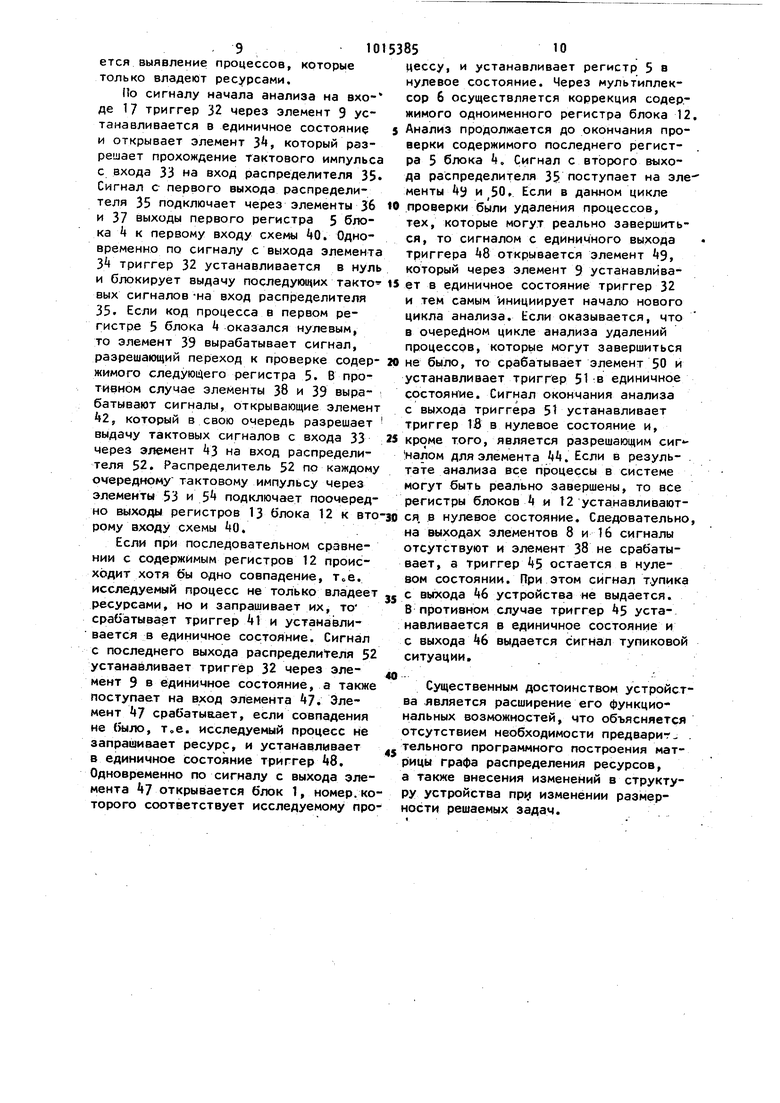

Изобретение относится к вычислительной технике и может бь1ть использовано в современных высокопроизводительных мультипрограммных вычислитель ных системах. Известно устройство управления, содержащее регистры и дешифраторы Г. Недостатком этого устройства является невозможность контроля распределения ресурсов в вычислительной сиётеме. Йаиболее близким к предлагаемому является устройство для контроля распределения ресурсов в вычислительной системе содержащее триггер режима, триггер фиксации тупика, четыре группы -элементов И, две группы элементов ИЛИ, первый элемент ИЛИ и два блока регистров, причем единичный вход триг гера режима подключен к входу пуска устройства, нулевой вход триггера режима подк/йочен к первому входу первой группы элементов И, второй вход первой группы элементов И подключён к первому информационному входу устройства, а выходы первой- группы элементов И подключены к информационным входам первого блока регистров, выход которого подключен к первым выходам элементов И второй группы,: выходы кьторых подключены к входам элементов ИЛИ первой группы, а выходы элементов И третьей группы соединены с первыми входами элементов ИЛИ второй группы, выходы четвертой группы эле- ментов И подключены к первой группе управляющих входов второго блока регистров. Известное устройство предназначено для контроля распределения pecyg-. сов в вычислительной системе на осно3ве выявления тупиковых ситуаций. Тупиковая ситуация (клинч) возникает вследствие перехода в состояние ожидания освобождения ресурсов всех про цессов, функционирующих в вычислительной системе (ВС). В известном объекте производится обнаружение тупиков при распределении ресурсов, в качестве которых могут в принципе в ступать компоненты программных или аппаратных средств ВС, предоставляемые ВС для выполнения вычислительных процессов f 2 1. Ограниченные функциональные возможности из вестного устройства обусловлены тем, что для его работы необходимо построение матрицы, описывающей граф распределения ресурсов который получают вне устройства, например программными средствами. При этом используется первичная информация о владельцах ресурсов и запросах на них. Необходимость предварительно го построения матрицы приводит к существенному снижению быстродействия ВС. Кроме того, сужение функциональных возможностей прототипа обусловле но возможностью решения задач только для фиксированного числа процессов а системе. Изменение числа процессов приводит к-необходимости изменения связей между элеменхами устройстваФ .Это свидетельствует об отсутствии универсальности уст|р1ойства. Таким образом, перечисленные недостатки снижают экономичность и ухудшают фун циональные возможности устройства. . Цель изобретения - расширение фун циональных возможностей устройства. С этой целью в устройство контроля, содержащее два блока регистров, три группы блоков элементов И, триггер режима, элемент ИЛИ, два мультиплексора и триггер тупика, выход ко торого соединен с выходом устройства выходы блоков элементов И первой и второй групп подключены соответствен но к первым входам установки и входа данных соответствующих регистров пер вого блока, а выходы блоков элементов И третьей группы соединены с вхо дами данных соответствующих регистров второго блока, nepebie входы блоков элементов И второй и третьей групп подключены соответственно к первому и второму входам данных устройства , а вторые входы этих блоков . элементов И соединены с инверсным 385 выходом триггера режима, вход установки которого подключен к управляющему входу устройства, первому входу элемента ИЛИ и входу сброса триггера тупика, первые входы первого и второго мультиплексоров соединены с выходами соответствующих регистров первого и второго блока, введены два управляющих мультиплексора, два распределителя импульсов, два триггера управления, триггер совпадения, триг-; анализа, элемент ИЛИ-НЕ и восемь элементов И, при этом входы данных первого и второго управляющих мультиплексоров подключены к выходам соответствующих регистров первого и второго блоков, управляющие входы этих мультиплексоров соединены с инверсным выходом триггера режима, первые выходы первого и второго управляющих мультиялексоров подключены соответственно к входам установки регистров второго блока и вторым входам установки регистров первого блока, вход ус-, тановки первого триггера управления соединен с выходом элемента ИЛИ, выход этого триггера подключен к первому входу первого элемента И, выход которого соединен с входом первого рас-, пределителя импульсов, входами сброса первого триггера управления и триггера совпадения, первые выходы первого распределителя импульсов подключены к первым входам соответствующих блоков элементов И первой группы, соответствующим входам элемента ИЛИ-НЕ и соответствующим первым входам первого мультиплексора, вторые входы которого соединены с выходами соответствующих регистров первого блока, выход первого мультиплексора подключен к лервому входу сравнения и первым входам второго элемента И, выход которого соединен с вто|жм входом элемента ИЛИ и первым входом третьего элемента И, выход элемента. ИЛИ-НЕ подключен к вторым входам второго и третьего элементов И, выход которого соединен с первым входом четвертого элемента И, вторые входы первого и четвертого элементов И подключены к тактовому входу устройства, вход второго распределителя импульсов соединен с выходом четвертого элемента И, первые выходы этого распределителя подключены к соответствующим первым входам второго мультиплексора, вторые входы которого соединены с выхоами соответствующих регистров втооого блока, а выход этбго мультиплексора подключен к второму входу схемы сравнения, выход которой соединен с входом установки триггера фвпадения. первый, второй и третий вх(|ды пятого элемента И подключены к выходам соответственно первого и второго управляющих мультиплексоров и триггера ана лиза, а выход этого элемента И соединен с входом установки триггера tyпика, инверсный выход триггера совладения подключен к первому входу шестого элемента И, выход которого соединен с входом установки второго триггера управления и вторыми входами блоков элементов И первой группы, прямой и инверсный выходы второго триггера управления подключены к первым входам соответственно седьмого и восьмого элементов И, вторые входы которых сое динены с вторым выходом первого распределитедя импульсов, выход седьмого элемента И подключен к входу сброса второго триггера управления и третьему входу элемента ИЛИ, а выход .восьмого элемента И соединен с входом установки триггера анализа, вход сброса которого подключен к управляющему входу устройства, а выход - к входу сброса триггера режима, причем зо второи выход второго распределителя импульсов соединен с вторым входом шестого элемента И и четвертым входом элемента ИЛИ. Кроме того, распределитель импуль- jj сов содержит счетчик и дешифратрр, вход данных которого подключен к выходу счетчикаi управляющий вход дешифратора и вход счетчика соединены с входом распределителя, а выходы дешифратора подключены к первым и вторым выходам распределителя. На фиг. 1 и 2 изображена функциональная схема предлагаемого устройства; на фиг. 3 функциональная схема первого (второго) распределителя импульсов; на фиг, k - пример временной диаграммы работы устройства. Устройство содержит (фиг. 1) первую группу блоков 1 элементов И, пёрвый информационный вход (вход данных) 2 устройства соединен с первыми входами блоков 3 элементов И второй груп пы. Первый блок 4 регистров содержит

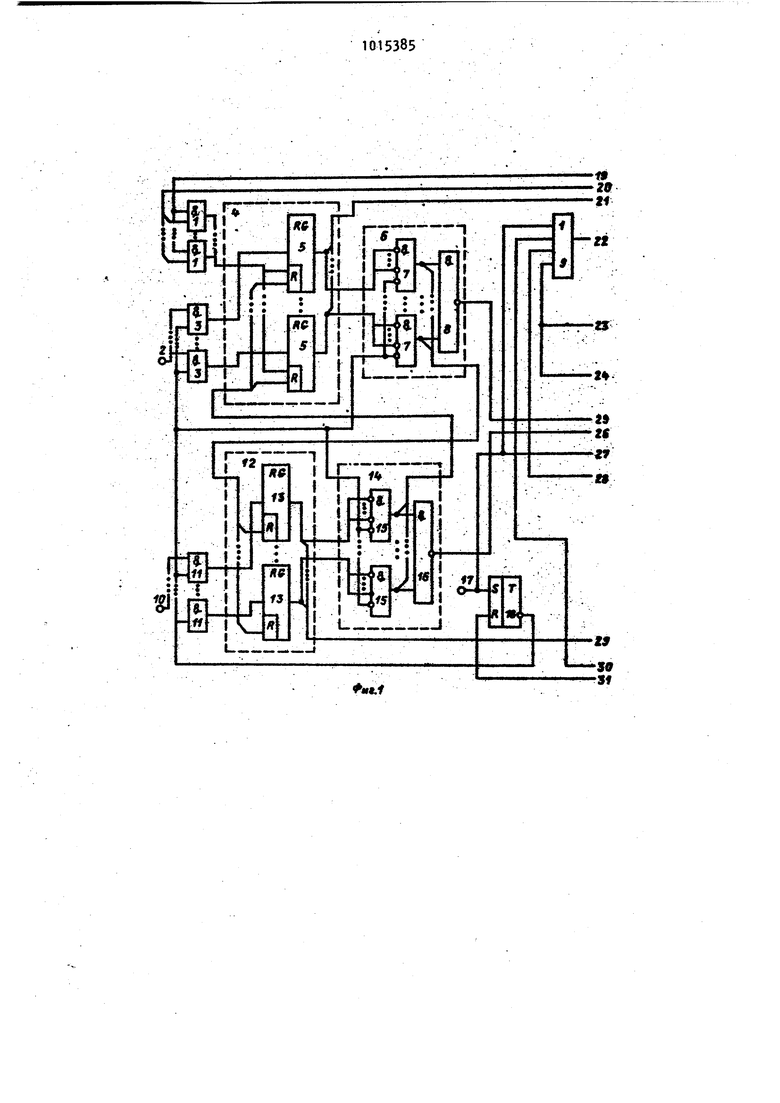

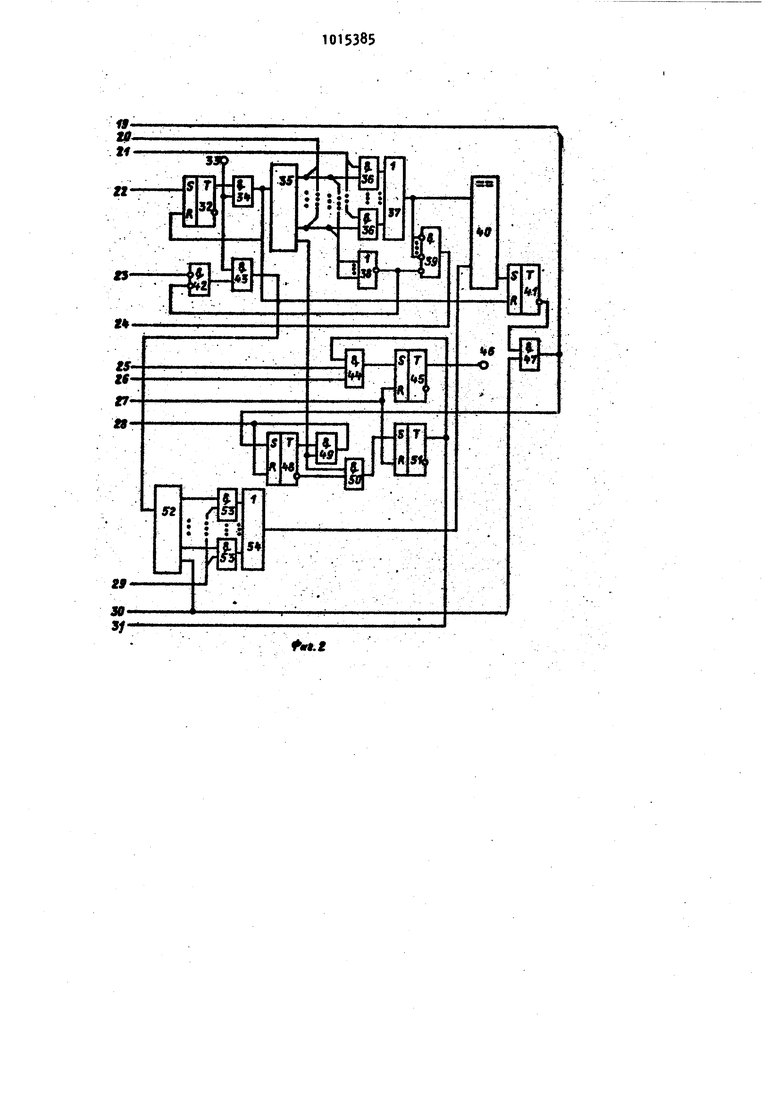

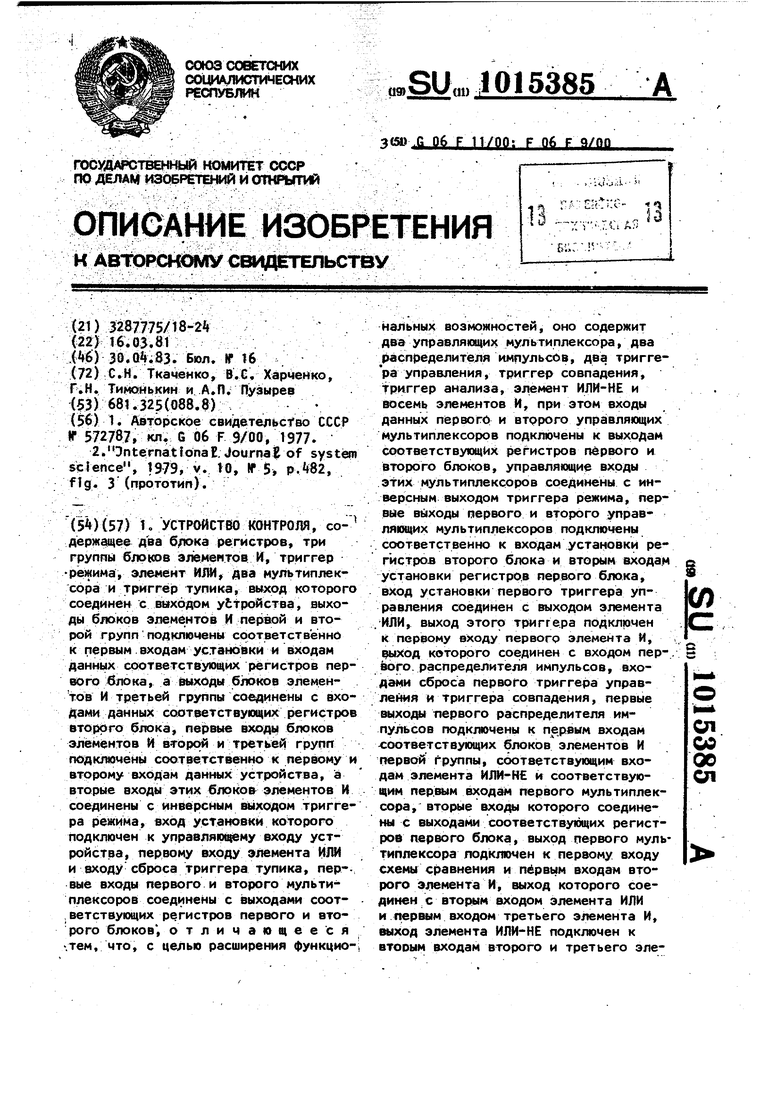

регистры 5, входы данных которых соединены с выходами соответствующих блоков 3 а первые установочные входч регистров 5 подключены к выходам соответствующих блоков I. Первый управляюПервые выходы распределителя 35 подключены к вторым входам блоков 1, первым входам элементов 36 и входам элемента 38. Второй выход распределителя 35 соединен с первыми входами щий мультиплексор 6 содержит элементы И и элемент И-НЕ, первые входы элементов И 7 соединены с выходами соответствующих регистров 5| а выходы с .ходами этемента И-НЕ 8. Устройство содержит та(е элемент ИЛИ 9. Второй информационный вход 10 (вход данных) устройства подключен к первым входам блоков 11 элементов И третьей группы. Второй блок 12 регистров содержит регистры 13, входы данных которых соединены с выходами соответствующих блоков 11, а установочные входы подключены к выходам соответствующих элементов 7. Второй управляющий мультиплексор Ц содержит элементы И 15 и элемент И-НЕ 16. Первые входы элементов 15 соединены с выходами соответствующих регистров 13, а выходы .подключены к соответствующим входам элемента 1б и вторым установочным входам регистров 5. Управляющий вход 17 устройства соединен с установочным входом триггера 18 режима, инверсный выход которого подключен к вторым входам блоков 3 . Позиционные обозначения (входы и выходы) 19-31 использованы для обеспечения однозначности перехода с фиг. 1 на Фиг. 2. Устройство содержит (фиг. 2) перт вый триггер 32 управления, установочный вход которого соединен с выходом элемента ИЛИ 9. Тактовый вход 33 устройства грдключен к первому входу первого элемента И 3, второй вход которого соединен с выходом триггера 32, а выход - с входом первого распределителя 35 импульсов.. Устройство содержит также первый мультиплексор, образованный элементами И 36 и элементом ИЛИ 37, элемент ИЛИ-НЕ 38, второй элемент 14 39 схему kO сравнения, триггер jl совпадения, третий элемент И А2, четвертый элемент И 43, пятый элемент И tk, триггер kS тупика, выход которого соединен с выходом б устройства, шестой элемент И 7, второй триггер 48 управления, седьмой элемент И Э, восьмой элемент И 50, триггер 51 анализа, второй распределитель 52 импульсов и второй мультиплексор, образованный элементами И 53 и элементом ИЛИ элементов kS и 50, вторые входы элементов 36 подключены к выходам соответствующих регистров 5, а выходы со единены с входами элемента 37. Выход элемента 37 подключен к первым входаи элемента 39 и схемы «О, выход элемента 38,соединен с втрым входом элемента 39 и первым входом элемента k2; а выход элемента 39 подключен к второму входу элемента Л2 и первому входу элемента 9. Входы элемента «3 соединены с входом 33 устройства и вы ходом элемента 2, а его выход подключен .к входу распределителя 52, Второй вход схекнэ( kO соединен с выходом элемента 5, а выход - с установочным входом триггера ll о Вхбд сброса триггера подключен к вы ходу. элемента 3 а инверсный выход к первому входу элемента 47 Выход элемента 7 средйнен,с установочным входом Триггера k8 и вторыми входами блоков 1. Первые выходы распределителя 52 подключены к первым входам элементов 53 вторые входы которых соединены с выходами соответствующих регистров 13. Второй выход распределителя 52 подключен к второму входу элемента 7. и второму входу элемента 9. Вторые входы элементов (9 и 50 соединены соответственно с прямым и инверсным -выхадами триггера 8, вход . сброса которого гюдкпючен к выходу .элемента k3 и третьему входу элемента 9. Четвертый вход элемента 9 и вхо ды сброса триггеров AS и 51 соедин гны с входом 17 устройства. Установочнг б ,входы триггеров 5 и 51 подключены к выходам соответственно элементов 4 и 50, Выход триггера 51 соединен с входом сброса триггера .18 и первым ;входом элемента 4, второй и третий входы которого подключены к выходам элементов 8 и 16. Распределители 35 и 5 содержат последовательно соединенные счетчик -55 и дешифратор 56 (фиг. 3). .На фиг. f приведен пример временной диаграммы работы Устройства для случая формирования первого и второго выходных сигналов на выходе распределителя которым осуществляется выбор первого и второго регистров в блоке k: На этом чертеже использованы следующие условные обозначения: а .вход тактовых импульсов 33, б - выход :элемента 9 в - единичный выход триггеой 32, г - выход элемента З, Д Ш85 первый выход распределителя 35i второй выход распределителя 35; 1,2,...,n,n+f, - номера тактовых ямпульсов в случае, если устройство работает с п ресурсами. Формирование .третьего и последующих импульсов на выходах распределителя 35 осуществляется аналогично. Устройство работает следующим образом. В исходном состоянии все триггеры находятся в нулевом состоянии. Единичный сигнал с нулевого выхода триггера 18 разрешает прием информации через элементы 11 и 3 в регистры 13 и 5, а также запрещает прием информации Элементами 7 и 15 мультиплексоров 6 и Ik, т.е. запрещается, взаимная установка в .нулевое состояние регистров 5 и 13 блоков 4 и 12. В каждый регистр 5 (13) блока k (12)заносится код номера процесса, который владеет этим ресурсом. Информация в регистры поступает с входов 2 и 10 устройства по командам операционной системы ВС. По сигналу пуска (начало анализа), п6ступакадему на вход 17 устройства триггера 18 устанавливается в единичное состояние. При этом блокируется прием информации в регистры блоков 4 и 12. С помощью мультиплексоров 6 и 14 , устанавливаются в нулевое состояние те регистры 13 блока 12, которые хранят коды номёрюв процессов,запраши- . 1вающих свободные ресурсы.Для таких ресурсов соответствующие регистры 5 в , блоке k хранят нулевой код. Кроме то-. го, происходит установка в нулевое состояние тех регистров 5 блока 4, которые хранят коды номеров процессор, владеющих ресурсами, запросы на которые отсутствуют. Для таких ресурсов .соответствующий регистр 13/ в блоке 12 хранит нулевой код. Сущность этих операций сводится к удалению из дальнейшего рассмотрения процессов, которые заведомо могут быть завершены ивследствие этого не приведут к тупику. ... ,„ . Далее производится переход к выявлению процессов, которые являются только владельцами некоторых ресурсов, а сами дополнительно никакие другие ресурсы не запрашивают. Если некоторый процесс является только владельцем ресурса, то его номер не должен ыть записан ни в одном из регистров 13. На проверке этого факта основыва,9101 ется выявление процессов, которые только владеют ресурсами. По сигналу начала анализа на вхо- де 17 триггер 32 через элемент 9 устанавливается в единичное состояние и открывает элемент 3 который разрешает прохождение тактового импульса с входа 33 на вход распределителя 35. Сигнал с первого выхода распределителя 35 подключает через элементы 36 и 37 выходы первого регистра 5 блока k к первому входу схемы 0. Одновременно по сигналу с выхода элемента 3 триггер 32 устанавливается в нуль и блокирует выдачу последующих такто вых сигналов-на вход распределителя 35. Если код процесса в первом регистре 5 блока 4 оказался нулевым, то элемент 39 вырабатывает сигнал, разрегиакиций переход к проверке содержимого следую111его регистра 5. В протйеном случае элементы 38 и 39 вырабатывают сигналы, открывающие элемент ifZ, который в свою очередь разрешает выдачу тактовых сигналов с входа 33 через элемент k3 на вход распредели теля 52. Распределитель 52 по каждому очередному тактовому импульсу через элементы 53 и 5 подключает поочередно выходы регистров 13 блока 12 к второму входу схемы 0. Если при последовательном срэвнении с содержимым регистров 12 происходит хотя бы одно совпадение, т.е. исследуемый процесс не только владеет ресурсами, но и запрашивает их, то срабатывзет триггер Л1 и устанавливается в единичное состояние. Сигнал с последнего выхода распределителя 52 устанавливает триггер 32 через элемент 9 в единичное состояние, а также поступает на вход элемента 47. Элемент 47 срабатыаает, если совпадения не (ыло, т.е. исследуемый процесс не запрашивает ресурс, и устанавливает в единичное состояние триггер 48. Одновременно по сигналу с выхода элемента 47 открывается блок 1, номер.которого соответствует исследуемому про85 0цессу, и устанавливает регистр 5 в нулевое состояние. Через мультиплексор б осуществляется коррекция содержимого одноименного регистра блока 12. Анализ продолжается до окончания проверки содержимого последнего регист- . ра 5 блока Ц, Сигнал с второго выхода распределителя 35 поступает на эле менты ty Если в данном цикле проверки были удаления процессов, тех, которые могут реально завершиться, то сигналом с единичного выхода триггера 8 открывается элемент «9, который через элемент 9 устанавливает в единичное состояние триггер 32 и тем самым инициирует начало нового цикла анализа. Если оказывается, что в очередном цикле анализа удалений процессов которые могут завершиться не было, то срабатывает элемент 50 и устанавливает триггер 51 в единичное состояние. Сигнал окончания анализа с выхода триггера 51 устанавливает триггер IS в нулевое состояние и, кроме того, является разрешающим сигналом для элемента if4. Если в результате анализа все процессы в системе могут быть реально завершены, то все регистры блоков и 12 устанавливаются. в нулевое состояние. Следовательно, на выходах элементов 8 и 16 сигналы отсутствуют и элемент 38 не срабатывает, а триггер 45 остается в нулевом состоянии. При этом сигнал тупика с выхода 46 устройства не выдается, В противном случае триггер 5 устанавливается в единичное состояние и с выхода 46 выдается сигнал тупиковой ситуации, Существенным достоинством устройства является расширение его функциональных возможностей, что объясняется отсутствием необходимости предварит . тельного программного построения матрицы графа распределения ресурсов, а также внесения изменений в структуру устройства пру изменении размернести решаемых задач.

Авторы

Даты

1983-04-30—Публикация

1981-03-16—Подача