Изобретение относится к вычислительной технике и предназначено для построения быстродействующих матричных арифметических устройств. Цель изобретения - упрощение устройства для вычисления симметричес- -ких булевых функций о

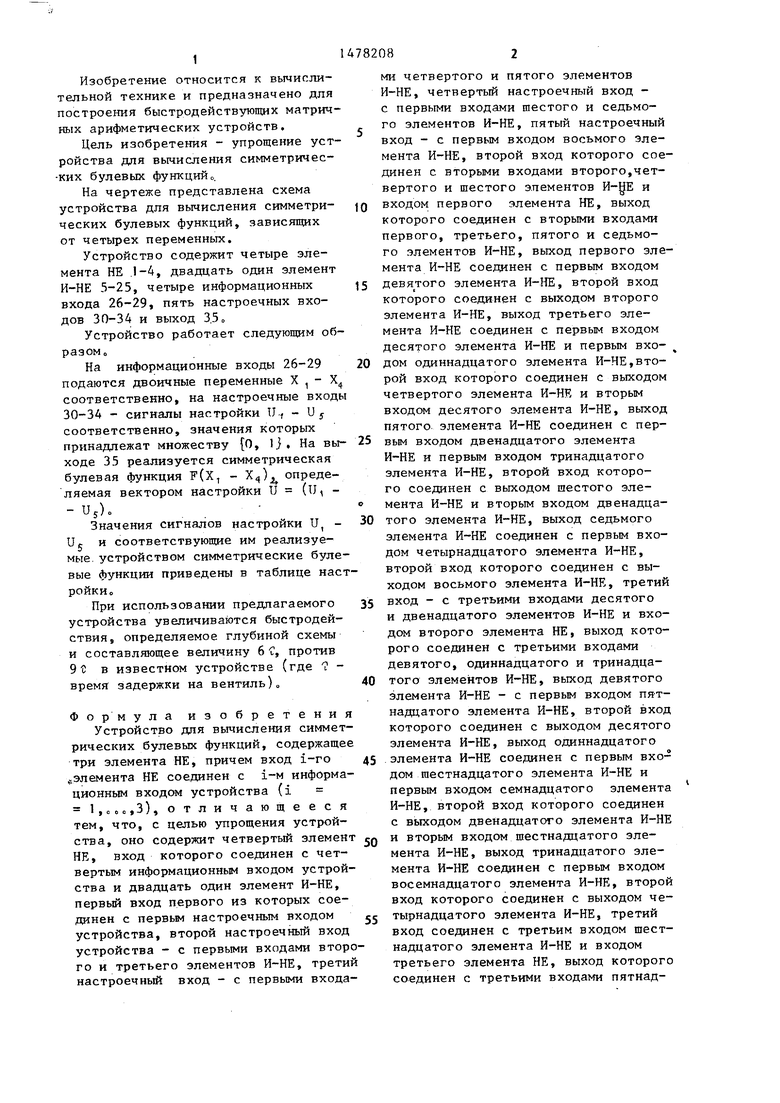

На чертеже представлена схема устройства для вычисления симметри- ческих булевых функций, зависящих от четырех переменных.

Устройство содержит четыре элемента НЕ 1-4, двадцать один элемент И-НЕ 5-25, четыре информационных входа 26-29, пять настроечных входов 30-34 и выход 35

Устройство работает следующим образом.

На информационные входы 26-29 подаются двоичные переменные X 1 - Х4 соответственно, на настроечные входы 30-34 - сигналы настройки U, - 1) 5 соответственно, значения которых принадлежат множеству {О, 1), На вы- ходе 35 реализуется симметрическая булевая функция F(Xt - Х,,) определяемая вектором настройки U (II, - и5К

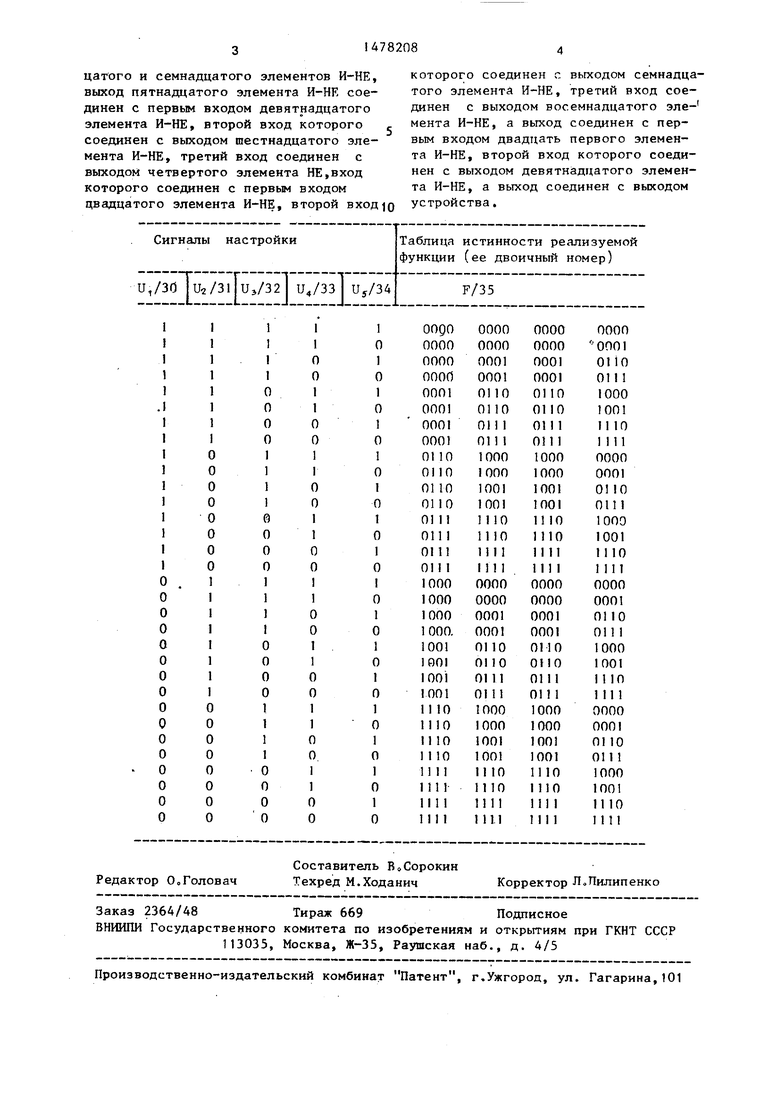

Значения сигналов настройки U, - Uс и соответствующие им реализуемые устройством симметрические буле- вые функции приведены в таблице настройки

При использовании предлагаемого устройства увеличиваются быстродействия, определяемое глубиной схемы и составляющее величину 6 С, против 9Ъ в известном устройстве (где - время задержки на вентиль)0

Формула изобретения Устройство для вычисления симметрических булевых функций, содержащее три элемента НЕ, причем вход 1-го элемента НЕ соединен с i-м информационным входом устройства (i 1,о,о,3), отличающееся тем, что, с целью упрощения устройства, оно содержит четвертый элемент НЕ, вход которого соединен с четвертым информационным входом устройства и двадцать один элемент И-НЕ, первый вход первого из которых соединен с первым настроечным входом устройства, второй настроечный вход устройства - с первыми входами второго и третьего элементов И-НЕ, третий настроечный вход - с первыми входами четвертого и пятого элементов И-НЕ, четвертый настроечный вход - с первыми входами шестого и седьмого элементов И-НЕ, пятый настроечный вход - с первым входом восьмого элемента И-НЕ, второй вход которого соединен с вторыми входами второго,четвертого и шестого элементов И-НЕ и входом первого элемента НЕ, выход которого соединен с вторыми входами первого, третьего, пятого и седьмого элементов И-НЕ, выход первого элемента И-НЕ соединен с первым входом девятого элемента И-НЕ, второй вход которого соединен с выходом второго элемента И-НЕ, выход третьего элемента И-НЕ соединен с первым входом десятого элемента И-НЕ и первым входом одиннадцатого элемента И-ЧЕ,второй вход которого соединен с выходом четвертого элемента И-НЕ и вторым входом десятого элемента И-НЕ, выход пятого элемента И-НЕ соединен с первым входом двенадцатого элемента И-НЕ и первым входом тринадцатого элемента И-НЕ, второй вход которого соединен с выходом шестого элемента И-НЕ и вторым входом двенадцатого элемента И-НЕ, выход седьмого элемента И-НЕ соединен с первым входом четырнадцатого элемента И-НЕ, второй вход которого соединен с выходом восьмого элемента И-НЕ, третий вход - с третьими входами десятого и двенадцатого элементов И-НЕ и входом второго элемента НЕ, выход которого соединен с третьими входами девятого, одиннадцатого и тринадцатого элементов И-НЕ, выход девятого элемента И-НЕ - с первым входом пятнадцатого элемента И-НЕ, второй вход которого соединен с выходом десятого элемента И-НЕ, выход одиннадцатого элемента И-НЕ соединен с первым входом шестнадцатого элемента И-НЕ и первым входом семнадцатого элемента И-НЕ, второй вход которого соединен с выходом двенадцатого элемента И-НЕ и вторым входом шестнадцатого элемента И-НЕ, выход тринадцатого элемента И-НЕ соединен с первым входом восемнадцатого элемента И-НЕ, второй вход которого соединен с выходом четырнадцатого элемента И-НЕ, третий вход соединен с третьим входом шестнадцатого элемента И-НЕ и входом третьего элемента НЕ, выход которого соединен с третьими входами пятнадцатого и семнадцатого элементов И-НЕ, выход пятнадцатого элемента И-НЕ соединен с первым входом девятнадцатого элемента И-НЕ, второй вход которого соединен с выходом шестнадцатого элемента И-НЕ, третий вход соединен с выходом четвертого элемента НЕ,вход которого соединен с первым входом двадцатого элемента И-НЕ, второй входю

которого соединен с выходом семнадцатого элемента И-НЕ, третий вход соединен с выходом восемнадцатого эле-1 мента И-НЕ, а выход соединен с первым входом двадцать первого элемента И-НЕ, второй вход которого соединен с выходом девятнадцатого элемента И-НЕ, а выход соединен с выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления симметрических булевых функций | 1991 |

|

SU1835542A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СРЕДЫ | 2006 |

|

RU2310902C1 |

| Многофункциональный логическийМОдуль | 1977 |

|

SU798802A1 |

| Устройство для вычисления симметрических булевых функций | 1990 |

|

SU1716502A1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2020 |

|

RU2757817C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СРЕДЫ | 2003 |

|

RU2251141C1 |

| Многофункциональный модуль | 1983 |

|

SU1117629A1 |

| Устройство для выделения симметрических булевых функций | 1991 |

|

SU1833859A1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2021 |

|

RU2776921C1 |

| Многофункциональный модуль | 1988 |

|

SU1509866A1 |

Изобретение относится к вычислительной технике и предназначено для построения быстродействующих матричных арифметических устройств. Цель изобретения - упрощение устройства для вычисления симметрических булевых функций. Устройство для вычисления симметрических булевых функций четырех переменных содержит элементы НЕ 1-4, элементы И-НЕ 5-25, информационные входы 26-29, настроечные входы 30-34 и выход 35. На информационные входы устройства подаются двоичные переменные X1 - X4

на настроечные входы - сигналы настройки U1 - U5, значения которых принадлежат множеству {0,1

на выходе устройства реализуется симметрическая булевая функция F = F(X1, X2, X3, X4), определяемая вектором настройки U=(U1, U2, U3, U4, U5). 1 ил., 1 табл.

| Мищенко В оА,, Козюминский В„Ц., Семашко А.Н, Многофункциональные автоматы и элементная база цифровых ЭВМ - М„: Радио и связь, 198), с„ 81, рис 4.12„ Авторское свидетельство СССР № 1119003, кл, G 06 F 7/00, 1983 |

Авторы

Даты

1989-05-07—Публикация

1987-04-22—Подача