Изобретение относится к вычислительной технике и микроэлектронике и предназначено для реализации симметрических булевых функций шести переменных.

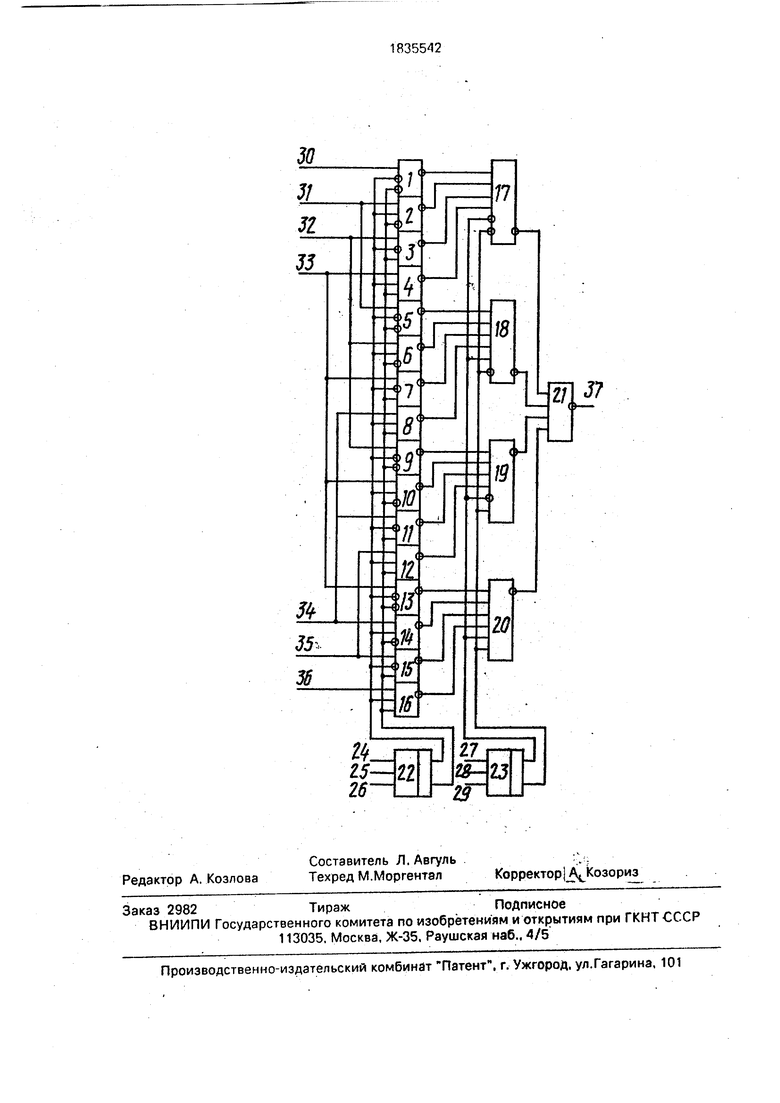

На чертеже представлена функциональная схема устройства для вычисления симметрических булевых функций.

Устройство содержит двадцать один элемент И-НЕ 1...21. два одноразрядных двоичных сумматора 22 и 23, шесть информационных входов 24.„29, семь настроечных входов 30...36, выход 37.

Устройство для вычисления симметрических булевых функций работает следующим образом. На информационные входы 24...29 поступают двоичные переменные xl ...хб (в произвольном порядке), на настро- енчые входы 30...36 - сигналы настройки u1...u7 соответственно, значения которых

принадлежат множеству {0.1}. На выходе 37 реализуется некоторая симметрическая булевая функция (x1.x6), определяемая вектором настройки U(u1,u2иб).

Рассмотрим алгоритм настройки. Пусть ps значение F на наборе аргументов

х1,х2хб. содержащем равно s единиц, т.е.

()ps при x1+x2+x3+x4+x5+x6 s, ,6.

Компоненты вектора настройки U инверсны соответствующим значениям ps, a

именно: . или

,u2,u3.u4.u5.u6,u7)(pO,p1.p2,

рЗ,р4,р5.р6).

Пример. Определим вектор настройки U устройства на реализацию функции

00 GJ СЛ СП

Ь. ГО

(x 1. хб) х 1x2x3x4x5x6 v x 1x2x3x4x5 v vх1х2хЗх4хбvх1х2хЗх5хбv

v x1x2x4x5x6xv x1x3x4x5x6 v

v x2x3x4x5x6

Решение. Очевидно, что p(F) ,р1 ,р2,р3.р4,р5,рб) (1,1,0,0,0.0,1). Тогда 1X0,0,1,1,1.0).

Следовательно, сигнал логического нуля должен быть подан на настроечные входы 30,31 и 36, сигнал логической единицы - на настроечные входы 32.33, 34 и 35.

Таким образом, устройство реализует все 128 симметрических булевых функций шести переменных.

Фор мула изобретения Устройство для вычисления симметрических булевых функций, содержащее шесть элементов И-НЕ, причем первый вход первого элемента И-НЕ соединен с первым настроечным входом устройства, второй настроечный вход которого соединен с первым входом третьего-элемента И-НЕ, первые входы четвертого и пятого элементов И-НЕ соединены с третьим настроечным входом устройства, четвертый настроечный вход которого соединен с первым входом шестого элемента И-НЕ, отличающее- с я тем, что, с целью расширения фунцио- нальных возможностей путем реализации симметрических булевых функций шести переменных/оно содержит с седьмого по двадцать первый элементы И-НЕ и два сумматора, причем первый вход седьмого элемента И-НЕ соединен с третьим построечным входом устройства, четвертый настроечный вход которого соединен с первыми входами восьмого, девятого и десятого элементов.V1-HE, первые входы одиннадцатого, двенадцатого и тринадцатого элементов И-НЕ соединены с пятым настроечным входом устройства, шестой настроечный вход которого соединен с первыми входами четырнадцатого и пятнадцатого элементов И-НЕ, первый вход шестнадцатого элемента И-НЕ соединен с седьмым настроечным входом устройства, первый, второй и третий информационные входы которого соединены с входами первого сумматора, выход суммы которого соединён с вторыми входами первого, третьего,

0

5

0

5

0

5

0

5

rf

четвертого, седьмого, восьмого, десятого, двенадцатого, пятнадцатого элементов И- НЕ и первыми инверсными входами второго, пятого, шестого, девятого, одиннадцатого, тринадцатого, четырнадцатого и шестнадцатого элементов И-НЕ, выход переноса первого сумматора соединен с третьими входами первого, третьего, седьмого, десятого элементов И-НЕ, вторыми входами второго, пятого, девятого, тринадцатого элементов И-НЕ, первыми инверсными входами четвертого, восьмого, двенадцатого, пятнадцатого элементов И-НЕ, и вторыми инверсными входами шестого, одиннадцатого, четырнадцатого и шестнадцатого элементов И-НЕ, выходы первого, второго/штвертого и шестого элементов И-НЕ соединены с первого по четвертый входами семнадцатого элемента И-НЕ, пятый вход которого соединен с инверсным входом восемнадцатого, первым входом девятнадцатого, первым инверсным входом двадцатого элементов И-НЕ и выходом суммы второго сумматора, выход переноса которого сбединен с шестым входом семнадцатого, первым входом восемнадцатого, инверсным входом девятнадцатого и. вторым инверсным входом двадцатого элементов И-НЕ, выход которого соединен с первым входом двадцать первого элемента И-НЕ, второй и третий входы которого соединены соответственно с выходами семнадцатого элемента И-НЕ и восемнадцатого элемента И-НЕ, с второго по шестой входы которого соединены с выходами третьего, пятого, восьмого и одиннадцатого элементов И-НЕ, выходы седьмого, девятого, двенадцатого и четырнадцатого элементов И-НЕ соединены с второго по пятый входами девятнадцатого элемента И-НЕ, выход которого соединен с четвертым входом двадцать первого элемента И-НЕ, выходы которого являются выходом устройства, с четвертого по шестой информационные входы которого соединены с входами второго сумматора, выходы десятого, тринадцатого, пятнадцатого и шестнадцатого элементов И-НЕ соединены с первого по четвертый входами двадцатого элемента И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА ОДНОРОДНОЙ СРЕДЫ | 2006 |

|

RU2310902C1 |

| Устройство для вычисления симметрических булевых функций | 1987 |

|

SU1478208A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СРЕДЫ | 2003 |

|

RU2251141C1 |

| Многофункциональный логическийМОдуль | 1977 |

|

SU798802A1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2020 |

|

RU2757817C1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР | 2009 |

|

RU2408058C2 |

| СУММАТОР | 2008 |

|

RU2380739C1 |

| Многофункциональный модуль | 1983 |

|

SU1117629A1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 2009 |

|

RU2408922C1 |

| Конвейерное устройство для деления итерационного типа | 1985 |

|

SU1262483A1 |

| Устройство для вычисления симметрических булевых функций | 1988 |

|

SU1587489A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления симметрических булевых функций | 1989 |

|

SU1683001A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-08-23—Публикация

1991-04-18—Подача