1

Изобретение относится к электроизмерительной технике и может быть использовано, например, для измерения скорости течения жидкостей.

Цель изобретения - повышение точности преобразования.

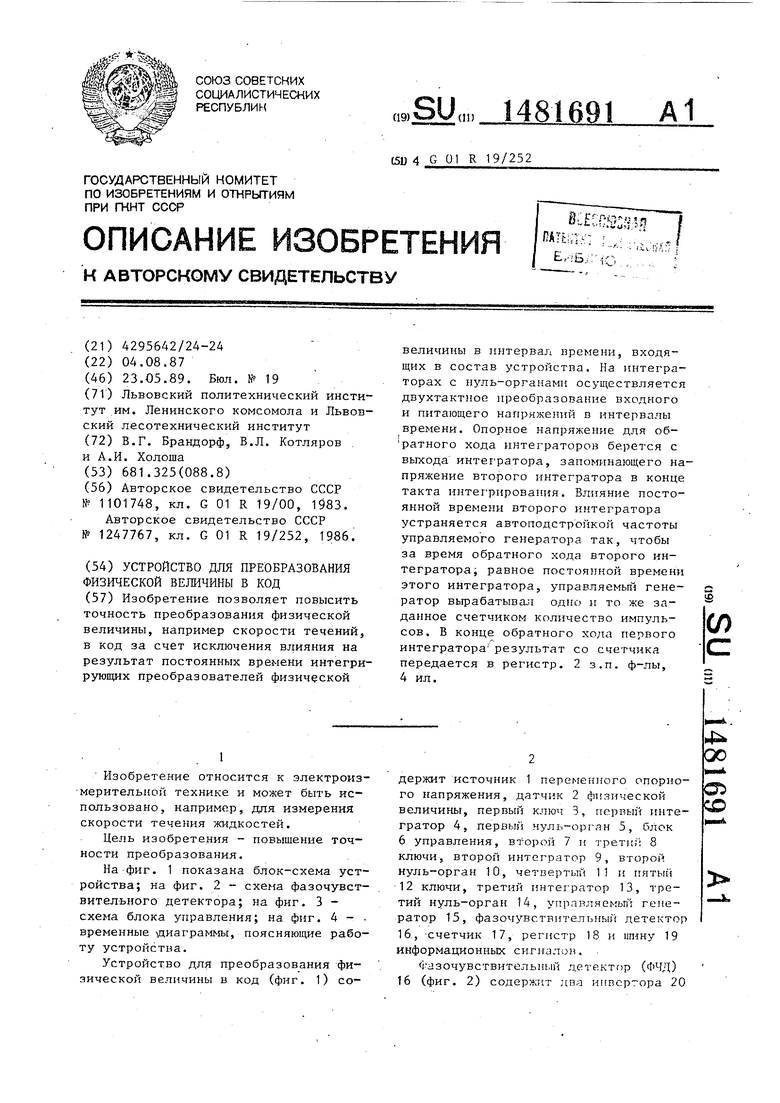

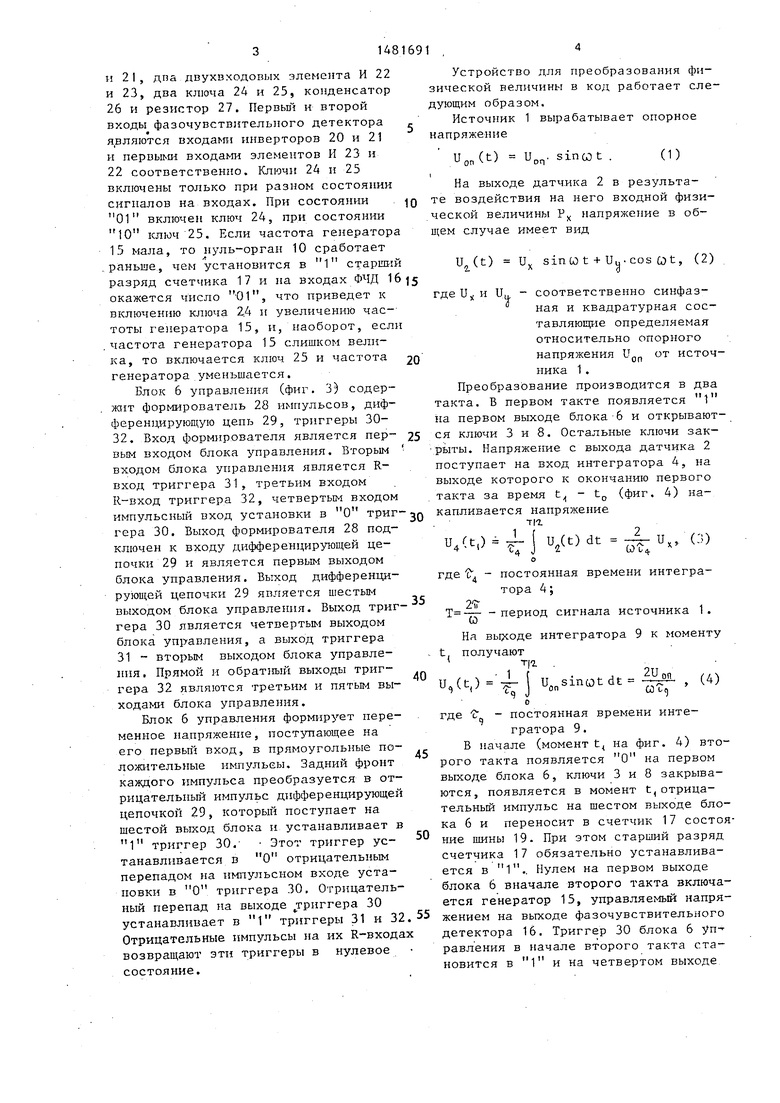

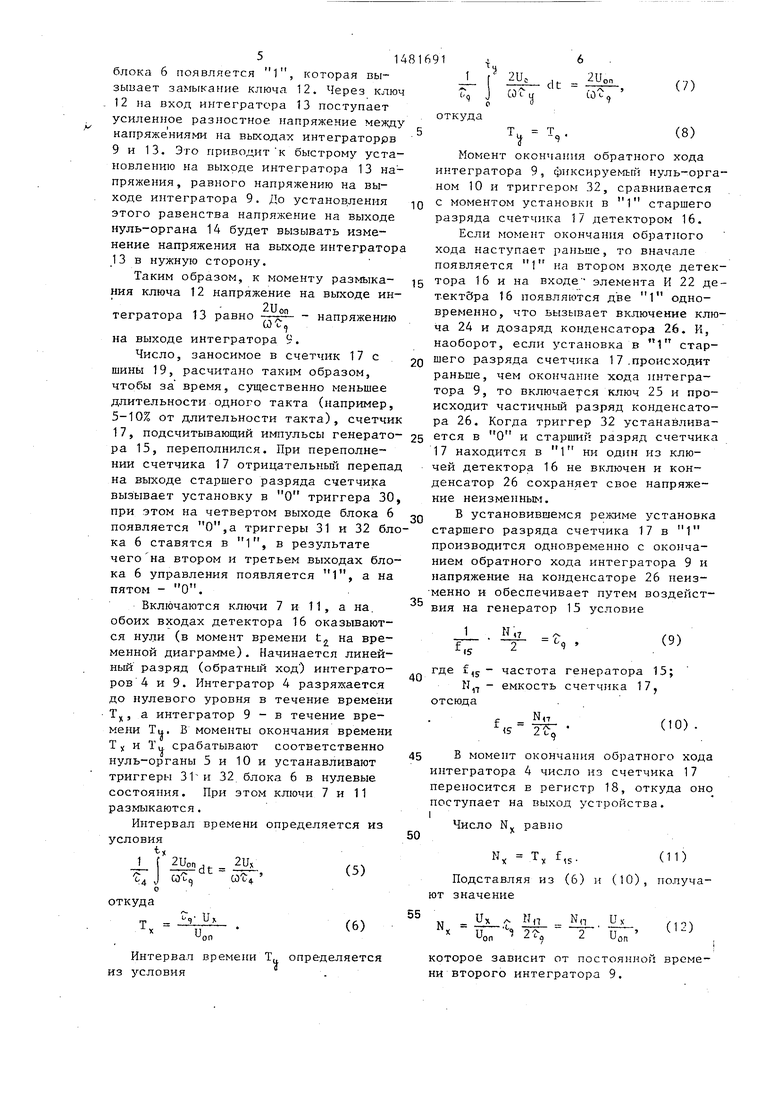

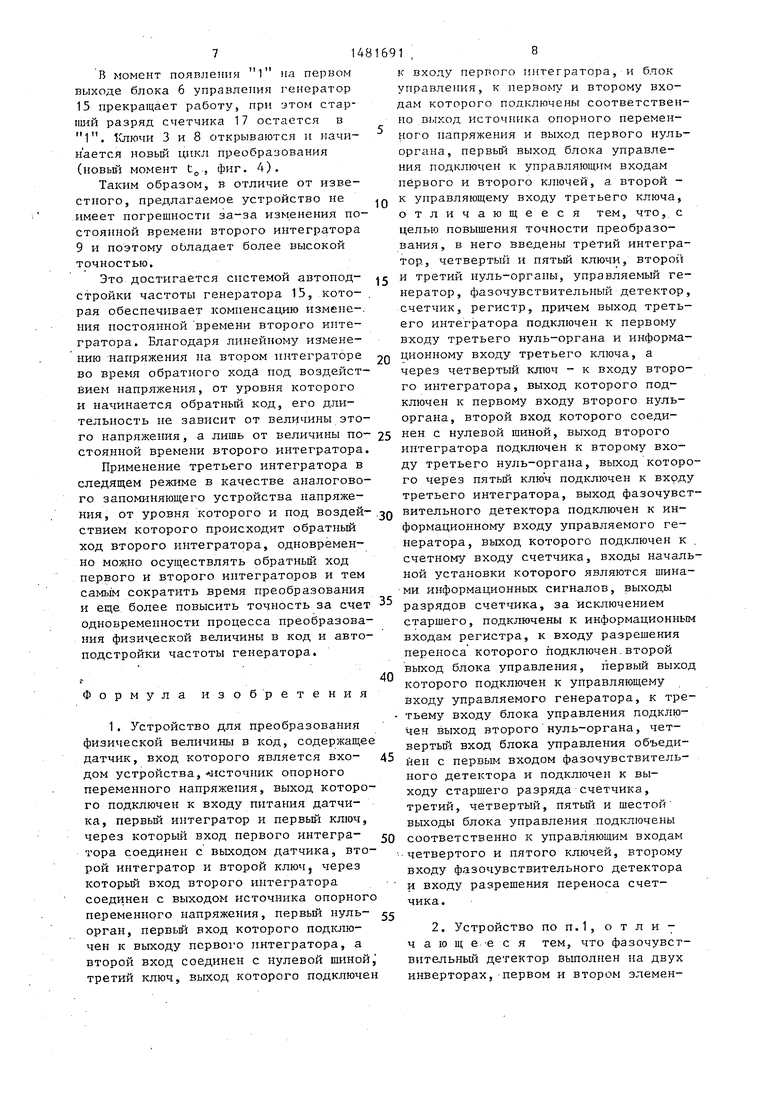

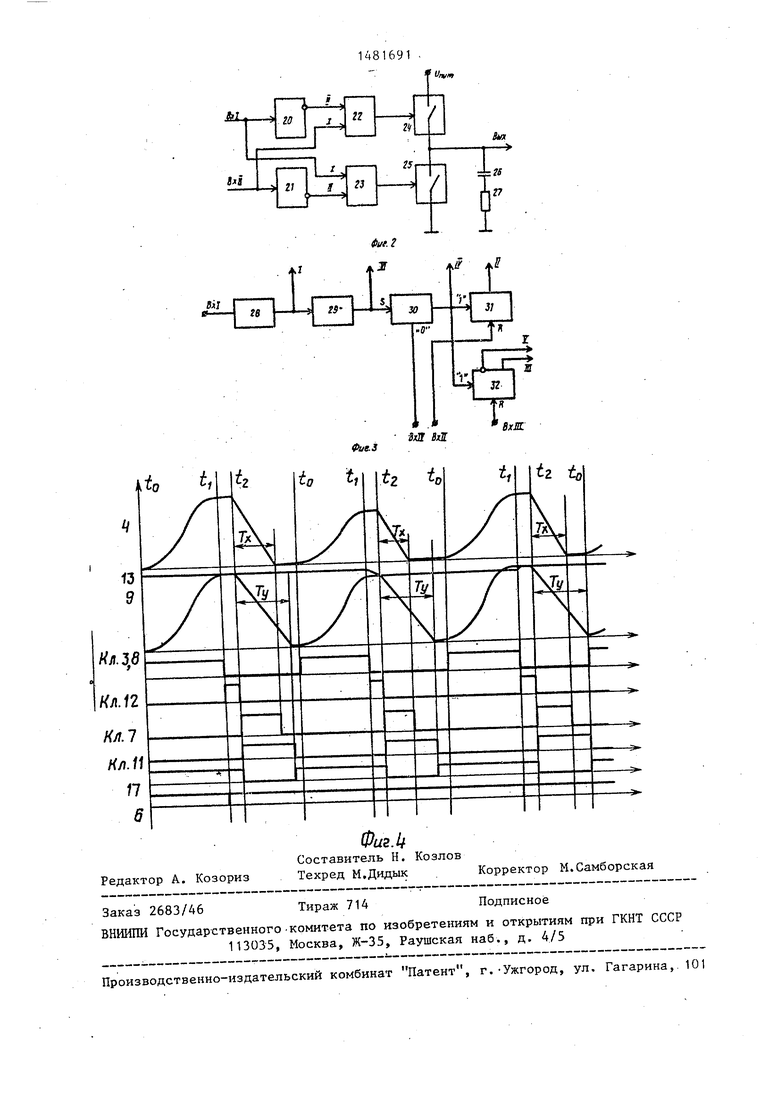

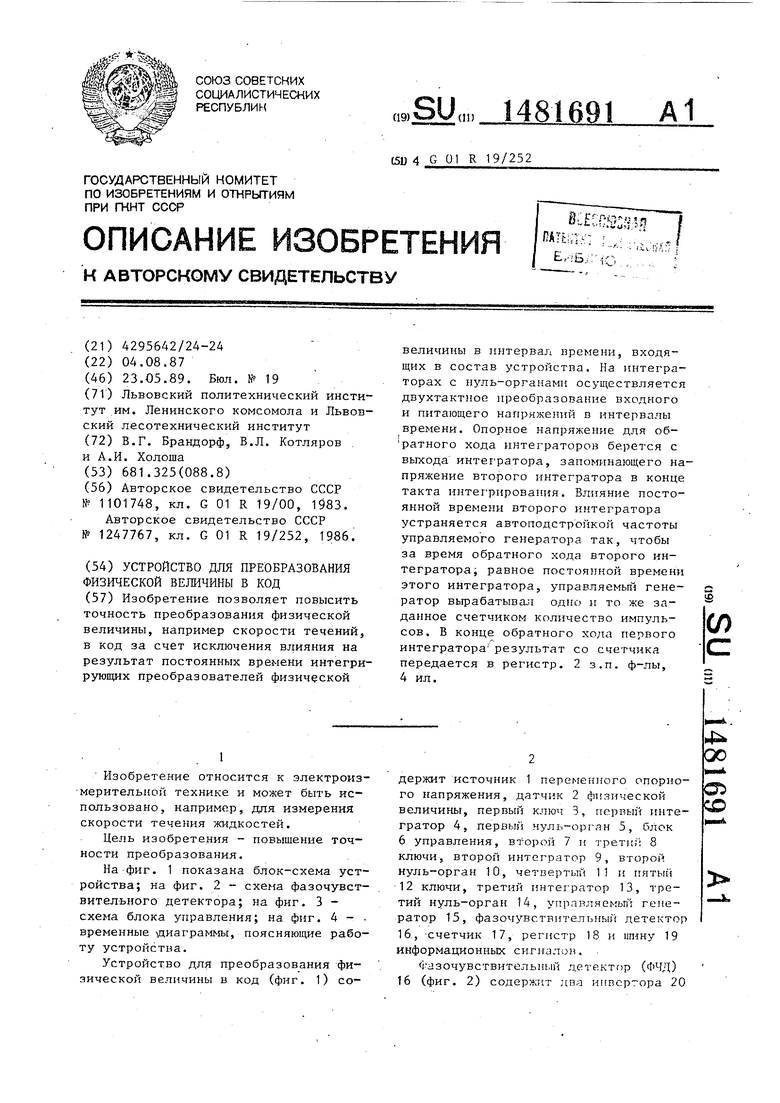

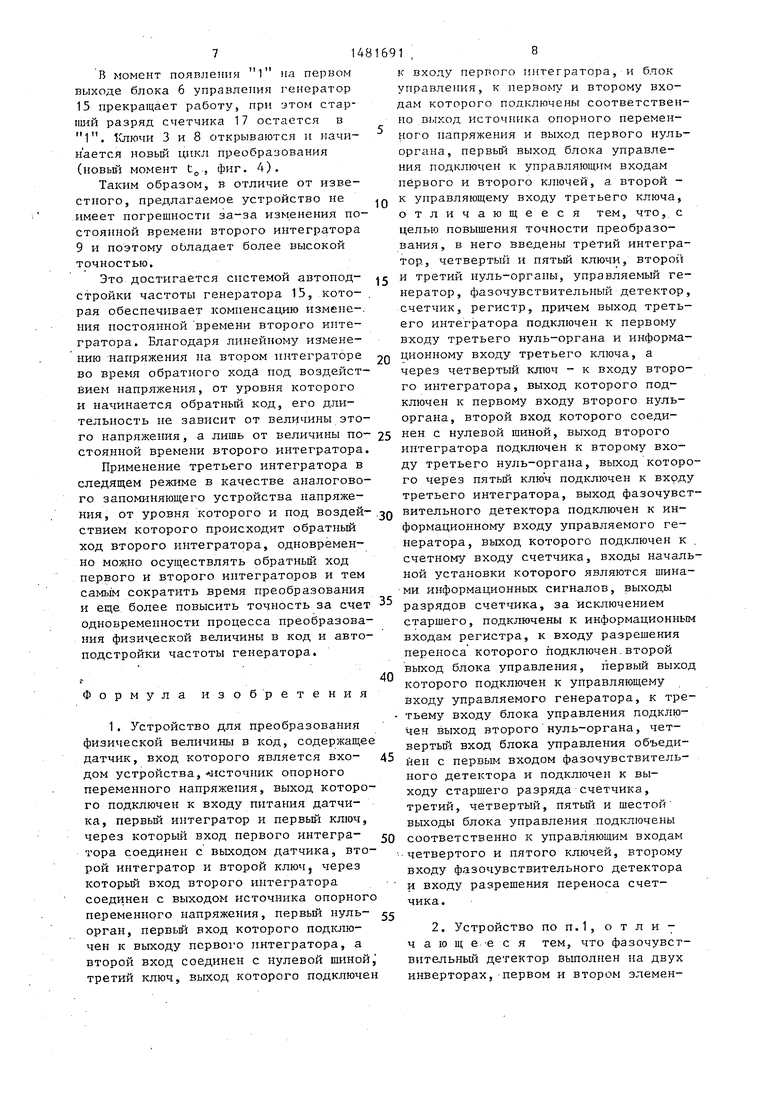

На фиг. 1 показана блок-схема устройства; на фиг. 2 - схема фазочувст- вительного детектора; на фиг. 3 - схема блока управления; на фиг. 4 - временные -диаграммы, поясняющие работу устройства.

Устройство для преобразования физической величины в код (фиг. 1) содержит источник 1 переменного опорного напряжения, датчик 2 физической величины, первый ключ 3, первый интегратор 4, первый нуль-орган 5, блок 6 управления, второй 7 и трети 1 8 ключи, второй интегратор 9, второй нуль-орган 10, четвертый И и пятый 12 ключи, третий инте ратор 13, третий нуль-орган 14, упртнлчекый генератор 15, фазочувствителънын детектор 16, счетчик 17, регистр 18 и шину 19 информационных сигналов.

iазочувсгвительнпй детектор (ФЧД) 16 (фиг. 2) содержит двз инвер-ора 20

-U

00

С5

со

и 21 , дпа двухвходовых -элемента И 22 и 23, два ключа 24 и 25, конденсатор 26 и резистор 27. Первый и второй входы фазочувствительного детектора являются входами инверторов 20 и 21 и первыми входами элементов И 23 и 22 соответственно. Ключи 24 и 25 включены только при разном состоянии сигналов на входах. При состоянии 01 включен ключ 24, при состоянии 10 ключ 25. Если частота генератор 15 мала, то нуль-орган 10 сработает раньше, чем установится в 1 старши разряд счетчика 17 и на входах ФЧД 1 окажется число 01, что приведет к включению ключа 2.4 и увеличению частоты генератора 15, и, наоборот, есл частота генератора 15 слишком велика, то включается ключ 25 и частота генератора уменьшается.

Блок 6 управления (фиг. 3) содержит формирователь 28 импульсов, дифференцирующую цепь 29, триггеры 30- 32. Вход формирователя является первым входом блока управления. Вторым входом блока управления является R- вход триггера 31, третьим входом R-вход триггера 32, четвертым входом импульсный вход установки в О триггера 30. Выход формирователя 28 подключен к входу дифференцирующей цепочки 29 и является первым выходом блока управления. Выход дифференцирующей цепочки 29 является шестым выходом блока управления. Выход триггера 30 является четвертым выходом блока управления, а выход триггера 31 - вторым выходом блока управления. Прямой и обратный выходы триггера 32 являются третьим и пятым выходами блока управления.

Блок 6 управления формирует переменное напряжение, поступающее на его первый вход, в прямоугольные положительные импульеы. Задний фронт каждого импульса преобразуется в отрицательный импульс дифференцирующей цепочкой 29, который поступает на шестой выход блока и устанавливает в 1 триггер 30. Этот триггер устанавливается в О отрицательным перепадом на импульсном входе установки в О триггера 30. Отрицательный перепад на выходе триггера 30 устанавливает в 1 триггеры 31 и 32 Отрицательные импульсы на их R-входа возвращают эти триггеры в нулевое состояние.

Устройство для преобразования физической величины в код работает следующим образом.

Источник 1 вырабатывает опорное напряжение

U0n(t Uon. sincot

(1)

На выходе датчика 2 в результате воздействия на него входной физической величины Рх напряжение в общем случае имеет вид

Ut(t) Ux sinCO t + Un-cos cot, (2)

где Ux и Un, соответственно синфазная и квадратурная составляющие определяемая относительно опорного напряжения Uon от источника 1 .

Преобразование производится в два такта. В первом такте появляется 1 на первом выходе блока 6 и открываются ключи 3 и 8. Остальные ключи закрыты. Напряжение с выхода датчика 2 поступает на вход интегратора 4, на выходе которого к окончанию первого

t такта за время .0 капливается напряжение

ТII

t (фиг. 4) наU

.Ct,)Јj ue(t), О)

где с4 - постоянная времени интегратора 4;

„, 2ЧГ

-период сигнала источника 1. ьо

На выходе интегратора 9 к моменту t получают

1 f „ ........ ,.. 2Uon

U(t)j Uonsin«tdt

Ч

(4)

5

0

5

где

9

- постоянная времени интегратора 9. В начале (момент t на фиг. 4) второго такта появляется О на первом выходе блока 6, ключи 3 и 8 закрываются, появляется в момент t,отрицательный импульс на шестом выходе блока 6 и переносит в счетчик 17 состояние шины 19. При этом старший разряд счетчика 17 обязательно устанавливается в 1. Нулем на первом выходе блока b вначале второго такта включается генератор 15, управляемый напряжением на выходе фазочувствительного детектора 16. Триггер 30 блока 6 ул- равления в начале второго такта ста- 1 и на четвертом выходе

новится в

Т

51

блока 6 появляется 1, которая вызывает замыкание ключа 12. Через клю

12на вход интегратора 13 поступает усиленное разностное напряжение межд напряжениями на выходах интеграторов

9 и 13. Эго приводит к быстрому установлению на выходе интегратора 13 напряжения, равного напряжению на выходе интегратора 9. До установления этого равенства напряжение на выходе нуль-органа 14 будет вызывать изменение напряжения на выходе интегратор

13в нужную сторону.

Таким образом, к моменту размыкания ключа 12 напряжение на выходе ин41 2 U on

тегратора 13 равно - напряжению

СО t-,j

на выходе интегратора 9.

Число, заносимое в счетчик 17с шины 19, расчитано таким образом, чтобы за время, существенно меньшее длительности одного такта (например, 5-10% от длительности такта), счетчи 17, подсчитывающий импульсы генерато ра 15, переполнился. При переполнении счетчика 17 отрицательный перепа на выходе старшего разряда счетчика вызывает установку в О триггера 30 при этом на четвертом выходе блока 6 появляется О,а триггеры 31 и 32 блка 6 ставятся в 1, в результате чего на втором и третьем выходах блока 6 управления появляется 1, а на пятом - О.

Включаются ключи 7 и 11, а на обоих входах детектора 16 оказываются нули (в момент времени t2 на временной диаграмме). Начинается линейный разряд (обратный ход) интеграторов 4 и 9. Интегратор 4 разряжается до нулевого уровня в течение времени

J

/ч.

() ;

ткуда

2U.

U.-N. t

dL

2U0

CO,

Т

(/)

(8)

5

0

5

0

5

Момент окончания обратного хода интегратора 9, фиксируемый нуль-органом 10 и триггером 32, сравнивается с моментом установки в 1 старшего разряда счетчика 17 детектором 16.

Если момент окончания обратного хода наступает раньше, то вначале появляется 1 на втором входе детектора 16 и на входе1 элемента И 22 детектора 16 появляются две 1 одновременно, что вызывает включение ключа 24 и дозаряд конденсатора 26. К, наоборот, если установка в 1 старшего разряда счетчика 17 происходит раньше, чем окончание хода интегратора 9, то включается ключ 25 и происходит частичный разряд конденсатора 26. Когда триггер 32 устанавливается в О и старший разряд счетчика 17 находится в 1 ни один из ключей детектора 16 не включен и конденсатор 26 сохраняет свое напряжение неизменным.

В установившемся режиме установка старшего разряда счетчика 17 в 1 производится одновременно с окончанием обратного хода интегратора 9 и напряжение на конденсаторе 26 неизменно и обеспечивает путем воздействия на генератор 15 условие

Э

(9)

40

генератора 15; счетчика 17,

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ИНТЕГРИРУЮЩИЙ ВОЛЬТАМПЕРМЕТР | 1972 |

|

SU347909A1 |

| Устройство для измерения постоянной времени | 1987 |

|

SU1504626A1 |

| Цифровой электромагнитный толщиномер | 1988 |

|

SU1839228A1 |

| Цифровой термометр | 1986 |

|

SU1397749A1 |

| Электромагнитный интегрирующий толщиномер | 1986 |

|

SU1427165A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин с мультипликативной автокоррекцией | 1984 |

|

SU1185604A1 |

| Устройство для измерения отклонения сопротивления от заданного значения | 1986 |

|

SU1536322A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012130C1 |

| Устройство для измерения отношения сопротивлений | 1988 |

|

SU1619195A1 |

Изобретение позволяет повысить точность преобразования физической величины, например скорости течений, в код за счет исключения влияния на результат постоянных времени интегрирующих преобразователей физической величины в интервал времени, входящих в состав уа. На интеграторах с нуль-органами осуществляется двухтактное преобразование входного и питающего напряжений в интервалы времени. Опорное напряжение для обратного хода интеграторов берется с выхода интегратора, запоминающего напряжение второго интегратора в конце такта интегрирования. Влияние постоянной времени второго интегратора устраняется автоподстройкой частоты управляемого генератора, чтобы за время обратного хода второго интегратора, равное постоянной времени этого интегратора, управляемый генератор вырабатывал одно и то же заданное счетчиком количество импульсов. В конце обратного хода первого интегратора результат со счетчика передается в регистр. 2 з.п. ф-лы, 4 ил.

А х мени

Т и

а интегратор 9 - -V

В моменты о

; п ТЛ срабатывают нуль-органы 5 и 10 и и 32 бло При этом

триггеры 31 состояния. размыкаются.

Интервал времени условия t 1 f 2Uon

I ОП J 4-

« ;„

2U Wt4

откуда

т

ix

U

ил

Интерваа времени Тц определяется

из условия

Ч

(Ю)

45

50

В момент окончания обратного хода интегратора 4 число из счетчика 17 переносится в регистр 18, откуда оно

поступает на выход устройства. I

Число N.. равно

N

Т f х х L

Подставляя из ют значение

is (6)

(Ю)

(11) попуча6)

55

N.

U, Ц

п

on

1 2

С9

Nn 2

U

оп

которое зависит от постоянной времени второго интегратора 9.

7148

В момент появления 1 на первом выходе блока 6 управления генератор 15 прекращает работу, при этом старший разряд счетчика 17 остается в 1. Ключи 3 и 8 открываются и начинается новый цикл преобразования (новый момент 10, фиг. 4).

Таким образом, в отличие от известного, предлагаемое устройство не имеет погрешности за-за изменения постоянной времени второго интегратора 9 и поэтому обладает более высокой точностью.

Это достигается системой автоподстройки частоты генератора 15, которая обеспечивает компенсацию изменения постоянной времени второго интегратора. Благодаря линейному изменению напряжения на втором интеграторе во время обратного хода под воздействием напряжения, от уровня которого и начинается обратный код, его длительность не зависит от величины этого напряжения, а лишь от величины постоянной времени второго интегратора.

Применение третьего интегратора в следящем режиме в качестве аналогового запоминяющего устройства напряжения, от уровня которого и под воздействием которого происходит обратный ход второго интегратора, одновременно можно осуществлять обратный ход первого и второго интеграторов и тем самым сократить время преобразования и еще более повысить точность за счет одновременности процесса преобразования физической величины в код и автоподстройки частоты генератора.

Формула изобретения

691 ,8

к входу первого интегратора, и бчок управления, к первому и второму входам которого подключены соответственно выход источника опорного переменного напряжения и выход первого нупь- органа, первьй выход блока управления подключен к управляющим входам первого и второго ключей, а второй к управляющему входу третьего ключа, отличающееся тем, что, с целью повышения точности преобразования, в него введены третий интегратор, четвертый и пятый ключи, второй

и третий нуль-органы, управляемый генератор, фазочувствительный детектор, счетчик, регистр, причем выход третьего интегратора подключен к первому входу третьего нуль-органа и информаQ ционному входу третьего ключа, а

через четвертый ключ - к входу второго интегратора, выход которого подключен к первому входу второго нуль- органа, второй вход которого соеди5 нен с нулевой шиной, выход второго интегратора подключен к второму входу третьего нуль-органа, выход которого через пятый ключ подключен к входу третьего интегратора, выход фазочувстQ вительного детектора подключен к информационному входу управляемого генератора, выход которого подключен к счетному входу счетчика, входы начальной установки которого являются шинами информационных сигналов, выходы разрядов счетчика, за исключением старшего, подключены к информационным входам регистра, к входу разрешения переноса которого подключен второй выход блока управления, первый выход которого подключен к управляющему входу управляемого генератора, к тре- тьему входу блока управления подключен выход второго нуль-органа, четвертый вход блока управления объеди5 йен с первым входом фазочувствитель- ного детектора и подключен к выходу старшего разряда счетчика, третий, четвертый, пятый и шестой выходы блока управления подключены

0 соответственно к управляющим входам четвертого и пятого ключей, второму входу фазочувствительного детектора и входу разрешения переноса счетчика.

5

0

так И, двух ключах, интегрирующем элементе, выполненном на конденсаторе, и токоограничивающем элементе, выполненном на резисторе, причем вход первого инвертора является первым входом фазочувствительного детектора и соединен с первым входом второго элемента И, вторым входом фазочувствительного детектора является вход второго инвертора, который объединен с первым входом первого элемента И, второй вход которого соединен с выходом первого инвертора, выход второго инвертора соединен с вторым входом второго элемента И,выходы первого и второго элементов И соединены с управляющими входами первого и второго ключей соответственно, первая обкладка конденсатора соединена с выходом фазочастотного детектора и через первый и второй ключи с шиной питания и нулевой шиной, вторая обкладка конденсатора через резистор соединена с нулевой шиной.

J

етеречи

481691 Ю

1

первым, вторым, третьим и четвертым . входами блока управления являются соответственно вход формирователя импульсов, R-вход второго триггера, R-вхо д третьего триггера и вход установки в О первого триггера, а первым, вторым, третьим, четвертым, пятым и шестым выходами блока управления являются соответственно выходы формирователя импульсов, выход второго триггера, прямой выход третьего триггера, выход первого триггера,инверсный выход третьего триггера и выход дифференцирующей цепи.

| Способ измерения электрических и неэлектрических параметров | 1983 |

|

SU1101748A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для преобразования физической величины в интервал времени | 1982 |

|

SU1247767A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-05-23—Публикация

1987-08-04—Подача