Изобретение относится к импульсной технике, в частности к преобразователям напряжения в цифровой код с интегрированием входного и опорного напряжений, и может быть использовано в устройствах сбора аналоговой информации различных систем, выполняемых на средствах вычислительной техники.

Известны аналого-цифровые преобразователи (АЦП), которые содержат интегратор, источник опорного напряжения, ноль-орган, два триггера, генератор импульсов и счетчик [1] .

В этих АЦП преобразование выполняется в два такта: сначала за To=  (fo - частота генератора импульсов) интегрируется входной сигнал Uх, а затем полученное напряжение разынтегрируется за Tx=

(fo - частота генератора импульсов) интегрируется входной сигнал Uх, а затем полученное напряжение разынтегрируется за Tx=  с помощью опорного напряжения Uо, откуда k Ux To = k Uo Tx, где k - коэффициент интегратора,

с помощью опорного напряжения Uо, откуда k Ux To = k Uo Tx, где k - коэффициент интегратора,

x=  ·No.

·No.

Для подавления помех, наложенных на Uх, длительность первого такта должна быть равна (кратна) периоду помехи T1 = Tn, что в этих АЦП недопустимо, так как это приводит к появлению погрешности в результате преобразования из-за изменения Т1 во времени.

Эти недостатки устранены в АЦП [2] , который содержит первый счетчик, информационные выходы которого являются выходной шиной, первый ключ, информационный вход которого является входной шиной, управляющий вход соединен с первым выходом блока управления и объединен с первым входом первого элемента И, а выход объединен с выходом второго ключа и через резистивный элемент подключен к входу интегратора и к информационному входу третьего ключа, причем управляющий вход второго ключа соединен с вторым выходом блока управления, а его информационный вход соединен с выходом переключателя, управляющий вход которого соединен с третьим выходом блока управления, первый информационный вход через аналоговый инвертор соединен с его вторым информационным входом, который соединен с выходом источника опорного напряжения и объединен с первым входом компаратора, выход которого соединен со счетным входом второго счетчика и с первым входом первого элемента ИЛИ, а второй вход соединен с выходами третьего ключа и интегратора и объединен с первым входом нуль-органа, второй вход которого соединен с входом источника опорного напряжения, который является шиной нулевого потенциала, выход нуль-органа соединен с первым входом блока управления, управляющий вход третьего ключа соединен с выходом первого элемента ИЛИ, второй вход которого соединен с четвертым выходом блока управления и объединен с первым входом второго элемента И, выход которого подключен к входам установки в ноль второго и третьего счетчиков, а второй вход объединен с вторым входом блока управления, входом установки в ноль первого счетчика, который является входной шиной синхронизации, и с первым входом второго элемента ИЛИ, выход которого соединен с входом установки в ноль первого делителя частоты, информационные входы которого подключены к выходам соответствующих разрядов третьего счетчика, выход - к первому входу третьего элемента И, импульсный вход подключен к пятому выходу блока управления и объединен с вторым входом первого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход которого подключен к счетному входу первого счетчика, выход переполнения которого соединен со счетным входом третьего счетчика, единичные выходы соответствующих старших разрядов второго счетчика подсоединены к входам четвертого элемента ИЛИ, выход которого соединен с третьим входом блока управления, и четвертый счетчик, при этом информационный и управляющие входы третьего ключа, соединены соответственно с выходом цифроаналогового преобразователя (ЦАП) и с вторым выходом блока управления, шестой и первый выходы которого подсоединены соответственно к вторым входам второго счетчика и третьего элемента И, первый вход которого соединен с вторым входом третьего элемента ИЛИ, а выход - со счетным входом четвертого счетчика, вход установки нуля которого подсоединен к выходу переполнения первого счетчика и к второму входу второго элемента ИЛИ, а выходы разрядов - к информационным входам ЦАП, вход которого соединен с выходом переключателя, а последний вход четвертого элемента ИЛИ соединен с третьим выходом блока управления.

В этом АЦП по сравнению с аналогами время интегрирования Тизадается по внешним синхронизирующим импульсам, интервал времени между которыми выбирается в зависимости от периода частоты помехи Тn или ее гармоник. При этом, если за Ти выходное напряжение интегратора превышает величину его рабочего диапазона, то срабатывает компаратор и выполняется разряд конденсатора интегратора и продолжается дальнейшее интегрирование Uх. За время Ти определяются два кода р и  , обеспечивающие соотношение Ти = (pNo + n) to; где to - квант работы АЦП в первом такте; No=

, обеспечивающие соотношение Ти = (pNo + n) to; где to - квант работы АЦП в первом такте; No=  и То - наименьшее время интегрирования Uх; q - число срабатываний компаратора. Во втором такте для выполнения разынтегрирования и компенсационного интегрирования используется напряжение

и То - наименьшее время интегрирования Uх; q - число срабатываний компаратора. Во втором такте для выполнения разынтегрирования и компенсационного интегрирования используется напряжение

Uк=  No+

No+

, где Δ- квант АЦП, равный Uo/No. Сначала разынтегрируется остаточное напряжение U1 интегратора за время Тр, а затем q раз выполняется интегрирование Uk до напряжения Uo = k Uk Tk, что занимает общее время Т2 = Tp + q Tk. Время Т2 преобразуется в код Хр результата преобразования с временным квантом pto:

, где Δ- квант АЦП, равный Uo/No. Сначала разынтегрируется остаточное напряжение U1 интегратора за время Тр, а затем q раз выполняется интегрирование Uk до напряжения Uo = k Uk Tk, что занимает общее время Т2 = Tp + q Tk. Время Т2 преобразуется в код Хр результата преобразования с временным квантом pto:

Xp=  .

.

Величина U1 + q Uо равна напряжению, получаемому на выходе интегратора в первом такте, т. е.

Uи= kUxTи= kUxp No+

No+  to, поэтому получают Xp=

to, поэтому получают Xp=  , т. е. Хр является точным результатом преобразования, который не зависит от величины Ти.

, т. е. Хр является точным результатом преобразования, который не зависит от величины Ти.

Но данный АЦП имеет недостаток, который состоит в том, что во втором такте для получения Хр затрачивается большое время на выполнение компенсационного интегрирования (qТк) и время этого такта почти такое же, как время интегрирования Uх в первом такте. Такие затраты времени существенно снижают быстродействие АЦП.

На уменьшение этих затрат времени и устранение недостатка прототипа направлено данное предложение, целью которого является повышение быстродействия АЦП.

Цель достигается тем, что в интегрирующий АЦП, содержащий первый счетчик, информационные выходы которого являются выходной шиной, первый ключ, информационный вход которого является входной шиной, управляющий вход соединен с первым выходом блока управления и объединен с первым входом первого элемента И, а выход объединен с выходом второго ключа и через резистивный элемент подключен к входу интегратора и к информационному входу третьего ключа, причем управляющий вход второго ключа соединен с вторым выходом блока управления, а его информационный вход соединен с выходом переключателя, управляющий вход которого соединен с третьим выходом блока управления, первый информационный вход через аналоговый инвертор соединен с его вторым информационным входом, который соединен с выходом источника опорного напряжения и объединен с первым входом компаратора, выход которого соединен со счетным входом второго счетчика и с первым входом первого элемента ИЛИ, а второй вход соединен с выходами третьего ключа и интегратора и объединен с первым входом нуль-органа, второй вход которого соединен с входом источника опорного напряжения, который является шиной нулевого потенциала, выход нуль-органа соединен с первым входом блока управления, управляющий вход третьего ключа соединен с выходом первого элемента ИЛИ, второй вход которого соединен с четвертым выходом блока управления и объединен с первым входом второго элемента И, выход которого подключен к входам установки в ноль второго и третьего счетчиков, а второй вход объединен с вторым входом блока управления, входом установки в ноль первого счетчика, который является входной шиной синхронизации, и с первым входом второго элемента ИЛИ, выход которого соединен с входом установки в ноль первого делителя частоты, информационные входы которого подключены к выходам соответствующих разрядов третьего счетчика, выход - к первому входу третьего элемента И, импульсный вход подключен к пятому выходу блока управления и объединен с вторым входом первого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход которого подключен к счетному входу первого счетчика, выход переполнения которого соединен со счетным входом третьего счетчика, единичные выходы соответствующих старших разрядов второго счетчика подсоединены к входам четвертого элемента ИЛИ, выход которого соединен с третьим входом блока управления, и четвертый счетчик, введены второй делитель частоты, коммутатор кодов, с четвертого по седьмой элементы И и пятый элемент ИЛИ, первый вход которого объединен с четвертым входом блока управления и с первыми входами третьего и четвертого элементов И, второй вход соединен с выходом второго элемента ИЛИ, а выход - с входом установки в ноль второго делителя частоты, выход которого соединен с первыми входами пятого и шестого элементов И, а информационные входы - с соответствующими выходами коммутатора кодов, вход управления которого объединен с вторым входом шестого элемента И и подключен к шестому выходу блока управления, информационные входы первого кода - к соответствующим выходам разрядов четвертого счетчика, а информационные входы второго кода - к соответствующим единичным выходам старших разрядов и младшему разряду второго счетчика, выход младшего разряда объединен с первым входом седьмого элемента И, остальные входы которого подсоединены к нулевым выходам старших разрядов второго счетчика, а выход - к пятому входу блока управления и к второму входу четвертого элемента И, третий вход которого соединен с третьим выходом блока управления и с вторым входом пятого элемента И, а выход - с вторым входом третьего элемента ИЛИ, третий и четвертый входы которого подключены к выходам третьего и пятого элементов И, третий вход последнего из которых объединен с третьим входом блока управления, пятый, седьмой и восьмой выходы которого подсоединены соответственно к импульсному входу второго делителя частоты, к второму входу третьего элемента И и к второму входу второго элемента ИЛИ, шестой и седьмой входы - к выходам соответственно компаратора и второго элемента И, а второй вход объединен с входом установки в ноль четвертого счетчика, счетный вход которого соединен с выходом шестого элемента И.

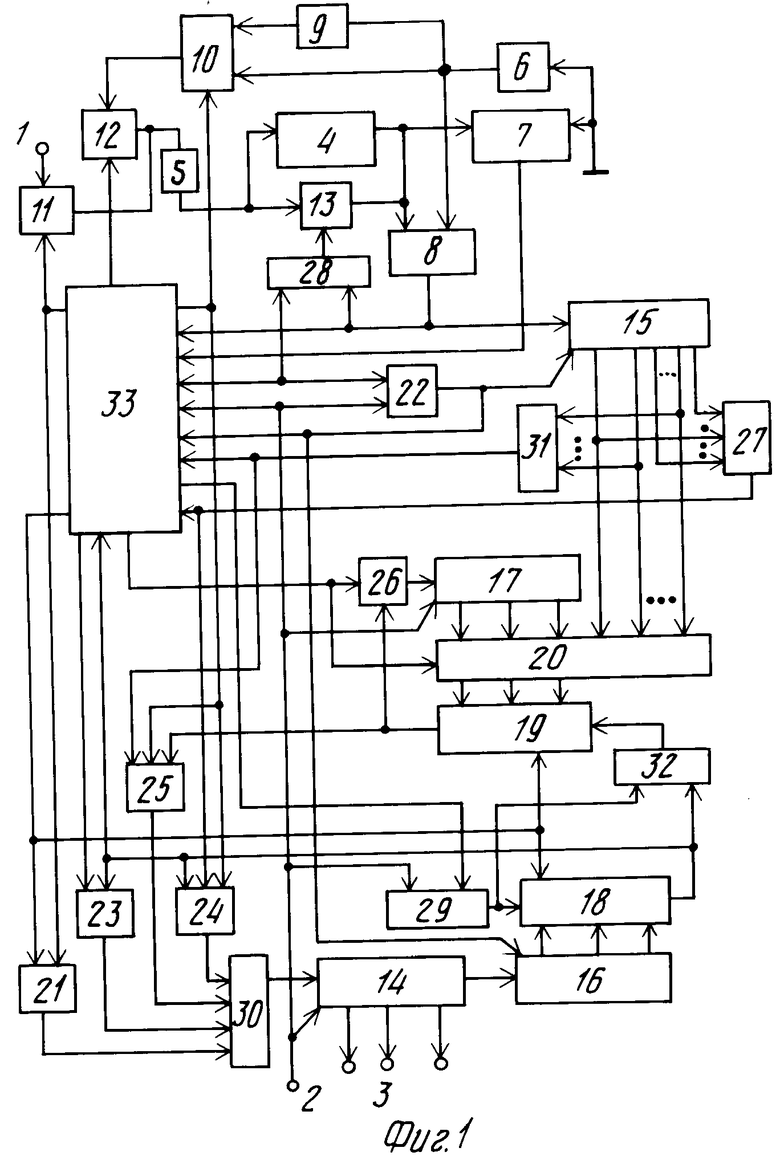

Блок управления выполнен на четырех триггерах, элементе задержки, шести элементах И, четырех элементах ИЛИ, формирователе импульсов и управляемом генераторе импульсов, выход которого является пятым выходом блока, а вход соединен с выходом первого элемента ИЛИ, первый вход которого является вторым входом блока и объединен с первым входом первого элемента И, а второй вход является восьмым выходом блока, через формирователь импульсов подключен к нулевому выходу первого триггера и объединен с первым входом второго элемента И, выход которого является четвертым выходом блока, а второй, третий и четвертые входы соединены с нулевыми выходами второго, третьего и четвертого триггеров соответственно, единичный выход последнего из которых является первым выходом блока и соединен с вторым входом первого элемента И, выход которого подключен к первым входам третьего, четвертого и пятого элементов И и к нулевому входу четвертого триггера, единичный вход которого является седьмым входом блока, а вход установки в исходное состояние объединен с одноименными входами остальных триггеров и подключен к выходу элемента задержки, при этом выход второго элемента ИЛИ является вторым выходом блока, а его первый и второй входы - соответственно третьим и седьмым выходами блока, которые соответственно соединены с единичными выходами соответственно первого и второго триггеров, последний из которых соединен с первым входом шестого элемента И, выход и второй вход которого подключены соответственно к первому входу третьего элемента ИЛИ и к выходу четвертого элемента ИЛИ, первый и второй входы которого являются соответственно третьим и пятым входами блока, которые объединены с вторыми входами соответственно пятого и четвертого элементов И, выходы которых подключены соответственно к единичному входу третьего триггера и к второму входу третьего элемента ИЛИ, третий вход которого является шестым выходом блока и соединен с единичным выходом третьего триггера, нулевой вход которого является четвертым входом блока, первым входом которого является нулевой вход второго триггера, который объединен с вторым входом третьего элемента И, выход которого соединен с единичным входом второго триггера, единичный вход первого триггера соединен с выходом третьего элемента ИЛИ, а его нулевой вход является шестым входом блока.

Среди известных технических решений не обнаружены АЦП, которые содержат признаки, сходные с отличительными признаками заявляемого технического решения.

В предлагаемом АЦП задача по устранению недостатка прототипа решается путем уменьшения времени компенсационного интегрирования. Это достигается за счет формирования различных временных квантов работы АЦП, которые используются при выполнении разынтегрирования и компенсационного интегрирования. Эти кванты соответственно равны tи и tq = tи/q, а величина tи формируется с помощью временных квантов t по результату измерения времени Ти интегрирования преобразуемого сигнала, который получается при использовании также квантов t. Преобразование времени разынтегрирования Тр и компенсационного интегрирования Тк с квантами tии tq в коды Х1 и Х2 и их суммирование позволяют получить результат преобразования Хр, который не зависит от величины Ти и t, а получен, как показано ниже, за значительно меньшее время по сравнению с прототипом, что повышает быстродействие предлагаемого АЦП.

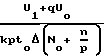

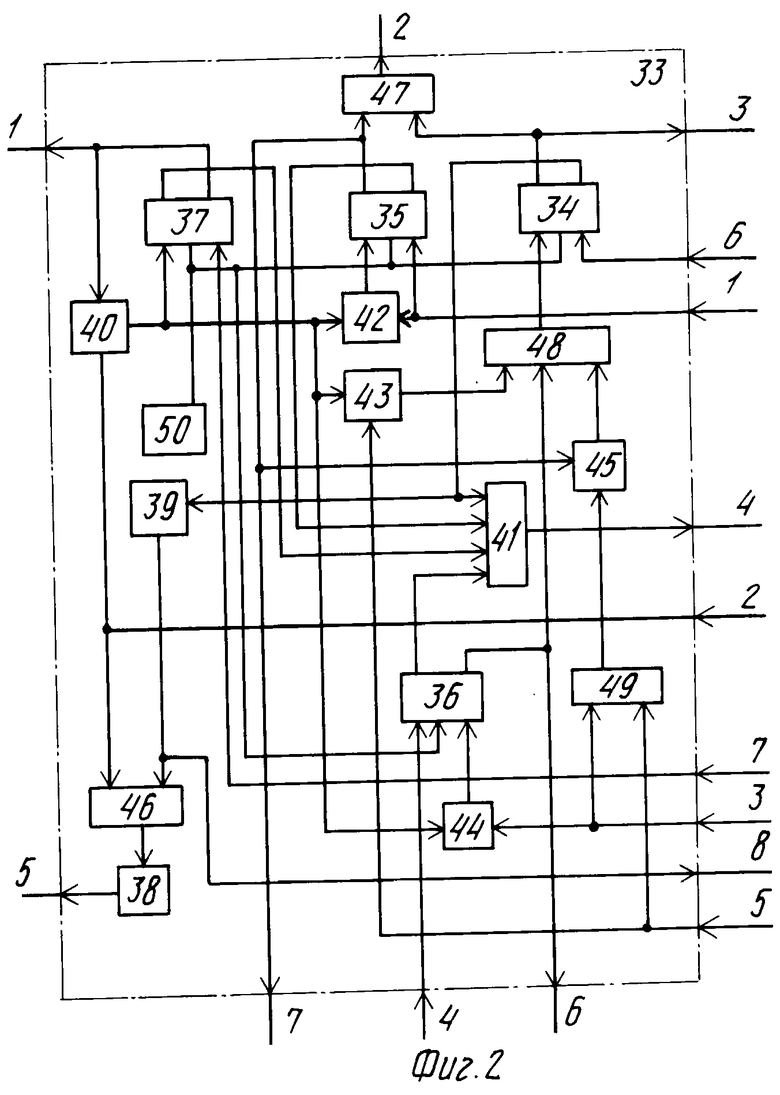

На фиг. 1, 2 и 3 приведены блок-схемы АЦП, его блока управления и временная диаграмма их работы, где 1 и 2 - входные шины преобразуемого напряжения Uх и импульсов синхронизации, задающих время Ти измерения, 3 - выходная шина результата преобразования, 4 - интегратор, например, выполненный на операционном усилителе с конденсатором в цепи отрицательной обратной связи, 5 - резистивный элемент, 6 - источник опорного напряжения - Uo, 7 и 8 - нуль-орган и компаратор, 9 - аналоговый инвертор, 10 - переключатель, выход которого подсоединен к второму информационному входу при отсутствии управляющего сигнала, а при его наличии к первому информационному входу, 11-13 - с первого по третий ключи, информационные входы которых подсоединяются к выходам при наличии управляющих сигналов, 14-17 - с первого по четвертый счетчики, 18 и 19 - первый и второй делители частоты, 20 - коммутатор кодов, на выходы которого проходят сигналы с входов первого кода при отсутствии сигнала управления, а при его наличии сигналы с выходов второго кода, 21-27 - с первого по седьмой элементы И, 28-32 - с первого по пятый элементы ИЛИ, 33 - блок управления, 34-37 - с первого по четвертый триггеры, 38 и 39 - управляемый генератор и формирователь импульсов, 40-45 - с первого по шестой элементы И, 46-49 - с первого по четвертый элементы ИЛИ, 50 - элемент задержки, 51 - импульсы синхронизации шины 2, 52-54 - импульсы на выходах элементов И 22, 40 и 41, 55-58 - сигналы на единичных выходах триггеров 37, 35, 34 и 36, 59 - сигнал на выходе элемента ИЛИ 47, 60 и 61 - напряжение на выходе интегратора 4 и источника 6, 62 и 63 - сигналы на выходах компаратора 8 и нуль-органа 7, 64, 65 и 66 - сигналы на выходах элементов ИЛИ 31, И 27 и ИЛИ 46.

Входная шина 1 соединена с входом ключа 11, шина 2 - с входом установки в ноль счетчиков 14 и 17, с первым и вторым входами соответственно элементов ИЛИ 29 и И 22 и с вторым входом блока 33, шина 3 - с выходами счетчика 14, счетный вход которого соединен с выходом элемента ИЛИ 30, а выход переполнения - со счетным входом счетчика 16. Вход установки в ноль счетчика 16 подсоединен к одноименному входу счетчика 15, к выходу элемента И 22 и к седьмому входу блока 33, выходы - к входам делителя 18, импульсный вход которого соединен с одноименным входом делителя 19, с вторым входом элемента И 21 и с пятым выходом блока 33, вход установки в ноль - с выходом элемента ИЛИ 29, а выход - с четвертым входом блока 33, с первыми входами элементов И 23 и 24 и ИЛИ 32. Второй вход элемента ИЛИ 32 соединен с выходом элемента ИЛИ 29, а выход - с входом установки в ноль делителя 19, выход которого соединен с первыми входами элементов И 25 и 26, входы - с выходами коммутатора 20. Входы первого кода коммутатора соединены с выходами счетчика 17, входы второго кода - с единичными выходами счетчика 15, а вход управления - с шестым выходом блока 33 и с вторым входом элемента И 26, выходы которого соединен со счетным входом счетчика 17. Единичный выход младшего разряда счетчика 15 и нулевые выходы его старших разрядов соединены с входами элемента И 27, а единичные выходы его старших разрядов - с входами элемента ИЛИ 31, выход которого соединен с третьими входами блока 33 и элемента И 25. Выход элемента И 27 соединен с пятым входом блока 33 и с вторым входом элемента И 24, третий вход которого соединен с управляющим входом переключателя 10, с третьим выходом блока 33 и с вторым входом элемента И 25, а выход - с вторым входом элемента ИЛИ 30. Первый, третий и четвертый входы последнего соединены с выходами элементов И 21, 23 и 25, первый вход первого из них соединен с первым выходом блока 33 и с входом управления ключа 11, второй вход второго - с седьмым выходом блока 33, второй выход которого соединен с входом управления ключа 12. Выход ключа 12 соединен с выходом ключа 11 и через резистор 5 с входами интегратора 4 и ключа 13, а вход - с выходом переключателя 10, первый вход которого соединен через инвертор 9 с вторым входом, который объединен с первым входом компаратора 9 и с выходом источника 6. Вход источника 6 соединен с шиной нулевого потенциала и с вторым входом нуль-органа 7, первый вход которого соединен с выходами интегратора 4 и ключа 13 и с вторым входом компаратора 8, а выход - с первым входом блока 33. Шестой вход блока 33 соединен с выходом компаратора 8, со счетным входом счетчика 15 и с первым входом элемента ИЛИ 28, выход которого соединен с входом управления ключа 13, а второй вход - с первым входом элемента И 22 и с четвертым выходом блока 33, восьмой выход которого подсоединен к второму входу элемента ИЛИ 29.

В блоке 33 пятым выходом является выход генератора 38, вход которого соединен с выходом элемента ИЛИ 46. Первый вход элемента ИЛИ 46 является вторым входом блока и соединен с первым входом элемента И 40, а второй вход является восьмым выходом блока и через формирователь 39 подсоединен к нулевому выходу триггера 34 и к первому входу элемента И 41, выход которого является четвертым выходом блока, а второй, третий и четвертый входы соединены с нулевыми выходами триггеров 35, 36 и 37. Единичный выход последнего является первым выходом блока и соединен с вторым входом элемента И 40, выход которого подсоединен к первым входам элементов И 42, 43 и 44 и к нулевому входу триггера 37. Единичный вход триггера 37 является седьмым входом блока, а вход установки в исходное состояние объединен с одноименными входами остальных триггеров и подсоединен к выходу элемента 50. Выход элемента ИЛИ 47 является вторым выходом блока, а его первый и второй входы - соответственно третьим и седьмым выходами блока, которые соединены с единичными выходами соответственно триггеров 34 и 35. Последний из них объединен с первым входом элемента И 45, выход и второй вход которого подсоединены соответственно к первому входу элемента ИЛИ 48 и к выходу элемента ИЛИ 49. Первый и второй входы элемента ИЛИ 49 являются соответственно третьим и пятым входами блока, которые подсоединены к вторым входам соответственно элементов И 44 и 43. Выходы последних подсоединены соответственно к единичному входу триггера 36 и второму входу элемента ИЛИ 48, третий вход которого является шестым выходом блока и соединен с единичным выходом триггера 36. Нулевой вход триггера 36 является четвертым входом блока, первым входом которого является нулевой вход триггера 35, который объединен с вторым входом элемента И 42. Выход элемента И 42 подсоединен к единичному входу триггера 35, единичный вход триггера 34 соединен с выходом элемента ИЛИ 48, а его нулевой вход является шестым входом блока.

Предложенный АЦП работает следующим образом.

После включения питания на время переходных процессов на шинах питания элемент 50 задержки поддерживает на выходе сигнал с нулевым уровнем. Это обеспечивает установку в исходное нулевое состояние триггеров 34-37. Сигналы с их нулевых выходов с помощью элемента И 41 образуют сигнал 54 на четвертом выходе блока 33, который проходит через элемент ИЛИ 28 и с помощью ключа 13 поддерживает в исходном состоянии интегратор 4, а также разрешает работу элемента И 22. Отсутствие сигналов на остальных выходах блока 33 (кроме импульсов генератора 38 на пятом выходе) запрещает работу элементов И 21, 23-26 и соответственно счетчиков 14, 16 и 17. В этом состоянии АЦП готов к началу преобразования, которое выполняется по внешним импульсам синхронизации 51. Эти импульсы устанавливают в ноль счетчики 14 и 17, а также синхронизируют начало очередного импульса в генераторе 38, пройдя через элемент ИЛИ 46 (импульс 66). Первый из импульсов 51 проходит через элемент И 22, образуя импульс 52, который устанавливает в ноль счетчики 15 и 16 и в единицу триггер 37.

С установкой в единицу триггера 37 появляется сигнал 55 и начинается интегрирование Uх интегратором 4, так как сигнал 54 снимается, ключ 13 размыкается, а ключ 11 подключает Uх через резистор 5 к интегратору 4. Сигнал 55 разрешает работу элемента И 21, через который проходят импульсы генератора 38, имеющие период повторения t, на вход счетчика 14 (через элемент ИЛИ 30). Емкость счетчика 14 равна No, и на его выходе появляется импульс переполнения через время to = Not, которое подсчитывается счетчиком 16.

Процесс интегрирования Uх и подсчета импульсов tо продолжается до появления второго импульса 51, по которому заканчивается время измерения Uх, равное интервалу Ти между этими двумя импульсами 51.

За время Ти в счетчике 16 получен код Nи=  =

=  , а в интеграторе - выходное напряжение 60, равное -Uи = k Uх Ти, которое может при больших величинах Uх и Ти превышать его рабочий диапазон, что недопустимо.

, а в интеграторе - выходное напряжение 60, равное -Uи = k Uх Ти, которое может при больших величинах Uх и Ти превышать его рабочий диапазон, что недопустимо.

Для исключения этого напряжения -U сравнивается с помощью компаратора 8 с напряжением 61, равным -Uо и рабочему диапазону интегратора 4. При -U = -Uо компаратор 8 срабатывает, его выходной импульс 62 проходит через элемент ИЛИ 28 и с помощью ключа 13 разряжает конденсатор интегратора 4.

Процесс интегрирования Uх продолжается с исходного состояния интегратора 4, а импульсы 62 подсчитываются счетчиком 15. В зависимости от величин Uх и Ти, наименьшая величина которого равна Noto, может происходить различное число q срабатываний компаратора 8. На фиг. 3 в качестве примера показаны три случая:

q1 = 3, q2 = 1 и q3 = 0.

За время Ти интегрирования Uх напряжение Uи на выходе интегратора 4 может изменяться q раз по Uо и к окончанию Ти на его выходе может остаться напряжение U1, т. е. общее изменение этого напряжения равно Uи = q Uo + U1 = k Uх Ти.

С окончанием Ти напряжение U1 может быть равно нулю при Uх = 0 или при совпадении импульсов 62 с моментом окончания Ти. Из этих состояний интегратора 4 с помощью нуль-органа 7 образуется сигнал 63, который используется для управления дальнейшей работой АЦП и при разынтегрировании U1 напряжением -Uо.

По окончании Ти дальнейший процесс получения результата преобразования путем разынтегрирования U1 и компенсационного интегрирования Uо выполняется в последовательности, определяемой тремя сигналами: 63 с выхода нуль-органа 7, 65 и 64 с выходов соответственно элементов И 27 и ИЛИ 31, которые по коду q счетчика 15 формируют эти сигналы для q = 1 и для q ≥ 2. Кроме приведенных на фиг. 3 трех примеров соотношений этих сигналов могут быть еще три случая, когда сигнал 63 имеет нулевой уровень и при отсутствии одного из сигналов 65 или 64, а также при отсутствии их обоих.

С учетом этих шести комбинаций сигналов в блоке 33 формируются сигналы управления на выполнение режимов разынтегрирования и компенсационного интегрирования, а также сигналы управления счетчиком 17, коммутатором 20 кодов и делителем 19 частоты, которые формируют различные временные кванты tи и tq для этих режимов работы АЦП при преобразовании их длительностей в коды, сумма которых представляет собой результат преобразования.

Окончание Ти происходит по второму импульсу 51, который проходит через элемент И 40 и образует импульс 53. Этот импульс устанавливает в ноль триггер 37, его сигнал 55 снимается, прекращаются интегрирование Uхи подсчет импульсов генератора 38 счетчиком 14. Импульс 53 проходит через те элементы И 42, 43 и 44, работа которых разрешена сигналами 63, 65 и 64, на единичные входы триггеров 35, 34 и 36.

Для случая наличия сигналов 63 и 64 (первый приведенный пример на фиг. 3 с q = 3) импульс 53 проходит через элементы И 42 и 44 и устанавливает в единицу триггеры 35 и 36. Сигнал 56 первого из них разрешает работу элементов И 23 и 45 и, пройдя через элемент ИЛИ 47 (сигнал 59), с помощью ключа 12 подключает к резистору 5 и далее к интегратору 4 напряжение -Uо с выхода источника 6, которое прошло на выход переключателя 10, так как на его управляющем входе сигнал с третьего выхода блока 33 отсутствует. В интеграторе начинается разынтегрирование остаточного напряжения U1 напряжением -Uо. Этот процесс продолжается до момента получения равенства -U1 = -k UoTp, когда выходной сигнал 63 нуль-органа снимается и устанавливает в ноль триггер 35, снимая сигнал 56.

В течение Тр счетчик 14 подсчитывает импульсы с выхода делителя 18, которые проходят на его счетный вход через элементы И 23 и ИЛИ 30. На импульсный вход делителя 18 поступают от генератора 38 импульсы с периодом t, число которых делится на величину кода Nи=  , поступающего с выходов счетчика 16, и на выходе делителя 18 появляются импульсы с периодом повторения tи = Nиt = Ти/Nо.

, поступающего с выходов счетчика 16, и на выходе делителя 18 появляются импульсы с периодом повторения tи = Nиt = Ти/Nо.

Делитель 18 частоты может быть, например, выполнен на основе счетчика, выходы разрядов которого соединены с первыми входами схемы сравнения кодов. Ее вторые входы являются информационными входами делителя, а выход соединен с первым входом элемента И, второй вход которого соединен через элемент задержки с входом делителя и со счетным входом счетчика, а выход является выходом делителя и соединен с первым входом элемента ИЛИ, выход которого подсоединен к входу установки в ноль счетчика, а второй вход является входом установки в ноль делителя. При получении в счетчике делителя 18 кода Nи, т. е. через время tи после установки в ноль, схема сравнения кодов разрешает прохождение импульса от элемента задержки на выход. Этот же импульс через элемент ИЛИ устанавливает ноль в счетчике, и процесс деления числа импульсов на Nипродолжается с получением выходных импульсов с периодом повторения tи. При подаче импульса на вход установки в ноль делителя осуществляется его синхронизация, обеспечивающая появление первого импульса на выходе делителя через время tи независимо от состояния, в котором находился счетчик перед поступлением импульса синхронизации.

В качестве синхронизирующих импульсов перед началом разынтегрирования для делителя 18 используются импульсы 51, которые проходят через элемент ИЛИ 29. В результате подсчета импульсов с выхода делителя 18 за время Тр в счетчике 14 получен код

X1=  =

=

С установкой в единицу триггера 36 его сигнал 58 разрешает работу элемента И 26 и подключает с помощью коммутатора 20 код с выхода счетчика 15 на входы делителя 19 частоты, который выполнен аналогично делителю 18 и так же, как он, устанавливается в ноль импульсами 51, проходящими через элемент ИЛИ 32. На выходе делителя 19 формируются импульсы с периодом повторения t1 = qt, которые проходят через элемент И 26 на счетный вход счетчика 17, установленного в ноль импульсами 51.

Длительность сигнала 58 равна tи, так как триггер 36 устанавливается в ноль первым импульсом с выхода делителя 18. За это время в счетчике 17 получен код

Nq=  =

=  =

=  .

.

Сигналы 58 и 56 (последний через элемент И 45, работа которого разрешена сигналом 64, прошедшим через элемент ИЛИ 49), поступают на входы элемента ИЛИ 48, на выход которого проходит сигнал с наибольшей длительностью, и его снятие устанавливает в единицу триггер 34. Его сигнал 57 проходит через элемент ИЛИ 47 и оставляет включенным ключ 12, он поступает также на управляющий вход переключателя 10, подключая к его выходу напряжения Uо с выхода инвертора 9, и на входы элементов И 24 и 25.

В интеграторе 4 начинается компенсационное интегрирование напряжения Uо, которое продлится в течение времени Тк до срабатывания компаратора 8 при равенстве напряжений -Uи = -Uo = -k Uо Тк. Выходной импульс 62 компаратора 8 устанавливает в ноль триггер 34, сигнал 57 снимается и компенсационное интегрирование заканчивается. На его выполнение требуется время

Tk=  = 1/k.

= 1/k.

С появлением сигнала 57 по снятии сигнала с нулевого выхода триггера 34 запускается формирователь 39 и его импульс синхронизирует работу генератора 38 (импульсы 66) и делителей 18 и 19 частоты (через элементы ИЛИ 29 и 32).

На информационные входы делителя 19 с помощью коммутатора 20 подается код Nq с выходов счетчика 17, так как сигнал 58 на его управляющем входе отсутствует. На выходе делителя 19 формируются импульсы, период повторения которых равен

tq= Nqt=  ·t=

·t=  =

=  =

=  .

.

Для исключения накапливаемой в процессе формирования tq погрешности от ошибки квантования в Nq, которая могла иметь место при преобразовании tи в Nq с помощью временных квантов t1, работа делителя 19 синхронизируется импульсами с выхода делителя 18, которые проходят через элемент ИЛИ 32 на его вход установки в ноль.

Импульсы с выхода делителя 19 проходят через элемент И 25, работа которого разрешена сигналами 64 и 57, и подсчитываются счетчиком 14. За время Тк код Х1 счетчика 14 увеличивается на

X2=  =

=  , и в нем формируется код результата преобразования Хр = Х1 + Х2.

, и в нем формируется код результата преобразования Хр = Х1 + Х2.

Со снятием сигнала 57 возникает сигнал 54, который устанавливает в исходное состояние интегратор 4 и информирует, что на выходной шине 3 находится результат преобразования Хр. Код Хр соответствует среднему значению сигнала Uх, полученному за время Ти его интегрирования с квантом преобразования Δ =  . Действительно, подставляя в выражение для Хр значения Х1 и Х2, выраженные через tи и tq, а затем значения последних, выраженные через Ти, получают

. Действительно, подставляя в выражение для Хр значения Х1 и Х2, выраженные через tи и tq, а затем значения последних, выраженные через Ти, получают

Xp=  +

+  =

=

+

+  = N

= N (U1+qUo).

(U1+qUo).

Величина в скобках соответствует напряжению Uи, на которое изменяется выходное напряжение интегратора 4 за время Ти, т. е. Uи = k UхТи = (U1 + q Uо).

Поэтому величина Хр равна

Xp=  =

=  · No=

· No=  .

.

Она не зависит от длительности Ти измерения Uх, и на ее получение затрачено время Тр + Тк, которое значительно меньше по сравнению с прототипом благодаря уменьшению в q раз времени компенсационного интегрирования. Это существенно уменьшает затраты времени на выполнение преобразования и повышает быстродействие АЦП.

Для других комбинаций сигналов 63, 64 и 65 блок 33 также обеспечивает необходимые выходные сигналы управления работой АЦП. Так, в рассмотренном примере наличие к окончанию Ти сигнала 64 и отсутствие сигнала 63 приводит к выполнению только одного такта Тк компенсационного интегрирования Uо без выполнения разынтегрирования в связи с тем, что U1= 0. В этом случае после Ти сначала выполнен такт tи с получением кода Nq в счетчике 17 для формирования временного кванта tq, как это было описано выше, а затем по снятии сигнала 58, который проходит через элемент ИЛИ 48, благодаря отсутствию сигнала с выхода элемента И 45, так как отсутствует сигнал 56, устанавливается в единицу триггер 34, по сигналу 57 которого выполняется такт Тк с временным квантом работы tq. Для этого случая в выражении для Хр величина U1 = 0, a q соответствует коду, полученному в счетчике 15.

Во втором примере, приведенном на фиг. 3, q = 1, поэтому к окончанию Ти сигнал 64 отсутствует и имеется сигнал 65. При наличии сигнала 63 в АЦП выполняется разынтегрирование за время Тр и компенсационное интегрирование за время Тк. При этом временной квант преобразования в код этих временных интервалов одинаков и равен tи, так как разрешается работа элементов И 23 и 24 соответственно сигналами 56, 57 и 65. Если в этом примере сигнал 63 к окончанию Ти отсутствует, то импульс 53 проходит через элементы И 43 и ИЛИ 48 и устанавливает в единицу триггер 34, т. е. сразу начинается компенсационное интегрирование Uо, по окончании которого получен результат преобразования Хр = Х2. Для этого случая в выражении для Хр величины U1 = 0 и q = 1. Третий пример фиг. 3 соответствует q = 0, поэтому к окончанию сигналы 64 и 65 отсутствуют и при наличии сигнала 63 выполняется только такт разынтегрирования с временным квантом tи преобразования Тр в код Хр. Для этого примера в выражении для Хр величина q = 0, а при отсутствии сигнала 63 величины U1= 0 и q = 0, что означает Uи = 0 и Uх = 0. В последнем случае преобразование заканчивается с окончанием Ти, так как отсутствие сигналов 63, 64 и 65 выключает из работы элементы И 42, 43 и 44 и через них импульс 53 не проходит на триггеры 34, 35 и 36, которые остаются в нуле, и с установкой в ноль триггера 37 в элементе И 41 формируется сигнал 54, информирующий об окончании преобразования, а в счетчике 14 остается без изменения после установки в ноль импульсами 51 код Хр = 0.

Все это показывает, что в предлагаемом АЦП, как и в прототипе, время измерения преобразуемого сигнала может быть задано произвольно по внешним сигналам и для подавления помехи оно может быть кратно периоду помехи или ее гармоник. Если в течение этого времени выходное напряжение интегратоpа перекрывает его рабочий диапазон, то работа АЦП не нарушается и это может произойти многократно до q раз. В этом случае преобразование выполняется до получения окончательного результата с установленной для АЦП точностью и на него не оказывают влияние изменения в широких пределах времени Ти измерения преобразуемого напряжения.

В отличие от прототипа, в котором при изменении Ти, приводящем к q-кратному срабатыванию компаратора, происходят соответствующее изменение времени компенсационного интегрирования и увеличение времени преобразования, в предлагаемом АЦП благодаря формированию с помощью делителей частоты различных временных квантов: tи для выполнения разынтегрирования в течение Тр, t1 для дальнейшего формирования временного кванта tq, используемого в течение Тк при компенсационном интегрировании, и использованию tи и tq для преобразования временных интервалов Тр и Тк в коды Х1 и Х2 результата преобразования затраты времени на получение последнего сокращены в q раз, что уменьшает общее время преобразования и повышает быстродействие АЦП.

Таким образом, предлагаемый АЦП решает поставленную перед ним задачу, направленную на устранение недостатка прототипа, по сравнению с которым достигается повышение быстродействия его работы.

Необходимо также отметить, что по сравнению с прототипом в предлагаемом АЦП устранены дополнительные погрешности, обусловленные в прототипе необходимостью преобразования кода, который получается при измерении времени интегрирования, в напряжение компенсационного интегрирования с помощью ЦАП, работающего в режиме переключения знака опорного напряжения. Эти погрешности в предлагаемом АЦП устранены, так как такого преобразования и наличия ЦАП в нем не требуется, что достигнуто благодаря образованию временных квантов работы АЦП при получении результата преобразования, которые формируются из результата измерения полного времени интегрирования преобразуемого сигнала и с помощью делителей частоты, которые основываются на пересчете импульсов без применения аналоговых элементов.

Изобретение относится к импульсной технике, в частности к преобразователям напряжения в цифровой код с интегрированием преобразуемого напряжения, и может быть использовано в устройствах сбора аналоговой информации систем контроля и управления, выполняемых на средствах вычислительной техники. Целью изобретения является повышение быстродействия преобразователя за счет уменьшения времени компенсационного интегрирования и получения результата преобразования. Для этого в аналого-цифровой преобразователь, содержащий интегратор, нуль-орган, компаратор, источник опорного напряжения, инвертор, три ключа, переключатель, резистивный элемент, четыре счетчика, делитель частоты, блок управления и элементы И и ИЛИ, введены коммутатор кодов, второй делитель частоты, четыре элемента И и элемент ИЛИ. 1 з. п. ф-лы, 3 ил.

Авторы

Даты

1994-04-30—Публикация

1991-05-06—Подача