вычитающем счетчике, группе резисторов, группе аналоговых переключателей, формирователе импульсов стабильной длительности, выполненном на элементе И и счетчике, причем входы первого и второго операционных усилителей-инве торов соединены соответственно с шестым и седьмым входами аналогового блока, а через первый и второй аналоговые ключи - соответственно с входами первого и второго преобразователей напряжения в частоту, которые через третий и четвертый аналоговые ключи соединены с выходами соответственно первого и.второго операционных усилителей-инверторов, при этом входы управления первого и третьего аналоговых ключей соединены соответственно с перввлм и вторым входами аналогового блока, а входы управления второго и четвертого аналоговых ключей соединены соответственно с первым и вторым выходами формирователя импульсов стабильной длительности, первый и второй входы которого соединены соответственно с выходом -первого преобраэ(ователя напря:жения ,в частоту и четвертым входом аналогового блока, пятый вход которого соединен с входом вычитающего счетчика, вход сброса которого соединен с третьим входом аналогового блока, а выходы с управляющими входами группы аналоговых переключателей, входы и выходы которых соединены соответственно с первым и через группу резисторов - с вторыми входами кор рекции каждого преобразователя напряжения в частоту, выход из которых соединен с выходом аналого вого блока.

3.Преобразователь по п. 1, о т личаю щийся тем, что устройство управления выполнено на нуль-оргaнe счетчике, дёшифраторе и сдвиговом регистре, причем вход нуль-органа соединен с входом устройства управления, выход - .с входом счетчика, выходы которого подключены к входам дешифратора и входу сдвигового регистра, а выходы дешифратора и сдвигового .регистра соединены соответственно с первыми и вторыми выходами устройства управления.

4.Преобразователь по п. 1, о т лйчаювдийся тем, что сумматор частот выполнен на 1црсти триггерах, СДВИ.ГОВОМ регистре, четырех элементах ИЛИ, трех ключах и инверторе, причем входы синхронизации первого, второго и третьего триггеров соединены соответственно с пятым, шестым

и седьмь входами сумматора частот, R-входы - соответственно с выходами четвертого, пятого и шестого триггеров и через ключи - с входами первого элемента ИЛИ, а выходы - соответственно с D-входами четвертого .пятого и шестого триггеров, входы синхронизации которых соединены с выходами сдвигового регистра, а R-входы объединены и соединены через инвертор с входом сдвигового регистра и восьмым входом сумматора частот, при этом первые входы второго, третьего и четвертого элементов ИЛИ соединены соответственно с вторым, третьим и четвертым входами сумматора частот, а вторые входы объединены и соединены с первым входом сумматора частот, а выходы - с управляющими входами клюг чей, причем выход первого элемента ИЛИ соединен с выходом сумматора частот.

5.Преобразователь по п. 1, о тличающийс я тем, что цифровой интегратор выполнен на реверсивном , триггере и элементе задержки, причем вход реверсивного счетчика соединен с первым входом цифрового интегратора, реверсивные входы - с. входами реверса цифрового интегратора, вход сброса с вторым входом цифрового интегратора и через элемент: задержки - с R-входом триггера, первый выход с входом синхронизации триггера/ а вто1яле его выходы и выход триггера соединены соответственно с вторыми и первым выходами ци Фовогр интегратора.

6.Преобразователь по п. 1/ отличающий с я тем, что блок деления на период выполнен на

I реверсивном счетчике-регистре, триггере, регистре, счетчике, делителе частоты с переменным коэффшщентом деления, двух элементах И, элементе задержки, вычитающем счетчике и пяти ключах, причем вход записи ре- версйвного счетчика-регистра соеди,нен с входом синхрониэации триггера и первым входом блока деления на период, информационные входы которого подключены к информационным входам реверсивного счетчика-регистра, а четвертый вход - к D-входу триггера, выходы которого соединены с входами реверса реверсивного Счетчика-регистра, выходы которого соединены с входами первого элемента И, выход которого соединен с входом управления первого, второго и третьего ключей, при этом первый вход счетчика соединен с третьим входом блока деления на период, первым входом делителя частоты с переменным коэффициентом деления и через второй и четвертый ключи - соответственно d первым и вторым выходами .блока деления на период, второй вход - с входом сброса вычитгиощего счетчика, втор1ам входом делителя частоты - с переменным коэффициентом деления и через элемент задержки - с входом записи регистра и вторым входом блока деления на период, а выходы счетчика соединены с входами регистра, выходы которого соединены с входами управления делителя частоты с переменным коэффициентом деления, выход ,,которого соединен через первый, третий и пятый ключи соответственно с входом реверсивного счетчика - регистра, третьим выходом блока деления на период и входом вычитающего счетчика, выходы которого соединены с входами второго элемента И, выход которого соединен с управляяжш ми входами четвертого и пятого ключей.

7. Йзрёобразователь по п. 1, о тличающийся тем, что блок маштабированйя выполнен на делителе

частоты с переменным коэффициентом деления, элементах ИЛИ, группе элементов И, пе реключателе управляющего кода, коммутаторе, входы которого соединены соответственно с первыми, третьим, четвертым, пятым и шестым входами блока маоитабирования, втоjaae входы которого соединены с первыми входами элементов И, вторые входы которых соединены с выходами переключателя управляющего кода а

выходы - с входами соответствующих

элементов ИЛИ, выходы которых соединены с входами управления делителя частоты с переменным коэффициентом деления, вход которого соединен с выходом коммутатора, а выход - с

.выходом блока масштабирования, при этом первый вход переключателя управляяяцего кода соединен с шиной питания,

а второй вход - с общей шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь интегральных характеристик электрических величин с мультипликативной автокоррекцией | 1984 |

|

SU1185604A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1986 |

|

SU1320900A1 |

| Аналого-цифровой интегратор | 1982 |

|

SU1037280A1 |

| Устройство для перемещения магнитной ленты | 1990 |

|

SU1705865A1 |

| Логарифмический преобразователь | 1978 |

|

SU765819A1 |

| РАСХОДОМЕР ТОПЛИВА | 1990 |

|

RU2035699C1 |

| Цифровой синтезатор частот | 1990 |

|

SU1748251A1 |

| Вероятностный интегрирующий преобразователь аналог-код | 1987 |

|

SU1441476A1 |

| Устройство для измерения средних значений нестационарных сигналов | 1985 |

|

SU1347028A1 |

| Устройство аналого-цифрового преобразования узкополосных сигналов | 1984 |

|

SU1225014A1 |

1. АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАi ЗОВАТЕЛЬ ИНТЕГРАЛЬНЫХ ХАРАКТЕРИСаИК ЭЛЕКТРИЧЕСКИХ ВЕЛИЧИН, содержавши иэвлейатель корня квадратного, согласующее устройство, входы которого сое- . динены с соответствующими шинами входных сигналов, а первые выходы - с первыми входами аналогового коммутатора, о т л и ч а ю щ и и с я тем, что, с целью повышения точности, надежности и расширения его функциональных возможностей, в него введены источник опорного напряжения, три аналоговых блока, три ключа, сумматор частот, генератор опорной-частоты, цифровой интегратор, элемент задержки, блок деления на период,: блок маелатабирования, элементы-Й, ИЛИ, счетчик результата, триггер паляяти знака, устройство управления,.вход которого соединен с вторым выходом согласующего устройства, первые выходы - соответственно с управляющими Аналогового кЬ|«а5лутатора, с первым, вторым и третьим входами каждого анашогового блока, с входами реверса цифрового интегратора, с первым входом сумматора, с входом элемента задержки,, с первым и вторым входами блока деления на период, с первым и вторым входами блока масштабирования, первым входом элемента И, входом сброса счетчика результата, входами элемента ИЛИ, первым .входом извлекателя корня, вторые входы - соответст венно с рходами управления первого, второго и третьего ключей,с вторым, третьим, четвертым входами сумматора частот, пятый шестой и седьмой входы которого соединены соответственно с выходом каждого- аналогового блока, .всэсьмой вход с выходом генератора опорной частоты, . четвертым входом каждого аналогового. блока, третьим входом блока деления г на период, а выход - с nepBbW вхо,дом цифрового интегратора, второй вход которого соединен с выходом элемента задержки, первый выход - с § .первьш входом триггера памяти знака : и с четвертым входом блока деления О) на период, информационные входы которого соединены с вторыми выходами CZ цифровЬго интегратора, а выходы соответственно с вторым входом извлекате.-- ля корня, третьим, четвертые и пяткмН входами блока масштабирования, шесто: fe вход которого соединен с выходом извлекателя корня, а выход - с входом счетчика результата и с вторым входом со элемента и, выход которого соединен с входами первого, второго и третьегеСЛ ключей, выход каждогр из которых сое динен соответственно с пятым входом ь, каждого аналогового блока, шестой «О и седьмой входаа каждого из которых соединены с выходами аналогового коммутатора, второй вход которого соединен с выходом источника опорного напряжения, при этом второй вход триггера памяти знака соединен с выходом элемента ИЛИ. 2. Преобразователь по пi 1, о тл и ч а ю щ и и с я- тем, что аналоговый блок выполнен на двух операционных усилителях-инверторах, четырех аналоговых ключах, двух преобразователях напряжения в частоту, содержащих каждый стабилизаторы тока и на- пряжения, мультивибратор и резистор.

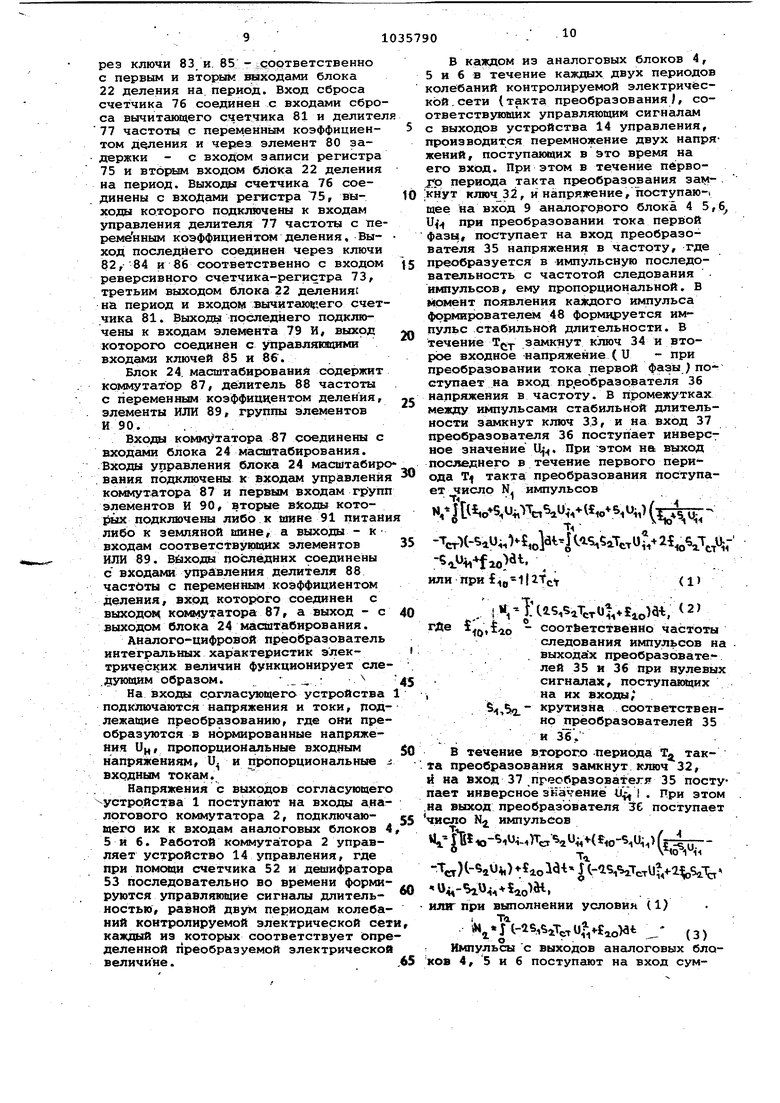

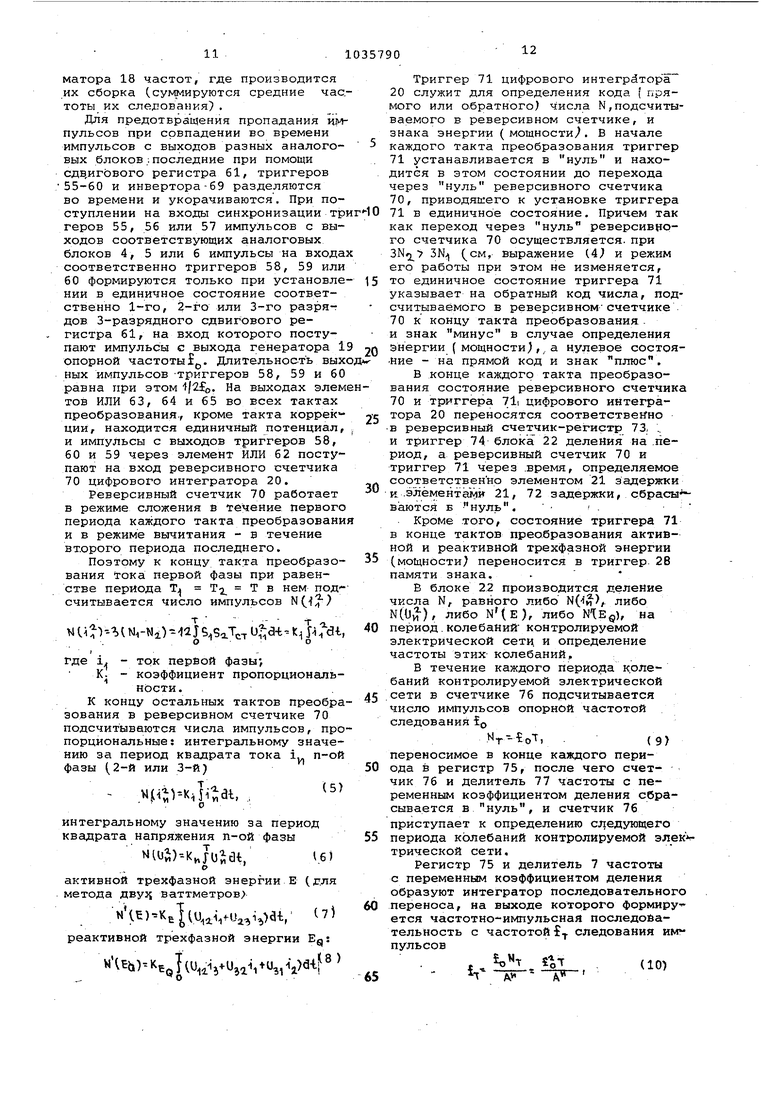

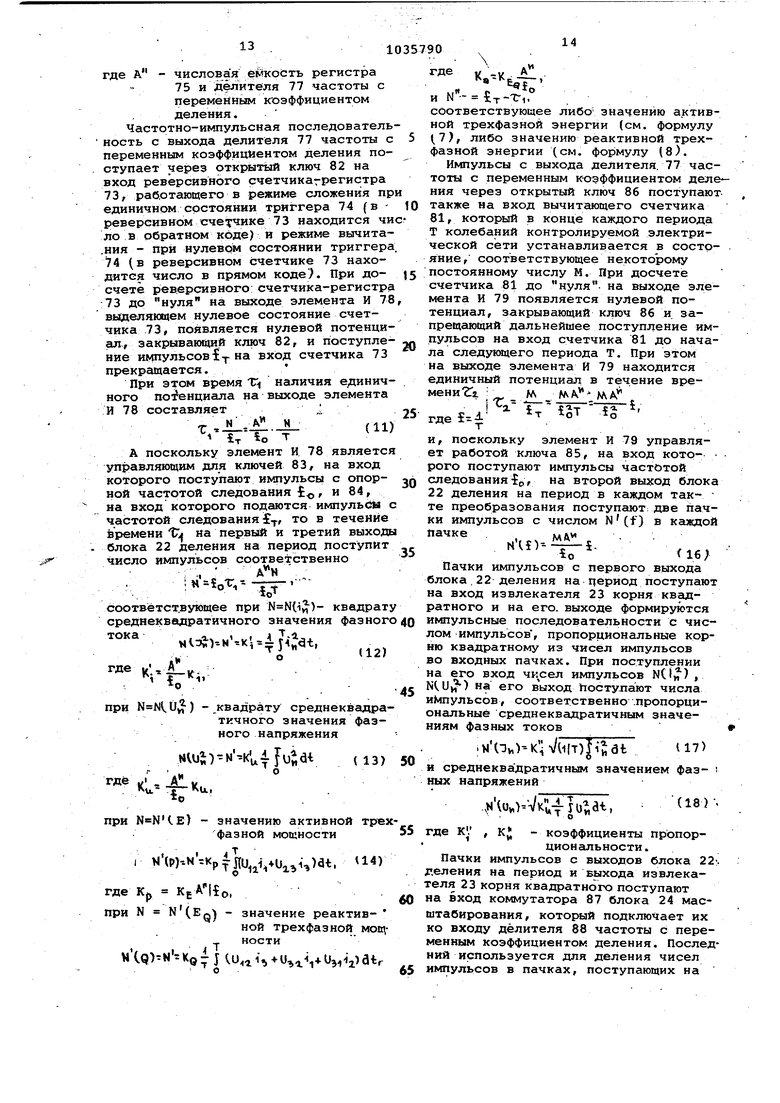

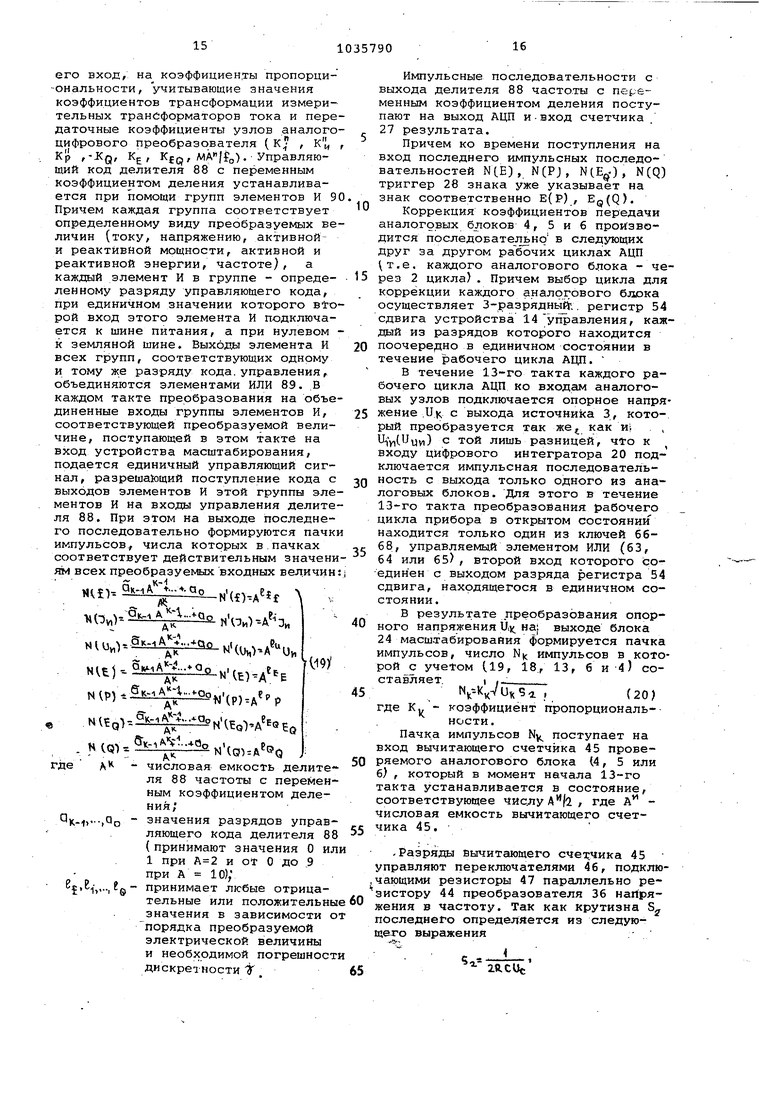

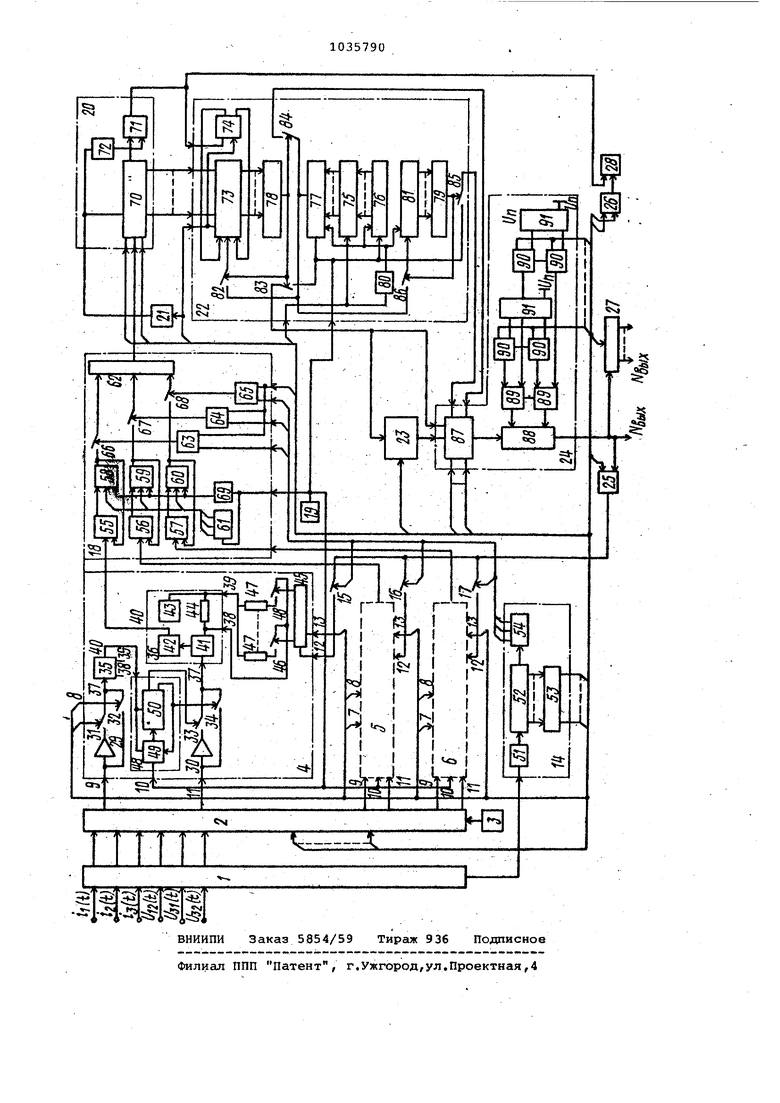

. 1 , Изобретение относится к энергетике и используется в измерительноинформационных системах/ автоматизированных системах управления, где предусматривается контроль и ввод ,данных об интегральных параметрах электрической сети в электронные вычислительные Мсшины для последующей обработки. : Известен измерительный комплекс, содержащий двухтактный преобразователь) напряжение временной интервал, счетчики,- генератор импульсов АЦП, ЦАП, частотомер и устройство коммутации,.преобразующий электрические величины сети в цифрЬвой код. В основу работы комплекса поло жено преобразование базовых величин и, 1, Т,У Ео временной интервал, который затем преобразуется с помощ АЦП и цифровой код; при измерении среднего за период значения напряже ния вначале производится преобразование в постоянный ток величины интеграла абсолютного значения входно го сигнала l3 . Указанное устройство характеризуется низкой точностью преобразования и надежностью. Известен аналого-цифровой преобразователь интегральных характеристик электрических величин, содержащий согласующее устройство, анало говые коммутаторы, усилители выборки и хранения, АЦП, квадраторы, мно житель, синхронизатор, устройство у реднения, интегратор, мйожитель, кв ратор, блок вычитания, извлекатели корня квадратного, интегратор 2. Недостатком данного устройства является также низкая точность преобразования и надежность. Цель изобретения - повышение точ- . ности, надежности и расширение функциональных возможностей за счет преобразования частоты, .масштабирования в Определения направления энергии и мощпости. Поставленная цель достигается тем, что в аналого-цифровой преобразователь интегральных характеристик электрических величин, содержащий иэвлекатель корня квадратного, согле1сующее устройство, входы которого соединены с соответствующими шинами входных сигнсшов, а первые ыходщ - с первыми входс т аналогового коммутатора, введены источник опорного напряжения, три аналоговых блока, три ключа, сумматор частот, генератор, опорной частоты, цифровой интегратор, элемент задержки, блок деления на период, блок масштабирования, элементы И, ИЛИ, счетчик результата, триггер памяти знака, устройство управления, вход которого соединен с вторым выходом согласующего устрой,ства, первые выходы - соответственно с управляющими входами аналогового коммутатора, с первым, вторым и третьим входами каждого аналогового блока, с входами реверса цифрового интегратора, с первым входом сумматора частот, с входом элемента задержки, с первым и вторым входами блока деленйя на период, с первым и вторым входами блока масштабирования, первым входом элемента И, входом сброса счетчика результата, входами элемента ИЛ .входом извлекателя корня, вторые выходы - соответственно с входами упра ления первого, второгои третьего кл чей, с вторым, третьим,.четвертым вх дами сумматора частот, пятый, шестой и седьмой,входы которого соединены соответственно с выходом каждого ан логового блока, восьмой вход - с вы ходом .генератора опорной .частоты, че вертыМ входом каждого аналогового бл ка, третьим входом блока деления на период, а выход - с первым входом цифрового интегратора, второй .вход которого соединен с выходом элемента задержки, первый выход - с первым входом триггера памяти знака и с че вертым входом блока деления на период, информацио 5ные в.ходы которого соединены с вторыми выходами цифрового интегратора, а выходы - соотве ствённо с вторым входом извлекателя корня, третьим, четвертым и пятым входами блока масштабирования, ше- стой вх.од которого соединен с выходо извлекателя корня, а выход - с входом счетчика результата и с вторым входом элемента И, выход которого соединен с входами первого, второго и третьего ключей, выход каждого из которых соединен соответственно с пятым входом каждого аналогового блока, шестой и -седьмой входы каждог.о из которых соединены с выходами аналогового коммутатора, второй вход которого соединен с выходом источника опорного напряжения, при этом второй вход триггера памяти знака соедине.н с выходом элемента ИЛИ. Кроме того, аналоговый блок выполнен на двух операционных усилителях-инверторах, четырех аналоговых ключах,- двух преобразователях напряжения в частоту, содержащих каж дый стабилизаторы тока и напряжения, мультивибратор и резистор, вычитающем счетчике,, группе резисторов группе аналоговых переключателей и формирователе-импульсов стабильной длительности, выполненном на элемен те И и счетчике, причем входы перво . го и второго операционных усилителей-инверторов соединены соответственно с. шестым и седьмым входами .аналогового блока, а через первый и второй-аналоговые ключи - соответственно с входс1ми первого и второ го преобразователей напряжения в час тоту, которые через третий и четвертый аналоговые ключи соединены с выходами соответственно первого и второго операционных усилителей-инверторов, при этом входы управления первого и третьего аналоговых ключей соединены соответственно с первым и вторым.входами аналогового блока, а входы управления второго и четвертого аналоговых ключей соединены соответственно с первым и вторьсм выходами формирователя импульсов стабильной длительности, первый и второйвходы которого соединены соответственно с выходом первого преобразователя напряжения в частоту и четвертым входом аналогового блока, пятый вход которого соединен с входом вычитающего счетчика, вход сброса которого соединен с третьим входом аналогового блока, а выходы - с управляющими вхо дами группы аналоговых переключателей входы и выходы которых соединены со- . ответственно с первым и через группу резисторов - с вторыми входами коррекции каждого преобразователя напряжения в частоту, выход iToporo из которых соединен с.йыходом аналогового блока. Кроме того, устройство управления выполнено на нуль-органе,, счетчике, дешифраторе и сдвиговом регистре, причем вход нуль-органа соединен с входом устройства управления, а вы-, ход - с входом счетчики, выходы которого подключены к входам дешифратора и. входу сдвигового регистра,, а выходы дешифратора и сдвигового регистра соединены соответственно с первыми и вторыми выходами устрой- ства управления,/, ; . . Сумматор частот выполнен на шести триггерах сдвиговом регистре, четырех элементах ИЛИ, трех ключах и инверторе, причем входы синхронизации первого, второго и третьего триггеров соединены соответственно с пятым, шестым и седьмым входами сумматора частот, R-входы - соответственно с выходами четвертого, пятого и шестого триггеров и через ключи - с входами первого элемента ИЛИ, а выходы - соответственно с D-входами четвертого, пятого и шестого триггеров, входы синхронизации которых соединены с выходами сдвигового регистра, а К-вхбды объединены и соединены через инвертор с входом сдвигового-регистра и восьмым входом сумматора частот, при этом первые входы второго, третьего и четвертого элементов ИЛИ соединены соответственно с вторым, третьим и четвертым входами сумматора частот, а вторые входы объединены и соединены с первым входом сумматора частот, а выходы - с управляющими входами ключей, причем выход пербого элемента ИЛИ соединен с выходом сумматора частот.. Цифровой интегратор выполнен на реверсивном счетчике, триггере и элементе згшержки, причем вход реверсивного счетчика соединен с первьлм входом цифрового интегратора, реверсивные входы - с входами реверса цифрового интегратора, вход сброса - с вторым входом цифрового интегратора и через элемент задержки -. с R-входом триггера, первый выход - с входом синхронизации триггера, а вторые его выходы и выход триггера соединены соответственно с вторыми и-первым выходами цифрового интегратора.. Кроме того, блок деления на период .выпоЛнё на реверсивном счетчикерегистре, триггере, регистре, счетчике, делителе частоты с переменным коэффициентом деления, двух элементах И, элементе задержки, вычитающем счетчике и пяти ключах, причем вход записи реверсивного счетчикарегистра соединен с входом синхронизации триггера и первым йходом блока деления на период, информационные входы которого подключены кинформационным входам реверсивного счетчика-регистра, а четвертый вход -. к D-входу триггера, выхода которого соединены с входами реверса реверсивного счетчика-регистра, выходы последнего соединены с входами первого элемента И, выход которого соединен с входом управления .первого; второго и третьего ключей, при.этом первый вход счетчика соединен с третьим входом блока деления на период, первым входом делителя частоты -г с переменным коэффициентом деления и через второй и четвертый ключи - соответственно с первым и вторым выходами блока деления на период, второй вход - с входом сброса вычитающе го счетчика, вторым входом делителя частоты - с переменным коэффициентом .деления и чере.з элемент задержки с входом записи регистра и вторым входом блока деления на период, а выходы счётчика соединены с входами регистра, выходы которого соединены с вхЬдамн управления делителя частоты с переменным коэффициен том делени выход которого соединен через первый третий и пятый ключи соответственно с входом реверсивного счетчика-регистра, третьим выходом блока деления на период и входом вычитавмцего счетчика, -выходы которого соединены с входами второго. элемента И, ввасол которого соединен с управляющими входами, четвертого и пятого ключей. Кроме того, блок масштабирования выполнен на делителе частоты с пере менным коэффициентом деления, элемен тах ИЛИ, группе элементов И, переключателе.управляющего кода, коммутаторе, входы которого соединены соо ветственно с первыми, третьим четве .тым, пятым и шестым входами блока масштабирования, вторые входы которого .соединены с первыми входами эле ментов И, вторые входы которых соединены с выходами переключателя упра лякяцего кода, а выходы - с входами соответствующих элементов ИЛИ, выходы которых соединены с входами управления делителя частоты с переменным коэффициентом деления, вход которого соединен с выходом коммутатора , а выход - с выходом блока масштабирования, при этом первый вход переключателя управляющего кода соединен с шиной питания, а второй вход с общей шиной. На чертеже предстанлена структур-; ная- схема предлагаемого аналого-цифрового преобразователя интегргшьных характеристик электрических величин. Аналого-цифровой; преобразователь: . состоит из Согласующего устройства 1, аналогового коммутатора 2, источника 3 опорного напряжения, аналоговых блоков 4, 5 и 6 с входами 7-13, устройства 14 управления, ключей 15, 16 и 1-7, сумматора 18 частот, генератора 19 опорной частоты, цифрового интегратора 20, элемента. 21 -задержки, блока 22 делеН1 я напериод, из-; влекателя 23 корня квадратного, устройств.а 24 масштабирования, элементов И 25, ИЛИ 26, счетчика27 результата и триггера, 28 Ъамяти знака.. Входы согласующего устройства 1 соединены с шинами входных сигналов, а выходы - с входами аналогового.коммутатора 2 и входом устройства 14 управления.. Выходы последнего соедянёвы с управляклцими входами ана(ЛОгового коммутатора 2j входами 7, 8 и 13 аналоговых блокоВ 4, 5 и 6, входами реверса цифрового интегратора 20, входом элемента .21 задержки, BTOiMiEM и третьим входами ..блока 22 деления на период, выходами управления блока 24 масштабирования, первым входом элемента И 25, входом сброса счетчика 27 результата, входами элемента ИЛИ 26. восьмым, пятым, шестым и седьмым входами сумматора 18 частот, входами управления ключей 15, 16 и 17 и вто1«ам входом извлекателя 23 корня квадратного. Входы 9 и 11 аналоговых блоков 4, 5 и 6 соединень с выходами анало)пового коммутатора 2, входа 12 - с выходами ключей 15, 16 и 17, входы которых .соединены с выходам элемента И 25. Выходы аналоговых блоков 4, 5 и 6 соединены соответственно с первым, вторым и третьим входами сумматора 18 частот, четвертый вход которого . соединен с выходом генератора 19 опорной частоты, входами 10 аналоговых блоков, 4, 5 и 6 и первым входом блока 22 деления на период, а выход - с входом цифрового интегратора 20. Вход Сброс последнего подключен к выходу элемента 21 задержки, а выходы - соответственно к информационным входам блока 22 деления на период и входу триггера 28памяти знака, вход синхронизации которого соединен с выходом элемент ИЛИ 26. Выходы блока 22 деления на период соединены соответственно с первым входом извлекателя 23 корня квадратного, первым, третьим и четве тым входами блока 24 масштабирования Второй вход последнего соединен с выходом извлекателя 23 корня квадра ного, а выход - с вторым входом эле мента И 25 и входом счетчика 27 результата. Аналоговый блок 4(5,6) содержит операционные усилители-инверторы 29и 30, аналоговые ключи 31-34, преобразователи 35 и 36 напряжения в частоту, содержащие входы 37, 38 и 39, выход 40, стабилизатор 41 ток мультивибратор 42, стабилизатор 43 напряжения и резистор 44 вычитающий счетчик 45, группу аналоговых переключателей 46, резисторы 47 и формирователь 48 импульсов стабильной длительности, содержащий элемен И 49 и счетчик 50. Входы операционных усилитеЛей 29 и 30 соединены соответственно- с вхо дами 9 и 11 аналогового блока 4(5,6 а. также через аналоговые переключатели 31 и 33 - соответственно с входами преобразователей 35 и 36 напряжения в частоту и выходамианалоговых ключей 32 и 34, входы которых соединены с выходами соответственно операционных усилителей 29 и 30., Вхо ды управления аналоговых переключагелей 31 и 32 подключены соответственно к входам 7 и 8 аналогового блока 4{5,6) . Входы управ;пения аналоговых переключателей 33 и 34 соеди нены соответственно с первым и вторы выходами формирователя 48 импульсов стабильной длительности, первый и вт рой входы которого соединены соответ ственно с выходом 40 преобразователя 35 напряжения в частоту и входом 10 аналогового блока 4(5,6). Вход вычитаиощего счетчика 45 соед нен с входом 12 аналогового блока 4(5,6), вход сброса - с входом 13 аналогового блока 4(5,6), а выходы с управляющими входами аналоговых переключателей 46. Входы и выходы последних подключены соответственно к входу 38 и через резисторы 47 - к входу 39 преобразователя 36 напряжения в частоту йыход 40 которого является выходом аналогового блока 4 5,6 г Устройство 14 управления содержит нуль-орган 51, счетчик 52, Дешифратор 53, сдвиговый регистр 54. Вход нуль-органа 51 соединен с входом устройства 14 управления, а выход с входом счетчика 52. Выходы последнего подключены соответственно к вхо дам дешифратора 53 и входу сдвигового регистра 54. Выходы дешифратора 53 и сдвигового регистра 54 являются выходами устройства 14 управления. Сумматор 18 частот содержит триггеры 55-60, сдвиговый регистр 61 ,U. элементы ИЛИ 62-65, ключи 66, 67и 68 и инвертор 69. Входы синхронизацииптриггеров 55, 56 и 57 соединены соответственно с первым, вторым и третьим входами .сумматора 18 частот, R-входы - соответственно с выходами триггеров 58, 59 и 60 и через ключи 66, 67 и 68 - с входами элемента ИЛИ 62, а выходы - соответственно с D-входами триггеров 58, 59 и 60. Входы синхронизации последних соединены с выходами сдвигового регистра 61, а R-входы объединены и соединены через инвертор 69 с входом сдвигового регистра 61 и четвертым входом сумматора 18 частот. Первые входы элементов ИЛИ 63, 64 и 65 соединены соответственно с ПЯТЕЛМ, шестым и седьмым входами, сумматора 18 частот, вторые входы объединены и подключены к восьмому входу сумматора 18 частот, а выходы - соответственно с управляю-щими в.ходами ключей 66, 67 и 68. Выход элемента ИЛИ 62 является вы содом сумматора 18 частот. Цифровой интегратор 20 содержит реверсивный счетчик 70, триггер 71 и элемент 72 задержки. Вход реверсивного счетчика 70 соединен с входом цифрового интегратора 20, входы реверса - с входами реверса послед него, вход сброса - с входом сброса цифрового интегратора 20 и через элемент 72 задержки с R-входом триггера 71. Выход реверсивного счетчика 70 подключен к входу синхронизации триггера 71, а выходы разрядов реверсивного счетчика 70 и выход триггера 71 являются выходами цифрового интегра тора 20. Блок 22 деления на период содержит реверсивный счетчик-регистр 73, триггер 74, регистр 75, счетчик 76, делитель 77 частоты с переменным коэффициентом деления, элементы И 78 и 79, элемент 80 задержки, вычитающий счетчик 81 и ключи 82-86. Вход записи реверсивного счетчикарегистра 73 соединен с входом синхронизации триггера 74 и третьим входом блока 22 деления на период. Информационные входы последнего подключены к информационным входгйл реверсивного счетчика-регистра 73 и D-BXOду триггера 74, выходы которого соединены с входами реверса реверсивного счетчика-регистра 73. Выхода послед него соединены с входами элемента И 78, выход которого соединен с входом управления ключей 82, 83 и 84. Вход счетчика 76 соединен с первым входом блока 22 деления на период, входом делителя 77 частоты с переменным коэффициентом деления и через ключи 83 и, 85 -,соответственно с первым и вторым №ходами блока 22 деления на период. Вход сброса счетчика 76 соединен с входами сброса вычитакщего счетчика 81 и делител 77 частоты с переменным коэффициентом деления и через элемент 80 задержки - с входом записи регистра 75 и вторым входом блока 22 деления на период. Выходы счетчика 76 соединены с входами регистра 75, выходы которого подключены к входам управления делителя 77 частоты с переменным коэффициентом деления. Выход последнего соединен через ключи 82, 84 и 86 соответственно с входом реверсивного счетчика-регистра 73, третьим выходом блока 22 деления на период и входом вычитаю1{;его счетчика 81. ВыходЕл последнего подключены к входам 79 И, выход которого соединен с управляняфсми входами ключей 85 и в€. Блок 24. масштабирования содержит коглмутатор 87, делитель 88 частоты с переменным коэффиццеВТОМ деления, элементы ИЛИ 89, группы элементов И 90. . Входы коммутатора 87 соединены с входами блока 24 маоштабирования. Входы управления блока 24 масштабиро . вания подключены к входам управления коммутатора 87 и первым входам групп элементов И 90, вторые вЗсоды которых подключены либо к шине 91 питани либо к земляной шине, а выходы - квходам соответствующих элементов ИЛИ 89. В| хода1 последних соединены с входами управления делителя 88 частоты с переменным коэффициентом деления, вход которого соединен с выходоц коммутатора 87, а выход - с выходом блока 24 масштабирования. Аналого-цифровой преобразователь интегральных характеристик электрнческих величин функционирует сле дующим образом. , : На входы согласующега устройства подключаются напряжения и токи, подлежащие преобразованию, где оки преобразуются в нормированные напряжения Цц, прюпорциональные входным напряжениям, U и пропорциональные входным токам. Напряжения с выходов согласующего -устройства 1 поступают на входы аналогового коммутатора 2, подключающего их к входам аналоговых блоков 4 5 и 6. Работой коммута тора 2 управляет устройство 14 управления, где при помощи счетчика 52 и дешифратора 53 последовательно во времени формируются управляющие сигналы длителькостью, равной двум периодам колебаний контролируемой электрической сет каждый из которых соответствует Опре деленной преобразуемой электрической величине. В каждом из аналоговых блоков 4, 5 и 6 в течение каждых двух периодов колебаний контролируемой электрической, сети (такта преобразования/, соответствующих управляющим сигналам с выходов устройства 14 управления, производится перемножение двух напряжений, поступающих в &то время на его вход. При этом в течение пёрвоj43 периода такта преобразования зам:кнут ключ 32, и напряжение, поступаю-1 щее на вход 9 аналогорого блока 4 5,6 Щ при преобразовании тока первой фазы, поступает на вход преобразователя 35 напряжения в частоту, где преобразуется в импульсную последовательность с частотой следования импульсов, ему пропорциональной. В момент появления кгикдого импульса Формихювателем 48 формируется импульс стабильной длительности. В течение T{v замк-нут ключ 34 и второе входное напряжение ( U - при преобразовании тока первой фазыJ поступает на вход преобразователя 36 напряжения в частоту. В промежутках между импульсами стабильной длительности замкнут ключ 33, и на вход 37 преобразователя 36 поступа ет инверсное значение Щ. При этом на выход последнего в течение первого периода Т такта преобразования поступает число N. импульсов V j В VS.U4,,,u,) (),V,,5aTeTU,2{ VcT4r .ii fM}« или npHf o lUTet(1) .- гДе , соотЬетственно частоты следования импульсов на . выходах преобразовате. лей 35 и 36 при нулевых сигналах, поступакяцих ,на их входа, 1 крутизна соответственно .преобразователей 35 я Зб. В течение второго периода Т такта преобразования замкнут ключ 32, ri на ьход 37 преобразоватегя 35 поступает инверсное значение Щ . При этом на выход преобразователя 36 поступает число Нд импульсов V-|BJio- i i-.TV4U«(t«-5,u,(g -fcr)-) 5ао1аЬ |Vas,4TcTllVl Ta ,W. ипя при выполнении условия (1) 4 «jViS,4VUf,-,,o)at (3) Импульсы с выходов аналоговых блоков 4, 5 и 6 поступают на вход сумматора 18 частот, где производится их сборка (.суммируются средние час тоты их следования). Для предотвращения пропадания импульсов при совпадении во времени импульсов с выходов разных аналоговых блоков,; последние при помощи сдв,игЬвого регистра 61, триггеров 55-60 и инвертора-69 разделяются во времени и укорачиваются. При поступлении на входы синхронизации тр геров 55, 56 или 57 импульсов с выходов соответствующих аналоговых блоков 4, 5 или 6 импульсы на входа соответственно триггеров 58, 59 или 60 формируются только при установле НИИ в единичное состояние соответственно 1-го, 2-го или 3-го разрядов 3-разрядного сдвигового регистра 61, на вход которого поступают импульсы с выхода генератора 1 опорной частоты. Длительность вых ных импульсов -триггеров 58, 59 и 60 равна при этом l2fo- На выходах элем тов ИЛИ 63, 64 и 65 во всех тактах преобразования., кроме такта коррекции, находится единичный потенциал, и импульсы с выходов триггеров 58, 60 и 59 через элемент ИЛИ 62 поступают на вход реверсивного счетчика 70 цифрового интегратора 20, Реверсивный счетчик 70 работает в режиме сложения в течение первого периода каждого такта преобразовани и в режиме вычитания - в течение второго периода последнего. Поэтому к концу такта преобразования тока первой фазы при равенстве периода Т Т, Т в нем подсчитывается число импульсов N(lJ) (N,-Ni)j4s SaTcTlJ,a-tlJi.clt, где i. - ток перйой фазы; К. - коэффициент пропорциональности, К концу остальных тактов преобра зования в реверсивном счетчике 70 подсчитываются числа импульсов, про порциональные ; интегральному значению за период квадрата тока i., п-ой фазы (2-й или 3-й) - .. интегральному значению за период квадрата напряжения п-ой фазы O-K Ujjdt, активной трехфазной энергии Е (для метода двуг; ваттметров U),,,)at, 7 реактивной трехфазной энергии Eqt )(U,,,i,tU,,ii)4 Триггер 71 цифрового интегрйтора 20 служит для определения кода ( прямого или обратного) числа N,подсчитываемого в реверсивном счетчике, и знака энергии ( мощности,. В начале каждого такта преобразования триггер 71 устанавливается в нуль и находится в этом состоянии до перехода через нуль реверсивного счетчика 70, приводящего к установке триггера 71 в единичное состояние. Причем так как переход через нуль реверсивррго счетчика 70 осуществляется, при 5Щ (см, выражение (4 и режим его работы при этом не изменяется, то единичное состояние триггера 71 указывает на обратный код числа, подсчитываемого в реверсивномсчетчике 70 к концу такта преобразования . и знак минус в случае определения энергии ( мощности),, а нулевое состоя.ние - на прямой код и знак плюс. В конце каждого такта преобразования состояние реверсивного счетчика 70 и триггера 7li цифрового интегратора 20 переносятся соответстве1 но в реверсивный счет чик-регистр 73. . и триггер 74 блока 22 деления на .период, а реверсивный счетчик 70 и триггер 71 через .время, определяемое соответственно элементом 21 задержки к .элементами 21, 72 задержки, сбрасы- ваются в . . Кроме .того, состояние триггера 71 в конце тактов преобразования активной и реактивной трехфазной энергии (мощности) переносится в триггер. 2В памяти знака. В блоке 22 производится деление числа Nf равного либо либо N(OM)): ибо N(E), либо ЖЕ), на период.колебаний контролируемой электрической сети, и определение частоты этих- колебаний, В течение каждого периода колебаний контролируемой электрической сети в счетчике 76 подсчитывается число импульсов опорной частотой следования (, T-toT,(9) переносимое в конце каждого периода в регистр 75, после чего счетчик 76 и делитель 77 частоты с переменным коэффициентом деления сбрасывается в нуль, и счетчик 76 приступает к определению следующего периода колебаний контролируемой элек трической сети. Регистр 75 и делитель 7 частоты с переменным коэффициентом деления образуют интегратор последовательного переноса, на выходе которого формиру ется частотно -импульсная последовательность с частотой {,. следования им пульсов So «т - П V -SF- -J где А - числовая емкость регистра 75 и делителя 77 частоты с переменным коэффициентом деления. Частотно-импульсная последователь ность с выхода делителя 77 частоты с переменным коэффициентом деления поступает через открытый ключ 82 на вход реверсивного счетчикагрегистра 73, работающего в режиме сложения пр единичном состоянии триггера 74 {в реверсивном 73 находится чи ло в обратном коде) и режиме вычита.ния - При нулевом состоянии триггера 74 (в реверсивном счетчике 73 находится число в прямом коде ). При досчете реверсивного; счетчика-регистра :73 до нуля на выходе элемента И 78 выделяющем нулевое состояние счетчика 73, появляется нулевой потенциал, закрывающий ключ 82, и поступлевне импульсов Y вход счетчика 73 прекращается. При этом время Т наличия единичного потенциала на выходе элемента И 78 составляет I л. ди ы t rtJL-s- ri т о т А поскольку элемент И 78 является управляющим для ключей 83, на вход которого поступают импульсы с опорной частотой следования f, и 84, на вход которого подаются импульЫа частотой следования , то в течение времени 1Г иа первый и третий выходы - блока 22 деления на период поступит число импульсов соответственно : .. Л .соответствующее при (iJJ)- квадрат среднеквбшратичного значения фазного тока , - I I J т.4 .0 1-N--lct--4:J at, к;.-« при ,U) - квадрату среднеквадратичного значения фазного напряжения MuJt N-K iJu ai где v - А о лц.- . Ut IB при NeN4E) - значению активной фазной мощности Я (р)-.мгкр яи,1,из.1,). где Kj, КЕ Alio и N N4EQ) при N N(EQ) - значение реактив- ной трехфазной мощ. ности J и,г1Ч г +1 м2а г о (13) V -V « Е Т И N- , соответствующее либо значению активной трехфазной энергии (см. формулу (7), либо значению реактивной трехфазной энергии (см. формулу (8). Импульсы с выхода делителя. 77 частоты с переменным коэффициентом деления через открытый ключ 86 поступаюттакже на вход вычитающего счетчика 81, который в конце каждого периода Т колебаний контролируемой электрической сети устанавливается в состр- . яние, соответствующее некоторому постоянному числу М. При досчете счетчика 81 до нуля, на выходе элемента И 79 появляется нулевой потенциал, закрывающий ключ 86 и запрещающий дальнейшее поступление импульсов на вход счетчика 81 до начала следукяцего периода Т. При этом на выходе элемента И 79 находится единичный потенциал в течение времени STz где И, поскольку элемент И 79 управляет работой ключа 85, на вход кото-- рого поступают импульсы частотой следования{р, на второй выход блока 22 деления на период в каждом так- те преобразования поступают: две пачки импульсов с числом N(f) в каждой io 16 Пачки импульсов с первого выхода блока 22 деления на период поступают на вход извлекателя 23 корня квадратного и на его. выходе формируются импульсные последовательности с числом импульсов , пропорциональные корню квадратному из чисел импульсов во входных пачках. При поступлении на его вход чисел импульсс1В N(1,) , N4U) на его выход постулают числа импульсов, соответственно .пропорциональные среднеквадратичным значениям фазных токов iN4lv,)-K;- /ll(T) 47) и среднеквадратичным значением фазных напряжений -.мХоИт/к; b,at, где ку , Kj - коэффициенты пропорциональности. Пачки импульсов с выходов блока 22:. деления на период и выхода извлекателя 23 корня квадратного поступают на вход коммутатора 87 блока 24 масштабирования, который подключает их ко входу делителя 88 частоты с переменным коэффициентом деления. Последний используется для деления чисел импульсов в пачках, поступающих на его вход, на коэффициен.ты пропорци-ональности, учитывающие значения коэффициентов трансформации измерительных трансформаторов тока и пере даточные коэффициенты узлов аналого цифрового преобразователя (к , К , Кр ,-JCQ, КЕ, Kfp, MA-lfo). Управляющий код делителя 88 с переменным коэффициентом деления устанавливается при помощи групп элементов И 9 Причем каждая группа соответствует определенному виду преобразуемых ве личин (току, напряжению, активнойи реактивной мощности, активной и реактивной энергии, частоте), а каждый элемент И в группе - определенному разряду управляющего кода, при единичном значении которого вто рой вход этого элемента И подключается к шине питания, а при нулевом к земляной шине. Выходы элемента И всех групп, соответствующих одному и тому же разряду кода.управления, объединяются элементами ИЛИ 89. В каждом такте преобразования на объе диненные входы группы элементов И, соответствующей преобразуемой величине, поступающей в этом такте на вход устройства масштабирования, подается единичный управляющий сигнал, разреша1ощий поступление кода с выходов элементов И этой группы эле ментов И на входы управления делите ля 88. При этом на выходе последнего последовательно формируются пачк импульсов,, числа которых в . пачках соответствует действительным значени яем всех преобразуемых входных величин () Dv,)- bHA±U±Q . .e, ...4.QQ NЧЦ), NlUv, )-° It -K4Er A E ).gK......0o. NAtQ) H(. A - числовая емкость делите ля 88 частоты с перемен ным коэффициентом деления, ,0 - значения разрядов управляющего кода делителя 8 ( принимают значения О ил 1 при и от О до 9 при А 10); К.,,.., 8g - принимает любые отрицательные или положительны значения в зависимости о порядка преобразуемой электрической величины и необходимой погрешност дискретности Т Импульсные последовательности с выхода делителя 88 частоты с переменным коэффициентом деления поступают на выход АЦП и-вход счетчика 27 результата. Причем ко времени поступления на вход последнего импульсных последовательностей NCE), N(PJ, N(.) N(Q) триггер 28 знака уже указывает на знак соответственно Е(Р), Eg(Q). Коррекция коэффициентов передачи аналоговых блоков 4, 5 и 6 производится последовательно в следующих друг за другом рабочих циклах АЦП т.е. каждого аналогового блока - через 2 цикла). Причем выбор цикла для коррекции каждого аналогового блока осуществляет З-разряднь й.. регистр 54 сдвига устройства 14 управления, каждый из разрядов которого находится поочередно в единичном Состоянии в течение рабочего цикла АЦП. В течение 13-го такта каждого рабочего цикла АЦП ко входам аналоговых узлов подключается опорное напряжение .UK с выхода источника 3, который преобразуется так же как Mi Цу,(ицу,) с той лишь разницей, что к входу цифрового интегратора 20 подключается импульсная последовательность с выхода только одного из аналоговых блоков. Для этого в течение 13-го такта преобразования рабочего цикла прибора в открытом состоянии Находится только один из ключей бб6В, управляемый элементом ИЛИ (63, 64 или 65)/ второй вход которого Соединен с выходом разряда регистра 54 сдвига, находящегося в единичном состоянии. В результате преобразования опорного напряжения 1) на| выходе блока 24 масштабирования формируется пачка импульсов, число N|( импульсов в которой с учетом (.19, 18., 13, б и 4) составляет I ,-. N --VUx9a , (20) где Kj. - коэффициент пропорциональности. Пачка импульсов Ny поступает на вход вычитающего счетчика 45 проверяемого аналогового блока {4, 5 или 6), который в момент начала 13-го такта устанавливается в состояние, соответствующее числу А /2, где А числовая емкость вычитающего счетчика 45. -Разряды вычитающего счет.чика 45 управляют переключателями 46, подключающими резисторы 47 параллельно резистору 44 преобразователя 36 найряжения в частоту. Так как крутизна 5, последнего определяется из следующего выражения .5 где R - сопротивление между стабилизаторами 41 и 43 тока и напряжения; С г емкость времязадакяцих конденсаторов преобразователя - зе; .. : . Ui - напряжение иа выходе стаби лизатора 43, и Си Uc явл ются постоявшими г т.е. выражение ( 20) можно-переписать в виде iH,0-Vl/R М UK , (21) где К„ - коэФФици Нт пропорциональ - ностр.. / -.- - / При правильной работе проверяемого аналогового блока (4, 5 или б| и всех остёшьных блоков АЦП, участв кидих в преовразовании U|, число ям пульсов коррекции: Ы равно коэффй-циенту пересчета вьгаитаюцего счетчика 45. При эт п(ри поступлении всей пачки импульсоь N на вход вычитаюиего счетчика 45, последний ус танавливается в. то же состояние, в котором игЬсодился до коррекции, и, следовательно, сопротивление R меж ду стабилизаторами 41 и 43 тока и . напряжения остаётся; без изменения. При .изменении функции преобразования проверяемого ангшогового блока (4, 5, или 6) число корректир псяцих импульсов изменяется на &N|( „в. результате чего в вычктаюкем,счетчике 45 устанга)ливаётся чиcлp )tlДHJ(, чт приводят к изменению сопротивления . R между стабилизаторами 41 и 43 Tokai и напряжения, а следовательно, и числа корректирующих импульсов N,. При двоичном счетчике 45 его 1-ый {разряд управляет подключением к резистору 44 резистора из --группы реЗисзгоров 47 с сопротивлением vCf , где г - .сопротивление резистора 44, п - число разрядов счетчика 45. Таким о разом,. за счёт введения автоматической периодической коррекции коэффициентов передачианалоговых узлов и непрерыВ1рого преобразования контролируемых сигналов в предлагаемом АЦП достигается более высокая точность преобразования. Крсше того, за счет решения вопроса масштабирования преобразуемых сигналов и, следовательно, возможности определения последних в реальном масштабе времени, за счет определения направления преобразуемой мощнОсти и энергии и выполнения преобразования важного пара 4ётра энергообъектов - частоты контролируемых сигналов, а также, за счет того, что п|реобразование реактивной энергии и мОидаостй производится при неизкюнной ст1зукт.уре основного канала преобразования с изменением только порядка к мута1|ии аналогового ксялмутатора расширены функциональные возможности и по81|1Шена надежность-работы устройСУХ9Л :- - .

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| М., Советское радио, 1973, с | |||

| Переносный кухонный очаг | 1919 |

|

SU180A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент Великобритании 1445118, Кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-08-15—Публикация

1981-03-17—Подача