Изобретение относится к цифровой вычислительной технике и к технике связи и может быть использовано для моделирования систем связи, вычислительных систем, систем передачи данных, в которых решение о правильности переданного сообщения принимается на приемной стороне.

Известно устройство для моделирования систем связи, содержащее счетчик, коммутаторы, регистры памяти, регистр максимального числа, регистр минимального числа, схему сравнения, генератор случайного потока импульсов помех. Недостатком известного устройства является то, что не производится проверка кодов передаваемых сообщений на принадлежность заданному классу сообщений, а также не обеспечивается повторная передача сообщений в случаях обнаружения ошибок в прямом канале и ошибок, связанных с влиянием помех в обратном канале связи, и подсчет статистики для дальнейшего определения вероятностных характеристик моделируемой системы.

Наиболее близким по технической сущности к предлагаемому является выбранное в качестве прототипа устройство для моделирования систем связи, содержащее генератор импульсов сообщений, выход которого подключен к счетному входу счетчика переданных сообщений и управляющему входу первого коммутатора, генератор случайного потока импульсов помех, выход которого подключен к управляющему входу второго коммутатора, первый и второй регистры памяти, регистр максимального числа, регистр минимального числа, первую схему сравнения, выход равенства которой подключен к счетному входу счетчика неискаженных сообщений, счетчик сообщений,

VJ N 00

удовлетворяющих критерию проверки, установочные входы всех счетчиков обьедине- ны и являются установочным входом устройства, разрядные входы первого регистра памяти (РП) являются информационным входом устройства, разрядные выходы первого РП подключены соответственно к информационным входам первого коммутатора и входам первой группы первой схемы сравнения, входы второй группы которой соединены соответственно с разрядными выходами второго РП, датчик случайного числа (ДСЧ), вторую и третью схемы сравнения, блок элементов ИЛИ и элемент И, причем выходы первого и второго коммутаторов соединены соответственно с входами блока элементов ИЛИ, выход которого соединен соответственно с оазрядны- ми входами второго РП, разрядные выходы регистра максимального числа соединены соответственно с входами первой группы второй схемы сравнения, а разрядные выходы регистра минимально числа подключены соответственно % к входам первой группы третьей схемы сравнения, входы второй группы второй и третьей схем сравнения подключены соответственно к разрядным выходам второго РП, выход Меньше второй схемы сравнения подключен к первому входу элемента И, второй вход которого соединен с выходом Больше третьей схемы сравнения, выход элемента И подключен к счетному входу счетчика сообщений, удовлетворяющих критерию проверки, а разряд- ные выходы ДСЧ соединены соответственно с информационными входами второго коммутатора.

Недостатком известного устройства является то, что не моделируется работа системы связи при обнаруживаемых и необнаруживаемых ошибках в прямом канале передачи сообщений, когда возможна трансформация сообщения AI в А), принадлежащее заданному классу сообщений, потере данных, ложное повторение данных

Цель изобретения - расширение области применения за счет моделирования режимов передачи сообщений в системах с решающей обратной связью в прямом канале передачи данных.

Данная цель достигается тем, что в устройство для моделирования систем связи, содержащее генератор случайной последовательности импульсов, счетчик, генератор случайного числа, блок элементов ИЛИ, два регистра памяти, два блока сравнения, первый элемент И, генератор случайных импульсов отказов, причем выход генератора случайной последовательности импульсов соединен со счетным входом счетчика, группа выходов первого регистра памяти подключена к первым группам входов первого и второго блоков сравнения, выход второго блока сравнения соединен с первым входом

первого элемента И, введены элемент НЕ, блок элементов НЕ, блок генераторов случайных импульсов отказов, коммутатор, генератор тактовых импульсов, блок памяти, демультиплексор, первый, второй, третий

0 элементы задержки, блок элементов И, с первого по шестой элементы ИЛИ, с первого по пятый триггеры, с второго по седьмой элементы И, блок счетчиков, причем выход генератора случайной последовательности

5 импульсов соединен с первым входом второго элемента И, выход которого подключен к входу запуска генератора случайного числа, группа выходов которого соединена с группой информационных входов второго

0 регистра памяти, группа выходов которого подключена к второй группе соответствующих входов первого блока сравнения и к первой группе соответствующих входов блока элементов И, группа выходов которо5 го подключена к группе соответствующих информационных входов первого регистра памяти, вход обнуления которого, а также вход обнуления второго регистра памяти подключены к выходу первого элемента

0 ИЛИ и нулевому входу первого триггера, инверсный выход которого соединен с вторым входом второго элемента И, а единичный вход первого триггера подключен к выходу второго элемента ИЛИ, группа вхо5 дов которого соединена с группой соответствующих выходов генератора случайного числа, выход второго элемента ИЛИ подключен к первому входу третьего элемента ИЛИ, выход которого соединен с входом

0 записи первого регистра памяти, с входом запуска генератора тактовых импульсов, с нулевым входом второго триггера и через первый элемент задержки - с первым входом третьего элемента И, вход записи вто5 рого регистра памяти подключен к выходу второго элемента ИЛИ, группа входов блока генераторов случайных импульсов отказов через блок элементов НЕ соединена с второй группой входов блока элементов И, вы0 ход первого бюлока сравнения подключен к второму входу третьего элемента И, выход которого соединен с единичным входом третьего триггера, прямой выход которого подключен к управляющему входу демуль5 типлексора, первый и второй выходы которого соединены соответственно с вторым и третьим входами третьего элемента ИЛИ, третий и четвертый выходы демультиплек- сора подключены соответственно к первому и второму входам первого элемента ИЛИ,

выходы с первого по четвертый демультип- лексора соединены с соответствующими входами четвертого элемента ИЛИ, выход которого подключен к нулевому входу четвертого триггера, прямой выход которого соединен с первым входом четвертого элемента И, выход которого подключен к первому информационному входу демультиплексора, выход второго блока сравнения соединен с единичными входами второго и четвертого триггеров и через второй элемент задержки - с вторым входом четвертого элемента И, инверсный выход второго триггера соединен с первым входом пятого элемента И, выход которого подключен к входу Останов генератора тактовых импульсов, входу установки в О коммутатора, к единичному входу пятого триггера, через третий элемент задержки - к первому входу шестого элемента И, к первому входу седьмого элемента И, выход которого соединен с первым входом пятого элемента ИЛИ, выход которого подключен к нулевому входу пятого триггера, выход которого соединен с втор ым входом шестого элемента И, выход которого соединен с вторым входом пятого элемента ИЛИ, выход генератора тактовых импульсов подключен к управляющему входу блока памяти, группа выходов которого соединена с группой соответствующих входов блока элементов ИЛИ, группа выходов которого подключена к второй группе соответствующих входов второй схемы сравнения, выход генератора тактовых импульсов соединен с управляющим входом коммутатора, первый выход которого подключен к второму входу пятого элемента И, а группа выходов, начиная с второго, соединена с группой соответствующих информационных входов блока памяти, выход генератора случайных импульсов отказов через элемент НЕ подключен к вторым входам первого и седьмого элементов И, выход первого элемента И соединен с вторым информационным входом демультиплексора, второй и четвертый выходы которого подключены соответственно к первому и второму входам шестого элемента ИЛИ, выход которого соединен с нулевым входом третьего триггера, первый, второй, третий, четвертый, пятый, шестой входы блока счетчиков соединены соответственно с третьим, первым выходами демультиплексора, выходом седьмого элемента И, выходом шестого элемента И, четвертым, вторым выходами демультиплексора, выход седьмого элемента И подключен к четвертому входу третьего элемента ИЛИ, третьему входу шестого элемента ИЛИ, четвертый вход которого соединен с выходом шестого

элемента И, третьим входом первого элемента ИЛИ.

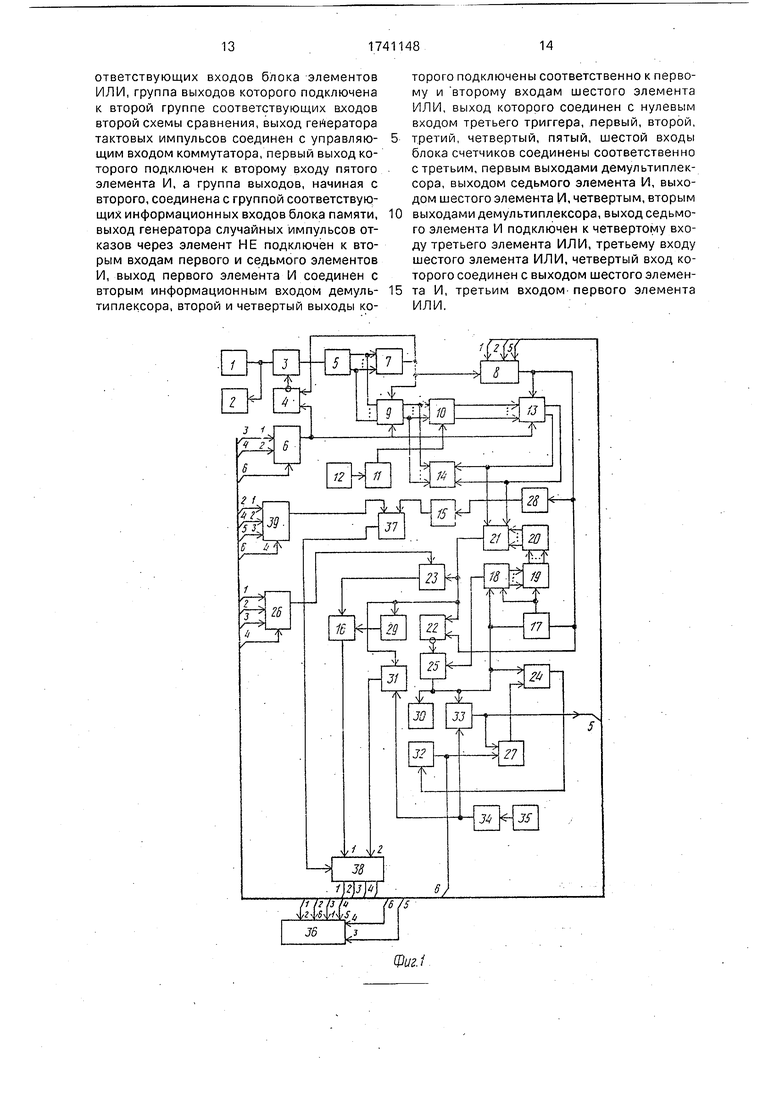

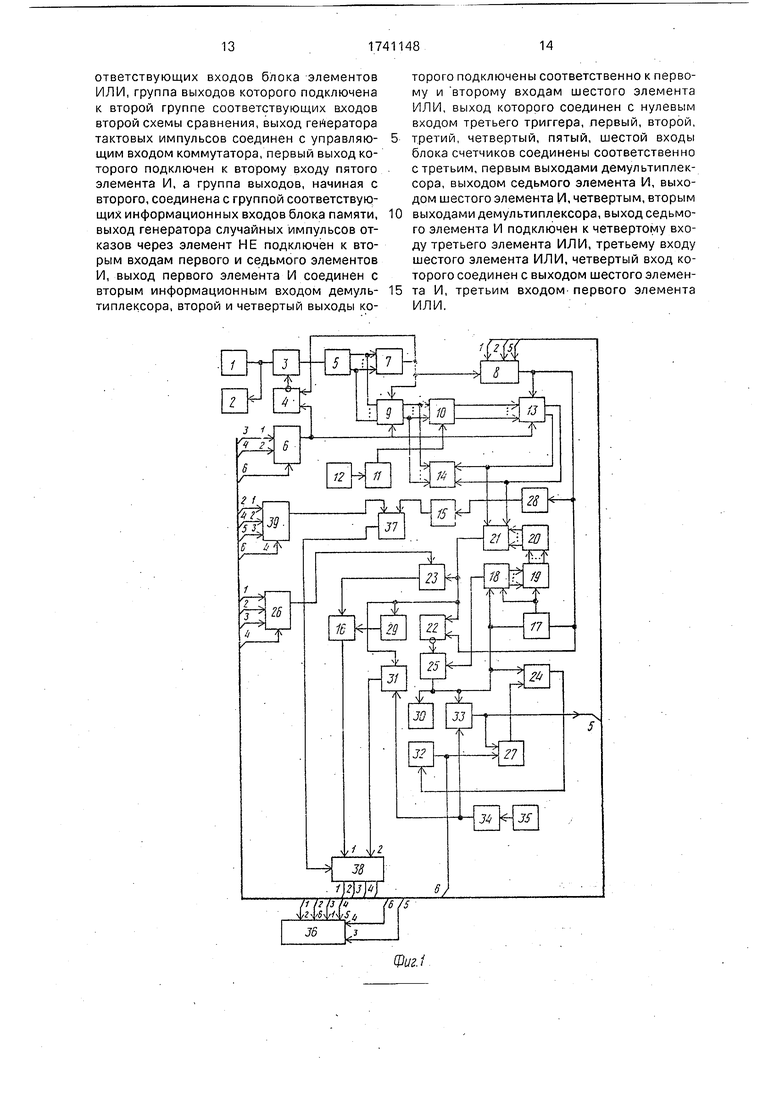

На фиг. 1 представлена функциональная схема устройства для моделирования

систем связи; на фиг. 2 - схема демультиплексора.

Устройство для моделирования систем связи (фиг. 1) содержит генератор 1 случайной последовательности импульсов, счет0 чик 2, второй элемент И 3, первый триггер 4, генератор 5 случайного числа, первый 6, второй 7, третий 8 элементы ИЛИ, второй 9, первый 13 регистры памяти, блок 10 элементов И, блок 11 элементов НЕ, блок 12

5 генераторов случайных импульсов отказов, первый блок 14 сравнения, третий 15, четвертый 16 элементы И, генератор 17 тактовых импульсов, коммутатор 18, блок 19

0 памяти, блок 20 элементов ИЛИ, второй блок 21 сравнения, второй 22, четвертый 23, пятый 24 триггеры, пятый элемент И 25, четвертый 26, пятый 27, элементы ИЛИ, первый 28, второй 29, третий 30 элементы

5 задержки, первый 31, шестой 32, седьмой 33 элементы И, элемент НЕ 34, генератор35 случайных импульсов отказов, блок 36 счетчиков, третий триггер 37, демультиплексор 38, шестой элемент ИЛИ 39.

0 Демультиплексор 38 (фиг. 2) представляет собой объединение двух демультип- лексоров с общим управляющим входом (с прямого выхода триггера 37).

Блоки 14 и 21 могут быть выполнены на

5 микросхемах (МКС) К 555 СП 1 (цифровой компаратор) с задействованием одного из трех выходов МКС.

Блок 36 объединяет шесть однотипных счетчиков, которые в начальный момент об0 нулены.

Генераторы блока 12 и генератор 35 являются генераторами случайной последовательности импульсов.

Выход генератора 1 соединен с входом

5 счетчика 2, а через элемент И 3 - с входом генератора 5, выходы которого подключены к входам элемента ИЛИ 7, информационным входам регистра 9, вход Запись которого соединен с единичным входом

0 триггера 4, выходом элемента ИЛИ 7, первым входом элемента ИЛИ 8, а вход обнуления - с входом обнуления регистра 13, выходом элемента ИЛИ 6. Выходы регистра 9 соединены с второй группой входов блока

5 14, а через бюлок10 - с информационными входами регистра 13, вход записи которого подключен к выходу элемента ИЛИ 8, входу запуска генератора 17, входу О триггера 22, а выходы - к первым группам входов блока 21 и блока 14, выход которого через элемент ИЛ И 15 соединен с входом Т триггера 37, прямой выход которого подключен к управляющему входу демультиплексора 38, а вход О - к выходу элемента ИЛИ 39, первый, второй, третий, четвертый входы которого соединены соответственно с вторым, четвертым выходами ДМ 38, выходами элементов И 33, 32. Первый, второй выходы ДМ 38 через элемент ИЛИ 8, элемент 28 задержки соединены с вторым входом элемента И 15, а третий, четвертый выходы ДМ 38 через элемент ИЛИ 6, триггер 4 - с разрешающим входом элемента И 3. Выходы блока 12 через блок 11 подключены к соответствующим входам блока 10. Выход генератора 17 соединен с управляющими входами коммутатора 18 и блока 19, выходы которого через блок 20 подключены к второй группе входов блока 21, выход которого через триггер 22 соединен с разрешающим входом элемента И 25, через триггер 23 - с разрешающим входом элемента И 16, через элемент 29 задержки, элемент И 16 - с первым информационным входом ДМ 38, второй информационный вход которого подключен к выходу элемента И 31, а выходы через элемент ИЛИ 26 - к входу О триггера 23. Группа выходов, начиная с второго, коммутатора 18 соединена с группой соответствующих информационных входов блока 19, а первый выход через элемент И 25 соединен с входом Останов генератора 17, входом установки в О коммутатора 18, с единичным входом триггера 24, через элемент 30 задержки, элемент И 32 - с четвертым входом блока 36 и третьим входом элемента ИЛИ 6, через элемент И 33 - с третьим входом блока 36, четвертым входом элемента ИЛИ 8, первым входом элемента ИЛИ 27, выход которого через вход О, прямой выход триггера 24 подключен к второму входу элемента И 32, выход которого соединен с вторым входом элемента ИЛИ 27. Выход генератора 35 через элемент НЕ 34 подключен к вторым входам элементов И 33 и 31. Первый, второй, третий, четвертый выходы ДМ 38 также соединены соответственно с вторым, шестым, пятым и первым входами блока 36.

Устройство моделирует систему связи с решающей обратной связью с неограниченным повторением передаваемых сообщений, причем учитываются возможные исходы в прямом канале, в котором передается кодовый сигнал, и в обратном канале, осуществляющем передачу квитанций Да или Нет. Рассматриваются шесть исходов: 1) правильный прием в прямом и обратном каналах; 2) правильный прием в прямом канале, а в обратном канале - трансформация квитанции Да и в Нет (ложное повторение); 3) в прямом канале ошибка обнаружена и в обратном канале передается квитанция 4) в прямом канале ошибка обнаружена, а в обратном квитанция Нет

трансформируется в Да (пропуск сообщения); 5) в прямом канале ошибка не обнаружена и передается квитанция Да (трансформация сообщения); 6) в прямом канале ошибка не обнаружена, а в обратном

0 квитанция Да трансформировалась в Нет (прием ложного сообщения).

Устройство работает следующим образом.

В начальный момент времени все счет5 чики и триггеры - в состоянии О. Генератор 1 случайной последовательности импульсов имитирует факт формирования сообщения для передачи по прямому каналу связи. Эти импульсы подсчитываются в

0 счетчике 2, который перед началом работы обнулен, а также поступают через элемент И 3 на вход запуска генератора 5 случайного числа, на выходе которого вырабатывается ненулевая кодовая комбинация, которая че5 рез входы, выход элемента ИЛИ 7 устанавливает в 1 триггер 4, который в начальный момент времени был в состоянии О, после чего на его инверсном выходе появляется сигнал низкого уровня, и элемент И 3 закры0 вается. Сигнал с выхода элемента ИЛИ 7 является сигналом записи регистра 9, после чего сигнал с выходов генератора 5 записывается в регистре 9, с входов которого через первую группу входов блока 10 элементов И

5 -в регистр 13 по сигналу Записи, поступающему в регистр 13 через элемент ИЛИ 8. Вторая группа входов блока 10 подключена к выходам блока 11 элементов НЕ, входы которого соединены с выходами блока 12

0 случайных импульсов отказов; появление импульса на любом из его выходов соответствует действию помехи в прямом канале связи. Таким образом, в регистре 13 записывается кодовая комбинация, которая

5 сравнивается в блоке 14 сравнения с передаваемым сообщением, зафиксированным в регистре 9. Если кодовые комбинации неравны, то на выходе блока 14 вырабатывается импульс, который действует на первый

0 вход элемента И 15, второй вход которого соединен с выходом элемента ИЛИ 8 через элемент 28 задержки, необходимого для согласования срабатывания обеих групп входов блока 14.

5 Выходы регистра 13 также соединены с первой группой входов блока 21 сравнения, в котором сравнивается принятая комбинация с разрешенными кодовыми комбинациями, хранимыми в блоке 29 памяти, откуда они считываются под действием на информационные входы импульсов с выходов коммутатора 18. Сигнал с выхода элемента ИЛИ 8 запускает генератор 17 тактовых импульсов, с выхода которого импульсы обеспечивают последовательное появление сигнала на группе выходов коммутатора 18. При правильной передаче сообщения в прямом канале на выходе блока 21 в какой-то i-й момент (,п) времени вырабатывается импульс, который установит в 1 триггеры 22 и 23, первый из которых запирает элемент И 25, а второй открывает элемент И 16. Импульс с выхода блока 21 имитирует передачу квитанции Да, которая должна обеспечить передачу следующего сообщения. Сигнал Да через элемент И 31, второй информационный вход демультиплексора 38, его третий выход, ИЛИ 6 сбрасывает в О триггер 4, после чего устройство моделирует передачу следующего сообщения. С выхода элемента ИЛИ 6 сигнал одновременно устанавливает в О регистры 9 и 13. С третьго выхода ДМ 38 сигнал также поступает на первый вход блока 36 счетчиков, где подсчитывается число переданных квитанций Да, а через элемент ИЛИ 26 - на вход О триггера 23, после чего элемент И 16 запирается, и после задержки в элементе 29 импульс через элемент И 16 не пройдет. Однако при срабатывании генератора 25 случайных импульсов, имитирующего отказы в обратном канале, импульс через элемент И 31 не проходит, поэтому сработает элемент И 16, что соответствует ситуации трансформации квинтанции Да в Нет. Импульс с выхода элемента И 16 через первые вход и выход ДМ 38 поступает на второй вход блока 36, где подсчитывается число исходов-ложное повторение, а также через элемент ИЛИ 8 на вход записи регистра 13, обеспечивая запись сообщения в него в условиях возможного влияния помех в прямом канале. Таким образом, имитируется повторная передача сообщения. Поступление разрешенных кодовых комбинаций на вторую группу входов блока 21 осуществляется через блок 20 элементов ИЛИ, входы которого подключены соответствующим выходам блока 19 памяти, съем данных с которого производится под действием сигнала с выхода генератора 17 на его управляющий вход.

Ситуация, когда в прямом канале обнаруживается ошибка, воспроизводится появлением импульса на выходе элемента И 25, так как триггер 22 остается в состоянии О, и с первого выхода коммутатора 18 импульс через элемент И 25 останавливает генерацию в генераторе 17, устанавливает в О коммутатор 18, перебрасывает в 1 триггер

24 и поступает на входы элемента И 33 и элемента 30 задержки, где имитируется передача квитанции Нет. Если сигнал на выходе элемента И 33 выработался, то это

означает, что квитанция Нет по обратному каналу передана успешно, этот импульс одновременно поступает на третий вход блока 36 для подсчета, через элемент ИЛИ 27 устанавливает в О триггер 24, через элемент

0 ИЛИ 39 - триггер 37, а через элемент ИЛИ 8 производит перезапись сообщения в регистр 13, имитируя этим повторную передачу сообщения. Если же в обратном канале квитанция Нет трансформировалась в

5 Да, то импульс через элемент И 33 не проходит, так как в генераторе 35 вырабатывается импульс, имитирующий факт искажения в обратном канале. Импульс после задержки в элементе 30 на время, соответ0 ствующее длительности прохождения сигнала через элемент И 33,через элемент И 32 действует на соответствующий вход элемента ИЛИ 6, обеспечивая передачу следующего сообщения, через элемент ИЛИ 39

5 устанавливает в О триггер 37, через элемент ИЛИ 27 перебрасывает в О триггер 24, а также фиксируется на четвертом входе блока 36.

Пусть в прямом канале ошибка не обна0 ружена, т.е. в результате передачи сообщения трансформировалась в разрешенное сообщение, хотя и другое по смысловому содержанию. В этом случае срабатывают блок 14 и элемент И 15, триггер 37 устанав5 ливается в состояние 1. Импульсе выхода блока 21, имитирующий передачу квитанции, действует аналогично вышеизложенному: через элементы 29, И 16 - на первый вход ДМ 38, а через элемент И 31 - на второй

0 вход ДМ 38, на управляющий вход которого поступает напряжение с прямого выхода триггера 37. В этом случае с второго входа ДМ 38 сигнал проходит на четвертый выход ДМ 38, а затем на второй вход элемента

5 ИЛИ 6, обеспечивая моделирование передачи следующего сообщения, а через элемент ИЛИ 39 сбрасывает в О триггер 39, который управляется и с второго выхода ДМ 38, которой срабатывает в случае приема

0 ложного сообщения, когда квитанция Да преобразовалась в Нет. Импульсе второго выхода ДМ 38 через элемент ИЛИ 8 обеспечивает перезапись сигнала в регистр 13, устанавливает в О триггер 23 через элемент

5 ИЛИ 26. Информация с четвертого и второго выходов ДМ 38 фиксируется соответственно на пятом и шестом входах блока 36.

Таким образом, по показателям счетчиков, объединенных в блоке 36, а также счетчика 2 удается определить различные

вероятностные характеристики процесса передачи сообщений с неограниченным числом повторений, а именно: вероятность правильной передачи сообщения, вероятности необнаруженной ошибки, пропуска сообщений и другие.

Технико-экономическим эффектом является расширение функциональных возможностей устройства, а также повышение точности моделирования за счет более адекватного воспроизведения динамики и режимов функционирования систем связи с РОС в условиях случайных помех в каналах связи.

Формула изобретения Устройство для моделирования систем связи, содержащее генератор случайной последовательности импульсов, счетчик, генератор случайного числа, блок элементов ИЛИ, первый и второй регистры памяти, первый и второй блоки сравнения, первый элемент И, генератор случайных импульсов отказов, причем выход генератора случайной последовательности импульсов соединен со счетным входом счетчика, группа выходов первого регистра памяти подключена к первым группам входов первого и второго блоков сравнения, выход второго блока сравнения соединен с первым входом первого элемента И, отличающееся тем, что, с целью расширения области применения за счет моделирования режимов передачи сообщений в системах с решающей обратной связью в прямом канале передачи данных, в устройство введены элемент НЕ, блок элементов НЕ, блок генераторов случайных импульсов отказов, коммутатор, генератор тактовых импульсов, блок памяти, демультиплексор, первый, второй, третий элементы задержки, блок элементов И, с первого по шестой элементы ИЛИ, с первого по пятый триггеры, с второго по седьмой элементы И, блок счетчиков, причем выход renepaiOpa случайной последовательности импульсов соединен с первым входом второго элемента И, выход которого подключен к входу запуска генератора случайного числа, группа выходов которого соединена с группой информационных входов второго регистра памяти, группа выходов которого подключена к второй группе соответствующих входов первого блока сравнения и к первой группе соответствующих входов блока элементов И, группа выходов которого подключена к группе соответствующих информационных входов первого регистра памяти, вход обнуления которого, а также вход обнуления второго регистра памяти подключены к выходу первого элемента ИЛИ и нулевому входу

первого триггера, инверсный выход которого соединен с вторым входом второго элемента И, а единичный вход первого триггера подключен к выходу второго элемента ИЛИ, 5 группа входов которого соединена с группой соответствующих выходов генератора случайного числа, выход второго элемента ИЛИ подключен к первому входу третьего элемента ИЛИ, выход которого соединен с

0 входом записи первого регистра памяти, с входом запуска генератора тактовых импульсов, с нулевым входом второго триггера и через первый элемент задержки - с первым входом третьего элемента И, выход за5 писи второго регистра памяти подключен к выходу второго элемента ИЛИ, группа выходов блока генераторов случайных импульсов отказов через блок элементов НЕ соединена с второй группой входов блока

0 элементов И, выход первого блока сравнения подключен к второму входу третьего элемента И, выход которого соединен с единичным входом третьего триггера, прямой выход которого подключен к управляющему

5 входу демультиплексора, первый и второй выходы которого соединены соответственно с вторым и третьим входами третьего элемента ИЛИ, третий и четвертый выходы демультиплексора подключены соответст0 венно к первому и второму входам первого элемента ИЛИ, выходы с первого по четвертый демультиплексора соединены с соответствующими входами четвертого элемента ИЛИ, выход которого подключен к

5 нулевому входу четвертого триггера, прямой выход которого соединен с первым входом четвертого элемента И, выход которого подключен к первому информационному входу демультиплексора, выход второго

0 блока сравнения соединен с единичными входами второго и четвертого триггеров и через второй элемент задержки - с вторым входом четвертого элемента И, инверсный выход второго триггера соединен с первым

5 входом пятого элемента И, выход которого подключен к входу Останов генератора тактовых импульсов, входу установки в О коммутатора, единичному входу пятого триггера, через третий элемент задержки 0 к первому входу шестого элемента И, к первому входу седьмого элемента И, выход которого соединен с первым входом пятого элемента ИЛИ, выход которого подключен к нулевому входу пятого триггера, выход кото5 рого соединен с вторым входом шестого элемента И, выход которого соединен с вторым входом пятого элемента ИЛИ, выход генератора тактовых импульсов подключен куправляющему входу блока памяти, группа выходов которого соединена с группой соответствующих входов блока элементов ИЛИ, группа выходов которого подключена к второй группе соответствующих входов второй схемы сравнения, выход генератора тактовых импульсов соединен с управляющим входом коммутатора, первый выход которого подключен к второму входу пятого элемента И, а группа выходов, начиная с второго, соединена с группой соответствующих информационных входов блока памяти, выход генератора случайных импульсов отказов через элемент НЕ подключен к вторым входам первого и седьмого элементов И, выход первого элемента И соединен с вторым информационным входом демуль- типлексора, второй и четвертый выходы ко0

5

торого подключены соответственно к первому и второму входам шестого элемента ИЛИ, выход которого соединен с нулевым входом третьего триггера, первый, второй, третий, четвертый, пятый, шестой входы блока счетчиков соединены соответственно с третьим, первым выходами демультиплек- сора, выходом седьмого элемента И, выходом шестого элемента И, четвертым, вторым выходами демультиплексора, выход седьмого элемента И подключен к четвертому входу третьего элемента ИЛИ, третьему входу шестого элемента ИЛИ, четвертый вход которого соединен с выходом шестого элемента И, третьим входом первого элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СИСТЕМ ПЕРЕДАЧИ ДАННЫХ | 1991 |

|

RU2011219C1 |

| МОДУЛЬ МАТРИЧНОЙ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2168755C1 |

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

| Устройство для формирования маршрута сообщения в однородной вычислительной системе | 1988 |

|

SU1501080A1 |

| Устройство для моделирования процессов функционирования подвижных поверочных пунктов | 1990 |

|

SU1746386A2 |

| Устройство для моделирования систем передачи данных | 1983 |

|

SU1109758A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1988 |

|

SU1644158A1 |

| Устройство для моделирования систем передачи данных | 1990 |

|

SU1711178A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2000 |

|

RU2179787C1 |

Изобретение относится к цифровой вычислительной технике связи и может быть использовано для моделирования систем связи, вычислительных систем, систем передачи данных, в которых решение о правильности переданного сообщения принимается на приемной стороне. Цель изобретения - расширение области применения за счет моделирования режимов передачи сообщений Р. системах с решающей обратной связью ч прямом канале передачи данных. Устройство содержит генератор случайной последовательности импульсов, счетчик, семь элементов И, пять триггеров, генератор случайного числа, шесть элементов ИЛИ, два регистра памяти, блок элементов И, блок элементов НЕ, блок генераторов случайных импульсов отказов, два блока сравнения, генератор тактовых импульсов, коммутатор, блок памяти, блок элементов ИЛИ, три элемента задержки, элемент НЕ, генератор случайных импульсов отказов, блок счетчиков, демультиплексор. 2 ил.

(Риг. г

| Устройство для моделирования систем передачи и обработки данных | 1983 |

|

SU1150629A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования систем связи | 1986 |

|

SU1365093A1 |

Авторы

Даты

1992-06-15—Публикация

1990-03-23—Подача