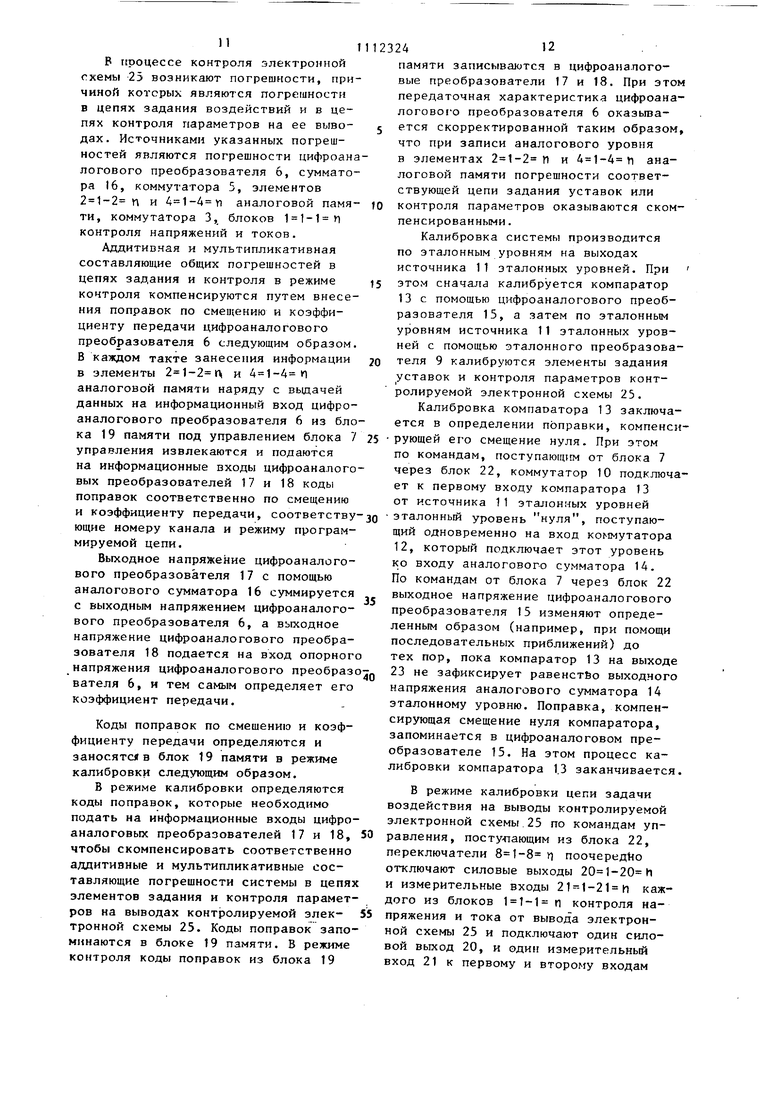

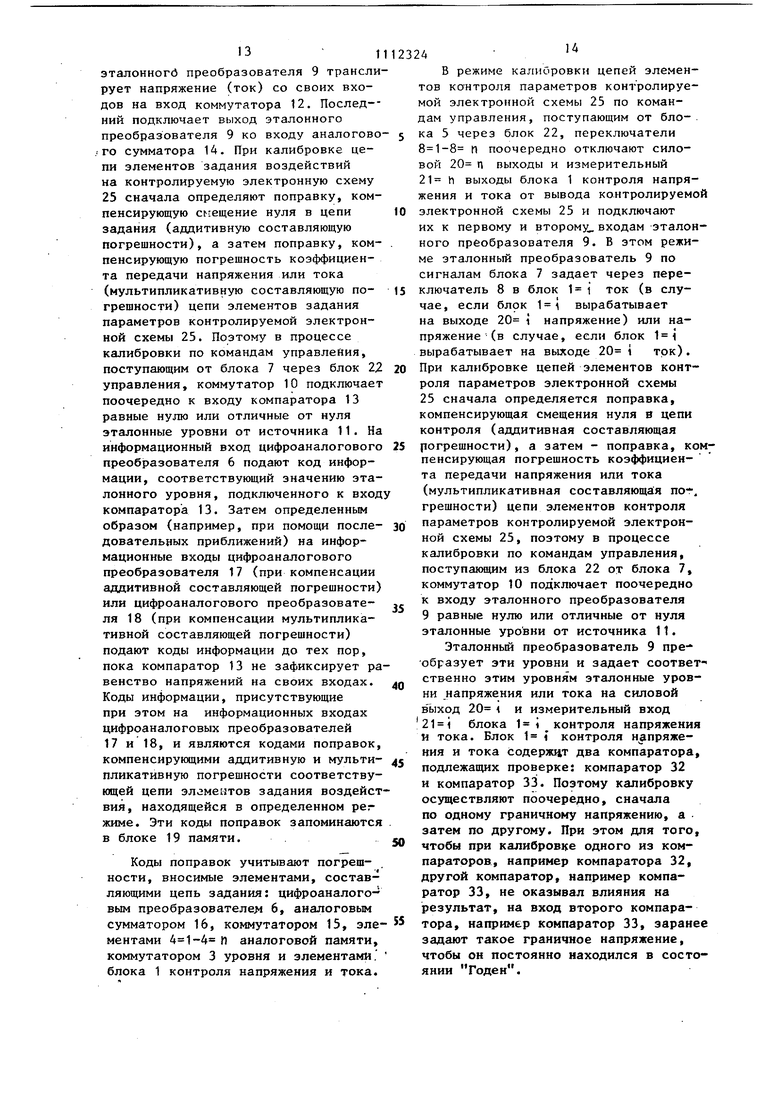

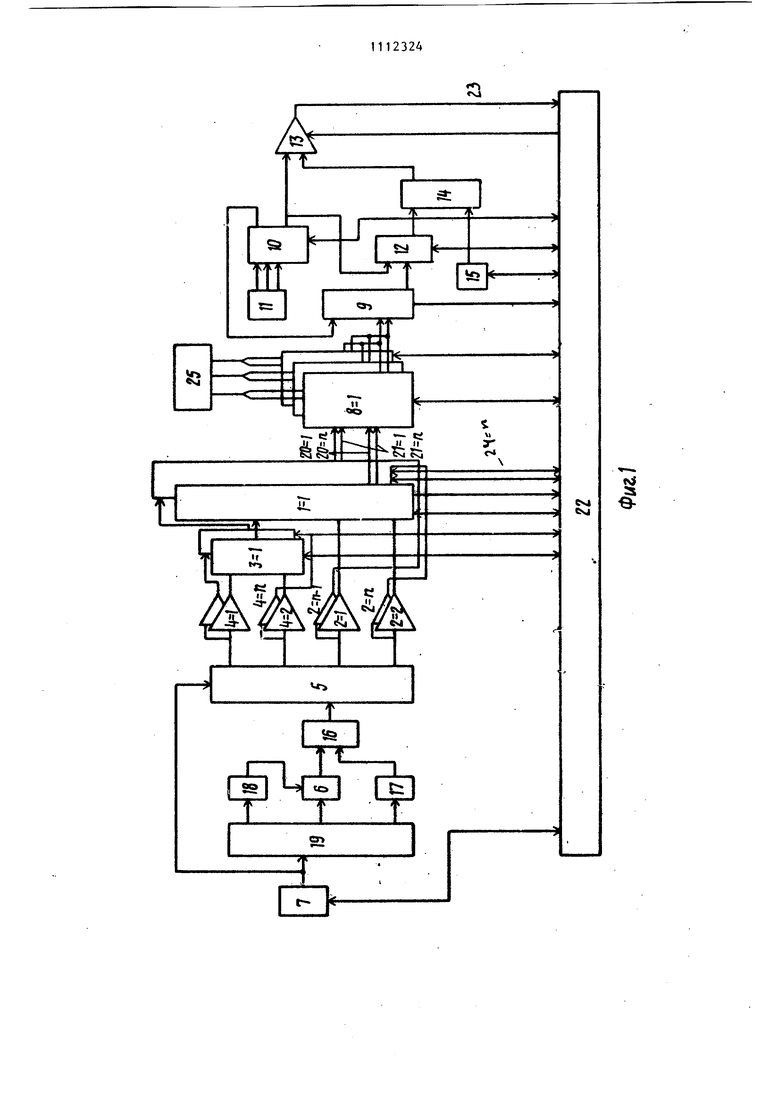

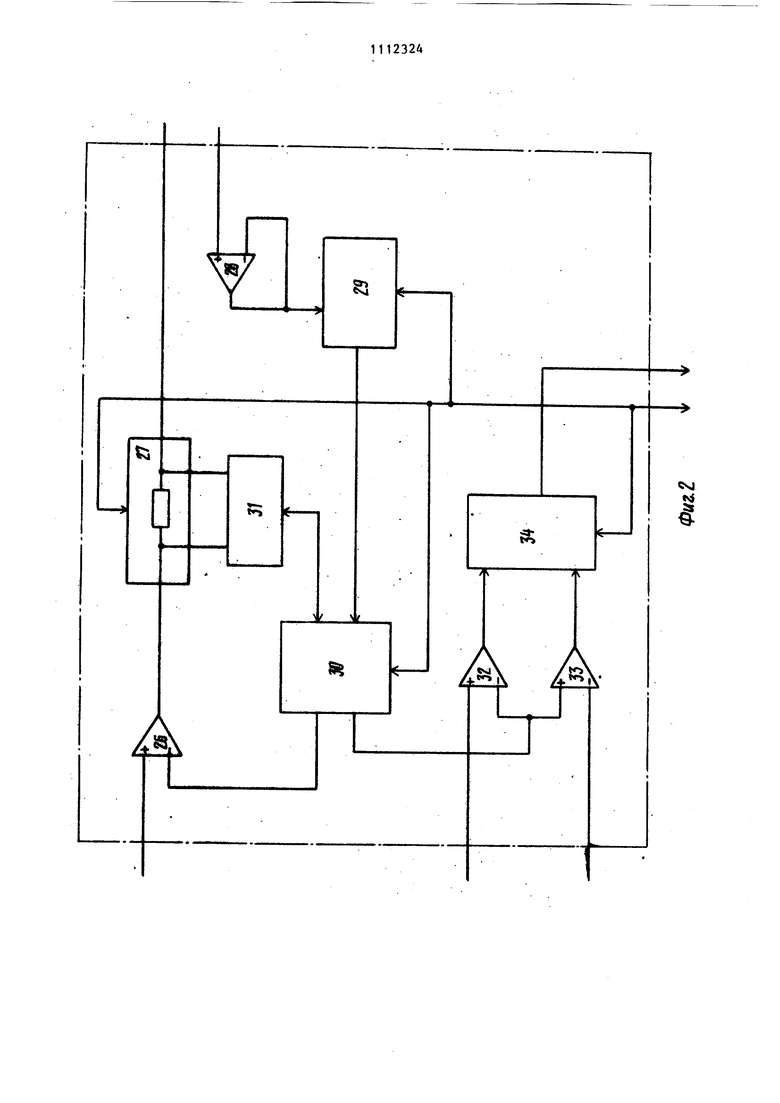

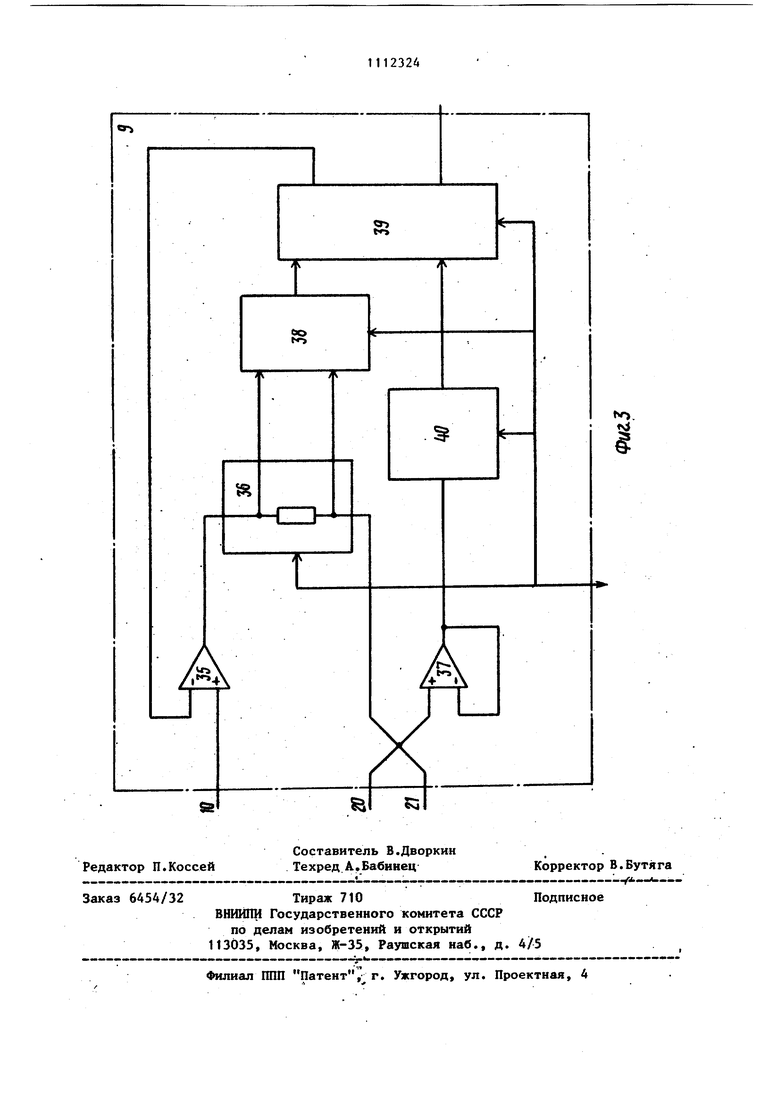

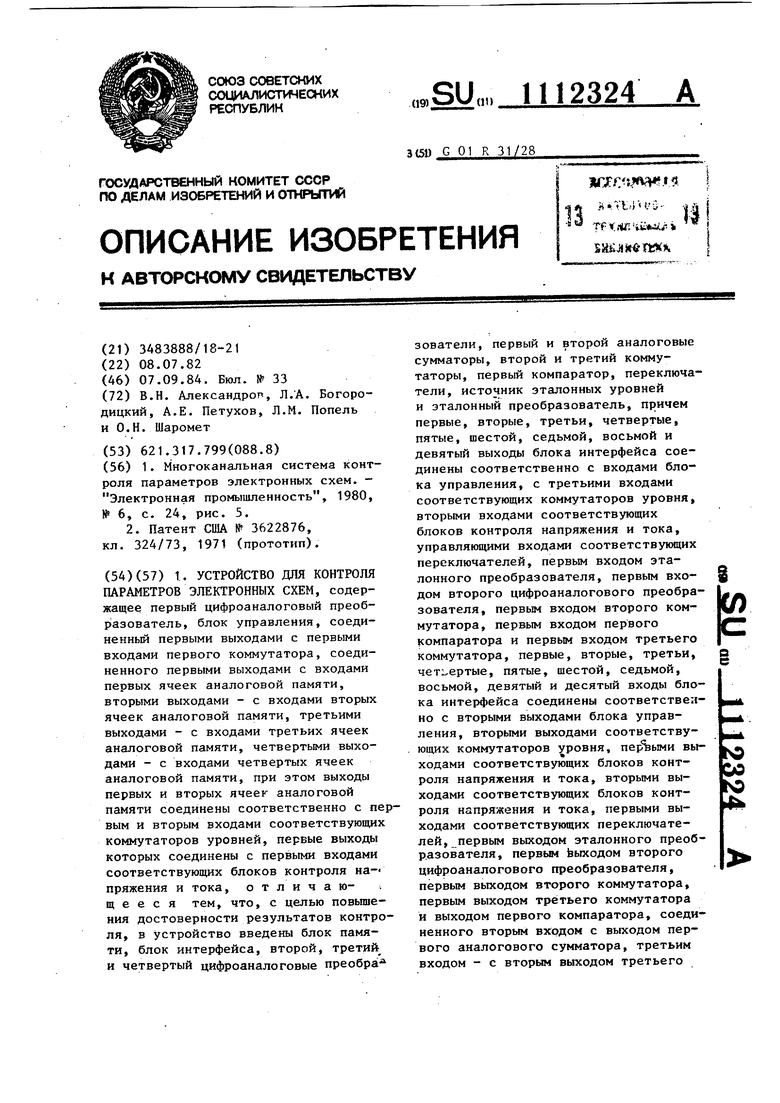

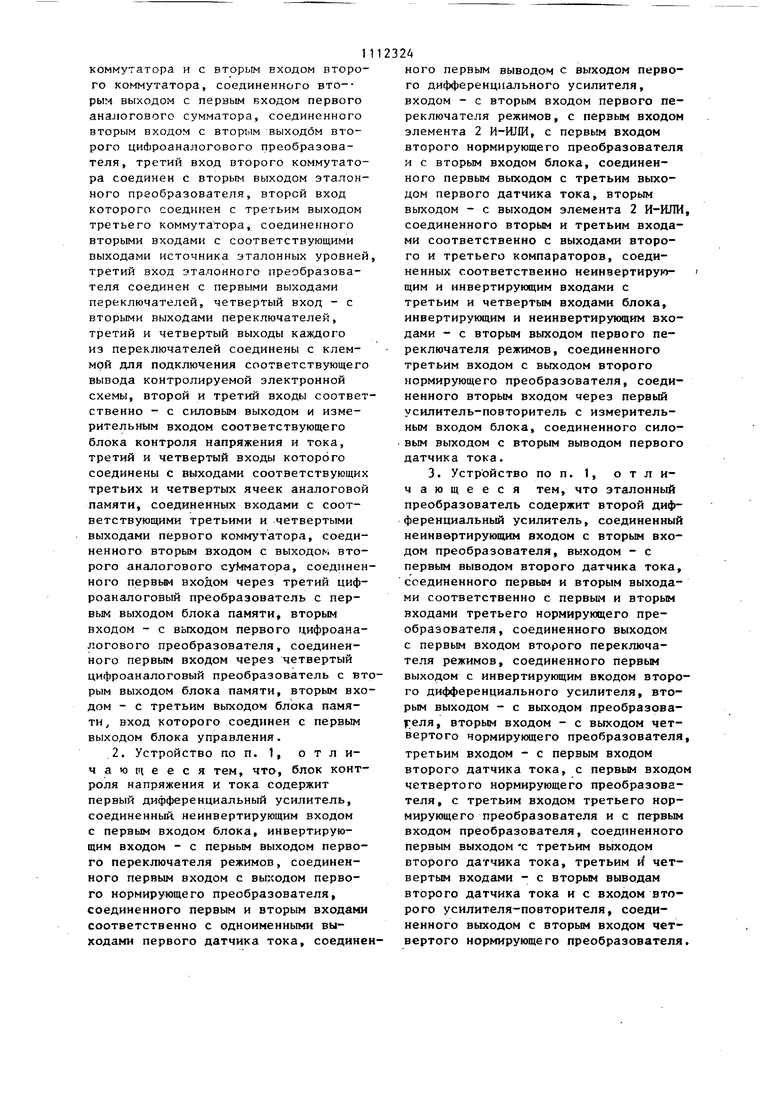

коммутатора и с вторым входом второ го коммутатора, соединенного вто-рым выходом с первым входом первого аналогового сумматора, соединенного вторым входом с вторым выходом второго ци(Ьроаналогового преобразователя, третий вход второго коммутато ра соединен с вторым выходом эталонного преобразователя, второй вход которого соединен с третьим выходом третьего коммутатора, соединенного вторыми входами с соответствующими выходами источника эталонных уровней третий вход эталонного преобразователя соединен с первыми выходами переключателей, четвертый вход - с вторыми выходами переключателей, третий и четвертый выходы каждого из переключателей соединены с клеммой для подключения соответствующег вывода контролируемой электронной схемы, второй и третий входы соответ ственно - с силовым выходом и измерительным входом соответствующего блока контроля напряжения и тока, третий и четвертый входы которого соединены с выходами соответствующих третьих и четвертых ячеек аналоговой памяти, соединенных входами с соответствующими третьими и четвертыми выходами первого коммутатора, соединенного вторым входом с выходом второго аналогового суМматора, соединен ного первм входом через третий цифроаналоговый преобразователь с первым выходом блока памяти, вторым входом - с выходом первого цифроаналогового преобразователя, соединенного первым входом через четвертый цифроаналоговый преобразователь с вт рым выходом блока памяти, вторым вхо дом - с третьим выходом блока памяти вход которого соединен с первым выходом блока управления. 2. Устройство по п. 1, о т л ич а ю Ц е е с я тем, что, блок конт роля напряжения и тока содержит первый дифференциальный усилитель, соединенный, неинвертирующим входом с первым входом блока, инвертирующим входом - с первым выходом первого переключателя режимов, соединенного первым входом с вьпсодом первого нормирующего преобразователя, соединенного первым и вторым входами соответственно с одноименными выходами первого датчика тока, соедине ного первым выводом с выходом первого дифференциального усилителя, входом - с вторым входом первого переключателя режимов, с первым входом элемента 2 И-ШШ, с первым входом второго нормирующего преобразователя и с вторым входом блока, соединенного первым выходом с третьим вькодом первого датчика тока, вторым выходом - с выходом элемента 2 И-ИЛИ, соединенного вторым и третьим входами соответственно с выходами второго и третьего компараторов, соединенных соответственно неинвертирующим и инвертирующим входами с третьим и четвертым входами блока, инвертирующим и неинвертирующим входами - с вторым выходом первого переключателя режимов, соединенного третьим входом с выходом второго нормирующего преобразователя, соединенного вторым входом через первый усилитель-повторитель с измерительным входом блока, соединенного силовым выходом с вторым выводом первого датчика тока. 3. Устройство по п. 1, отличающееся тем, что эталонный преобразователь содержит второй дифференциальный усилитель, соединенный неинввртирующим входом с вторым входом преобразователя, выходом - с первым выводом второго датчика тока, соединенного первым и вторым выходами соответственно с первым и вторым входами третьего нормирующего преобразователя, соединенного выходом с первым входом второго переключателя режимов, соединенного первым выходом с инвертирующим вкодом второго дифференциального усилителя, вторым выходом - с выходом преобразова|;еля, вторым входом - с выходом четвертого нормирующего преобразователя, третьим входом - с первым входом второго датчика тока, с первым входом четвертого нормирующего преобразователя , с третьим входом третьего нормирующего преобразователя и с первым входом преобразователя, соединенного первым выходом -с третьим выходом второго датчика тока, третьим li четвертым входами - с вторым выводам второго датчика тока и с входом второго усилителя-повторителя, соединенного выходом с вторым входом четвертого нормирующего преобразователя. 1 1 HaoepefeHHe относится к контрольно-измерительной технике и может быт использовано для контроля параметров электронных схем. Известна многоканальная система контроля параметров электронных схем содержащая блоки контроля напряжения и тока, первый и второй выходы которых соединены с клеммой для подклю чения вывода контролируемой электрон ной схемы, выходы преобразования сое динены с входами соответствующих компараторов, а входы - с выходами соответствующих цифроаналоговых преобразователей, управляющие входы блоков контроля напряжения и тока, цифроаналоговых преобразователей, компараторов соединены через магистраль управления с выходами блока управления l . Недостатком этой системы является низкая достоверность контроля из-за отсутствия возможности компенсации погрешностей контроля. Наиболее близкой к изобретению является система контроля цифровых блоков, содержащая первый цифроанало говый преобразователь, блок управления, соединенный первыми выходами с первыми входами первого коммутатора, соединенного первьЕми выходами со входами первых ячеек аналоговой памяти, вторыми входами - со входами вторых ячеек аналоговой памяти, третьими выходами - со входами третьи ячеек аналоговой памяти, четвертыми выходами - со входами четвертых ячеек аналоговой памяти, выходы первых и вторых ячеек аналоговой памяти соединены соответственно с первым и вторым входами .соответствующих коммутаторов уровней, первые выходы которых соединены с первыми входами соответствующих блоков контроля напряжения и тока 2 . Недостатком известной системы яьляется низкая достоверность контроля вследствие низкой точности формиро,:вания сигналов на выводах контролируемого цифрового узла из-за отсутствия возможности автоматической калибровки и возможности компенсации , погрешностей, вносимых блоками самой системы при имерении параметров. Цель изобретения - повышение достоверности контроля. Поставленная цель достигается тем, что в устройство для контроля 4. параметров электронных схем, содержащее первый цифроаналогоныи преобразователь, блок управления, соединенный первыми выходами с первыми входами первого коммутатора, соединенного первыми выходами с входами первых ячеек аналоговой памяти, вторыми выходами-с входами вторых ячееканалоговой памяти, третьими выходами с входами третьих ячеек аналоговой памяти, четвертыми выходами - с входами четвертых ячеек аналоговой памяти, при этом выходы первых и вторых ячеек аналоговой памяти соединены соответственно с первым и вторым входами соответствующих коммутаторов уровней, первые выходы которых соединены с первыми входами соответствующих блоков контроля напряжения и тока, введены блок памяти, блок интерфейса, второй, третий и четвертый цифроаналоговые преобразователи, первый и второй аналоговые сумматоры, второй и третий коммутаторы, первый компаратор, переключатели, источник эталонных уровней и эталонный преобразователь, причем первые, вторые, третьи, четвертые, пятые, шестой, седьмой, восьмой и девятый выходы блока интерфейса соединены соответственно с входами блока управления, с третьими входами соответствующих коммутаторов уровня, вторыми входами соответствующих блоков контроля напряжения и тока, управляющими входами соответствующих переключателей, первым входом эталонного преобразователя, первым входом второго цифроаналогового преобразователя, первым входом второго коммутатора, первым входом первого компаратора и первым входом третьего коммутатора, первые, вторые, третьи, четвертые, пятые, шестой, седьмой, восьмой, девятый и десятый входы блока интерфейса соединены соответственно с вторыми выходами блока управления, вторыми выходами соответствующих коммутаторов уровня, первыми выходами соответству1рщих блоков контроля напряжения и тока, вторыми выходами соответствующих блоков контроля напряжения и тока, первыми выходами соответствующих переключателей, первым выходом эталонного преобразователя, первым выходом второго цифроаналогового преобразователя, первым выходом второго коммутатора, первым выходом третьего коммутатора и выходом первого компаратора, соединенного вторы входом с выходом первого аналогового сумматора, третьим входом - с вторым выходом третьего коммутато а и с вторым входом второго коммутатора, соединенного вторым выходом с первым входом первого аналогового сумматора, соединенного вторым входом с вторым выходом второго цифроаналогового преобразователя, третий вход второго коммутатора соединен с вторым выходом эталонного преобразователя, второй вход которого соединен с третьим выходом третьего коммутатора, соединенного вторьми входами с соответствующими выходами источника эталонных уровней, третий вход эталонного преобразователя соединен с первыми выходами переключателей, четвертый вход - с вторыми выходами переключателей, третий и четвертый выходы каждого из переключателей соединены с клеммой для подключения соответствующего вывода контролируемой электронной схемы, второй и третий входы соответственно - с силовым выходом и измерительным входом соответствующего блока контроля напряжения и тока, третий и четвертый входы которого соединены с выходами соответствующих третьих и четвертых ячеек аналоговой памяти, соединенных входами с соответствующими третьими и четвертыми выходами первого коммутатора, соединенного вторым входом с выходом второго аналогового сумматора, соединенного первым входом через третий цифроаналоговый преобра зователь с первым выходом блока памяти, вторым входом - с выходом первого цифроаналогового преобразовател соединенного первым входом через четвертый цифроаналоговый преобразователь с вторым выходом блока памяти, вторым входом - с третьим выходом блока памяти, вход которого соединен с первым выходом блока управления. Блок контроля напряжения и тока содержит первый дифференциальный усилитель, соединенный неинвертирующим входом с первым входом блока, инвертирующим входом - с первым выхо дом первого переключателя режимов, соединенного первым входом с выходом первого нормирующего преобразователя соединенного первым и вторым входами соответственно с одноименными выходами первого датчика тока, соединенного первым выводом с выходом первого дифференциального усилителя, входом - с вторым входом первого переключателя режимов, с первым входом элемента 2 И-ИЛИ, с первым входом второго нормирующего преобразователя и с вторым входом блока, соединенного первым выходом с третьим выходом первого датчика тока, вторым выходом - с выходом элемента 2 И-ИЖ, соединенного вторым и третьим входами соответственно с выходами второго и третьего компараторов, соединенных соответственно неинвертирующим и инвертирующим входами с третьим и четвертым входами блока, инвертирующим и неинвертирующим входами - с вторым выходом первого переключателя режимов, соединенного третьим входом с выходом второго нормирующего преобразователя, соединенного вторым входом через первый усиЛитель-повторнтель с измерительным входом блока, соединенного силовьм выходом с вторым выводом первого датчика тока. Эталонный преобразователь содержит второй дифференциальный усилитель, соединенный неинвертирующим входом с вторим входом преобразователя, выходом - с первым выводом второго датчика тока, соединенного первым и вторым выходами соответственно с первым и вторым входами третьего нормирующего преобразователя, соединенного выходом с первым входом второго переключателя режимов, соединенного первым выходом с инвертирующим входом второго дифференциального усилителя, вторым выходом - с выходом преобразователя, вторым входом - с выходом четвертого нормирующего преобразователя, третьим входом - с первым входом второго датчика тока, с первым входом четвертого норм11рующего преобразователя, с третьим входом третьего нормирующего преобразователя и с первым входом преобразователя, соединенного первым выходом с третьим выходом второго да-гчйка тока, третьим и четвертым входами - с вторым выводом второго датчика тока и с входом второго усилителя-повторителя, соединенного выходом с вторым входом четвертого нормирующего преобразователя. На фиг. 1 приведена блок-схема устройства; на фиг. 2 - схема блока контроля напряжения и тока, на фиг. 3 - схема эталонного преобразова теля. Устройство содержит (фиг. 1) блоки И контроля напряжения и трка, третьи и четвертые Ч ячейки аналоговой памяти коммутаторы ft уровней, первые П-1 и вторые П ячейки аналоговой памяти, первый коммутатор 5, первый цифроаналоговый преобразователь 6, блок 7 управления, переключатели И, эталонный преобразователь 9, третий коммутатор 10, источник 11 эталонных уровней, второй коммутатор 12, компаратор 13, первый аналоговый сумматор 14, второ цифроаналоговый преобразователь 15, второй аналоговый сумматор 16, третий 17 и четвертый 18 цифроаналоговые преобразователи, блок 19 памяти, силовые выходы и измерительные входы М блоков п контроля напряжения и тока, блок 22 интерфейса, выход 23 компара тора 13, выходы Г) блоков 1 1-.1 контроля напряжения и тока, контролируемая электронная схема 25 (фиг. 1). Блоки ц содержат первый дифференциальный усилитель 26, первый датчик 27 тока, первый усилитель повторитель 28, второй нормирующий преобразователь 29, первый переключа .тель 30 режимов, первый нормирующий преобразователь 31, второй 32 и третий 33 компараторы, элемент 34 2И-ИЛИ. Эталонный преобразователь 9 содер жит второй дифференциальный усилител 35, второй датчик 36 тока, второй усилитель-повторитель 37, третий нормирующий преобразователь 38,второй переключатель 39 режимов, четвертый нормирующий преобразователь 40. Устройство для контроля параметров электронных схем содержит первый цифроаналоговый преобразователь 6, блок 7 управления, соединенный первыми выходами с первыми входами первого коммутатора 5, соединенного пер выми выходами со входами первых яче ек аналоговой памяти, вто рыми входами - со входами вторых яче ек П аналоговой памяти, треть ми выходами - со входами третьих яче ек аналоговой памяти, четвертьми выходами - со входами 4et 1 46 вертых ячеек П аналогорой памяТ-и. Выходы первых 4 1-4 П-1 и рторых п ячеек етналоговой памяти соединены соответственно с первым и вторым входами соответствующих коммутаторов и уровнен, первые выходы которых соединены с первыми входами соответствующих блоков 1 1-1 контроля напряжения и тока. Первые, вторые, третьи, четвертые, пятые, шестой, седьмой, восьмой и девятый выходы блока 22 интерфейса соединены соответственно со входами блока 7 управления, с третьими входами соответствующих коммутаторов М уроэня, вторыми входами соответствующих блоков h контроля напряжения и тока, управляющими входами соответствующих перек1тючателей П , первым входом эталонного преобразователя 9, первым входом второго цифрового преобразователя 15, первым входом второго коммутатора 12, первым входом первого компаратора 13 и первым входом третьего коммутатора 10. Первые, BTOpi.ie, третьи, четвертые, пятые, щестой ,седьдевятый и десятый входы мои восьмой, блока 22 интерфейса соединены соответственно с вторыми выходами блока 7 управления, вторыми выходами соответствующих коммутаторов И уровня, первыми выходами соответствующих блоков 1 контроля напряжения и тока, вторыми выходами соответствующих блоков 1 контроля напряжения и тока, первыми выходами соответствующих переключателей И , первым выходом эталонного преобразователя 9, первым выходом второго циф- роаналогового преобразователя 15, первьм выходом второго коммутатора 12, первым выходом третьего коммута- . тора 10 и выходом первого компаратора 13, соединенного вторым входом с выходом первого аналогового сумматора 14, третьим входом - с вторым выходом третьего коммутатора 10 и с вторым входом второго коммутатора 12, соединенного вторым выходом с Первым входом первого аналогового сумматора 14, соединенного вторым входом с вторым выходом второго ЦИФроаналогового преобразователя 15, третий вход второго коммутатора 12 соединен с вторым выходом эталонного преобразователя 9, второй вход которого соединен с третьим выхолим третьего коммутатора 10,.соединенног вторыми входами с соответствующими выходами источника 11 эталонных уров ней, третий вход эталонного преобразователя 9 соединен с первыми выходами переключателей , четвертый вход - с вторыми выходами пер ключателей . Третий и четвер тый выходы каждого из переключателей h соединены с клеммой для подключения соответствующего вывода электронной схемы 25, второй и трети входы соответственно - с силовым выходом и измерительным входом 21 соответствующего блока 1 1-1 контроля напряжения и тока, третий и четвертый входы которого соединены с выходами соответствующих третьих .П-1 и четвер тых h ячеек аналоговой памяти соединенных входами с соответствующими третьими и четвертыми выходами первого коммутатора 5, соединенного вторым входом с выходом второго аналогового сумматора 16, соединенного первым вхрдом через третий цифроаналоговый преобразователь 17 с пе вым выходом блока 19 памяти, вторым входом - с выходом первого цифроаналогового преобразователя 6, соединенного первым входом через четверты цифроаналоговый преобразователь 18 с вторым выходом блока 19 памяти, вторым входом третьим выходом блока 19 памяти, вход которого соеди нен с первыми выходами блока 7 управ ления . В блоке контроля напряжения и тока неинвертирующий выход первого дифференциального усилителя 26 соединен первым входом блока , инвер тирующим входом - с первым выходом первого переключателя 30 режимов, соединенного первым входом с выходом первого нормирующего преобразователя 31, соединенного первым и вторым входами соответственно с одноименными выходами первого датчика 27 тока, соединенного первым выводом с выходом первого дифференциального усилителя 26, входом - с вторым входом первогб переключателя 30 режимов с первым входом элемента 34 2 И-ИЛИ, с первым входом второго нормирующего преобразователя 29 и с вторым входом блока , соединенного первым выходом с третьим выходом первого датчика 27 тока, вторым выходом - с выходом элемента 34 2 И-ИЛИ, соединенного вторым и третьим входами соответственно с выходами второго 32 и третьего 33 компараторов, соединенных соответственно неинвертирующим и инвертирующим входами с третьим и четвертым входами блока , инвертирующим и неинвертирующим входами с вторым выходом первого переключателя 30 режимов, соединенного третьим входом с выходом второго нормирующего преобразователя 29, соединенного вторым входом через первый усилитель-повторитель 28 С измерительным входом блока , соединенного силовым выходом с вторым вьшодом первого датчика 27 тока. В эталонном преобразователе 9 инвертирующий вход второго дифференциального усилителя 35 соединен с вторым входом преобразователя 9, выход - с первым выводом второго датчика тока 36, соединенного первым и вторым выходами соответственно с первым и вторым входами третьего нормирующего преобразователя 38, соединенного выходом с первым входом второго переключателя 39 режимов, соединенного первым выходом с инвертирующим входом второго дифференциального усилителя 35, вторым выходом - с выходом преобразователя 9, вторым входом - с выходом четвертого нормирующего преобразователя 40, третьим входом - с первым входом второго датчика 36 тока, с первым входом четвертого нормирующего преобразователя 40, с третьим входом третьего нормирукйцего преобразователя 38 и с первым входом преобразователя 9,соединенного первым выходом с третьим выходом второго датчика 36 тока, третьим и четвертым входами - с вторым вьшодом второго датчика 36 тока и с входом второго усилителя-повторителя 37, соединенного выходом с. вторым входом четвертого нормирующего преобразователя 40. Устройство работает следующим образом. В режиме контроля с помощью блоков 1 контроля напряжений и тока выводы и и 21 , которые с помощью переключателя В попарно соединены с выводами контролируемой электронной схемы 25, задают уровни напряжений и контролируют токи в цепях входов или задают токи нагрузки и контролируют напряжения на выходах контролируемой электронной схемы 25. Блок 1 контроля напряжения и тока (фиг. 3) может работать в двух режима;х: задания напряжения - контро ля тока в цепи вывода электронной схемы 25; задания тока - контроля напряжения в цепи вывода электронной схемы 25. В режиме задания напряжения - контроля тока по командам управления, поступающим от блока 7 через блок 22, переключатель 30 режи мов подключает к инвертирующему входу дифференциального усилителя 26 сигнал с выхода первого нормирующего преобразователя 29, а к инвертирующему входу компаратора 32 и к неинве тирующему входу компаратора 33 - сиг нал с выхода нормирующего преобразователя 31. В результате осуществляется отрицательная обратная связь по напряжению, котортя стабилизирует напряжение на выходе схемы 22 на уровне, пропорциональном напряжению уставки, подаваемому на неинвертирующий вход дифференциального усилителя 26, а на выходе 24 блока 1 контро ля появляется результат контроля, являющийся логической функцией сигна лов на выходах компараторов 32 и 33, которые и производят двупороговое сравнение напряжения на выходе нормирующего преобразователя 31, пропорционального току в цепи вывода контролируемой электронной схемы 25, с граничными напряжениями. В режиме задания тока - контроля напряжения по командам управления переключатель 30 режимов подключает инвертирующему входу дифференциального усилителя 26 сигнал с выхода нормирующего преобразователя 31, а к инвертирующему входу компаратора 32 и к неинвертирующему входу компаратора 33 - сигнал с выхода нормирую щего преобразователя 29. В результате действия отрицательной обратной связи ток в цепи силовых выводов )1 , как и в цепях выводов контролируемой электронной схемы 25, стабилизируется на уровне, пропорцио нальном напряжению уставки, подаваемому на неинвертирующий вход дифференциального усилителя 26, а на выходе 24 блока 1 появляется результат 1контроля, являющийся логической функцией результата сравнения напря жения, пропорционального напряжению на выводе 21 (равного напряжению на выходе контролируемой электронной схемы 25) с граничным напряжением. Формирование нормированных напряжений уставок, задаваемых на неинвертирующий вход усилителя 26, и напряжений граничных уставок, задаваемых на неинвертирующий вход компаратора 32 и инвертирующий вход компаратора 33, производится с помощью блока 7 управления, блока 19 памяти, цифроаналоговой памяти и П. Эти блоки и элементы взаимодействую: следующим образом. Под управлением блока 7 управления цифровая информация из блока 19 памяти последовательно подается на вход данных цифроаналогового преобразователя 6 так, что на его выходе последовательно в течение определенного отрезка времени воспроизводятся уровни напряжения, соответствующие уровням, напряжения уставок и напряжениям граничных уставок для каждого блока 1 контроля напряжения и тока. Синхронно с выдачей данных на вход цифроаналогового преобразователя 6 блок 7 управления переключает коммутатор 5 таким образом, что на вход каждого элемента и аналоговой памяти каждого блока h в течение определенного отрезка времени подается соответствующее установившееся напряжение, которое запоминается этим элементом. Процесс воспроизведения аналоговой информации на выходах элементов -2 1 и И аналоговой памяти повторяется периодически - таким образом, что на выходах этих элементов всегда присутствует напряжение необходимого уровня, соответствующее напряжению уставки (элементы 4 1-4-h) или напряжению граничных уставок контролируемого параметра (элементы ). В соответствии с фиг. 1 уровни напряжений :уставок задавав-, мого на схему 22 параметра (напряжения или тока), подаваемые на инвертирующий вход усилителя 26 блока 1, коммутируются с помощью коммутатора 3 уровней, что может использоваться, например, для быстрой смены задаваемого на вход контролируемой электронной схемы 12 напряжения с уровня логического О до уровня логической 1, или наоборот.

В 1 роцессе контроля электронной схемы 25 возникают погрешности, причиной которых являются погрешности в цепях задания воздействий и в цепях контроля параметров на ее выводах. Источниками указанных погрешностей являются погрешности цифроаналогового преобразователя 6, сумматора 16, коммутатора 5, элементов n и аналоговой памяти, коммутатора 3, блоков контроля напряжений и токов.

Аддитивная и мультипликативная составляющие общих погрешностей в цепях задания и контроля в режиме контроля компенсируются путем внесения поправок по смещению и коэффициенту передачи цифроаналогового преобразователя 6 следующим образом. В каждом такте занесения информации в элементы и аналоговой памяти наряду с выдачей данных на информационный вход цифроаналогового преобразователя 6 из блока 19 памяти под управлением блока 7

управления извлекаются и подаются на информационные входы цифроаналоговых преобразователей 17 и 18 коды поправок соответственно по смещению и коэффициенту передачи, соответству ющие номеру канала и режиму программируемой цепи. Выходное напряжение цифроаналогового преобразователя 17 с помощью аналогового сумматора 16 суммируется с выходным напряжением цифроаналогового преобразователя 6, а выходное напряжение цифроаналогового преобразователя 18 подается на вход опорног напряжения цифроаналогового преобраз вателя 6, и тем самым определяет его коэффициент передачи. Коды поправок по смешению и коэффициенту передачи определяются и заносятся в блок 19 памяти в режиме калибровки следующим образом. В режиме калибровки определяются коды поправок, которые необходимо подать на информационные входы цифро аналоговых преобразователей 17 и 18, чтобы скомпенсировать соответственно аддитивные и мультипликативные составляющие погрешности системы в цепях элементов задания и контроля параметров на выводах контролируемой электронной схемы 25. Коды поправок запоминаются в блоке 19 памяти. В режиме контроля коды поправок из блока 19

памяти записываются в цифроаналоговые преобразователи 17 и 18. При этом передаточная характеристика цифроаналогового преобразователя 6 оказьгоается скорректированной таким образом, что при записи аналогового уровня в элементах И и аналоговой памяти погрешности соответствующей цепи задания уставок или

контроля параметров оказываются скомпенсированными .

Калибровка системы производится по эталонным уровням на выходах источника 11 эталонных уровней. При

этом сначала калибруется компаратор 13 с помощью цифроаналогового преобразователя 15, а затем по эталонным уровням источника 11 эталонных уровней с помощью эталонного преобразователя 9 калибруются элементы задания уставок и контроля параметров контролируемой электронной схемы 25.

Калибровка компаоатора 13 заключается в определении поправки, компенсипо командам, поступающ1гм от блока 7 через блок 22, коммутатор 10 подключает к первому входу компаратора 13 от источника 11 эталонных уровней 25 рующей его смещение нуля. При этом эталонный уровень нуля, поступающий одновременно на вход коммутатора 12, который подключает этот уровень ко входу аналогового сумматора 14. По командам от блока 7 через блок 22 выходное напряжение цифроаналогового преобразователя 15 изменяют определенным образом (например, при помощи последовательных приближений) до тех пор, пока компаратор 13 на выходе 23 не зафиксирует равенстбо выходного напряжения аналогового сумматора 14 эталонному уровню. Поправка, компенсирующая смещение нуля компаратора, запоминается в цифроаналоговом преобразователе 15. На этом процесс калибровки компаратора 1.3 заканчивается. В режиме калибровки цепи задачи воздействия на выводы контролируемой электронной схемы.25 по командам управления, постучтающим из блока 22, переключатели n поочередно отключают силовые выходы и измерительные входы каждого из блоков n контроля напряжения и тока от вывода электронной схемы 25 и подключают один силовой вькод 20, и один измерительный вход 21 к первому и второму входам 3 эталонногс5 преобразователя 9 трансли рует напряжение (ток) со своих входов на вход коммутатора 12. Послед- НИИ подключает выход эталонного преобразователя 9 ко входу аналогово . го сумматора 14. При калибровке цепи элементов задания воздействий на контролируемую электронную схему 25 сначала определяют поправку, компенсирующую c ;eщeниe нуля в цепи задания (аддитивную составляющую погрешности), а затем поправку, компенсирующую погрешность коэффициента передачи напряжения или тока (мультипликативную составляющую погрешности) цепи элементов задания параметров контролируемой электронной схемы 25. Поэтому в процессе калибровки по командам управления, поступающим от блока 7 через блок 22 управления, коммутатор 10 подключает поочередно к входу компаратора 13 равные нулю или отличные от нуля эталонные уровни от источника 11. На информационный вход цифроаналогового преобразователя 6 подают код информации, соответствующий значению эталонного уровня, подключенного к вход компаратора 13. Затем определенным образом (например, при помощи последовательных приближений) на информационные входы цифроаналогового преобразователя 17 (при компенсации аддитивной составляющей погрешности) или цифроаналогового преобразователя 18 (при компенсации мультипликативной составляющей погрешности) подают коды информации до тех пор, пока компаратор 13 не зафиксирует ра венство напряжений на своих входах. Коды информации, присутствующие при этом на информационных входах цифроаналоговых преобразователей 17 и 18, и являются кодами поправок компенсирующими аддитивную и мультипликативную погрешности соответствующей цепи эл эментов задания воздейст вия, находящейся в определенном per жиме. Эти коды поправок запоминаются в блоке 19 памяти. Коды поправок учитывают погрешности, вносимые элементами, составляющими цепь задания: цифроаналоговым преобразователе 6, аналоговым сумматором 16, коммутатором 15, эле ментами И аналоговой памяти, коммутатором 3 уровня и элементами. блока 1 контроля напряжения и тока. А В режиме калнСфовки цепей элементов контроля параметров контролируемой электронной схемы 25 по командам управления, поступающим от блока 5 через блок 22, переключатели м поочередно отключают силовой 20 п выходы и измерительный 21 h выходы блока 1 контроля напряжения и тока от вывода контролируемой электронной схемы 25 и подключают их к первому и второму входам эталонного преобразователя 9. В этом режиме эталонный преобразователь 9 по сигналам блока 7 задает через переключатель 8 в блок 1 1 ток (в случае, если блок 1 вырабатывает на выходе 20 i напряжение) или напряжение (в случае, если блок вырабатывает на выходе 20 i ток). При калибровке цепей элементов контроля параметров электронной схемы 25 сначала определяется поправка, компенсирующая смещения нуля в цепи контроля (аддитивная составляющая погрешности), а затем - поправка, компенсирующая погрешность коэффициента передачи напряжения или тока (мультипликативная составляющая по-, грешности) цепи элементов контроля параметров контролируемой электронной схемы 25, поэтому в процессе калибровки по командам управления, поступающим из блока 22 от блока 7, коммутатор 10 подключает поочередно к входу эталонного преобразователя 9 равные нулю или отличные от нуля эталонные уровни от источника 11. Эталонный преобразователь 9 пре образует эти уровни и задает соответственно этим уровням эталонные уровни напряжения или тока на силовой выход 20 1 и измерительный вход блока контроля напряжения и тока. Блок 1 1 контроля н 1пряжения и тока содержит два компаратора, подлежащих проверке: компаратор 32 и компаратор 33. Поэтому калибровку осуществляют поочередно, сначала по одному граничному напряжению, а затем по другому. При этом для того, чтобы при калибровке одного из компараторов, например компаратора 32, другой компаратор, например компаратор 33, не оказывал влияния на результат, на вход второго компаратора, например компаратор 33, заранее задают такое граничное напряжение, чтобы он постоянно находился в состоянии Годен. На информационный вход цифроанал гового преобразователя 6 подают KO;I информации, соответствующий значени эталонного уровня, подключенного к входу эталонного преобразователя 9 от блока 11 через блок 10. Затем оп деленным образом, например, при помощи последовательных приближений на информационные входы цифроаналогового преобразователя 17 (при компенсации аддитивной составляющей погрешности) или цифроаналогового преобразователя 18 (при компенсации мультипликативной составляющей погрешности) подают коды информации до тех пор, пока проверяемый Ромпаратор 32 (или 33) блока 1 контроля напряжения и тока не зафиксирует равенство напряжений на своих входа Коды информации, присутствующие при этом на информационных входах цифро аналоговьгх преобразователей 17 и 18 и являются кодами поправок, компенсирующих, аддитивную и мультипликативную погрешности соответствующей цепи элементов- контроля параметров, находящейся в заданном режиме. Эти коды поправок запоминаются в блоке 19 памяти. Коды поправок учитывают погрешности, вносимые элементами, составляющими цепь контроля: цифроаналоговым преобразователем 6, аналоговым сумматором 16, коммутатором 5, элементами i аналоговой памяти, элементами блока 1 контроля напряжения и тока. Эталонный преобразователь 9 (фиг работает в двух режимах: в режиме задания эталонного тока в цепи выводов , или в режиме ния напряжения в цепи выводов 20 i 21 1 . Задание тока и напря;жения в цепи выводов 20 i , блока 1 i необходимо при калибровке цепей элементов измерения параметров схемы 25, например при калибровке компараторов 32, 33, и при калибровке цепей задания воздей ствий. В режиме задания тока по командам управления от блока 7 через блок 25 переключатель 39 режима раб ты подключает к инвертирующему вход дифференциального усилителя 35 выход нормирующего преобразователя 38, а к выходу блока 9 - выход нормирующего преобразователя 40. Следовательно, на выходе блока 9 формируется в этом случае пронормированньш сигнал, пропорциональный напряжению, выдаваемому блоком и выводах 20 t , , а в цепи этих выводов задается ток, определяемый напряжением на неинвертирующем входе усилителя 26. В режиме задания напряжения по командам от блока 7 через блок 25 переключатель 39 режима работы подключает к инвертирующему i входу дифференциального усилителя 35 выход нормирующего преобразователя 38. В этом случае на выходе блока 9 имеется нормированный сигнал, пропорциональный току в цепи выводов , блока 1 i , а на выводы 20 1 , задается напряжение, определяемое напряжением на неинвертирующем входе усилителя 35. Таким образом, предложенная многоканальная система контроля параметров электронных схем обеспечивает повьш ение достоверности результатов контроля путем повышения точности формирования сигналов на выводах контролируемой электронной схемы 25. Предлагаемая система позволяет корректировать погрешности, причиной которых являются погрешности аналоговых сумматоров 14 и 16, коммутато- ров 3, 5, 10, 12, элементов , аналоговой памяти, блока 1 контроля напряжения и тока, компа- .. .ратора 13, цифроаналогового преобразователя 6, для всех блоков 1 и любых граничных значений, по любому выходному параметру. В итоге погрешности контроля и задания параметров определяются погрешностями только эталонного преобразователя 9, источника 11 эталонных уровней, которые являются общими ля системы и должны удовлетворять повьщ1енным требованиям по погрешностям, тогда как в известном устройстве повьшгенным требованиям должны удовлетворять все блоки 1 контроля апряжения и тока.

о

| название | год | авторы | номер документа |

|---|---|---|---|

| Выходной узел тестера для контроля электронных блоков | 1980 |

|

SU945830A1 |

| СПОСОБ ДИАГНОСТИРОВАНИЯ МЕТАЛЛИЧЕСКИХ КОНСТРУКЦИЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2339938C1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ИЗМЕНЕНИЯ МОЩНОСТИ НАГРУЗКИ ТОКОВЕДУЩИХ ЭЛЕМЕНТОВ СИСТЕМ ЭЛЕКТРОСНАБЖЕНИЯ | 1994 |

|

RU2079886C1 |

| УСТРОЙСТВО ВЛАГОМЕТРИИ ТЕХНОЛОГИЧЕСКИХ ЖИДКОСТЕЙ | 2019 |

|

RU2699241C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ИЗМЕНЕНИЯ СОПРОТИВЛЕНИЯ РЕЗИСТИВНЫХ ДАТЧИКОВ В ЭЛЕКТРИЧЕСКИЙ СИГНАЛ | 2010 |

|

RU2499237C2 |

| Устройство для измерения температуры и разности температур | 1990 |

|

SU1786374A1 |

| СОСТАВНОЙ БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2006 |

|

RU2311731C1 |

| Устройство для регулирования мощности | 1986 |

|

SU1422230A1 |

| МНОГОКАНАЛЬНОЕ АКУСТИКО-ЭМИССИОННОЕ УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИЗДЕЛИЙ | 2004 |

|

RU2300761C2 |

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ, содержащее первый цифроаналоговый преобразователь, блок управления, соединенный первыми выходами с первыми входами первого коммутатора, соединенного первыми выходами с входами первых ячеек аналоговой памяти, вторыми выходами - с входами вторых ячеек аналоговой памяти, третьими выходами - с входами третьих ячеек аналоговой памяти, четвертыми выходами - с входами четвертых ячеек аналоговой памяти, при этом выходы первых и вторых ячеек аналоговой памяти соединены соответственно с первым и вторым входами соответствующих коммутаторов уровней, первые выходы которых соединены с первыми входами соответствующих блоков контроля напряжения и тока, отличаю- ; щ е е с я тем, что, с целью повьпиения достоверности результатов контроля, в устройство введены блок памяти, блок интерфейса, второй, третий и четвертый цифроаналоговые преобра зователи, первый и второй аналоговые сумматоры, второй и третий коммутаторы, первый компаратор, переключатели, источник эталонных уровней и эталонный преобразователь, причем первые, вторые, третьи, четвертые, пятые, шестой, седьмой, восьмой и девятый выходы блока интерфейса соединены соответственно с входами блока управления, с третьими входами соответствующих коммутаторов уровня, вторыми входами соответствующих блоков контроля напряжения и тока, управляющими входами соответствующих переключателей, первым входом этаi лонного преобразователя, первым входом второго цифроаналогового преобразователя, первым входом второго коммутатора, первым входом первого |сомпаратора и первым входом третьего § коммутатора, первые, вторые, третьи, чет:.ертые, пятые, шестой, седьмой, восьмой, девятый и десятый входы блока инте1 фейса соединены соответственно с вторыми выходами блока управления, вторыми выходами соответствующих коммутаторов уровня, перЪьми ходами соответствующих блоков конт 9 роля напряжения и тока, вторыми ходами соответствующих блоков контроля напряжения и тока, первыми выходами соответствующих переключателей, первым выходом эталонного преобразователя, первым выходом второго цифроаналогового гфеобразователя, первым выходом второго коммутатора, первым выходом третьего коммутатора и выходом первого компаратора, соединенного вторым входом с выходом первого аналогового сумматора, третьим входом - с вторым выходом третьего

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многоканальная система контроля параметров электронных схем | |||

| Электронная промышленность, 1980, № 6, с | |||

| Пишущая машина для тюркско-арабского шрифта | 1922 |

|

SU24A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3622876, кл | |||

| Телефонный аппарат, отзывающийся только на входящие токи | 1921 |

|

SU324A1 |

Авторы

Даты

1984-09-07—Публикация

1982-07-08—Подача