Изобретение относится к вычислительной технике и может быть использовано при разработке прецизионных цифроаналоговых преобразователей.

Цель изобретения - упрощение и расширение области использования устройства.

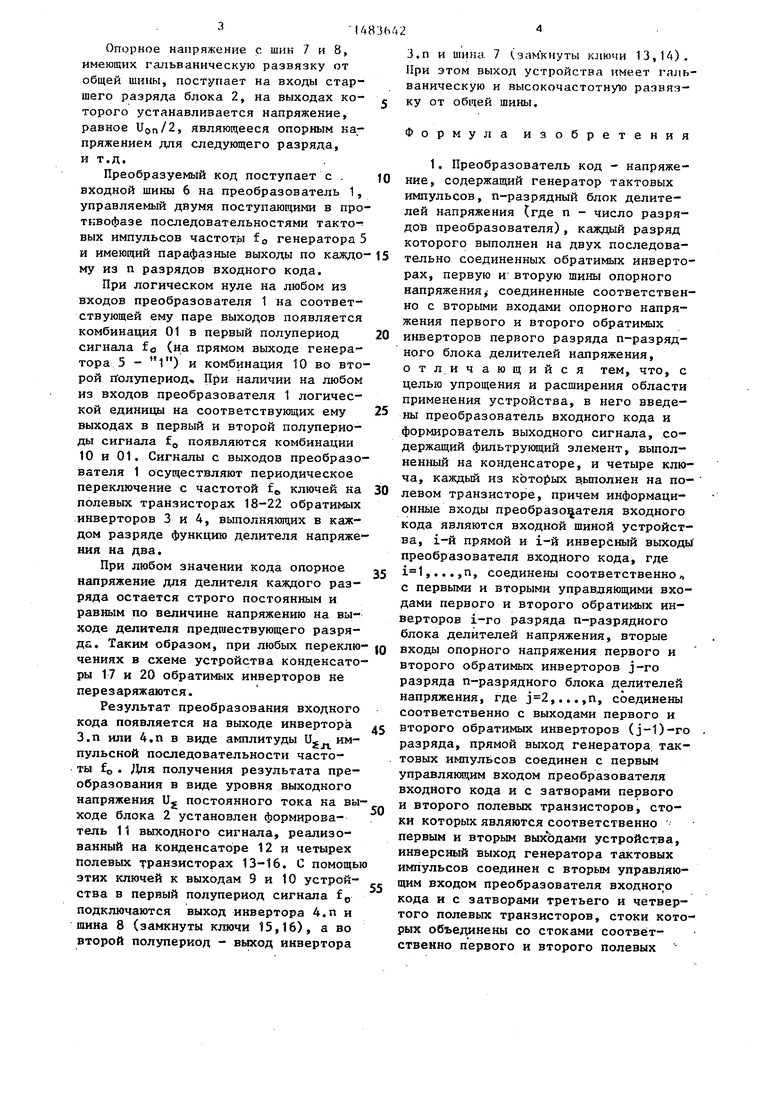

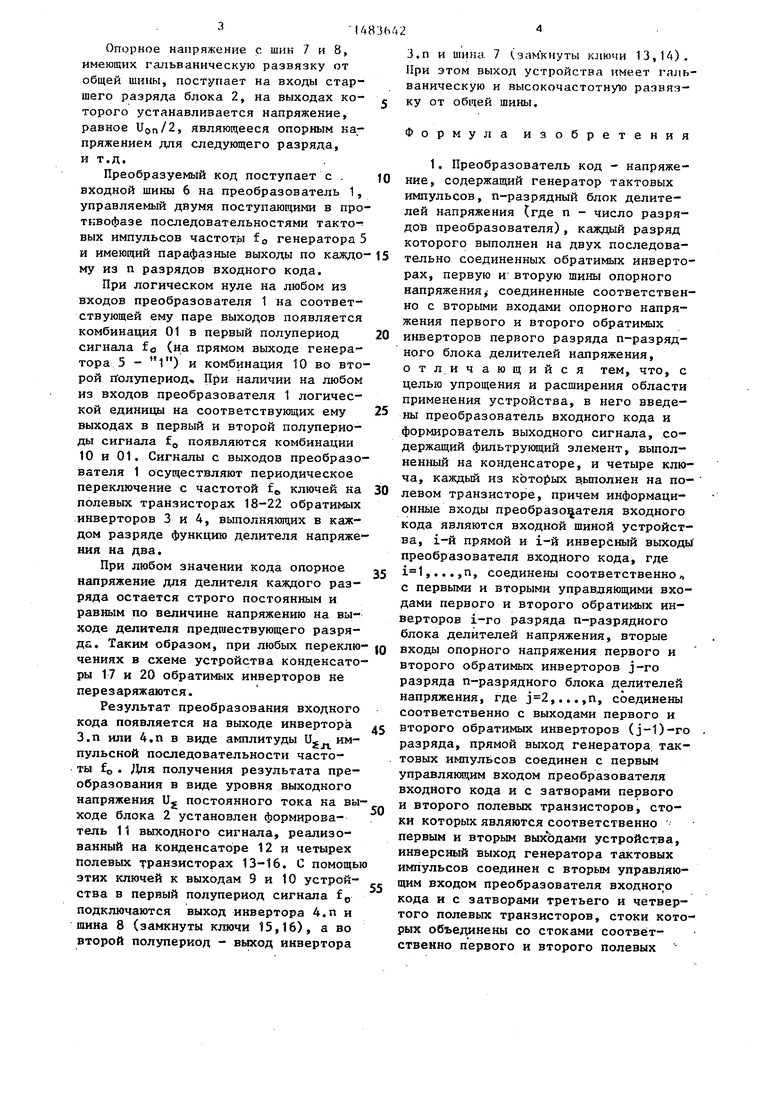

На чертеже представлена функциональная схема устройства.

Устройство содержит преобразователь 1 входного кода, п-разрядный блок 2 делителей напряжения, каждый разряд которого выполнен на двух последовательно соединенных обратимых инверторах 3 и 4, генератор 5 тактовых импульсов, входную шину 6, шины 7 и 8 опорного напряжения, выходы 9, 10 и формирователь 11 выходного сигнала, содержащий фильтрующий элемент,

выполненный на конденсаторе 12, и четыре ключа, выполненные на полевых транзисторах 13-16.

Первый обратимый инвертор 1-го разряда n-разрядного блока делителей напряжения содержит накопительный элемент, выполненный на конденсаторе 17, и два ключа, выполненные на полевых транзисторах 18 и 19. Второй обратимый инвертор 1-го разряда п-раз- рядного блока делителей напряжения содержит накопительный элемент, выполненный на конденсаторе 20, и два ключа, выполненные на полевых транзисторах 21 и 22. Преобразователь входного.кода содержит п групп из двух элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 23,24.

Устройство работает следующим образом.

I

4 00. ОЭ

N5

3-|4

Опорное напряжение с шин / и 8, имеющих гальваническую развязку от общей шины, поступает на входы старшего разряда блока 2, на выходах ко- торого устанавливается напряжение, равное Uon/2, являющееся опорным напряжением для следующего разряда, и т.д.

Преобразуемый код поступает с . входной шины 6 на преобразователь 1, управляемый двумя поступающими в про- тквофазе последовательностями тактовых импульсов частоты f0 генератора 5 и имеющий парафазные выходы по каждо- му из п разрядов входного кода.

При логическом нуле на любом из входов преобразователя 1 на соответствующей ему паре выходов появляется комбинация 01 в первый полупериод сигнала f0 (на прямом выходе генератора 5 - 1) и комбинация 10 во второй пголупериод. При наличии на любом из входов преобразователя 1 логической единицы на соответствующих ему выходах в первый и второй полупериоды сигнала f0 появляются комбинации 10 и 01. Сигналы с выходов преобразователя 1 осуществляют периодическое переключение с частотой fe ключей на полевых транзисторах 18-22 обратимых инверторов 3 и 4, выполняющих в каждом разряде функцию делителя напряжения на два.

При любом значении кода опорное напряжение для делителя каждого разряда остается строго постоянным и равным по величине напряжению на выходе делителя предшествующего разряда. Таким образом, при любых переклю чениях в схеме устройства конденсаторы 17 и 20 обратимых инверторов не перезаряжаются.

Результат преобразования входного кода появляется на выходе инвертора З.п или 4.п в виде амплитуды К „импульсной последовательности частоты fo . Для получения результата преобразования в виде уровня выходного напряжения Uj постоянного тока ка вы ходе блока 2 установлен формирователь 1t выходного сигнала, реализованный на конденсаторе 12 и четырех полевых транзисторах 13-16. С помощь этих ключей к выходам 9 и 10 устройства в первый полупериод сигнала f0 подключаются выход инвертора 4.п и шина 8 (замкнуты ключи 15,16), а во второй полупериод - выход инвертора

З.п и шина 7 (.зам кнуты ключи 13,14). При этом выход устройства имеет гальваническую и высокочастотную развяч- ку от общей шины.

Формула

и з

обретения

1. Преобразователь код - напряжение, содержащий генератор тактовых импульсов, n-разрядный блок делителей напряжения (где п - число разрядов преобразователя), каждый разряд которого выполнен на двух последовательно соединенных обратимых инверторах, первую и вторую шины опорного напряжения,- соединенные соответственно с вторыми входами опорного напряжения первого и второго обратимых инверторов первого разряда п-разряд- ного блока делителей напряжения, отличающийся тем, что, с целью упрощения и расширения области применения устройства, в него введены преобразователь входного кода и формирователь выходного сигнала, содержащий фильтрующий элемент, выполненный на конденсаторе, и четыре ключа, каждый из которых в.ыполнен на по- левом транзисторе, причем информационные входы преобразователя входного кода являются входной шиной устройства, i-й прямой и i-й инверсный выходы преобразователя входного кода, где ,...,п, соединены соответственно „ с первыми и вторыми управляющими входами первого и второго обратимых инверторов 1-го разряда п-разрядного блока делителей напряжения, вторые входы опорного напряжения первого и второго обратимых инверторов j-ro разряда n-разрядного блока делителей напряжения, где ,...,n, соединены соответственно с выходами первого и второго обратимых инверторов (j-1)-ro разряда, прямой выход генератора тактовых импульсов соединен с первым управляющим входом преобразователя входного кода и с затворами первого и второго полевых транзисторов, стоки которых являются соответственно первым и вторым выхЪдами устройства, инверсный выход генератора тактовых импульсов соединен с вторым управляющим входом преобразователя входного кода и с затворами третьего и четвертого полевых транзисторов, стоки которых объединены со стоками соответственно первого и второго полевых

транзисторов, потоки первого u четвертого поиевых гранчисторов подключены соотнетственно к второй и первой шинам опорного напряжения, исток третьего полевого транзистора соединен с первым выводом конденсатора и с выходом первого обратимого инвертора n-го разряда n-разрядного блока делителей напряжения, исток второго полевого транзистора соединен с вторым выводом конденсатора и с выходом второго обратимого инвертора n-го разряда n-разрядного блока делителей напряжения .

2.Преобразователь по п. 1, отличающийся тем, что преобразователь входного кода выполнен на п группах из двух элементов ИСКЛЮЧАЮЩЕЕ ИЛИ каждая, первые входы первых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ п групп объединены между собой и являются первым управляющим входом блока, первые входы вторых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ п групп объединены между собой и являются вторым управляющим входом блока, вторые входы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ i-й группы объединены и являются i-м информационным входом блока, выходы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ i-й группы являются соответственно i-м инверсным и i-м прямым выходами блока.

3.Преобразователь по п. 1, отличающийся тем, что первый обратимый инвертор содержит два клют

« h- . ч а

0

5

каждый нч которых выполнен на полевом транзисторе, ,и накопительный элемент, выполненный на конденсаторе, первый и второй выходы которого являются соответственно первым и вторым входами опорного напряжения и соединены со стоком второго и истоком первого полевых транзисторов соответственно, сток первого полевого транзистора соединен с истоком второго полевого транзистора и является выходом первого обратимого инвертора, затворы первого и второго обратимых инверторов являются соответственно первым и вторым управляющими входами первого обратимого инвертора. 4. Преобразователь по п. отличающийся тем, что второй обратимый инвертор содержит два ключа, каждый из которых выполнен на-полевом транзисторе, и накопительный элемент, выполненный на конденсаторе, первый и второй выводы которого

25 являются соответственно вторым и первым входами опорного напряжения второго обратимого инвертора и соединены со стоком второго и истоком первого полевых транзисторов соответственно,

0 сток первого полевого транзистора соединен с истоком второго полевого транзистора и является выходом второго обратимого инвертора, затворы первого и второго обратимых инверторов являются соответственно первым и вторым управляющими входами второго обратимого инвертора.

0

35

.О

-v 6

:.. °..

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь | 1985 |

|

SU1398099A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ТОКА | 2019 |

|

RU2728284C1 |

| Вероятностный аналого-цифровой преобразователь | 1987 |

|

SU1531216A1 |

| Преобразователь напряжение-код | 1983 |

|

SU1256207A1 |

| ИСТОЧНИК ПИТАНИЯ НЕЛИНЕЙНОЙ ИЛИ ЛИНЕЙНОЙ НАГРУЗКИ | 2021 |

|

RU2768272C1 |

| Преобразователь заряд-число | 1979 |

|

SU819960A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1297228A1 |

| Измерительный преобразователь напряжения в частоту | 1985 |

|

SU1241423A1 |

| ЭЛЕКТРИЧЕСКИЙ ИМИТАТОР СТАЦИОНАРНОГО ПЛАЗМЕННОГО ДВИГАТЕЛЯ | 2024 |

|

RU2830092C1 |

| СПОСОБ ИЗМЕРЕНИЯ МАЛЫХ СОПРОТИВЛЕНИЙ, В ТОМ ЧИСЛЕ И СОПРОТИВЛЕНИЯ СТОК-ИСТОК ОТКРЫТОГО КАНАЛА ПОЛЕВОГО ТРАНЗИСТОРА | 2011 |

|

RU2451297C1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке прецизионных цифроаналоговых преобразователей. Цель изобретения - упрощение и расширение области применения устройства. Поставленная цель достигается за счет введения в устройство преобразователя входного кода и формирователя выходного сигнала, что позволило упростить N = разрядное соединение делителей напряжения, выполненных на обратимых инверторах, и сформировать результат преобразования, имеющий гальваническую и высокочастотную развязку от общей шины. 3 з.п. ф-лы, 1 ил.

| Авторское свидетельство СССР № ЗЗОЬЗб, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Грехов Ю.Н | |||

| Преобразователь код - напряжение на коммутируемых конденсаторах | |||

| - Приборы и техника эксперимента, 1975, ff 6, 98-100, рис | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1989-05-30—Публикация

1986-06-04—Подача