| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для компенсации виброакустического поля | 1982 |

|

SU1073795A1 |

| АДАПТИВНОЕ УСТРОЙСТВО ЗАЩИТЫ РАДИОЛОКАЦИОННОЙ СТАНЦИИ ОТ ПАССИВНЫХ ПОМЕХ | 1994 |

|

RU2097781C1 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ СИГНАЛОВ ПЕРЕДАЧИ В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 2001 |

|

RU2233553C2 |

| Цифровой нерекурсивный фильтр | 1986 |

|

SU1350826A2 |

| СПОСОБ ОБНАРУЖЕНИЯ ДВИЖУЩИХСЯ ЦЕЛЕЙ В ГИДРОЛОКАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2357269C2 |

| Нерекурсивный цифровой фильтр-дециматор | 1982 |

|

SU1109890A1 |

| Устройство для симметрирования токов трехфазных сетей | 1988 |

|

SU1686600A1 |

| ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2008 |

|

RU2393641C1 |

| СПОСОБ И УСТРОЙСТВО ОПРЕДЕЛЕНИЯ МЕСТОПОЛОЖЕНИЯ ИСТОЧНИКА РАДИОИЗЛУЧЕНИЯ | 2011 |

|

RU2465613C1 |

| Цифровой анализатор спектра по функциям уолша | 1975 |

|

SU636554A1 |

Изобретение относится к технической акустике и может быть использовано для компенсации акустических колебаний, возникающих в механических конструкциях и средах под действием работающих источников стационарных колебаний, например механизмов. Цель изобретения - увеличение быстродействия работы устройства. Обработка сигналов с помощью быстрых преобразователей Фурье позволила осуществить одновременное управление коэффициентами нерекурсивного фильтра и увеличить быстродействие работы устройства, так как время сходимости предложенного процесса компенсации равно одному циклу управления. 1 з.п. ф-лы, 3 ил.

О

с

Фив. г

Изобретение относится к технической акустике и может быть использовано для компенсации акустических колебаний, возникающих в механических конструкциях и средах под действием работающих источников колебаний.

Цель изобретения - увеличение быстродействия работы устройства.

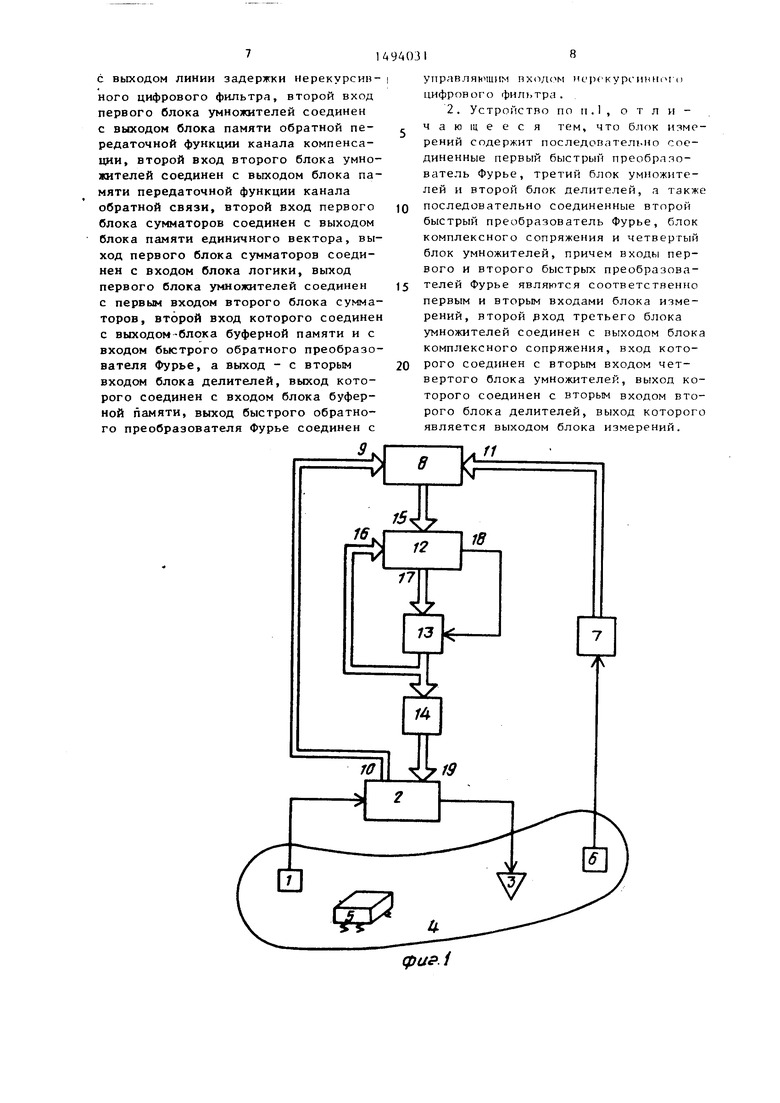

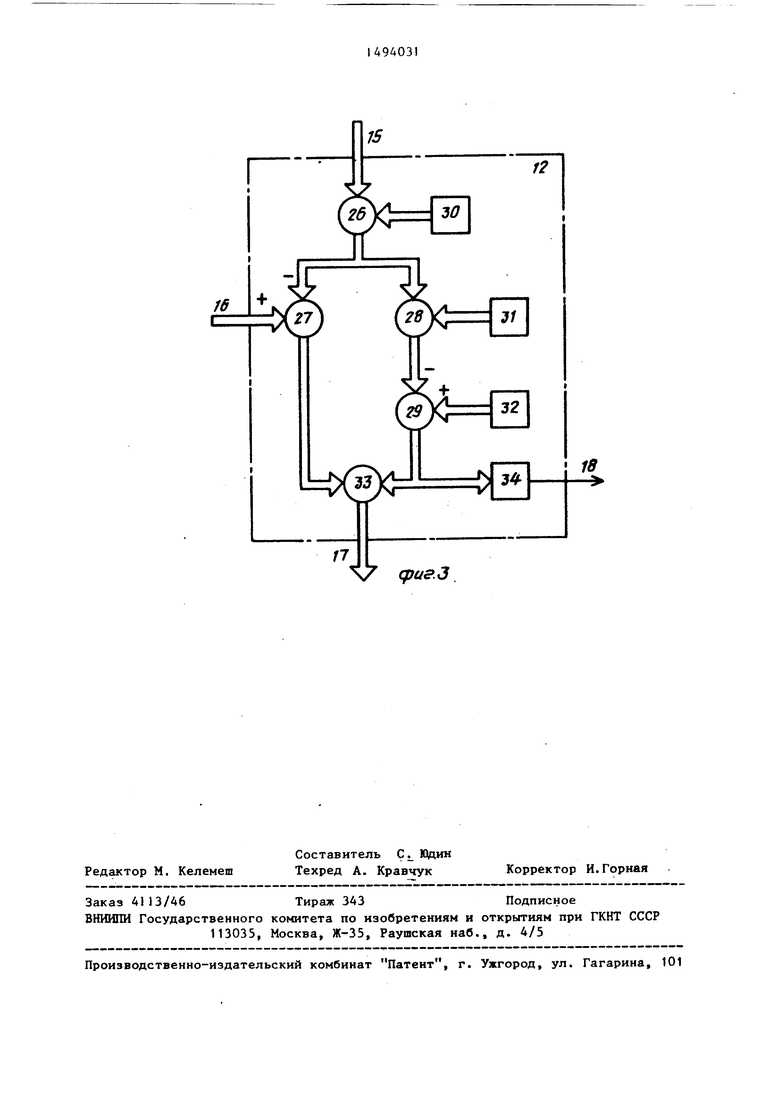

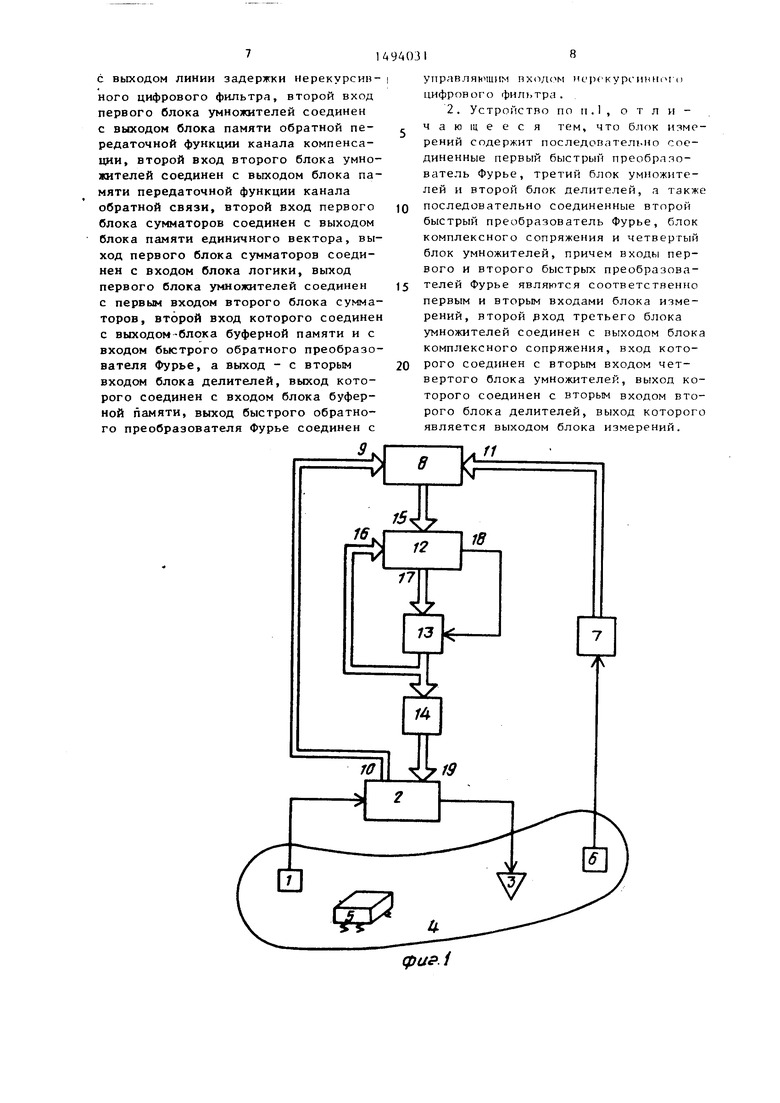

На фиг. 1 приведена схема пред- ложенного устройства; на фиг. 2 - схема блока измерений; на фиг. 3 - схема вычислителя.

Устройство для компенсации акустических колебаний в конструкциях и средах содержит последовательно соединенные приемник 1 колебаний, нерекурсивный цифровой фильтр 2 и излучатель 3, установленный на конструкции или среде 4, возбуждаемой механизмом 5, последовательно соединенные контрольный приемник 6, установленный в области компенсации, и линию задержки 7, блок 8 измерений, вход 9 которого соединен с выходом 10 линии за- держки фильтра 2, а вход 11 - с выходом линии 7 задержки, вычислитель 12, блок 13 буферной памяти и быстрый обратный преобразователь 14 Фурье, причем вычислитель 12 входом 15 подключен к выходу блока 8 измерений входом 16 - к выходу блока 13 буфер- -ной памяти и входу преобразователя I4, выходом 17 - к входу блока 13 буферной памяти, а выходом 18 - к выход записи блока 13 буферной памяти, а выход преобразователя 14 соединен с управляющим входом 19 фильтра 2.

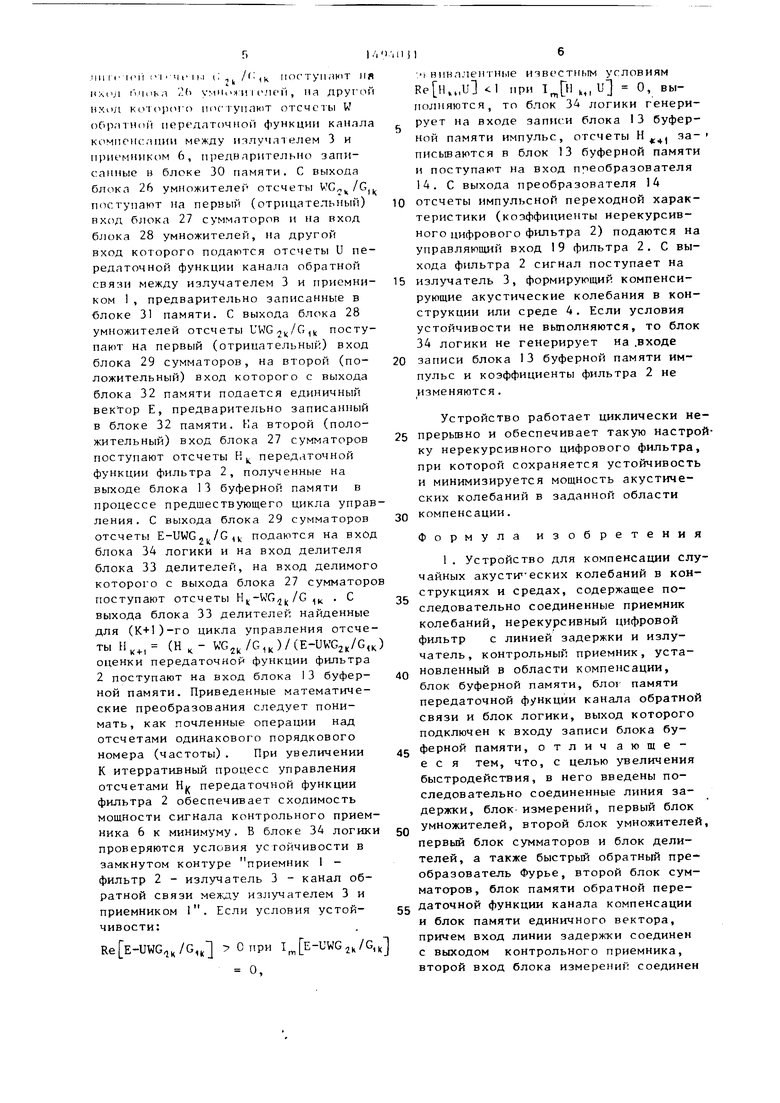

Блок-8 измерений содержит быстрые преобразователи 20 и 21 Фурье, входы которых являются соответственно входами 9 и II блока 8 измерений, блоки

22и 23 умножителей, первые входы которых соединены с выходами соответственно преобразователей 20 и 21, блок 24 комплексного сопряжения,

вход которого объединен с первым вхо- ом блока 22 умножителей, а выход подключен к вторым входам блоков 22

23умножителей, и блок 25 делителей, вход делителя которого соединен с выходом блока 22 умножителей, вход делимого - с выходом блока 23 умножителей, а выход является выходом блока 8 измерений.

Вьнислитель I2 содержит блок 26 уножителей, первый вход которого является входом 15 вычислителя 12, блок

27 сумматоров, первый (положительный) вход которого является входом I6 вычислителя 12, блок 28 умножителей, первый вход которого соединен с выходом блока 26 умножителей и с вторым (отрицательным) входом блока 27 сумматоров, блок 29 сумматоров, первый (отрицательный) вход которого свзан с выходом блока 28 умножителей, блок 30 памяти обратной передаточной функции канала компенсации, выходом подключенный к второму входу блока 26 умножителей, блок 31 памяти передаточной функции канала обратной связи, выход которого соедине с вторым входом блока 28 умножителей, блок 32 памяти единичного вектора, выход которого связан с вторым (положительным) входом блока 29 сумматоров, блок 33 делителей, вход делимого которого соединен с выходом блока 27 сумматоров, а его выход является выходом 17 вычислителя 12, и блок 34 логики, вход которого соединен с выходом блока 29 сумматоров и с входом делителя блока 33 делителей, а выход является выходом 18 вычислителя 12.

Устройство работает следующим образом.

Сигнал приемника I поступает на вход фильтра 2, формирующего сигнал возбуждения излучателя 3. С выхода 10 линии задержки фильтра 2 временные отсчеты сигнала приемника 1 подаются на вход преобразователя 20. Одновременно сигнал контрольного приемника 6 поступает на вход линии 7 задержки, с отводов которой временные отсчеты сигнала поступают на вход преобразователя 21. С выходов преобразователей 20 и 21 частичные отсчеты фурье-образов сигналов приемников 1 и 6 подаются на входы соответственно блоков 22 и 23 умножителей, на другие входы которых с выхода блока 24 комплексного сопряжения поступают отсчеты, комплексно сопряженные отсчетам фурье-образа сигнала приемника I, В К-й цикл управления фильтром 2 с выходов блоков 22 и 23 умножителей соответственно отсчеты спектральной плотности сигнала приемника 1 и отсчеты GJH взаимной спектральной плотности сигналов приемников 6 и 1 поступают на входы делителя и делимого блока 25 делителей. С выхода блока 23 де

ми I loi t 1-1 ч с I ).i ,K погтуп.чют 11Я nxivi i i44b,i 2b умичя 11 I еле й , па друт ой нхчд Kii icipoi o ног rynnniT отсчеты W оОр. П Hofi передлточиой функции наняла компеис лаии между излучл1едем 3 и приемиикч М 6, предварительно записанные в блоке 30 памяти. С выхода блока 26 умножителей отсчеты , поступают па первый (отрицательный) вход блока 27 сумматоров и на вход блока 28 умножителей, на другой вход которого подаются отсчеты U передаточной функции канала обратной связи между излучателем 3 и приемни- ком 1, предварительно записанные в елоке 31 памяти. С выхода блока 28 умножителей отсчеты поступают на первый (отрицательный) вход блока 29 сумматоров, на второй (по- ложительный) вход которого с выхода блока 32 памяти подается единичный вектор Е, предварительно записанный в блоке 32 памяти. На второй (положительный) вход блока 27 сумматоров поступают отсчеты К | передаточной функции фильтра 2, полученные на выходе блока 13 буферной памяти в процессе предшествующего цикла управления . С выхода блока 29 сумматоров отсчеты E-UWGji /G ,k; подаются на вход блока 34 логики и на вход делителя блока 33 делителей, на вход делимого которого с выхода блока 27 сумматоро поступают отсчеты ,/G ,«; . С выхода блока 33 делителей найденные для (К+1)-го цикла управления отсчеты Н, (Н - ,J/(E-UWG2 /G,J оценки передаточной функции фильтра 2 поступают на вход блока 13 буфер- ной памяти. Приведенные математические преобразования следует понимать, как почленные операции над отсчетами одинакового порядкового Номера (частоты). При увеличении К итерративный процесс управления отсчетами Н передаточной функции фильтра 2 обеспечивает сходимость мощности сигнала контрольного приемника 6 к минимуму. В блоке 34 логики проверяются условия устойчивости в замкнутом контуре приемник 1 - фильтр 2 - излучатель 3 - канал обратной связи между излучателем 3 и приемником 1. Если условия устой- чивости:

Re E-UWG,/G,, С при I E-UWG2K/G, 0.

ч ннвл.чентные известным условиям .,и 1 при k,, и О, выполняются, то блок 34 логики генерирует на входе записи блока 13 буферной памяти импульс, отсчеты Н за- письшаются в блок 13 буферной памяти и поступают на вход преобразователя 14. G выхода преобразователя 14 отсчеты импульсной переходной характеристики (коэффициенты нерекурсивного цифрового фильтра 2) подаются на управляющий вход 19 фильтра 2. С выхода фильтра 2 сигнал поступает на излучатель 3, формирующий компенсирующие акустические колебания в конструкции или среде 4. Если условия устойчивости не выполняются, то блок 34 логики не генерирует на .входе записи блока 13 буферной памяти импульс и коэффициенты фильтра 2 не изменяются.

Устройство работает циклически не- прерьшно и обеспечивает такую настройку нерекурсивного цифрового фильтра, при которой сохраняется устойчивость и минимизируется мощность акустических колебаний в заданной области компенсации.

Формула изобретения

с выходом линии задержки нерекурсив- ного цифрового фильтра, второй вход первого блока умножителей соединен с выходом блока памяти обратной передаточной функции канала компенсации, второй вход второго блока умножителей соединен с выходом блока памяти передаточной функции канала обратной связи, второй вход первого блока сумматоров соединен с выходом блока памяти единичного вектора, выход первого блока сумматоров соединен с входом блока логики, выход первого блока умножителей соединен с первым входом второго блока сумматоров, второй вход которого соединен с выходом-блока буферной памяти и с входом быстрого обратного преобразователя Фурье, а выход - с вторым входом блока делителей, выход которого соединен с входом блока буферной памяти, выход быстрого обратного преобразователя Фурье соединен с

управлянмиим нход. нс рскурс ииного цифрового фил))Тра .

последовательно соединенные второй быстрый преобразователь Фурье, блок комплексного сопряжения и четвертый блок умножителей, причем входы первого и второго быстрых преобразователей Фурье являются соответственно первым и вторым входами блока измерений, второй рход третьего блока умножителей соединен с выходом блока комплексного сопряжения, вход которого соединен с вторым входом четвертого блока умножителей, выход которого соединен с вторым входом второго блока делителей, выход которого является выходом блока измерений.

фа.1

п

7 (риг.З

| Устройство для компенсации виброакустического поля | 1982 |

|

SU1073795A1 |

| G Ю К П/00, опублик | |||

| Гальванический элемент | 1920 |

|

SU984A1 |

Авторы

Даты

1989-07-15—Публикация

1987-01-30—Подача