4

со 4 ю

314

Изобретение относится к радиотехнике и связи и может быть использовано в вычислительной технике и автоматике.Цель изобретения - обеспечение оперативного изменения коэффициента умножения частоты в широком диапазоне частот входного сигнала.

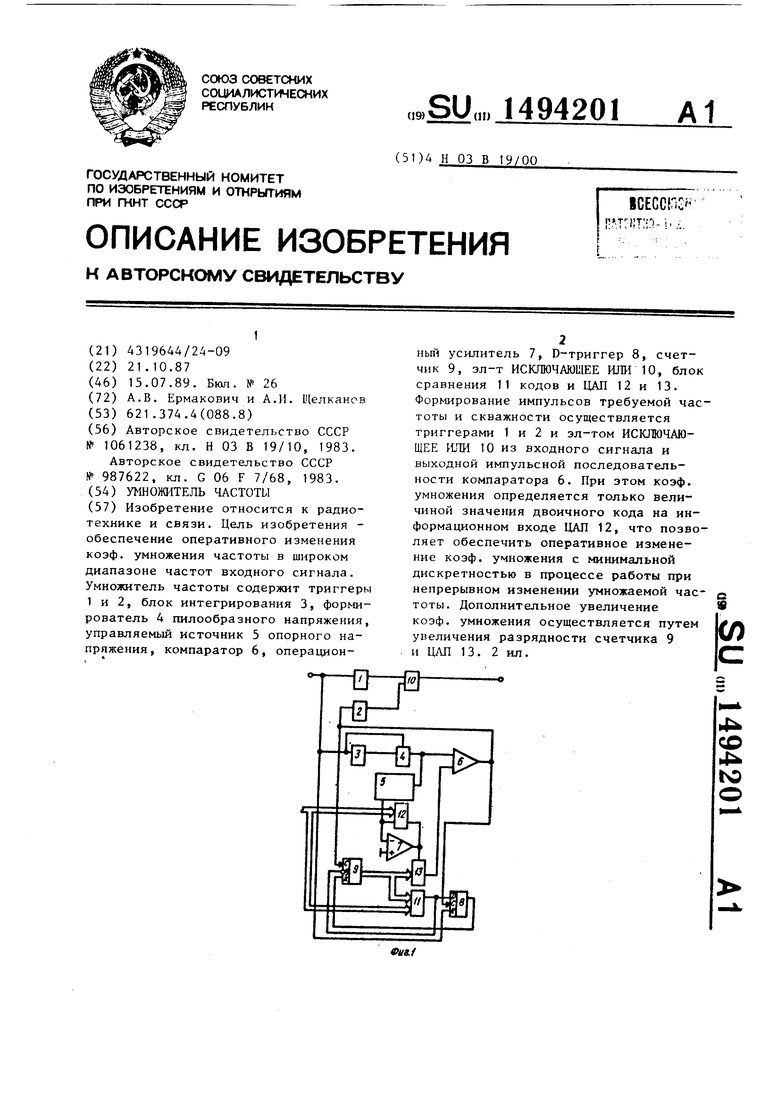

На фиг. 1 представлена структур- ная электрическая схема умножителя, частотыi на фиг. 2 - временные диаграммы, поясняющие его работу.

Умножитель частоты содержит первый 1 и второй 2 триггеры,блок 3 интегрирования, формирователь 4 пилообразного напряжения, управляемый источник 5 опорного напряжения, компаратор 6, операционный усилитель 7, D-триггер 8, счетчик 9, элемент ИСКПЮЧАЮР1ЕЕ ИЛИ 10, блок 11 сравнения кодов и первый 12 и второй 13 цифроаналоговые преобразователи.

Умножитель частоты работает следующим образом,

Последовательность прямоугольных импульсов со скваж юстью равной двум поступает на вход блока 3, на установочный вход D-триггера 8 и на первый вход формирователя 4, на второй вход которого поступает сигнал с выхода блока 3. Пилообразное напряжени с. выхода формирователя 4 поступает на первый вход компаратора 6 и на управляющий вход управляемого источника 5.

Выходное напряжение Кд управляемого ис- -очника 5 поступает на инвер- тирующи вход операционного усилителя 7, на выходе которого формируется выходное напряжение U,, зависящее от значения U и от значения двоичного кода N на информационном входе первого 1дифроаналогового преобразователя 12.

и,.и„|:.

где-п - число разрядов преобразова- ния цифроаналоговых преобразователей 12 и 13. Напряжение U, формируемое на выходе второго цифроаналогового преобразователя 13 и определяемое зна- чением U , на его опорном входе и значением двоичного кода N на выходе счетчика 9, поступает на второй вход компаратора 6.

и . 1 2

и N К

При каждом равенстве напряжений на первом и втором входах компаратора 6 последний срабатьшает, в результате чего значение двоичного кода на выходе счетчика 9 увеличивается иа единицу, а напряжение на выходе второго цифроаналогового преобразователя 13 возрастает на величину

ли i %

Как только вьтолнится равенство Nm N,-1 ,

что соответствует достижению значения напряжения на втором входе компаратора 6

,-.

на выходе блока сравнения 11 устанавливается 1, запрещая дальнейшее изменение состояний счетчика 9 по сигналу на его счетном входе.

При достижении пилообразным напряжением и на первом входе компаратора 6 значения

и и

TI

и в -

k

по фронту выходного сигнала компаратора 6 1 (с выхода блока сравнения 11) переписывается в D-триггер 8, устанавливая счетчик 9 в исходное состояние, что приводит к установлению на выходе блока 11 сравнения О, а напряжение на выходе второго цифро- аналогового преобразователя 13 принимает значение

и

1

N

и о -

с приходом очередного импульса умножаемой частоты D-триггер 8 устанавливается в исходное .состояние, снова разрешая работу всего умножителя частоты в цепом. ,1

Формирование импульсов требуемой частоты и требуемой скважности осуществляется триггерами 1 и 2 и элементом 10 из входного сигнала и выходной импульсной последовательности компаратора 6 согласно приведенным

на фиг. 2 временным диаграммам, где представлены входной сигнал умножителя частоты (фиг. 2а), выходной сигнал первого триггера 1 (фиг. 2б), выходной сигнал блока 3 (фиг. 2в), сигналы на первом и втором входах компаратора 6 (фиг. 2г), сигнал на выходе компаратора 6 (фиг. 2д), сигналы на выходах i epaoro, второго и третьего разрядов счетчика 9 (фиг. 2е,ж,з), сигнал на выходе блока сравнения 11 (фиг. 2и), сигнал на выходе D-триггера 8 (фиг. 2к), сигнал на выходе второго триггера (фиг. 2л), сигнал на выходе умножителя частоты (фиг. 2м).

Частота следования импульсов на выходе элемента 10

eirr

N

к

где f gx - частота входного сигнала.

Таким образом, коэффициент жения определяется только величиной N|, что позволяет обеспечить оперативное изменение коэффициента умножения с минимальной дискретностью в процессе его работы лрн непрерывном изменении умножаемой частоты.

Дополнительное увеличение коэффициента умножения умножителя частоты осуществляется путем увеличения разрядности счетчика 9 и второго цифро- аналогового преобразователя 13.

Формула изобретения

Умножитель частоты, содержащий блок интегрирования, компаратор, управляемый источник опорного напряжения и первый триггер, причем счетный вход первого триггера соединен с входом блока интегрирования, а первый вход компаратора -. с управляющим входом управляемого источника опорного напряжения, отличающийся тем, что, с целью обеспе0

5

0

5

0

5

0

5

чения оперативного изменения коэффициента умножения частоты в широком диапазоне частот входного сигнала, введены последовательно соединенные счетчик, блок сравнения кодов и D-триггер, второй триггер, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, формирователь пилообразного напряжения, первый и второй цифроаналоговые преобразователи и операционный усилитель, выход которого соединен с опорными входами первого и второго цифроаналоговых преобразователей, выход управляемого источника опорного напряжения соединен с выходом первого цифроаналогово- го преобразователя и с инвертирующим входом операционного усилителя, неинвертирующий вход которого соединен с общей шиной, выход счетчика соединен с информационным входом второго цифроаналогового преобра зователя, выход которого соединен с вторым входом компаратора, установочный вход D-триггера соединен с входом блока интегрирования и с первым входом формирователя пилообразного напряжения, второй вход которого соединен с выходом блока интегрирования, выход формирователя пилообразного напряжения соединен с первым входом компаратора, выход которого соединен со счетными входами второго триггера, счетчика и D-триггера, выход блока сравнения кодов соединен с управляющим входом счетчика, установочный вход которого соединен с выходом D-триггера, информационный вход первого цифроаналогового преобразователя соединен с вторым информационным входом блока сравнения кодов и является входом установки коэффициента умножения, выходы первого и второго триггеров соединены соответственно с первым и вторым входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом умножителя частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1986 |

|

SU1429133A1 |

| Умножитель частоты | 1989 |

|

SU1672476A1 |

| Электропривод постоянного тока | 1986 |

|

SU1661951A1 |

| Устройство для счета движущихся объектов | 1985 |

|

SU1312623A1 |

| Умножитель частоты | 1981 |

|

SU1020961A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1481887A1 |

| ЛАЗЕРНЫЙ ИМПУЛЬСНЫЙ ДАЛЬНОМЕР | 2014 |

|

RU2551700C1 |

| Устройство для измерения времени установления цифроаналогового преобразователя | 1986 |

|

SU1432776A1 |

| Аналого-цифровой частотомер | 1988 |

|

SU1712894A1 |

| ЦЕЗИЕВЫЙ СТАНДАРТ ЧАСТОТЫ | 1994 |

|

RU2076411C1 |

Изобретение относится к радиотехнике и связи. Цель изобретения - обеспечение оперативного изменения коэффициента умножения частоты в широком диапазоне частот входного сигнала. Умножитель частоты содержит триггеры 1 и 2, блок интегрирования 3, формирователь 4 пилообразного напряжения, управляемый источник 5 опорного напряжения, компаратор 6, операционный усилитель 7, D-триггер 8, счетчик 9, эл-т ИСКЛЮЧАЮЩЕЕ ИЛИ 10, блок сравнения 11 кодов и ЦАП 12 и 13. Формирование импульсов требуемой частоты и скважности осуществляется триггерами 1 и 2 и эл-том ИСКЛЮЧАЮЩЕЕ ИЛИ 10 из входного сигнала и выходной импульсной последовательности компаратора 6. При этом коэф. умножения определяется только величиной значения двоичного кода на информационном входе ЦАП 12, что позволяет обеспечить оперативное изменение коэф. умножения с минимальной дискретностью в процессе работы при непрерывном изменении умножаемой частоты. Дополнительное увеличение коэф. умножения осуществляется путем увеличения разрядности счетчика 9 и ЦАП 13. 2 ил.

| Умножитель частоты следования импульсов | 1982 |

|

SU1061238A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Умножитель частоты | 1981 |

|

SU987622A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-07-15—Публикация

1987-10-21—Подача