Изобретение относится к области вычислительной техники и может быть использовано при построении высоконадежных вычислительных управляющих систем.

Цель изобретения - повышение надежности и упрощение системы.

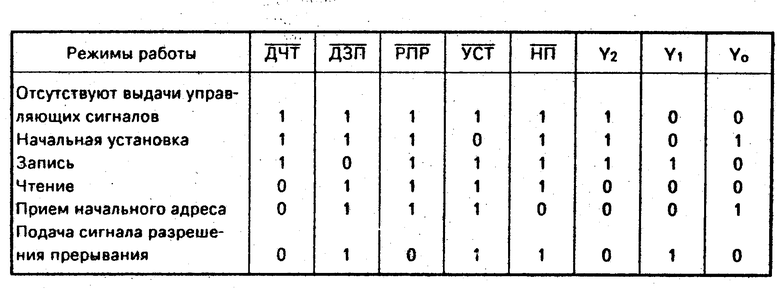

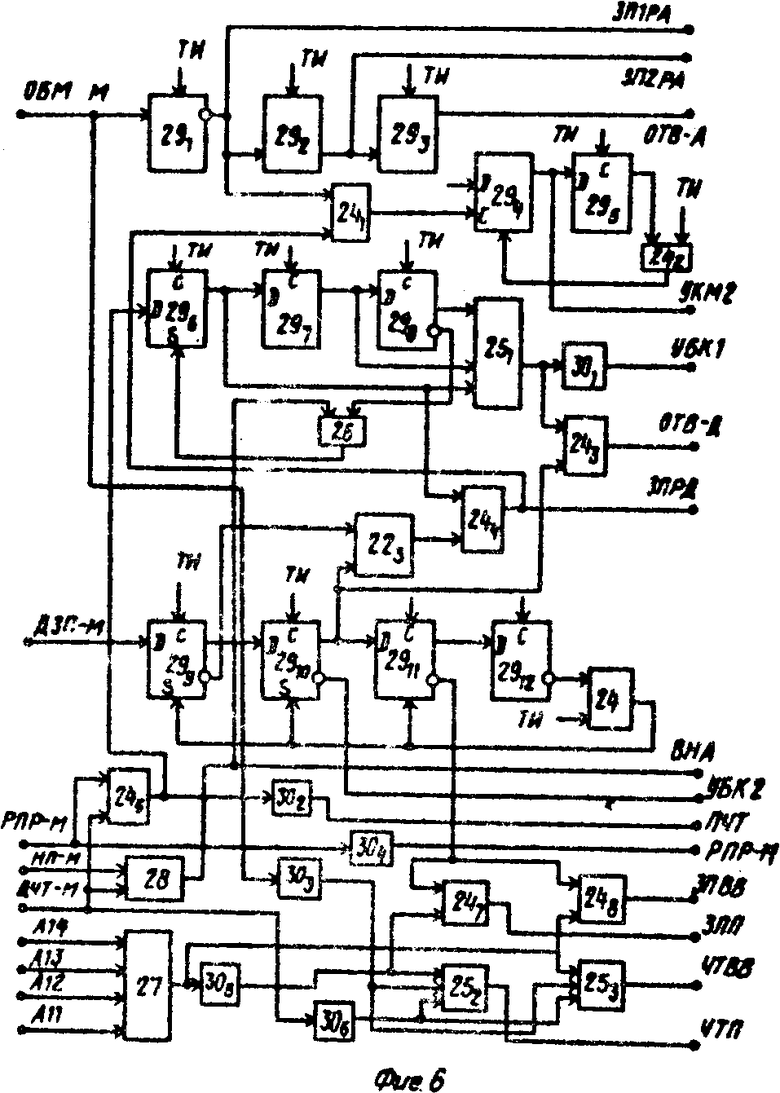

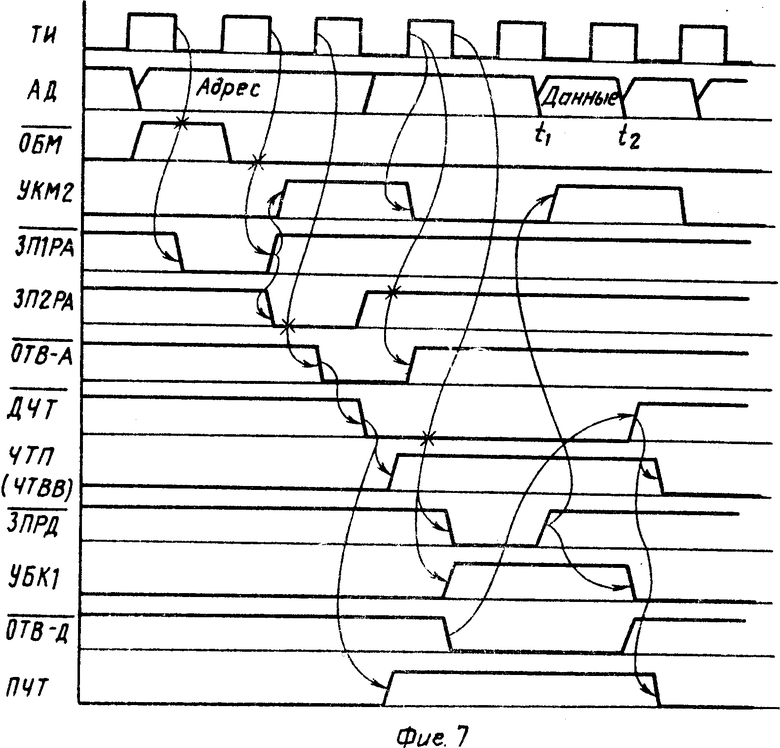

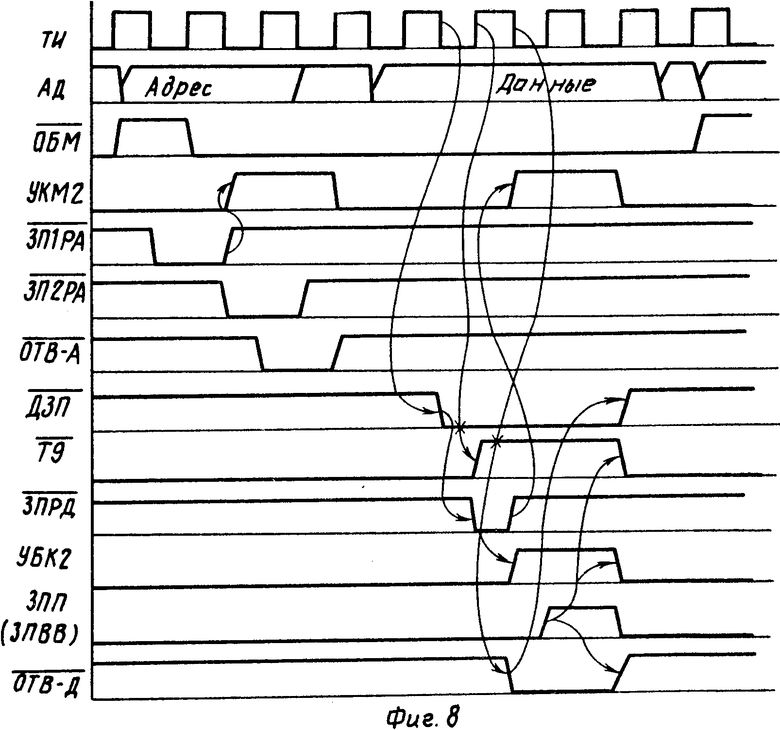

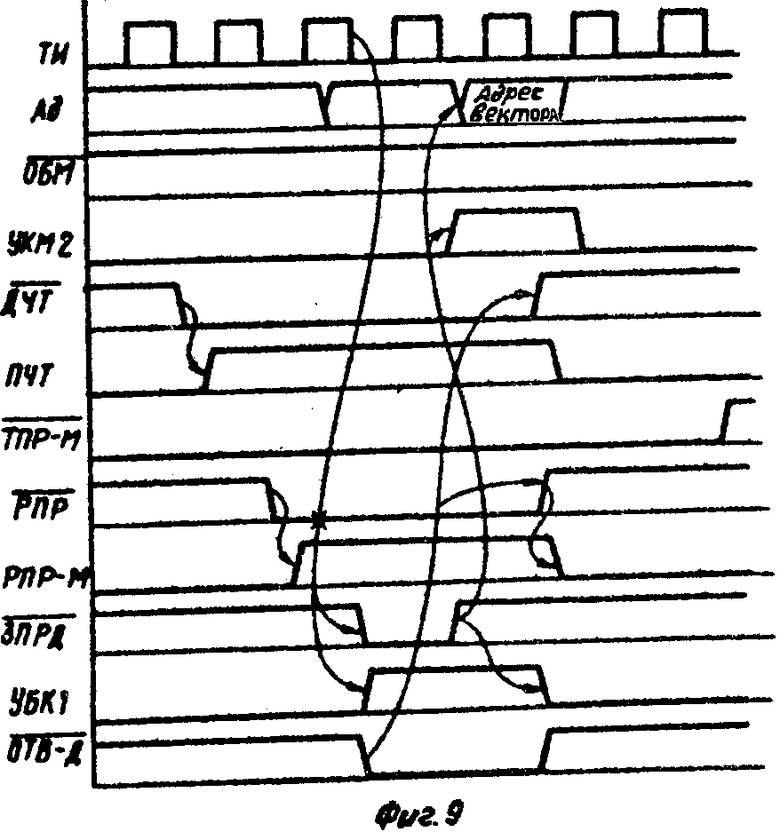

На фиг. 1 представлена функциональная схема системы; на фиг. 2 - функциональная схема первого блока исправления информации; на фиг. 3 - временная диаграмма работы первого блока исправления информации; на фиг. 4 - функциональная схема блока исправления информации в двунаправленной магистрали; на фиг. 5 - функциональная схема второго блока исправления информации; на фиг. 6 - функциональная схема блока управления; на фиг. 7 - временная диаграмма работы системы в режиме чтения данных в микропроцессор; на фиг. 8 - временная диаграмма работы системы в режиме записи данных, выдаваемых из микропроцессора; на фиг. 9 - временная диаграмма работы системы в режиме прерывания.

Система состоит из трех однотипных резервных каналов 1, каждый из которых содержит микропроцессор 2, блок 3 памяти, блок 4 ввода-вывода, регистр 5 адреса, блок 6 управления, блок 7 исправления информации в двунаправленной магистрали, первый блок 8 исправления информации, второй блок 9 исправления информации.

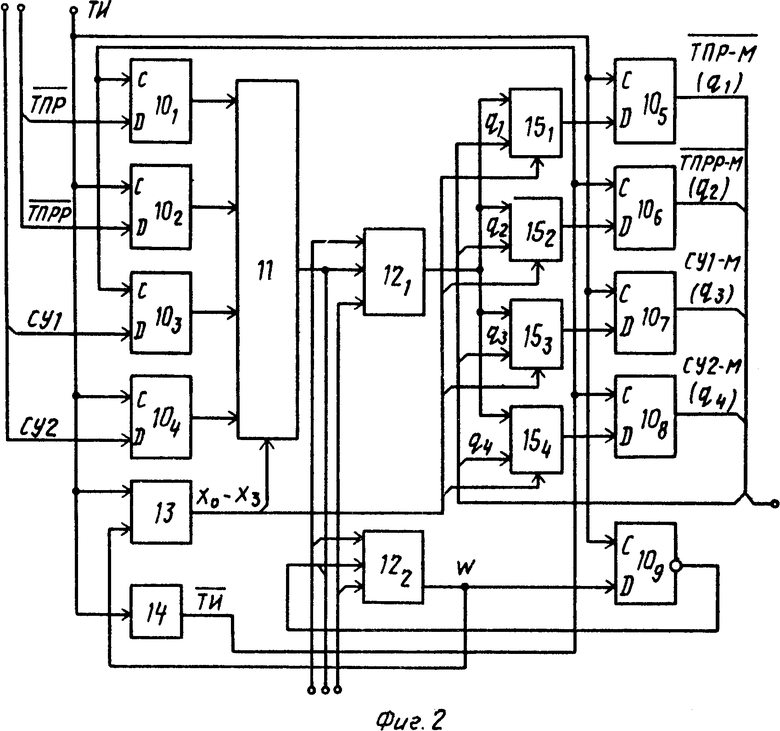

В состав первого блока исправления информации входят триггеры 101-109, четырехвходовый коммутатор 11, мажоритарные элементы 121, 122, дешифратор 13, элемент НЕ 14, двухвходовые коммутаторы 151-154.

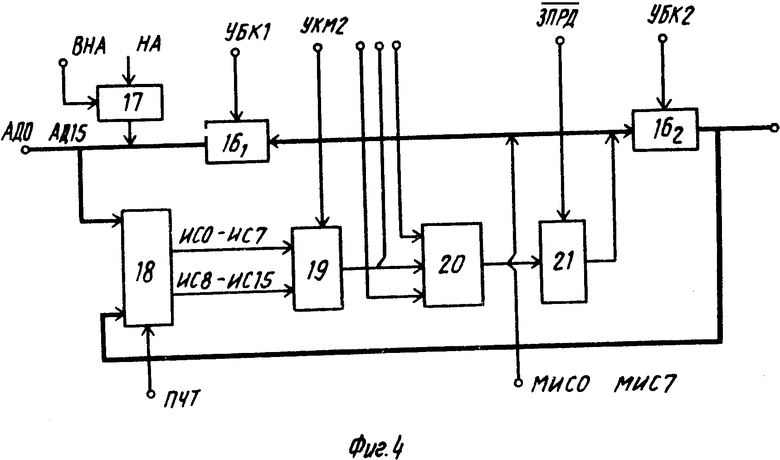

Блок исправления информации в двунаправленной магистрали содержит группы 161, 162 ключей, узел 17 коммутатора, первый коммутатор 18, второй коммутатор 19, группу 20 мажоритарных элементов, регистр 21 данных.

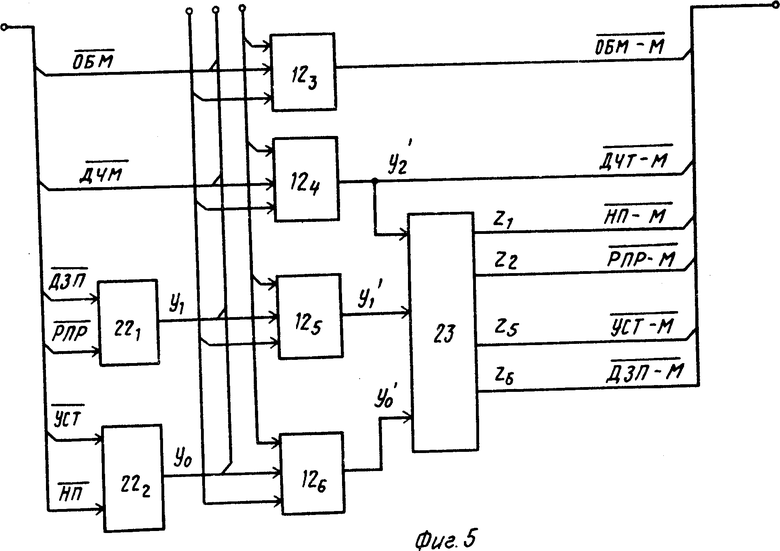

Второй блок исправления информации включает в свой состав мажоритарные элементы 123-126, элементы И-НЕ 221, 222, дешифратор 23.

Блок управления содержит элемент И-НЕ 223, двухвходовые элементы И 241-248, трехвходовые элементы И 251, 252, 253, элемент ИЛИ 26, четырехвходовый элемент И 27, элемент ИЛИ-НЕ 28, триггеры 291-2912, элементы НЕ 301-306.

Предлагаемая система состоит из трех однотипных резервных каналов 1, которые обозначены литерами А, В, С (фиг. 1). В состав каждого канала входит микропроцессор 2, обеспечивающий преобразование информации и информационное взаимодействие между составными частями системы. В блоке 3 памяти хранятся программы и данные, используемые микропроцессором. С помощью блока 4 ввода-вывода обеспечивается взаимодействие системы с внешними устройствами; на входы этого блока подается информация с внешних устройств, с выходов блока осуществляется передача информации в эти устройства.

Информационное взаимодействие между микропроцессором 2 и блоками 3 и 4 производится по 16-разрядной двунаправленной мультиплексной магистрали, в сечение которой включен блок 7 исправления информации в двунаправленной магистрали. Этот блок связан с микропроцессором 2 двунаправленной магистралью АД и с блоками 3 и 4 двунаправленной магистралью Д. Блоки 7 всех резервных каналов связаны между собой мажоритарными связями, что обеспечивает работоспособность системы при отказах, возникающих в отдельных каналах. При обмене с блоком 3 производится запись информации в заданную ячейку, либо из заданной ячейки производится считывание информации. Информационный обмен между микропроцессором 2 и блоком 4 осуществляется в результате реализации процедур чтения и записи информации по отношению к программмно-доступным регистрам, содержащимся в блоке 4.

При выполнении операций чтения и записи по отношению к ячейкам блока 3 и регистрам блока 4 магистраль АД работает в режиме разделения времени: сначала по ней передается код адреса ячейки или регистра, а затем - данные. Код адреса принимается в регистр 5 адреса и хранится там до окончания операции обмена. По магистрали Д производится двунаправленная передача данных.

В режиме обработки требования векторного прерывания, поступающего из блока 4 в микропроцессор 2, по магистралям АД, Д передается адрес вектора прерывания.

На входы второго блока 9 исправления информации из микропроцессора 2 подаются следующие сигналы, обеспечивающие выполнение операций обмена на магистралях АД, Д: сигнал обмена  , имеющий нулевое значение при выполнении операций чтения и записи данных; сигнал чтения данных

, имеющий нулевое значение при выполнении операций чтения и записи данных; сигнал чтения данных  , нулевое значение которого указывает на необходимость выполнения операции чтения; сигнал записи данных

, нулевое значение которого указывает на необходимость выполнения операции чтения; сигнал записи данных  , нулевое значение которого указывает на необходимость выполнения операции записи; сигнал разрешения прерывания

, нулевое значение которого указывает на необходимость выполнения операции записи; сигнал разрешения прерывания  , нулевое значение которого указывает на необходимость передачи адреса вектора прерывания из блока 4 в микропроцессор 2; сигнал начальной установки

, нулевое значение которого указывает на необходимость передачи адреса вектора прерывания из блока 4 в микропроцессор 2; сигнал начальной установки  , нулевое состояние которого обеспечивает установку в исходное состояние элементов памяти блока 4; сигнал начального пуска

, нулевое состояние которого обеспечивает установку в исходное состояние элементов памяти блока 4; сигнал начального пуска  , нулевое значение которого возникает одновременно с активным значением сигнала

, нулевое значение которого возникает одновременно с активным значением сигнала  и указывает на необходимость установки на магистрали АД адреса командного слова в памяти, с которого начинается работа системы.

и указывает на необходимость установки на магистрали АД адреса командного слова в памяти, с которого начинается работа системы.

Блоки 9 резервных каналов системы содержат мажоритарные элементы, с помощью которых производится исправление ложных значений вышеуказанных сигналов, которые являются следствием неисправностей или сбоев в одном из резервных каналов. Блоки 9 связаны между собой мажоритарными связями. На выходах блока 9 формируются значения сигналов  ,

,  ,

,  ,

,  ,

,  ,

,  , соответствующих входным сигналам блока, причем сигналы

, соответствующих входным сигналам блока, причем сигналы  и

и  подаются в блок 4, остальные - в блок 6 управления.

подаются в блок 4, остальные - в блок 6 управления.

Регистр 5 содержит 15-разрядный код адреса (А14-А0), с помощью которого производится адресация ячеек блока 3 и программно-доступных регистров блока 4. Значение разряда А14 определяется логическим состоянием старшего разряда магистрали АД в фазе передачи адреса. При А14 = А13 = А12 = А11 = 1 адресуются программно-доступные регистры, причем адреса отдельных регистров задаются значением младших разрядов кода адреса. Остальные значения адресных кодов соответствуют блоку 3. Информационный вход регистра 15 подключен к однонаправленному информационному выходу блока 7.

Информационные входы блоков 3 и 4 подключены к магистрали Д. На управляющие входы блока 3 из блока 6 поступают: сигнал ЗПП записи в блоке 3; сигнал ЧТП чтения из блока 3, признак чтения ПЧТ, определяющий режим работы блока 3 (чтение/запись).

На управляющие входы блока 4 из блока 6 поступают сигналы чтения программно-доступного регистра и записи в регистр (ЧТВВ и ЗПВВ соответственно). Из блока 4 на вход блока 8 подаются сигналы требования векторного ( ) и радиального (

) и радиального ( ) прерываний.

) прерываний.

Работа блока 7 организуется за счет подачи управляющих сигналов из блока 6.

Резервные каналы системы работают строго синхронно. Синхронизация обеспечивается тактовыми импульсами ТИ = А, ТИ = В, ТИ = С, которые взаимно синхронны и синфазны. Импульсы подаются в микропроцессор 2, блоки 6, 8 каждого резервного канала. На входы микропроцессора 2 из блоков 6 подаются сигналы  и

и  , первый из которых определяет окончание фазы передачи адреса по магистрали АД, второй оповещает микропроцессор 2 о приеме выданной им информации либо о подаче информации на его вход по магистрали АД.

, первый из которых определяет окончание фазы передачи адреса по магистрали АД, второй оповещает микропроцессор 2 о приеме выданной им информации либо о подаче информации на его вход по магистрали АД.

Аналогично блокам 9 блоки 8 обеспечивают исправление поступающих на их входы сигналов на основе принципа мажорирования (голосования по принципу 2 и 3).

На входы блока 8 отдельного резервного канала поступают сигналы  и

и  , а также сигналы СУ1 и СУ2, первый из которых обеспечивает начальную установку микропроцессора 2, второй производит пуск микропроцессора (на фиг. 1 для СУ1 и СУ2 использовано обобщенное обозначение СУ). На выходах блока 8 формируются соответственно сигналы

, а также сигналы СУ1 и СУ2, первый из которых обеспечивает начальную установку микропроцессора 2, второй производит пуск микропроцессора (на фиг. 1 для СУ1 и СУ2 использовано обобщенное обозначение СУ). На выходах блока 8 формируются соответственно сигналы  ,

,  , СУ1-М, СУ2-М. В системе должно быть обеспечено условие строгой синхронности подачи этих сигналов на входы микропроцессора 2. Для обеспечения этого условия в блок 8 подаются тактовые импульсы ТИ.

, СУ1-М, СУ2-М. В системе должно быть обеспечено условие строгой синхронности подачи этих сигналов на входы микропроцессора 2. Для обеспечения этого условия в блок 8 подаются тактовые импульсы ТИ.

Блок 8 содержит (см. фиг. 2) четыре входных триггера 101-104, на информационные входы которых поступают сигналы  ,

,  , СУ1, СУ2. Выходы триггеров подключены к входам четырехвходового коммутатора 11, который управляется сигналами Х0-Х3 с выхода дешифратора 13. Формируемые последовательно во времени единичные значения этих сигналов обеспечивают передачу на вход мажоритарного элемента 121 значений сигналов с выходов триггеров 101-104. На выходах триггеров 103-108 формируются значения сигналов

, СУ1, СУ2. Выходы триггеров подключены к входам четырехвходового коммутатора 11, который управляется сигналами Х0-Х3 с выхода дешифратора 13. Формируемые последовательно во времени единичные значения этих сигналов обеспечивают передачу на вход мажоритарного элемента 121 значений сигналов с выходов триггеров 101-104. На выходах триггеров 103-108 формируются значения сигналов  ,

,  , СУ1-М, СУ2-М. К информационному входу каждого из этих триггеров подключены соответственно двухвходовые коммутаторы 151-154, через которые в зависимости от состояния сигнала Хi на выходе дешифратора 13 передается либо значение сигнала с выхода элемента 121(при Хi = 1), либо значение выходного сигнала самого триггера (при Х1 = 0). Таким образом, блок 8 содержит четыре пары триггеров, каждая из которых обеспечивает совместно с коммутатором 11, мажоритарным элементом 121 и коммутаторами 151-154, мажорирование одного из сигналов

, СУ1-М, СУ2-М. К информационному входу каждого из этих триггеров подключены соответственно двухвходовые коммутаторы 151-154, через которые в зависимости от состояния сигнала Хi на выходе дешифратора 13 передается либо значение сигнала с выхода элемента 121(при Хi = 1), либо значение выходного сигнала самого триггера (при Х1 = 0). Таким образом, блок 8 содержит четыре пары триггеров, каждая из которых обеспечивает совместно с коммутатором 11, мажоритарным элементом 121 и коммутаторами 151-154, мажорирование одного из сигналов  ,

,  , СУ2, СУ1. Прием информации в триггеры каждой пары производится по разным фронтам тактовых импульсов ТИ. При единичном значении одного из сигналов Х0-Х3 устанавливается информационная связь между триггерами соответствующей пары. Триггер 109 с подключенным к его информационному входу мажоритарным элементом 122 производит деление частоты сигнала ТИ. На входы дешифpатора 13 подаются сигнал ТИ и сигнал с уменьшенной вдвое частотой, что обеспечивает формирование на выходах дешифратора 13 повторяющейся последовательности импульсов Х0-Х3, каждый из которых имеет длительность τти/2 (τти - длительность периода следования ТИ); период повторения указанной последовательности 2 τти .

, СУ2, СУ1. Прием информации в триггеры каждой пары производится по разным фронтам тактовых импульсов ТИ. При единичном значении одного из сигналов Х0-Х3 устанавливается информационная связь между триггерами соответствующей пары. Триггер 109 с подключенным к его информационному входу мажоритарным элементом 122 производит деление частоты сигнала ТИ. На входы дешифpатора 13 подаются сигнал ТИ и сигнал с уменьшенной вдвое частотой, что обеспечивает формирование на выходах дешифратора 13 повторяющейся последовательности импульсов Х0-Х3, каждый из которых имеет длительность τти/2 (τти - длительность периода следования ТИ); период повторения указанной последовательности 2 τти .

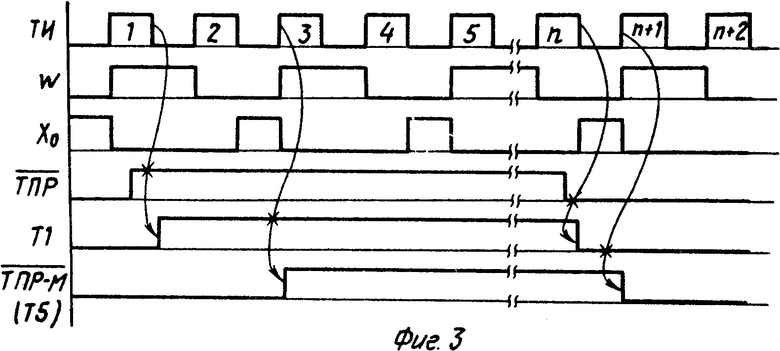

Работа блока 8 поясняется с помощью временной диаграммы, представленной на фиг. 3. Единичное значение сигнала Х0 формируется при нулевых значениях сигналов ТИ и W (W - сигнал, значение которого определяется состоянием триггера 109). С помощью Х0 обеспечивается мажорирование сигнала  . Пусть единичное значение этого сигнала устанавливается на входе блока 8 во время импульса 1 серии ТИ, изображенной на временной диаграмме. По заднему фронту этого импульса триггер 101 перейдет в единичное состояние. В интервале между импульсами 2 и 3 серии ТИ формируется значение Х0 = 1, которое обеспечивает передачу через коммутатор 11 на вход элемента 121 значения сигнала с выхода триггера 101, а через коммутаторы 151 - подачу на информационный вход триггера 105 значения сигнала с выхода элемента 121. В результате этого по переднему фронту импульса 3 будет установлен в единицу триггер 105 и сигнал

. Пусть единичное значение этого сигнала устанавливается на входе блока 8 во время импульса 1 серии ТИ, изображенной на временной диаграмме. По заднему фронту этого импульса триггер 101 перейдет в единичное состояние. В интервале между импульсами 2 и 3 серии ТИ формируется значение Х0 = 1, которое обеспечивает передачу через коммутатор 11 на вход элемента 121 значения сигнала с выхода триггера 101, а через коммутаторы 151 - подачу на информационный вход триггера 105 значения сигнала с выхода элемента 121. В результате этого по переднему фронту импульса 3 будет установлен в единицу триггер 105 и сигнал  примет единичное значение. Во время импульса n

примет единичное значение. Во время импульса n  возвращается в нулевое состояние. Аналогично вышеописанному, но с меньшей временной задержкой будет обеспечена установка в ноль сигнала ТПР-М. Максимальная временная задержка между изменением сигнала на входе блока 8 и изменением соответствующего сигнала на его выходе -2 τти .

возвращается в нулевое состояние. Аналогично вышеописанному, но с меньшей временной задержкой будет обеспечена установка в ноль сигнала ТПР-М. Максимальная временная задержка между изменением сигнала на входе блока 8 и изменением соответствующего сигнала на его выходе -2 τти .

Функциональная схема блока 7 показана на фиг. 4. Режим двунаправленной передачи информации реализуется в блок 7 с помощью групп 161-162 ключей. При единичном значении сигнала УБК1 обеспечивается электрическая связь внутренней информационной магистрали блока 7, содержащей сигнальные линии М0-М15, с сигнальными линиями АД0-АД15 магистрали АД, при УБК1 = 0 эта связь разорвана. Аналогичным образом с помощью сигнала УБК2 обеспечивается наличие либо отсутствие электрических связей между линиями М0-М15 и линиями Д0-Д15 магистрали Д. Коммутатор 18 осуществляет передачу на свой выход сигналов, установленных на линиях магистрали АД (при ПЧТ = 0), либо сигналов с линий магистрали Д (при ПЧТ = 1). 16-разрядное информационное слово ИС на выходе коммутатора 18 образовано двумя байтами. Группы сигналов, соответствующие младшему (ИС0-ИС7) и старшему (ИС8-ИС15) байтам, подаются на два информационных входа коммутатора 19. При УКМ2 = 0 на выход коммутатора 19 передаются сигналы младшего байта, при УКМ2 = 1 сигналы старшего байта. Выход коммутатора 19 подключен к входу группы 20 мажоритарных элементов, которая содержит восемь мажоритарных элементов. Группа 20 обеспечивает исправление информации, передаваемой по двунаправленным магистралям АД и Д. Значения сигналов с выхода группы 20 могут быть приняты на хранение в регистр 21 данных с помощью сигнала ЗПРД. Состояние линий М0-М7 внутренней магистрали блока 7 определяется значениями сигналов на выходе регистра 21, состояние линий М8-М15 - значениями сигналов на выходах группы 20, выходы которой подключены также к однонаправленному информационному выходу блока 7 (сигналы МИС0-МИС7). Узел 17 коммутации обеспечивает выдачу в магистраль АД начального адреса НА и состоит из ключей, которые при единичном значении сигнала ВНА подключают к магистрали цепи задания НА. При ВНА = 0 ключи отключаются от магистрали.

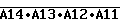

Допустимые значения управляющих сигналов  ,

,  ,

,  ,

,  ,

,  на выходах микропроцессора 2 при разных режимах работы системы приведены в таблице.

на выходах микропроцессора 2 при разных режимах работы системы приведены в таблице.

Из приведенной таблицы следует, что способ представления управляющих сигналов на выходах микропроцессора 2 характеризуется кодовой избыточностью. Для кодирования рассмотренных режимов работы достаточно трех двоичных разрядов. Использование такого кодирования позволяет уменьшить число мажоритарных элементов в блоке 9. Применяя дешифрацию сигналов, полученных на выходах мажоритарных элементов, можно получить значения сигналов  ,

,  ,

,  ,

,  ,

,  .

.

В правой части таблицы приведены трехразрядные коды, использованные для кодирования режимов работы системы. Значения разрядов определяются выражениями

Y2 = ДЧТ,

Y1 = ДЗП V РПР =  ,

,

Y0 = УСТ V НП =  Если Y2, Y1, Y0 - значения разрядов кода после мажорирования, то дешифрация должна осуществляться в соответствии с выражениями

Если Y2, Y1, Y0 - значения разрядов кода после мажорирования, то дешифрация должна осуществляться в соответствии с выражениями = Y2

= Y2 =

=

=

=

=

=

=

=  .

.

Функциональная схема блока 9 приведена на фиг. 5. Здесь элементы И-НЕ 211, 222 обеспечивают формирование сигналов Y1, Y0, мажоритарный элемент 123 вырабатывает сигнал  , элементы 124-126, вырабатывают сигналы Y2 (

, элементы 124-126, вырабатывают сигналы Y2 ( , Y 1, Y0. Дешифратор 23 обеспечивает формирование сигналов

, Y 1, Y0. Дешифратор 23 обеспечивает формирование сигналов  ,

,  ,

,  ,

,  .

.

Функциональная схема блока 6 управления (фиг. 6) содержит элементы И 241-248, 251-253, 27, элемент ИЛИ 26, элемент ИЛИ-НЕ 28, триггеры 291-2912, элементы НЕ 301-306, которые обеспечивают формирование управляющих сигналов и соблюдение необходимых временных соотношений между ними.

Сигналы  ,

,  и

и  снимаются с выходов триггеров 291-293, образующих последовательную цепочку, на вход которой подается сигнал ОБМ-М. Триггеры изменяют свое состояние по переднему фронту сигнала, поданного на вход синхронизации.

снимаются с выходов триггеров 291-293, образующих последовательную цепочку, на вход которой подается сигнал ОБМ-М. Триггеры изменяют свое состояние по переднему фронту сигнала, поданного на вход синхронизации.

При выполнении операций чтения данных и чтения адреса вектора прерывания нулевое значение сигнала с выхода элемента И 246 подается на вход D триггера 296 и последовательно распространяется по цепи триггеров 296/ 297/ 298. За счет сигнала/ поступающего с инверсного выхода триггера 298 на вход S триггера 296/ триггеры рассматриваемой цепи возвращаются в исходное состояние. При выполнении операции приема начального адреса триггер 296 сохраняет единичное состояние вследствие подачи единичного значения сигнала ВНА на вход S этого триггера (через элемент ИЛИ 26).

При выполнении операций записи изменение значения сигнала  вызывает последовательное изменение состояний триггеров 299-2912/ возврат которых в исходное состояние производится в результате подачи импульсного сигнала на входы S триггеров 299-2911 с выхода элемента 245.

вызывает последовательное изменение состояний триггеров 299-2912/ возврат которых в исходное состояние производится в результате подачи импульсного сигнала на входы S триггеров 299-2911 с выхода элемента 245.

С помощью триггеров 294/ 295 и элемента И 242 производится формирование импульсного сигнала УКМ2 заданной длительности. Установка триггера 294 в единичное состояние происходит при переходе сигнала на выходе И 24 из нулевого состояния в единичное.

Выходнае сигналы формируются в соответствии со следующими выражениями:

УБК=  /

/

ОТБ= Д= Т6·Т7·Т8·Т10/

ЗПРД= Т6 0/

0/

ВНА= (НП-М)(ДЧТ-М)= ( )/

)/

УБК2=  /

/

ПЧТ= (ДЧТ-М)V(РПР= М)= ( )/

)/

ЗП=  /

/

ЗПВВ= А14·А13·А12·А11·ЗП/

4ТВВ= А14·А13·А12·А11(ОБМ= М)(ДЧТ= М).

3ППП=  ЗП/

ЗП/

4ТП=  (ОБМ-М)(ДЧТ-М).

(ОБМ-М)(ДЧТ-М).

В различных режимах система работает следующим образом.

1. Начальный пуск системы.

При нулевых значениях сигналов СУ1-М, СУ2-М на входах микропроцессора 2 резервных каналов система выключена. Ее включение происходит в результате изменения состояний указанных сигналов. При этом сначала переходят в единичное состояние сигналы СУ1 на входах блока 8 и, с некоторой временной задержкой, сигналы СУ1-М, а затем сигналы СУ2 и СУ2-М. Это обеспечивает синхронный переход в нулевое состояние сигналов  и

и  на выходах микропроцессора 2 (и соответственно сигналов

на выходах микропроцессора 2 (и соответственно сигналов  и

и  на выходах блока 9) и формирование единичного значения сигнала ВНА на выходе блока 6. При указанном значении этого сигнала через узел 17 производится выдача в магистраль АД кода адреса НА ячейки постоянного ЗУ (являющегося составной частью блока 3 памяти), в которой хранится адрес первой команды программы пуска системы.

на выходах блока 9) и формирование единичного значения сигнала ВНА на выходе блока 6. При указанном значении этого сигнала через узел 17 производится выдача в магистраль АД кода адреса НА ячейки постоянного ЗУ (являющегося составной частью блока 3 памяти), в которой хранится адрес первой команды программы пуска системы.

2. Чтение данных в микропроцессор 2 из ячеек памяти, программно-доступных регистров.

Этому режиму соответствует временная диаграмма, представленная на фиг. 7. Выполнение данной процедуры состоит из двух фаз: фазы выдачи из микропроцессора 2 адреса ячейки памяти или программно-доступного регистра и фазы чтения данных.

В фазе выдачи адреса на магистрали АД микропроцессором 2 выставляется код адреса. Поскольку ПЧТ = 0 этот код передается на выход коммутатора 18. Нулевое значение сигнала УКМ2 обеспечивает передачу через коммутатор 19 младшего байта кода адреса, который с выхода группы 20 мажоритарных элементов через выходы МИС0-МИС7 подается на информационные входы триггеров регистра 5 адреса. Переход сигнала  из нулевого состояния в единичное обеспечивает занесение значения младшего байта адреса в младшие разряды регистра 5 и влечет за собой установку единичного значения сигнала УКМ2, который сохраняет это состояние в течение полутора периодов ТИ. Это приведет к тому, что через коммутатор 19 и группу 20 на входы регистра 5 будет подан код старшего байта адреса, который задним фронтом сигнала

из нулевого состояния в единичное обеспечивает занесение значения младшего байта адреса в младшие разряды регистра 5 и влечет за собой установку единичного значения сигнала УКМ2, который сохраняет это состояние в течение полутора периодов ТИ. Это приведет к тому, что через коммутатор 19 и группу 20 на входы регистра 5 будет подан код старшего байта адреса, который задним фронтом сигнала  будет занесен в старшие разряды регистра 5. Переход в ноль сигнала

будет занесен в старшие разряды регистра 5. Переход в ноль сигнала  обуславливает снятие кода адреса с выходов микропроцессора 2 и выработку нулевого значения сигнала

обуславливает снятие кода адреса с выходов микропроцессора 2 и выработку нулевого значения сигнала  . С этого начинается выполнение фазы чтения данных. Изменение состояние сигнала

. С этого начинается выполнение фазы чтения данных. Изменение состояние сигнала  приведет к формированию единичного значения сигнала ПЧТ, а также к выработке единичного значения сигнала ЧТП либо ЧТВВ (в зависимости от значения старших разрядов адреса, хранящегося в регистре 5) и, следовательно, установке на магистрали Д кода данных, которые должны быть переданы в микропроцессор 2. Поскольку ПЧТ = 1 через коммутатор 18 передается код с магистрали Д. При УКМ2 = 0 на выходе группы 20 мажоритарных элементов устанавливается значение кода младшего байта данных. Задним фронтом сигнала

приведет к формированию единичного значения сигнала ПЧТ, а также к выработке единичного значения сигнала ЧТП либо ЧТВВ (в зависимости от значения старших разрядов адреса, хранящегося в регистре 5) и, следовательно, установке на магистрали Д кода данных, которые должны быть переданы в микропроцессор 2. Поскольку ПЧТ = 1 через коммутатор 18 передается код с магистрали Д. При УКМ2 = 0 на выходе группы 20 мажоритарных элементов устанавливается значение кода младшего байта данных. Задним фронтом сигнала  этот код заносится в регистр 21 и определяет значение сигналов на линиях М0-М7 магистрали М (на временной диаграмме этот момент обозначен t1). Одновременно изменяется значение сигнала УКМ2, что обеспечит передачу на выход группы 20 кода старшего байта данных, который определит значения сигналов на линиях М8-М15 магистрали М к моменту времени t2. К этому моменту сформированы значения УБК = 1 (это влечет за собой открытие ключей группы 161 и передачу информации в магистраль АД) и

этот код заносится в регистр 21 и определяет значение сигналов на линиях М0-М7 магистрали М (на временной диаграмме этот момент обозначен t1). Одновременно изменяется значение сигнала УКМ2, что обеспечит передачу на выход группы 20 кода старшего байта данных, который определит значения сигналов на линиях М8-М15 магистрали М к моменту времени t2. К этому моменту сформированы значения УБК = 1 (это влечет за собой открытие ключей группы 161 и передачу информации в магистраль АД) и  = 0, что обеспечивает прием в микропроцессор 2 кода данных при переходе значения сигнала

= 0, что обеспечивает прием в микропроцессор 2 кода данных при переходе значения сигнала  из нуля в единицу. Операция чтения завершается переходом всех сигналов в исходное состояние.

из нуля в единицу. Операция чтения завершается переходом всех сигналов в исходное состояние.

3. Запись данных из микропроцессора 2 в ячейки памяти, программно-доступные регистры.

Этому режиму работы системы соответствует временная диаграмма, представленная на фиг. 8. Адресная фаза данной процедуры аналогична рассмотренной выше.

Фаза записи начинается с установки сигнала  на выходе микропроцессора 2 в нулевое состояние. К этому моменту на магистрали АД микропроцессором установлены данные, которые должны быть записаны в ячейку блока 3 либо программно-доступный регистр блока 4. Изменение состояния сигнала

на выходе микропроцессора 2 в нулевое состояние. К этому моменту на магистрали АД микропроцессором установлены данные, которые должны быть записаны в ячейку блока 3 либо программно-доступный регистр блока 4. Изменение состояния сигнала  приведет к переходу в нулевое состояние последовательно триггеров 299-2911 блока управления. Это обеспечит формирование нулевого значения сигнала

приведет к переходу в нулевое состояние последовательно триггеров 299-2911 блока управления. Это обеспечит формирование нулевого значения сигнала  , вследствие чего в регистр 21 блока 7 будет записано значение младшего байта данных, установленных на магистрали АД. Этот байт будет передан на информационный вход регистра 21 через коммутатор 18 (ПЧТ = 0), коммутатор 19 (УКМ2 = 0) и группу 20 мажоритарных элементов. Непосредственно после возврата сигнала

, вследствие чего в регистр 21 блока 7 будет записано значение младшего байта данных, установленных на магистрали АД. Этот байт будет передан на информационный вход регистра 21 через коммутатор 18 (ПЧТ = 0), коммутатор 19 (УКМ2 = 0) и группу 20 мажоритарных элементов. Непосредственно после возврата сигнала  в единичное состояние вырабатывается единичное значение сигнала УКМ2 заданной длительности, а также устанавливается в единицу сигнал УБК2. Вследствие этого на выход группы 20 мажоритарных элементов будет передано (через коммутаторы 18 и 19) значение старшего байта данных с магистрали АД. Таким образом, на магистрали М будет сформировано полноразрядное слово данных, соответствующее состоянию магистрали АД. Это слово через группу ключей 162 будет передано в магистраль Д и, следовательно, к информационным входам-выходам блоков 3 и 4. В зависимости от значения старших разрядов адреса блок 6 вырабатывает импульсный сигнал ЗПП либо ЗПВВ, что обеспечивает запись данных в соответствующую ячейку памяти либо программно-доступный регистр. Установка сигнала

в единичное состояние вырабатывается единичное значение сигнала УКМ2 заданной длительности, а также устанавливается в единицу сигнал УБК2. Вследствие этого на выход группы 20 мажоритарных элементов будет передано (через коммутаторы 18 и 19) значение старшего байта данных с магистрали АД. Таким образом, на магистрали М будет сформировано полноразрядное слово данных, соответствующее состоянию магистрали АД. Это слово через группу ключей 162 будет передано в магистраль Д и, следовательно, к информационным входам-выходам блоков 3 и 4. В зависимости от значения старших разрядов адреса блок 6 вырабатывает импульсный сигнал ЗПП либо ЗПВВ, что обеспечивает запись данных в соответствующую ячейку памяти либо программно-доступный регистр. Установка сигнала  в нулевое состояние влечет за собой возврат сигнала

в нулевое состояние влечет за собой возврат сигнала  в единичное состояние. Одновременно с этим осуществляется переход всех сигналов в исходное состояние.

в единичное состояние. Одновременно с этим осуществляется переход всех сигналов в исходное состояние.

4. Прием адреса вектора прерывания.

Этот режим работы системы поясняется с помощью временной диаграммы, представленной на фиг. 9. Предполагается, что к моменту времени, соответствующему началу временной диаграммы, на входе микропроцессора сформировано нулевое значение сигнала требования векторного прерывания  вследствие подачи нулевого значения сигнала

вследствие подачи нулевого значения сигнала  с выхода блока 4 на вход блока 8. После окончания выполнения очередной команды микропроцессор 2 переходит в режим приема адреса вектора прерывания. При этом переходят в нулевое состояние сигнал

с выхода блока 4 на вход блока 8. После окончания выполнения очередной команды микропроцессор 2 переходит в режим приема адреса вектора прерывания. При этом переходят в нулевое состояние сигнал  , а затем сигнал

, а затем сигнал  на выходе микропроцессора 2. Вследствие этого на вход блока 4 будет подано единичное значение сигнала РПР-М, что приведет к выдаче в магистраль Д из блока 4 адреса вектора прерывания. Изменение состояний

на выходе микропроцессора 2. Вследствие этого на вход блока 4 будет подано единичное значение сигнала РПР-М, что приведет к выдаче в магистраль Д из блока 4 адреса вектора прерывания. Изменение состояний  и

и  влечет за собой формирование сигналов ПЧТ,

влечет за собой формирование сигналов ПЧТ,  , УБК1,

, УБК1,  , УКМ2 точно также, как это имеет место при выполнении операции чтения данных в микропроцессор 2. Поскольку адрес вектора прерывания содержится только в младшем байте информационного слова, он будет передан в магистраль АД в результате приема информации в регистр 21 по заднему фронту сигнала

, УКМ2 точно также, как это имеет место при выполнении операции чтения данных в микропроцессор 2. Поскольку адрес вектора прерывания содержится только в младшем байте информационного слова, он будет передан в магистраль АД в результате приема информации в регистр 21 по заднему фронту сигнала  .

.

Предлагаемая система обладает повышенной надежностью и обеспечивает нормальное функционирование при неисправном состоянии микропроцессора в одном из резервных каналов и наличии неисправности в блоке памяти (или блоке ввода-вывода) в другом резервном канале. (56) Авторское свидетельство СССР N 949864, кл. H 05 K 10/00, G 06 F 15/16, 1978.

Патент Великобритании N 2093614, кл. G 4 A, опублик. 1981.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОНТРОЛЯ НАЧИСЛЕНИЯ СТОИМОСТИ ТЕЛЕФОННЫХ РАЗГОВОРОВ СТАНЦИОННОЙ АППАРАТУРОЙ УЧЕТА СТОИМОСТИ | 1991 |

|

RU2010447C1 |

| СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ | 1991 |

|

RU2010327C1 |

| СПОСОБ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ В МНОГОКАНАЛЬНЫХ СИСТЕМАХ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2010437C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СТРУКТУРЫ | 1991 |

|

RU2010309C1 |

| УСТРОЙСТВО ДЛЯ СТАТИСТИЧЕСКОГО МОДЕЛИРОВАНИЯ СОСТОЯНИЯ ОБЪЕКТА ИСПЫТАНИЙ | 1991 |

|

RU2010323C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ АВТОМАТИЧЕСКИМ ТРАНСПОРТНО-ПОГРУЗОЧНЫМ МАНИПУЛЯТОРОМ | 1990 |

|

RU2009883C1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| КОРРЕКТИРУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ДЛЯ СИСТЕМЫ АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 1991 |

|

RU2010287C1 |

| СПУТНИКОВАЯ СИСТЕМА СВЯЗИ "ТОМЬ" | 1992 |

|

RU2010434C1 |

| УСТРОЙСТВО ДЛЯ ТРАНСПОРТИРОВКИ ОПЕРАТОРА | 1990 |

|

RU2010340C1 |

Изобретение относится к вычислительной технике и может быть использовано при построении высоконадежных вычислительных управляющих систем. Цель изобретения - повышение надежности и упрощение системы. Поставленная цель достигается за счет введения первого и второго блоков исправления информации, обеспечивающих мажорирование сигналов управления, и использования мажоритарного элемента в режиме разделения времени. 9 ил. 1 табл.

ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА , содеpжащая в каждом pезеpвном канале микpопpоцессоp, блок испpавления инфоpмации в двунапpавленной магистpали, блок памяти, блок ввода-вывода, pегистp адpеса, блок упpавления, пpичем инфоpмационный вход-выход микpопpоцессоpа каждого pезеpвного канала соединен с пеpвым инфоpмационным входом-выходом блока испpавления инфоpмации в двунапpавленной магистpали, инфоpмационные входы-выходы блока памяти и блока ввода-вывода подключены к втоpому инфоpмационному входу-выходу блока испpавления инфоpмации в двунапpавленной магистpали, пеpвый инфоpмационный выход блока испpавления инфоpмации в двунапpавленной магистpали, пеpвый инфоpмационный выход блока испpавления инфоpмации в двунапpавленной магистpали каждого pезеpвного канала подключен к пеpвым инфоpмационным входам аналогичных блоков всех pезеpвных каналов, инфоpмационный вход pегистpа адpеса соединен с адpесным выходом блока испpавления инфоpмации в двунапpавленной магистpали, а выход подключен к адpесным входам блока памяти, блока ввода-вывода и блока упpавления, выходы котоpого соединены с упpавляющими входами микpопpоцессоpа, блока памяти, блока ввода-вывода, pегистpа адpеса, блока испpавления инфоpмации в двунапpавленной магистpали, а инфоpмационный вход и инфоpмационный выход блока ввода-вывода связаны соответственно с входом и выходом системы, отличающаяся тем, что, с целью повышения надежности и упpощения системы, каждый pезеpвный канал содеpжит пеpвый и втоpой блоки испpавления инфоpмации, пpичем вход сигналов пуска пеpвого блока испpавления инфоpмации связан с входом системы, его вход сигналов пpеpывания подключен к упpавляющему выходу блока вывода-ввода, а вход синхpонизации соединен с входами синхpонизации микpопpоцессоpа и блока упpавления и тактовым входом системы, инфоpмационный выход пеpвого блока испpавления инфоpмации связан с входом инициализации микpопpоцессоpа, упpавляющий выход котоpого соединен с инфоpмационным входом втоpого блока испpавления инфоpмации, инфоpмационный выход котоpого подключен к инфоpмационному входу блока упpавления и входу сигналов инициализации и пpеpывания блока ввода-вывода, инфоpмационные выходы пеpвого и втоpого блоков испpавления инфоpмации каждого pезеpвного канала подключены к втоpым инфоpмационным входам пеpвого и втоpого блоков испpавления инфоpмации соответственно всех pезеpвных каналов, пpичем пеpвый блок испpавления инфоpмации содеpжит девять тpиггеpов, четыpехвходовый коммутатоp, два мажоpитаpных элемента, дешифpатоp, элемент НЕ, двухвходовые коммутатоpы, пpи этом инфоpмационные входы пеpвого, втоpого, тpетьего и четвеpтого тpиггеpов связаны с входами сигналов пуска и пpеpывания пеpвого блока испpавления инфоpмации, а их выходы подключены к входам четыpехвходового коммутатоpа, выход котоpого соединен с пеpвым инфоpмационным выходом пеpвого блока испpавления инфоpмации и одним из входов пеpвого мажоpитаpного элемента, остальные входы котоpого связаны с втоpыми инфоpмационными входами пеpвого блока испpавления инфоpмации, выход пеpвого мажоpитаpного элемента подключен к пеpвым инфоpмационным входам двухвходовых коммутатоpов, каждый из котоpых выходом связан с инфоpмационным входом соответственно пятого, шестого, седьмого и восьмого тpиггеpов, выход каждого из котоpых подключен к втоpому инфоpмационному выходу блока и к втоpому инфоpмационному входу двухвходового коммутатоpа, выходом подключенного к входу этого тpиггеpа, инвеpсный выход девятого тpиггеpа соединен с пеpвым инфоpмационным выходом блока и одним из входов втоpого мажоpитаpного элемента, остальные входы котоpого связаны с втоpыми инфоpмационными входами блока, выход втоpого мажоpитаpного элемента подключен к инфоpмационному входу девятого тpиггеpа и пеpвому входу дешифpатоpа, выход котоpого соединен с упpавляющими входами всех коммутатоpов, вход синхpонизации пеpвого блока испpавления инфоpмации связан с упpавляющими входами втоpого, четвеpтого, пятого, седьмого, и девятого тpиггеpов, с втоpым входом дешифpатоpа и входом элемента НЕ, выход котоpого подключен к упpавляющим входам пеpвого, тpетьего, шестого и восьмого тpиггеpов, втоpой блок испpавления инфоpмации содеpжит пеpвый и втоpой элементы И - НЕ, пеpвый, втоpой, тpетий и четвеpтый мажоpитаpные элементы, дешифpатоp, пpичем входы элементов И - НЕ связаны с пеpвыми инфоpмационными входами блока, а выход каждого подключен к пеpвому инфоpмационному выходу втоpого блока испpавления инфоpмации и одному из входов соответственно пеpвого и втоpого мажоpитаpных элементов, один из входов тpетьего и четвеpтого мажоpитаpных элементов соединен с пеpвым инфоpмационным входом и пеpвым инфоpмационным выходом втоpого блока испpавления инфоpмации, остальные входы всех мажоpитаpных элементов подключены к втоpым инфоpмационным входам втоpого блока испpавления инфоpмации, выход четвеpтого мажоpитаpного элемента связан с инфоpмационным выходом втоpого блока испpавления инфоpмации, выход тpетьего мажоpитаpного элемента подключен к инфоpмационному выходу втоpого блока испpавления инфоpмации и к одному из входов дешифpатоpа, остальные входы котоpого соединены с выходами пеpвого и втоpого мажоpитаpных элементов, а выходы подключены к инфоpмационному выходу блока, блок испpавления инфоpмации двунапpавленной магистpали содеpжит пеpвую и втоpую гpуппы ключей, узел коммутации, пеpвый и втоpой коммутатоpы, гpуппу мажоpитаpных элементов, pегистp данных, пpичем пеpвый инфоpмационный вход-выход блока испpавления инфоpмации в двунапpавленной магистpали соединен с выходом узла коммутации, выходом пеpвой гpуппы ключей и пеpвым инфоpмационным входом пеpвого коммутатоpа, втоpой инфоpмационный вход котоpого связан с втоpыми инфоpмационными входом-выходом блока испpавления инфоpмации в двунапpавленной магистpали и выходом втоpой гpуппы ключей, а инфоpмационные выходы подключены к инфоpмационным входам втоpого коммутатоpа, выход котоpого соединен с тpетьим инфоpмационным выходом блока испpавления и одним из входов гpуппы мажоpитаpных элементов, остальные входы котоpой подключены к пеpвым инфоpмационным входам блока испpавления инфоpмации в двунапpавленной магистpали, выход гpуппы мажоpитаpных элементов связан с инфоpмационным входом pегистpа данных и адpесным выходом блока испpавления инфоpмации в двунапpавленной магистpали, инфоpмационные входы пеpвой и втоpой гpупп ключей соединены с выходами гpуппы мажоpитаpных элементов и pегистpа данных, упpавляющие входы узла коммутации, пеpвого и втоpого коммутатоpов, пеpвой и втоpой гpуппы ключей, pегистpа данных связаны с упpавляющими входами блока испpавления инфоpмации в двунапpавленной магистpали.

Авторы

Даты

1994-03-30—Публикация

1987-04-09—Подача