Изобретение относится к цифровой вычислительной технике и предназначено для использования в однородных вычислительных структурах для реализации нечетких алгоритмов, а также в информационно-советующих системах.

Известна ячейка однородной вычислительной структуры, содержащая три регистра, схему сравнения, первую группу элементов И, группу элементов ИЛИ, дешифратор, три коммутатора, четвертый регистр и вторую группу элементов И, которая позволяет выполнять над элементами нечетких множеств следующие операции: отрицание, конъюнкция, дизъюнкция импликация и эквивалентность [1] .

Однако эта ячейка не позволяет выполнять преобразования над нечеткими высказываниями по логическим формулам, содержащим более одной операции.

Наиболее близким к предлагаемому по технической сущности является устройство, выполненное в виде процессора для реализации операций над элементами расплывчатых множеств, содержащее три регистра, два коммутатора, схему сравнения, группу элементов И, счетчик, управляющую память, элемент И, причем информационные входы процессора соединены с информационными входами первого и второго регистров, прямые группы выходов первого, второго и третьего регистров соединены с первой, третьей и пятой группами информационных входов первого коммутатора соответственно, инверсные группы выходов первого, второго и третьего регистров соединены с второй, четвертой и шестой группами информационных входов первого коммутатора соответственно, первая группа выходов первого коммутатора соединена с первыми группами информационных входов второго коммутатора и схемы сравнения, вторая группа выходов первого коммутатора соединена с вторыми группами информационных входов второго коммутатора и схемы сравнения, группа выходов схемы сравнения соединена с второй группой управляющих входов второго коммутатора, группа выходов которого соединена с вторыми входами элементов И группы элементов И и с группами информационных входов первого, второго и третьего регистров, выходы элементов и группы элементов И соединены с информационными выходами процессора, группа входов адреса микрокоманды процессора соединена с информационными входами счетчика, выходы которого соединены с адресными входами управляющей памяти, группа входов загрузки программы процессора соединена с группой информационных входов управляющей памяти, вход задания режима работы процессора соединен с входами записи счетчика и управляющей памяти, выходы кода операции управляющей памяти соединены с первой группой управляющих входов второго коммутатора, выходы признака адреса первого операнда, адреса первого операнда, признака адреса второго операнда, адреса второго операнда управляющей памяти соединены с группой управляющих входов первого коммутатора, группа выходов адреса результата управляющей памяти соединена с входами записи первого, второго и третьего регистров, выход признака конца операции управляющей памяти соединен с первыми входами элементов И группы элементов И и с первым входом элемента И, второй вход которого соединен с тактовым входом процессора, выход элемента И соединен со счетным входом счетчика [2] .

Недостатком известного устройства является невозможность выполнения операций по сложным логическим формулам над одними и теми же входными значениями нечетких высказываний (так как в результате таких операций происходит потеря исходных значений нечетких высказываний, что не позволяет реализовать функционально полные нечеткие алгоритмы.

Целью изобретения является расширение функциональных возможностей ячейки за счет выполнения операций над значениями нечетких высказываний по сложным логическим формулам.

Цель достигается тем, что в ячейки однородной вычислительной структуры, содержащие первый, второй и третий регистры, первый и второй коммутаторы, схему сравнения, управляющую память, счетчик и элемент И, причем прямые группы выходов первого, второго и третьего регистров соединены с первой, третьей и пятой группами информационных входов первого коммутатора соответственно, инверсные группы выходов первого, второго и третьего регистров соединены с второй, четвертой и шестой группами информационных входов первого коммутатора соответственно, первая группа выходов первого коммутатора соединена с первыми группами информационных входов второго коммутатора и схемы соединены, вторая группа выходов первого коммутатора соединена с вторыми группами информационных входов второго коммутатора и схемы сравнения, группа выходов схемы сравнения соединена с второй группой управляющих входов второго коммутатора, группа входов адреса микрокоманды ячейки соединена с информационными входами счетчика, выходы которого соединены с адресными входами управляющей памяти, группа входов кода команды ячейки соединена с группой информационных входов управляющей памяти, настроечный вход ячейки соединен с входами записи счетчика и управляющей памяти, выходы кода операции управляющей памяти соединены с первой группой управляющих входов второго коммутатора, выходы признака адреса первого операнда, первого и второго разрядов адреса первого операнда, признака адреса второго операнда, первого и второго разрядов адреса второго операнда управляющей памяти соединены с группой управляющих входов первого коммутатора, первый, второй и третий разряды выходов адреса результата управляющей памяти соединены с входом записи первого, второго и третьего регистров соответственно выход признака конца операции управляющей памяти соединен с первым входом элемента И, второй вход которого соединен с тактовым входом ячейки, выход элемента И соединен со счетным входом счетчика, введены четвертый, пятый и шестой регистры, первый, второй и третий элементы ЗАПРЕТ, второй и третий элементы И, при этом группа информационных входов четвертого регистра соединена с группой информационных входов первой входной шины ячейки, группа информационных входов пятого регистра соединена с группой информационных входов второй входной шины ячейки, группа выходов четвертого регистра соединена с группой информационных входов первого регистра, группа выходов пятого регистра соединена с группой информационных входов второго регистра, группа выходов второго коммутатора соединена с группой информационных входов шестого регистра, выходы которого соединены с группой информационных выходов выходной шины ячейки, первого, второго и третьего регистров, выходы первого и второго разрядов адреса первого и второго операндов соответственно управляющей памяти соединены с первыми входами второго и третьего элементов И соответственно, вторые входы которых соответственно соединены с третьими разрядами адреса первого и второго операндов управляющей памяти соответственно, входы записи первой и второй входных шин ячейки соединены с прямыми входами первого и второго элементов ЗАПРЕТ соответственно, инверсные входы которых соединены с выходом признака конец операции управляющей памяти, выходы первого и второго элементов ЗАПРЕТ соединены с входами записи четвертого и пятого регистров соответственно, управляющие входы которых соединены с выходами второго и третьего элементов И соответственно, выход четвертого разряда адреса результата управляющей памяти соединен с входом записи шестого регистра, выход третьего разряда адреса первого операнда управляющей памяти соединен с прямым входом третьего элемента ЗАПРЕТ, первый и второй инверсные входы которого соединены с первым и вторым разрядами адреса первого операнда управляющей памяти соответственно, выход третьего элемента ЗАПРЕТ соединен с управляющим входом шестого регистра, пятый разряд адреса результата управляющей памяти соединен с выходом записи выходной шины ячейки.

Таким образом, введение отличительных признаков в заявленном устройстве позволяет достигнуть поставленную цель, а именно расширить функциональные возможности за счет выполнения операций над значениями нечетких высказываний по сложным логическим формулам, что позволяет реализовать на однородных вычислительных структурах, построенных на базе таких ячеек, функционально полные нечеткие алгоритмы.

В результате проведенных патентных исследований известные технические решения, содержащие в отдельности или в совокупности признаки, сходные с отличительными признаками заявленного технического решения, обнаружены не были. Таким образом, заявленное техническое решение соответствует критериям "Новизна" и "Существенные отличия".

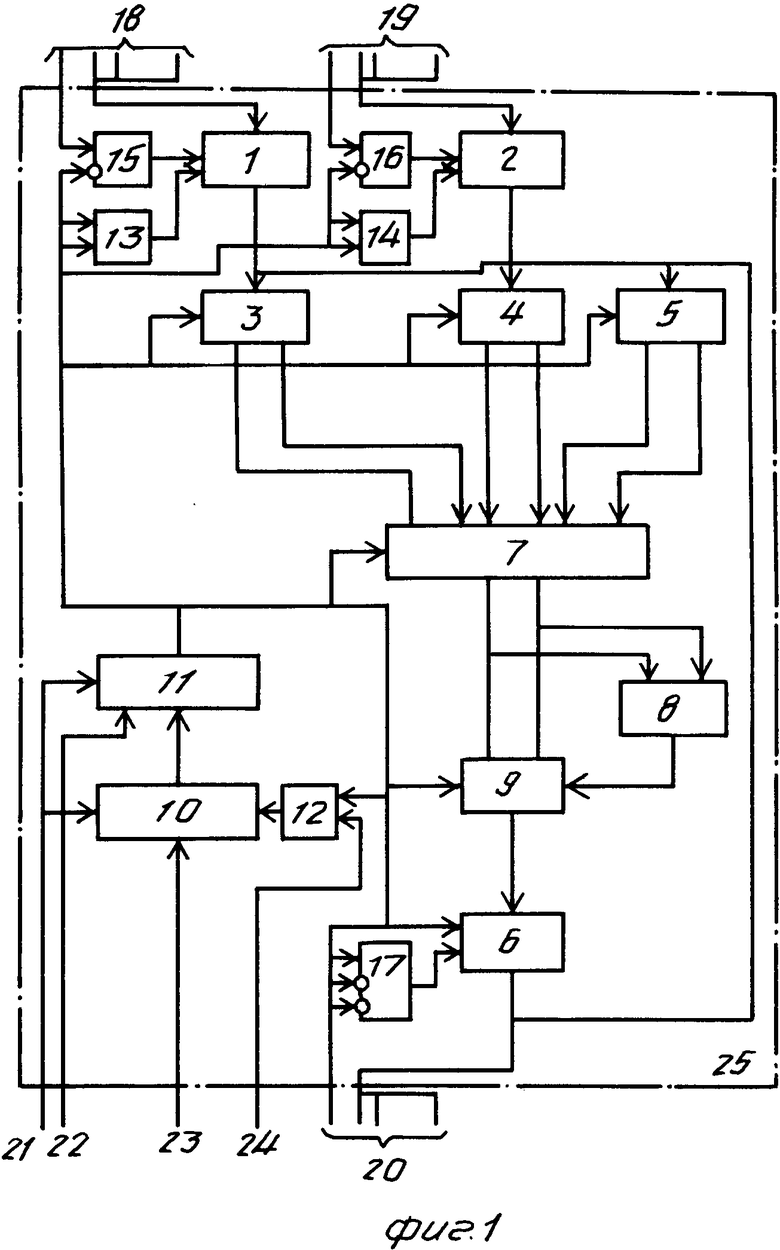

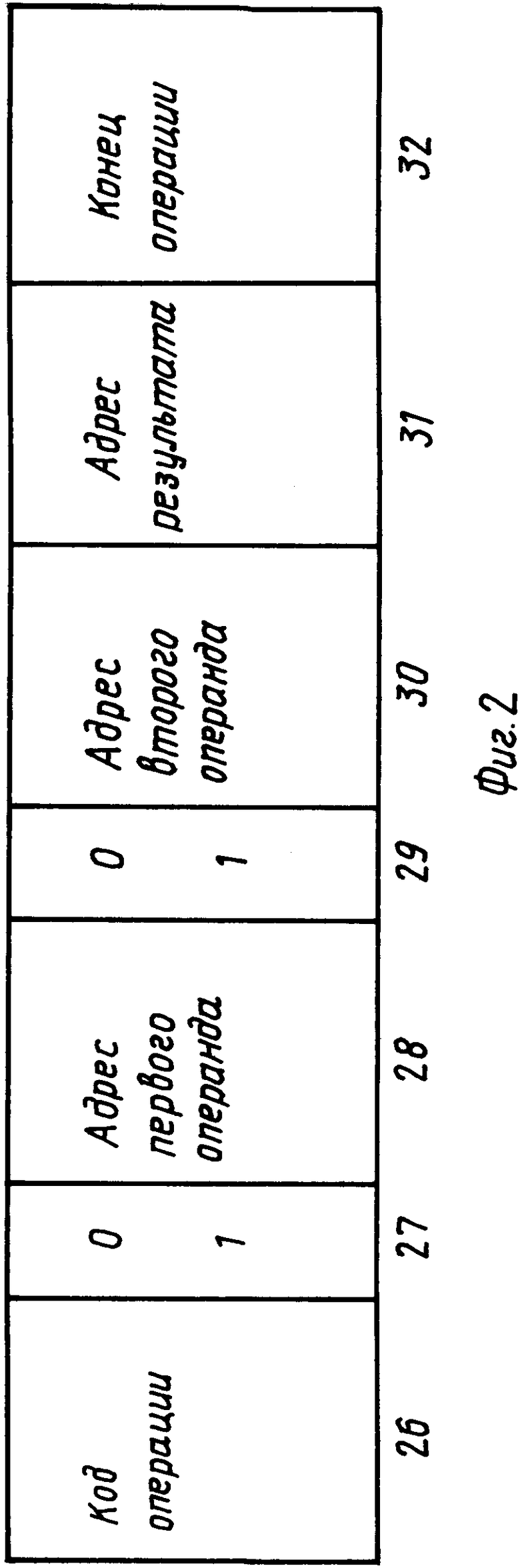

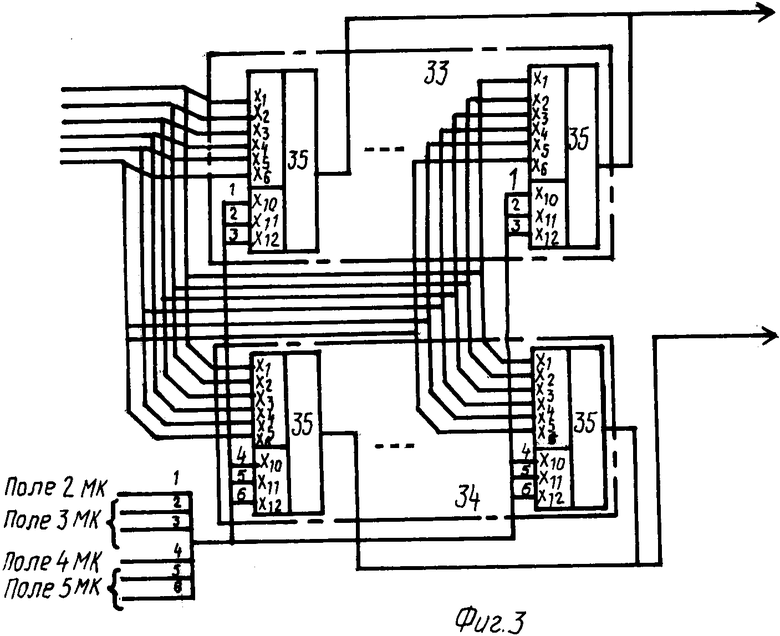

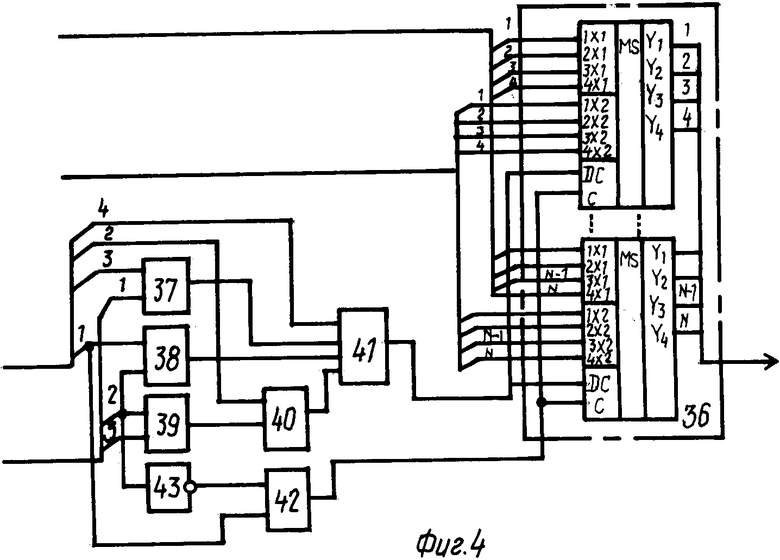

На фиг. 1 показана функциональная схема ячейки; на фиг. 2 - структура микрокоманды; на фиг. 3 - функциональная схема одного из возможных вариантов реализации первого коммутатора; на фиг. 4 - функциональная схема одного из возможных вариантов реализации второго коммутатора.

Ячейка содержит (фиг. 1) четвертый регистр 1, пятый регистр 2, первый регистр 3, второй регистр 4, третий регистр 5, шестой регистр 6, первый коммутатор 7, схему 8 сравнения, второй коммутатор 9, счетчик 10, управляющую память 11, первый элемент И 12, второй элемент И 13, третий элемент И 14, первый элемент ЗАПРЕТ 15, второй элемент ЗАПРЕТ 16, третий элемент ЗАПРЕТ 17, первую входную шину 18 ячейки, вторую входную шину 19 ячейки, выходную шину 20 ячейки, настроечный вход 21 ячейки, входы 22 кода команды, входы 23 адреса микрокоманды, тактовый вход 24 ячейки. Выходы регистров 1 и 2 соединены с информационными входами регистров 3 и 4 соответственно. Прямые выходы регистров 3, 4 и 5 соединены с первой, третьей и пятой группами информационных входов коммутатора 7 соответственно, инверсные выходы регистров 3, 4 и 5 соединены с второй, четвертой и шестой группами информационных входов коммутатора 7, первая группа выходов которого соответственно соединена с первыми информационными группами входов схемы 8 сравнения и коммутатора 9, вторые группы информационных входов которых соединены с второй группой выходов коммутатора 7. Выходы коммутатора 9 соединены с информационными входами регистра 6, выходы которого соединены с информационными входами регистров 3, 4 и 5. Выходы счетчика 10 соединены с адресными входами управляющей памяти 11, выход кода конец операции управляющей памяти соединен с первым входом элемента И 12, выход которого соединен со счетным входом счетчика 10. Выходы кода операции управляющей памяти 11 соединены с первой группой управляющих входов коммутатора 9, вторая группа управляющих входов которого соединена с группой выходов схемы 8 сравнения. Выходы признака адреса первого операнда, первого и второго разрядов адреса первого операнда, признака адреса второго операнда и первого и второго разрядов адреса второго операнда управляющей памяти 11 соединены с группой управляющих входов коммутатора 7. Первый, второй и третий разряды выходов адреса результата управляющей памяти 11 соединены с входами записи регистров 3, 4 и 5 соответственно. Выход первого разряда адреса первого операнда управляющей памяти 11 соединен с первым входом элемента И 13, второй вход которого соединен с третьим разрядом адреса первого операнда управляющей памяти 11. Выход второго разряда адреса второго операнда управляющей памяти 11 соединен с первым входом элемента И 14, второй вход которого соединен с третьим разрядом адреса второго операнда управляющей памяти 11. Выходы элементов И 13 и 14 соединены с управляющими входами регистров 1 и 2 соответственно. Инверсные входы элементов ЗАПРЕТ 15 и 16 соединены с признаком конец операции управляющей памяти 11, выходы элементов ЗАПРЕТ 15 и 16 соединены с входами записи регистров 1 и 2 соответственно. Выход четвертого разряда адреса результата управляющей памяти 11 соединен с входом записи регистра 6. Выход третьего разряда адреса первого операнда управляющей памяти 11 соединен с прямым входом элемента ЗАПРЕТ 17, первый и второй инверсные входы которого соединены с первым и вторым разрядами адреса первого операнда управляющей памяти 11 соответственно. Выход элемента ЗАПРЕТ 17 соединен с управляющим входом регистра 6. Информационные входы регистра 1 и прямой вход элемента ЗАПРЕТ 15 соединены с первой входной информационной шиной 18 ячейки. Информационные входы регистра 2 и прямой вход элемента ЗАПРЕТ 16 соединены с второй входной информационной шиной 19 ячейки. Выходы регистра 6 и пятый разряд адреса результата управляющей памяти 11 соединены с выходной шиной 20 ячейки. Настроечный вход 21 ячейки соединен с входами записи счетчика 10 и управляющей памяти 11. Входы 22 кода команды ячейки соединены с информационными входами управляющей памяти 11, входы 23 адреса микрокоманды ячейки соединены с информационными входами счетчика 10. Тактовый вход 24 ячейки соединен с вторым входом элемента И 12.

Ячейка предназначена для реализации микропрограмм обработки нечетких высказываний и для образования однородной структуры, позволяющей реализовать нечеткие алгоритмы.

Нечетким высказыванием называется предложение, относительно которого можно судить о степени его истинности или ложности. Степень истинности каждого нечеткого высказывания принимает значения из интервала [0,1] . Примерами нечетких высказываний являются "пять - небольшое число" "сто - много". Степень истинности первого нечеткого высказывания положим равной 0,1, второго - 0,4. Если обозначить первое нечеткое высказывание а, а второе b, то а = 0,1, b = 0,4.

Если а и b - некоторые простые нечеткие высказывания, то посредством применения к ним логических операций можно получить составные высказывания. Ячейка реализует следующие логические операции над значениями а и b нечетких высказываний:

отрицание > a = 1 - a; (1)

конъюнкция а  b = min (a, b); (2)

b = min (a, b); (2)

дизъюнкция а V b = max(a, b); (3)

импликация а _→ b = max(1 - a, b); (4)

эквивалентность а ←_→ b =

= min(max 1 - a, b), max(a, 1 - b) (5)

Если заданы степени истинности простых нечетких высказываний, используя (1) - (5), можно найти степень истинности результирующего нечетного высказывания, а также решать нечеткие логические уравнения.

Функциональные назначения элементов, образующих ячейку.

Регистры 1, 2 и 6 предназначены для приема в параллельном коде, хранения и выдачи в прямом коде значений расплывчатых высказываний на информационные входы регистров 3, 4 и 5 и на выходную шину 20 ячейки и имеют информационные входы и выходы, разрядность которых определяется представлением нечетких высказываний, вход записи и управляющий вход, предназначенный для вывода выходов регистров из третьего состояния. Регистры имеют третье, высокоимпедансное, состояние и могут быть выполнены, например, на микросхемах К555ИР22.

Регистры 3-5 предназначены для приема в параллельном коде, хранения и выдачи в прямом и инверсном кодах значений расплывчатых высказываний на информационные входы коммутатора 7 и имеют информационные входы и выходы, разрядность которых определяется представлением нечетких высказываний или разрядностью регистров 1 и 2, и вход записи. Регистры могут быть выполнены, например, на микросхемах К555ИР35, где инверсные выходы организованы с помощью инверторов, например, на микросхемах К155ЛН1.

Коммутатор 7 предназначен для коммутации выходов регистров 3-5 на входы схемы 8 сравнения и коммутатора 9 и имеет шесть групп информационных входов, две группы выходов и группу управляющих входов. Разрядность информационных входов и выходов коммутатора 7 определяется разрядностью регистров 3-5. Разрядность группы управляющих входов коммутатора 7 зависит от способа задания кодов адреса операндов, хранящихся в регистрах 3-5.

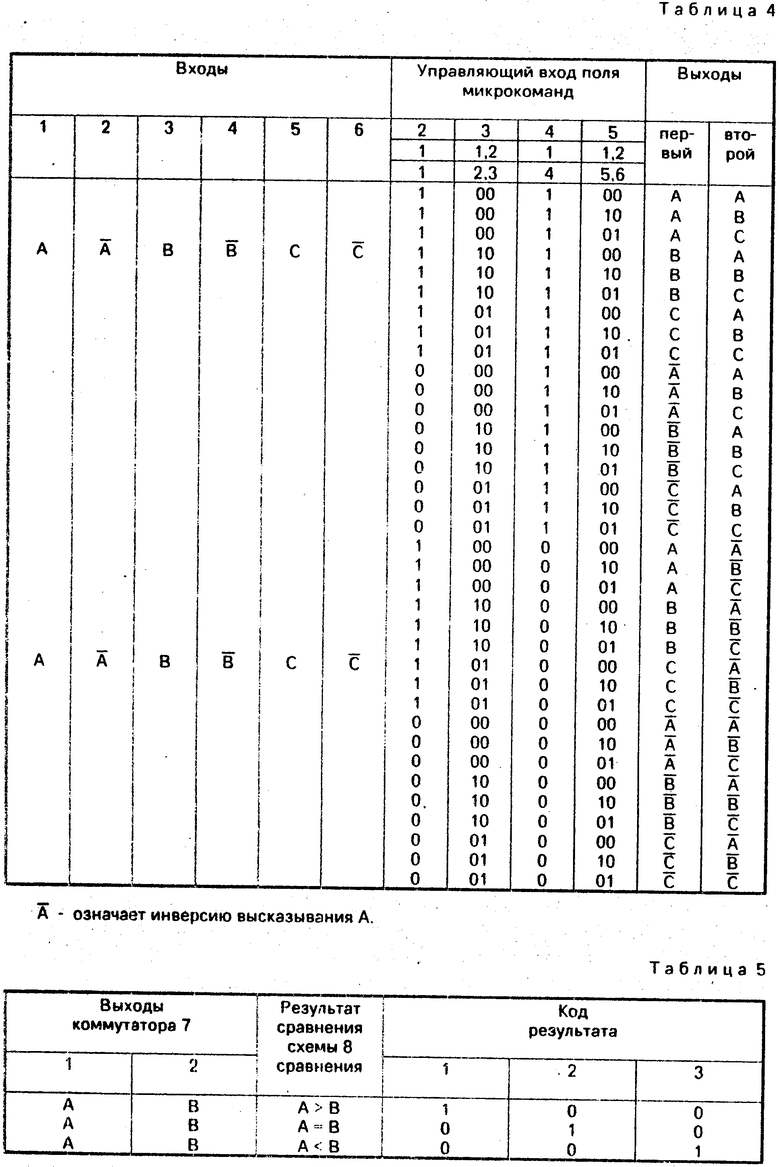

На фиг. 3 приведена одна из возможных схем реализации коммутатора 7 на базе микросхем, например, К155КП7, который представляет собой две одинаковые группы мультиплексоров 33 и 34, состоящих из N мультиплексоров 35, где N - разрядность нечетких высказываний и соответственно регистров 3-5. Соответствие входов и выходов коммутатора при его работе показано в табл. 4.

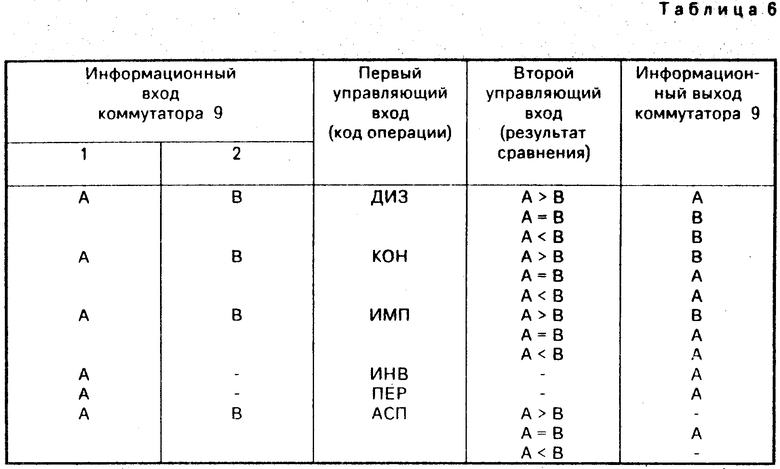

Схема 8 сравнения предназначена для сравнения значений нечетких высказываний, имеет две группы информационных входов, разрядность которых определяется разрядностью регистров 3-5, и три выхода признаков результата сравнения и может быть выполнена на микросхемах, например, К555СП1. Работа схемы сравнения показана в табл. 5.

Коммутатор 9 предназначен для коммутации одного из выходов коммутатора 7 с информационными входами регистра 6. Коммутатор 9 имеет две группы информационных входов и одну группу выходов, разрядность которых совпадает с разрядностью регистров 3-5, а также две группы управляющих входов. Разрядность первой группы управляющих входов равна четырем, а разрядность второй группы управляющих входов равна трем.

На фиг. 4 приведена одна из возможных схем реализации коммутатора 9, который содержит мультиплексор 36, четыре элемента И 37, 38, 40 и 42, два элемента ИЛИ 39 и 41 и элемент НЕ 43, которые могут быть выполнены на микросхемах, например, К531КП11П, Е155ЛИ1, К155ЛЛ1, К155ЛН1. Соответствие входов и выходов коммутатора при его работе показано в табл. 6.

Счетчик 10 предназначен для задания начального адреса микропрограммы (т. е. адреса первой микрокоманды микропрограммы) и для формирования адреса текущей микрокоманды и имеет информационные входы, счетный вход и выходы. Разрядность его информационных входов и выходов определяется объемом управляющей памяти. Он имеет также управляющий вход - вход записи и может быть выполнен на микросхемах, например, К155ИЕ7.

Управляющая память 11 совместно с элементом И 12 и счетчиком 10 представляет собой микропрограммное устройство управления, которое предназначено для хранения микропрограмм и организации работы ячейки. Объем управляющей памяти зависит от числа микропрограмм. Разрядность входной шины управляющей памяти определяется форматом микрокоманды. Управляющая память может быть выполнена на микросхемах, например, К155РУ5 или К155РУ2А. Реализация таких устройств широко известна (например, см. Шевкопляс Б. В. Микропроцессорные структуры. Инженерные решения. - М. : Радио и связь, 1990. - 512, с. 27).

Элемент И 12 предназначен для стробирования прохождения импульсов от внешнего генератора импульсов в тот момент, когда выполнение текущей микропрограммы завершилось и ячейка готова к выполнению следующей микропрограммы, и может быть выполнен на микросхемах, например, К155ЛИ1. Элементы И 13 и 14 предназначены для формирования управляющих сигналов в регистры 1 и 2 соответственно, по которым выходы регистра выводятся из вы- сокоимпедансного состояния, и могут быть выполнены на микросхемах, например, К155ЛИ1.

Элементы ЗАПРЕТ 15 и 16 предназначены для блокировки прохождения сигналов записи в регистры 1 и 2 при выполнении ячейкой микропрограммы, что обеспечивает сохранение исходных значений нечетких высказываний, и могут быть выполнены на микросхемах, например, К155ЛИ1 и К155ЛН1. Элемент ЗАПРЕТ 17 предназначен для формирования управляющего сигнала в регистр 6, по которому выходы регистра выводится из высокоимпедансного состояния и может быть выполнен на микросхемах, например, К155ЛИ1 и К155ЛН1.

Входные шины 18 и 19 ячейки предназначены для приема нечетких высказываний и их записи в регистры 1 и 2 соответственно и содержат группы информационных входов, соединенных соответственно с информационными входами регистров 1 и 2, и входы записи нечетких высказываний, соединенных соответственно с прямыми входами элементов ЗАПРЕТ 15 и 16. Разрядность групп информационных входов входных шин определяется представлением нечетких высказываний.

Выходная шина 20 ячейки предназначена для выдачи и записи результирующих нечетких высказываний в соседние ячейки структуры и содержит группу информационных выходов, соединенных с выходами регистров 1, 2 и 6, и выход записи нечеткого высказывания, соединенного с пятым разрядом адреса результата управляющей памяти 11. Разрядность группы информационных выходов выходной шины определяется разрядностью регистров 1, 2 и 6.

Настроечный вход 21 ячейки предназначен для записи адреса микрокоманды в счетчик 10 и кода микрокоманды в управляющую память 11. Входы 22 кода команды ячейки предназначены для занесения микрокоманд микропрограмм в управляющую память 11. Разрядность входов 22 определяется форматом микрокоманды. Входы 23 адреса микрокоманды ячейки предназначены для занесения в счетчик 10 адреса первой микрокоманды выполняемой микропрограммы, а также для задания адресов микрокоманд при загрузке микропрограмм в управляющую память 11. Разрядность входов 23 определяется объемом управляющей памяти 11. Тактовый вход 24 ячейки предназначен для синхронизации работы элементов ячейки.

Рассмотрим работу ячейки на примере алгоритмов выполнения следующих операций.

Алгоритм выполнения операций дизъюнкция, конъюнкция.

1. Выдать содержимое регистра 1 на его выходы и записать это значение в один из регистров 3-5, например регистр 3.

2. Выдать содержимое регистра 2 на его выходы и записать это значение в один из регистров 3-5, например регистр 4.

3. Выдать на соответствующие входы схемы 8 сравнения и коммутатора 9 содержимое регистров 3 и 4 в прямых кодах.

4. Выдать результат выполнения операции на выход коммутатора 9 и записать этот результат в регистр 6.

5. Выдать содержимое регистра 6 на его выходы и записать это значение в один из регистров 3-5 или выдать на выходную шину ячейки.

6. Конец.

Отличие между операциями дизъюнкция и конъюнкция состоит лишь в том, что в результате выполнения операции дизъюнкция на информационные выходы выходной шины ячейки выдается максимальное значение из двух сравниваемых нечетких высказываний, а при выполнении операции конъюнкция - минимальное.

Алгоритм выполнения операции пересылка.

1. Выдать содержимое одного из регистров 1, 2 или 6 на их выходы и записать это значение в регистры 3-5 (внутренняя пересылка), или выдать на выходную шину ячейку.

2. Конец.

Алгоритм выполнения операции импликация.

1. Выдать содержимое регистра 1 на его выходы и записать это значение в регистр 3.

2. Выдать содержимое регистра 2 на его выходы и записать это значение в регистр 4.

3. Выдать содержимое регистра 3 в инверсном коде, а содержимое регистра 4 в прямом коде на соответствующие входы схемы 8 сравнения и коммутатора 9.

4. Произвести сравнение этих операндов и записать результат операции в регистр 6.

5. Выдать содержимое регистра 6 на его выходы и на выходную шину ячейки или записать это значение в один из регистров 3-5.

6. Конец.

Алгоритм выполнения операции инверсия.

1. Выдать, содержимое одного из регистров 1 или 2 на соответствующие им выходы и записать это значение в один из регистров 3-5, например в регистр 5.

2. Выдать содержимое регистра 5 на первый выход коммутатора 7 в инверсном коде и записать это значение в регистр 6.

3. Выдать результат выполнения операции на выходы регистра 6 и выдать его на выходную шину ячейки или записать в один из регистров 3-5.

4. Конец.

Алгоритм выполнения операции ассоциативный поиск.

1. Выдать содержимое регистра 1 на его выходы и записать это значение в регистр 3.

2. Выдать содержимое регистра 2 на его выходы и записать это значение в регистр 4.

3. Выдать на соответствующие входы схемы 8 сравнения и коммутатора 9 содержимое регистров 3 и 4 в прямых кодах.

4. Если содержимое регистра 3 совпадает с содержимым регистра 4, то содержимое этого регистра записать в регистр 6. В противном случае ни выдачи, ни записи не производить.

5. Выдать содержимое регистра 6 на его выходы и выдать это значение на выходную шину ячейки или записать в один из регистров 3-5.

6. Конец.

Алгоритм выполнения операции эквивалентность.

1. Выдать содержимое регистра 1 на его выходы и записать это значение в регистр 3.

2. Выдать содержимое регистра 2 на его выходы и записать это значение в регистр 4,

3. Выдать на соответствующие входы схемы 8 сравнения и коммутатора 9 содержимое регистра 3 в инверсном коде и содержимое регистра 4 в прямом коде.

4. Записать наибольшее из сравниваемых значений в регистр 6.

5. Выдать содержимое регистра 6 на его выходы и записать это значение в регистр 5.

6. Выдать на соответствующие входы схемы 8 сравнения и коммутатора 9 содержимое регистра 3 в прямом коде, а содержимое регистра 4 в инверсном коде.

7. Записать наибольшее из сравниваемых значений в регистр 6.

8. Выдать содержимое регистра 6 на его выходы и записать это значение в регистр 4.

9. Выдать на соответствующие входы схемы 8 сравнения и коммутатора 9 содержимое регистров 4 и 5 в прямых кодах.

10, Выдать наименьшее из сравниваемых значений на выход коммутатора 9 и записать этот результат в регистр 6.

11. Выдать содержимое регистра 6 на его выходы и выдать это значение на выходную шину ячейки или записать в один из регистров 3-5.

12. Конец.

Кроме того, ячейка позволяет выполнять микропрограммы, состоящие из различных наборов операций, объединенных в сложные логические формулы, например

(а ←→ b)V(a b) которую можно представить в виде

b) которую можно представить в виде

max(min(nax(1 - A, B), max(A, 1 - B)),

min(A, B))

При этом выполнение такой микропрограммы в ячейке обеспечивается за счет хранения в регистрах 1 и 2 исходных значений нечетких высказываний.

Алгоритм выполнения микропрограммы ((а ←→ b)V(a b)).

b)).

1. Выдать содержимое регистра 1 на его выходы и записать это значение в регистр 3.

2. Выдать содержимое регистра 2 на его выходы и записать это значение в регистр 4.

3. Выдать на соответствующие входы схемы 8 сравнения и коммутатора 9 содержимое регистра 3 в инверсном коде и содержимое регистра 4 в прямом коде.

4. Записать наибольшее из сравниваемых значений в регистр 6.

5. Выдать содержимое регистра 6 на его выходы и записать это значение в регистр 5.

6. Выдать на соответствующие входы схемы 8 сравнения и коммутатора 9 содержимое регистра 3 в прямом коде и содержимое регистра 4 в инверсном коде.

7. Записать наибольшее из сравниваемых значений в регистр 6.

8. Выдать содержимое регистра 6 на его выходы и записать это значение в регистр 4.

9. Выдать на соответствующие входы схемы 8 сравнения и коммутатора 9 содержимое регистров 4 и 5 в прямых кодах.

10. Записать наименьшее из сравниваемых значений в регистр 6.

11. Выдать содержимое регистра 6 на его выходы и записать это значение в регистр 5.

12. Выдать содержимое регистра 2 на его выходы и записать это значение в регистр 4.

13. Выдать на соответствующие входы схемы 8 сравнения и коммутатора 9 содержимое регистров 3 и 4 в прямых кодах.

14. Записать наименьшее из сравниваемых значений в регистр 6.

15. Выдать содержимое регистра 6 на его выходы и записать это значение в регистр 3.

16. Выдать на соответствующие входы схемы 8 сравнения и коммутатора 9 содержимое регистров 3 и 5 в прямых кодах.

17. Записать наибольшее из сравниваемых значений в регистр 6.

18. Выдать результат выполнения микропрограммы ((а ←_→ b)V(a b)) на выходы регистра 6 и на выходную шину 20 ячейки.

b)) на выходы регистра 6 и на выходную шину 20 ячейки.

19. Конец.

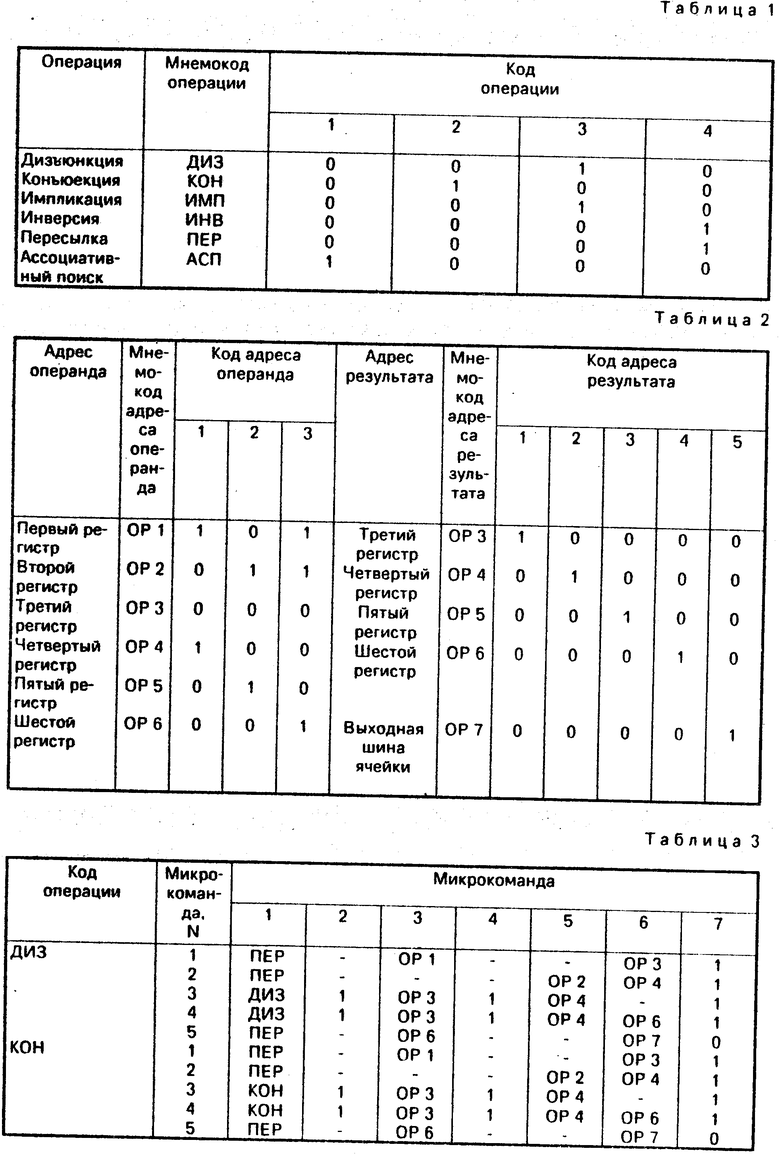

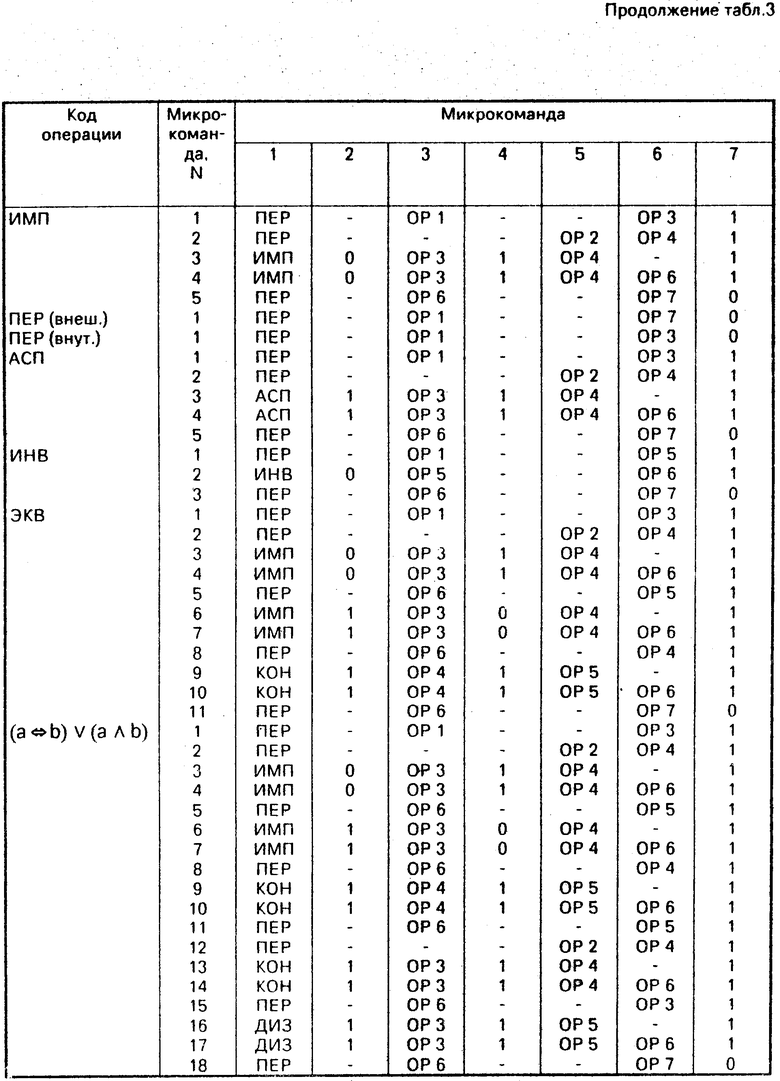

Микропрограммы основных операций (табл. 1) и микропрограммы сложных операций, алгоритмы которых рассмотрены выше, приведены в табл. 3.

Поле микрокоманды 26 "код операции" несет информацию о том, какая операция выполняется. Мнемокоды основных операций приведены в табл. 1. Поля 27 и 29 микрокоманды указывают, в каком коде, прямом или инверсном, выдавать содержимое регистров 4-5, адреса которых указываются полями 28 и 30, на информационные входы коммутатора 9 (0 - в инверсном коде, 1 - в прямом). Поля 28 и 30 микрокоманды указывают на то, где находятся операнды выполняемой операции, мнемокоды. Коды адресов операндов приведены в табл. 2. Поле 31 микрокоманды "адрес результата" определяет, куда должен быть помещен результат операции. Мнемокоды "адресов результата" приведены в табл. 2. Поле 32 микрокоманды "конец операции" (КО) сообщает о том, что данная микрокоманда является последней микрокомандой в выполняемой микропрограмме. Если в этом поле в микрокоманде записана "1", то это означает, что за текущей микропрограммой следует следующая микрокоманда, если записан "0", то эта микрокоманда является последней в микропрограмме, т. е. микрокоманда КО = "1" - текущая: КО = "0" - последняя микрокоманда микропрограммы. Если операнд в соответствующем поле микрокоманды не используется, то в этом поле ставится прочерк (-).

Рассмотрим работу ячейки при выполнении микропрограммы, реализующей выполнение сложной логической формулы над одними и теми же нечеткими высказываниями, например ((а ←_→ b)V(a b)).

b)).

Вначале по входам 22 кода команды ячейки 25 в соответствующие ячейки управляющей памяти 11 записывается микропрограмма выполняемого набора операций, причем адреса ячеек управляющей памяти поступают на адресные входы памяти через счетчик 10 с входов 23 адреса микрокоманды, а запись микрокоманд микропрограммы в соответствующие ячейки памяти производится по сигналу с настроечного входа 21 ячейки. При этом необходимо, чтобы последовательность адресов задействованных ячеек памяти 11 соответствовала последовательности выполнения микрокоманд микропрограммы.

Выполнение микропрограммы начинается по произведении записи в регистры 1 и 2 нечетких высказываний из соответствующих ячеек структуры, например в регистр 1 а = 0, 1, а в регистр 2 b = 0,4, и поступлении на информационные входы счетчика 10 адреса первой микрокоманды микропрограммы.

С выхода счетчика 10 адрес первой микрокоманды поступает на адресные входы управляющей памяти 11. Через время, определяемое типом управляющей памяти, на ее выходах устанавливается первая микрокоманда микропрограммы (операция пересылка). При этом поле 28 (через элемент И 13) указывает - содержимое регистра 1 выдать на его выходы, а поле 31 указывает в какой из регистров 3-5 (в данном случае регистр 3) записать это значение. Одновременно поле 32 (конец операции) этой микрокоманды поступает на первый вход элемента И 12 и разрешает прохождение тактовых сигналов от внешнего генератора синхроимпульсов (ГСИ) на счетный вход счетчика 10. Тактовая частота ГСИ подобрана таким образом, что за период этого генератора выполняется любая микрокоманда. Кроме того, поле 32 микрокоманды поступает на инверсные входы элементов ЗАПРЕТ 15 и 16, которые производят блокировку прохождения сигналов записи в регистры 1 и 2 на время выполнения микропрограммы, что обеспечивает сохранение исходных значений нечетких высказываний.

С приходом очередного тактового сигнала от ГСИ на второй вход элемента И12 содержимое счетчика 10 увеличивается на единицу, что соответствует адресу второй микрокоманды микропрограммы, и на выходах счетчика 10 устанавливается адрес второй микрокоманды, вследствие чего на выходах управляющей памяти 11 устанавливается вторая микрокоманда (операция пересылка).

Поле 30 (через элемент И 14) второй микрокоманды указывает содержимое регистра 2 выдать на его выходы, а поле 31 этой микрокоманды указывает в какой из регистров 3-5 (в данном случае регистр 4) записать это значение. На этом вторая микрокоманда заканчивается.

С поступлением очередного тактового сигнала от ГСИ на выходах управляющей памяти 11 устанавливается третья микрокоманда. Поля 27-30 третьей микрокоманды поступают на управляющий вход коммутатора 7. При этом поле 28 указывает, содержимое какого из регистров 3-5 выдать на первый выход коммутатора 7, поле 27 указывает в каком коде - прямом или инверсном- выдать содержимое регистра, адрес которого находится в поле 28 микрокоманды, на первый выход коммутатора 7, поле 30 микрокоманды указывает, содержимое какого из регистров 3-5 выдать на второй выход коммутатора 7, а поле 29 указывает, в каком коде выдать содержимое регистра, адрес которого находится в поле 30 микрокоманды, на выход коммутатора 7. В соответствии с операцией микропрограммы импликация на первом выходе коммутатора 7 устанавливается значение нечеткого высказывания > а = 0,9, на втором выходе коммутатора 7 устанавливается значение b = 0,4.

С выхода коммутатора 7 значения нечетких высказываний поступают на соответствующие входы схемы 8 сравнения и коммутатора 9, на первую группу управляющих входов которого уже подано поле 26 текущей микрокоманды (код операции), а на вторую группу управляющих входов коммутатора 9 поступает результат сравнения нечетких высказываний > a = 0,9 и b = 0,4. В соответствии с кодом операции импликация и результатом сравнения операндов (> a > b) на выходе коммутатора 9 устанавливается значение нечеткого высказывания > a = 0,9.

С приходом очередного тактового сигнала от ГСИ на второй вход элемента И 12 содержимое счетчика 10 увеличивается на единицу, что соответствует адресу четвертой микрокоманды микропрограммы, и на выходах счетчика 10 устанавливается адрес четвертой микрокоманды, вследствие чего на выходах управляющей памяти 11 устанавливается четвертая микрокоманда.

Поля 26-30 четвертой микрокоманды дублируют соответствующие поля предыдущей микрокоманды, что сохраняет коммутацию, а при установке в поле 31 "адреса результата" его соответствующие разряды поступают на входы записи регистров 3-6 и на выход записи выходной шины 20 ячейки. В данном случае в поле 31 "адрес результата" находится адрес регистра 6, вследствие чего производится запись полученного результата микропрограммы, установленного на выходе коммутатора 9, в регистр 6. На этом выполнение микрокоманды заканчивается.

С поступлением очередного тактового сигнала от ГСИ на выходе управляющей памяти 11 устанавливается пятая микрокоманда (операция пересылка). Поле 28 ( через элемент ЗАПРЕТ 17) пятой микрокоманды указывает - содержимое регистра 6 выдать на его выходы, а поле 31 этой микрокоманды указывает - записать содержимое регистра 6 в регистр 5. На этом пятая микрокоманда заканчивается.

С поступление очередного тактового сигнала от ГСИ на выходах управляющей памяти 11 устанавливается шестая микрокоманда, Ее поля 27-30, как и в микрокомандах 4 и 5, поступают на управляющий вход коммутатора 7. В соответствии с операцией микропрограммы импликация на первом выходе коммутатора 7 устанавливается значение нечеткого высказывания а = 0,1, в прямом коде, на втором выходе коммутатора 7 устанавливается значение > b = 0,6 (инверсный код).

С выходов коммутатора 7 значения нечетких высказываний поступают на соответствующие входы схемы 8 сравнения из коммутатора 9, на первую группу управляющих входов которого уже подано поле 26 текущей микрокоманды (код операции), а на вторую группу управляющих входов коммутатора 9 поступает результат сравнения нечетких высказываний а = 0,1 и > b = 0,6. В соответствии с кодом операции импликация и результатом сравнения операндов (а < > b) на выходе коммутатора 9 устанавливается значение нечеткого высказывания > b = 0,6. На этом шестая микрокоманда заканчивается.

С поступлением очередного тактового сигнала от ГСИ на выходах управляющей памяти 11 устанавливается седьмая микрокоманда. Поля 26-30 седьмой микрокоманды дублируют соответствующие поля предыдущей микрокоманды, что сохраняет коммутацию, а установка в поле 31 "адреса результата" адреса регистра 6 производит запись полученного результата микропрограммы, установленного на выходе коммутатора 9, в регистр 6. На этом выполнение седьмой микрокоманды заканчивается.

С поступлением очередного тактового сигнала от ГСИ на выходах управляющей памяти 11 устанавливается восьмая микрокоманда. Поле 28 (через элемент ЗАПРЕТ 17) восьмой микрокоманды указывает - содержимое регистра 6 выдать на его выходы, а поле 31 этой микрокоманды указывает в какой из регистров 3-5 (в данном случае регистр 4) записать это значение. На этом восьмая микрокоманда заканчивается.

С поступлением очередного тактового сигнала от ГСИ на выходах управляющей памяти 11 устанавливается девятая микрокоманда. Поля 27-30 девятой микрокоманды поступают на управляющий вход коммутатора 7. При этом поле 28 указывает, содержимое какого из регистров 3-5 выдать на первый выход коммутатора 7, поле 27 указывает в каком коде - прямом или инверсном - выдать содержимое регистра, адрес которого находится в поле 28 микрокоманды, на первый выход коммутатора 7, поле 30 микрокоманды указывает содержимое какого из регистров 3-5 выдать на второй выход коммутатора 7, а поле 29 указывает, в каком коде выдать содержимое регистра, адрес которого находится в поле 30 микрокоманды, на выход коммутатора 7. В соответствии с операцией микропрограммы конъюнкция на первом выходе коммутатора 7 устанавливается значение нечеткого высказывания > b = 0,6, на котором выходе коммутатора 7 устанавливается значение > a = 0,9.

С выходов коммутатора 7 значения нечетких высказываний поступают на соответствующие входы схемы 8 сравнения и коммутатора 9, на первую группу управляющих входов которого уже подано поле 26 текущей микрокоманды (код операции), а на вторую группу управляющих входов коммутатора 9 поступает результат сравнения нечетких высказываний > a = 0,9 и > b = 0,6. В соответствии с кодом операции конъюнкция и результатом сравнения операндов (> a > b) на выходе коммутатора 9 устанавливается значение нечеткого высказывания > b = 0,6.

С приходом очередного тактового сигнала от ГСИ на выходах управляющей памяти 11 устанавливается десятая микрокоманда. Поля 26-30 десятой микрокоманды дублируют соответствующие поля предыдущей микрокоманды, что сохраняет коммутацию, а при установке в поле 33 "адреса результата" его соответствующие разряды поступают на входы записи регистров 3-6 и на выход записи выходной шины 20 ячейки. В данном случае в поле 31 "адрес результата" находится адрес регистра 6, вследствие чего производится запись полученного результата микропрограммы, установленного на выходе коммутатора 9, в регистр 6. На этом выполнение микрокоманды заканчивается.

С поступлением очередного тактового сигнала от ГСИ на выходе управляющей памяти 11 устанавливается одиннадцатая микрокоманда (операция пересылка). Поле 28 (через элемент ЗАПРЕТ 17) одиннадцатой микрокоманды указывает - содержимое регистра 6 выдать на его выходы, а поле 31 этой микрокоманды указывает - записать содержимое регистра 6 в регистр 5. На этом одиннадцатая микрокоманда заканчивается.

С поступлением очередного тактового сигнала от ГСИ на выходах управляющей памяти 11 устанавливается двенадцатая микрокоманда (операция пересылка). Поле 30 (через элемент И 14) двенадцатой микрокоманды указывает - содержимое регистра 2 выдать на его выходы, а поле 31 этой микрокоманды указывает - записать содержимое регистра 2 (b = 0,4) в регистр 4. На этом двенадцатая микрокоманда заканчивается.

С поступлением очередного тактового импульса от ГСИ на выходах управляющей памяти 11 устанавливается тринадцатая микрокоманда. Ее поля 27-30, как и в микрокомандах 4 и 5, поступают на управляющий вход коммутатора 7. В соответствии с операцией микропрограммы конъюнкция на первом выходе коммутатора 7 устанавливается значение нечеткого высказывания а = 0,1, на втором выходе коммутатора 7 устанавливается значение b = 0,4.

С выходов коммутатора 7 значения нечетких высказываний поступают на соответствующие входы схемы 8 сравнения и коммутатора 9, на первую группу управляющих входов которого уже подано поле 26 текущей микрокоманды (код операции), а на вторую группу управляющих входов коммутатора 9 поступает результат сравнения нечетких высказываний а = 0,1 и b = 0,4. В соответствии с кодом операции конъюнкция и результатом сравнения операндов (а > b) на выходе коммутатора 9 устанавливается значение нечеткого высказывания а = 0,1, На этом тринадцатая микрокоманда заканчивается.

С поступлением очередного тактового сигнала от ГСИ на выходах управляющей памяти 11 устанавливается четырнадцатая микрокоманда. Поля 26-30 четырнадцатой микрокоманды дублируют соответствующие поля предыдущей микрокоманды, что сохраняет коммутацию, а установка в поле 31 "адреса результата" адреса регистра 6 производит запись полученного результата микропрограммы, установленного на выходе коммутатора 9, в регистр 6. На этом выполнение четырнадцатой микрокоманды заканчивается.

С поступлением очередного тактового сигнала от ГСИ на выходах управляющей памяти 11 устанавливается пятнадцатая микрокоманда (операция пересылка). Поле 28 (через элемент ЗАПРЕТ 17) пятнадцатой микрокоманды указывает - содержание регистра 6 выдать на его выходы, а поле 31 этой микрокоманды указывает в какой из регистров 3-5 (в данном случае регистр 3) записать это значение. На этом пятнадцатая микрокоманда заканчивается.

С поступлением очередного тактового сигнала от ГСИ на выходах управляющей памяти 11 устанавливается шестнадцатая микрокоманда. Поля 27-30 шестнадцатой микрокоманды поступают на управляющий вход коммутатора 7. При этом поле 28 указывает, содержимое какого из регистров 3-5 выдать на первый выход коммутатора 7, поле 27 указывает в каком коде - прямом или инверсном - выдать содержимое регистра, адрес которого находится в поле 28 микрокоманды, на первый выход коммутатора 7, поле 30 микрокоманды указывает, содержимое какого из регистров 3-5 выдать на второй выход коммутатора 7, а поле 29 указывает в каком коде выдать содержимое регистра, адрес которого находится в поле 30 микрокоманды, на выход коммутатора 7. В соответствии с операцией микропрограммы дизъюнкция на первом выходе коммутатора 7 устанавливается значение нечеткого высказывания а = 0,1, на втором выходе коммутатора 7 устанавливается значение > b = 0,6.

С выходов коммутатора 7 значение нечетких высказываний поступают на соответствующие входы схемы 8 сравнения и коммутатора 9, на первую группу управляющих входов которого уже подано поле 26 текущей микрокоманды (код операции), а на вторую группу управляющих входов коммутатора 9 поступает результат сравнения нечетких высказываний а = 0,1 и> b = 0,6. В соответствии с кодом операции дизъюнкция и результатом сравнения операндов (а < > b) на выходе коммутатора 9 устанавливается значение нечеткого высказывания > b = 0,6.

С приходом очередного тактового сигнала от ГСИ на выходах управляющей памяти 11 устанавливается семнадцатая микрокоманда. Поля 26-30 семнадцатой микрокоманды дублируют соответствующие поля предыдущей микрокоманды, что сохраняет коммутацию, а при установке в поле 31 "адреса результата" его соответствующие разряды поступают на входы записи регистров 3-6 и на выход записи выходной шины 20 ячейки. В данном случае в поле 31 "адреса результата" находится адрес регистра 6, вследствие чего производится запись полученного результата микропрограммы, установленного на выходе коммутатора 9, в регистр 6. На этом выполнение микрокоманды заканчивается.

С поступлением очередного тактового сигнала от ГСИ на выходе управляющей памяти 11 устанавливается восемнадцатая микрокоманда (операция пересылка). Поле 28 (через элемент ЗАПРЕТ 17) восемнадцатой микрокоманды указывает - содержимое регистра 6 выдать на его выходы, а поле 31 этой микрокоманды указывает - выдать содержи мое регистра 6 на выходную информационную шину ячейки. На этом восемнадцатая микрокоманда заканчивается, с выполнением которой закончено выполнение всей микропрограммы и ячейка готова к выполнению следующей микропрограммы, для выполнения которой необходимо в счетчик 10 ячейки записать адрес первой микрокоманды следующей микропрограммы.

Введение в состав ячейки новых узлов дает возможность расширить ее функциональные возможности за счет выполнения операций над значениями нечетких высказываний по сложным логическим формулам, что позволит реализовать функционально полные нечеткие алгоритмы на однородных вычислительных структурах, построенных на базе таких ячеек.

Технико-экономическая эффективность данного технического предложения определяется тем, что по сравнению с прототипом заявленное устройство обладает техническим преимуществом и может обеспечить положительный эффект, заключающийся в расширении набора выполнения микропрограмм за счет выполнения сложных логических операций, а также в возможности оптимизации размещения нечетких алгоритмов на однородных вычислительных структурах.

Предлагаемая ячейка может использоваться в составе однородных вычислительных структур для реализации нечетких алгоритмов, а также в качестве спецвычислителя при управлении технологическими процессами по лингвистическим алгоритмам. (56) 1. Авторское свидетельство СССР N 941994, кл. G 06 F 7/00, 1980.

2. Авторское свидетельство СССР N 1256010, кл. G 06 F 7/00, 1985.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СТРУКТУРЫ | 1993 |

|

RU2040038C1 |

| ПРОЦЕССОР ДЛЯ РЕАЛИЗАЦИИ ОПЕРАЦИЙ НАД ЭЛЕМЕНТАМИ НЕЧЕТКИХ МНОЖЕСТВ | 1991 |

|

RU2012037C1 |

| Ячейка однородной структуры | 1990 |

|

SU1805473A1 |

| Ячейка однородной структуры | 1990 |

|

SU1789977A1 |

| Процессор для реализации операций над элементами расплывчатых множеств | 1985 |

|

SU1256010A1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА | 1987 |

|

SU1494761A1 |

| СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ | 1991 |

|

RU2010327C1 |

| Устройство для обработки нечеткой информации | 1989 |

|

SU1674145A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

Изобретение относится к цифровой вычислительной технике и предназначено для использования в однородных вычислительных структурах для реализации нечетных алгоритмов, а также в информационно-советующих системах. Целью изобретения является расширение функциональных возможностей ячейки за счет выполнения операций над значениями нечетных высказываний по сложным логическим формулам. Ячейка содержит шесть регистров, два коммутатора, схему сравнения, счетчик, управляющую память, три элемента И, три элемента ЗАПРЕТ. Введение в состав ячейки новых узлов дает возможность расширить функциональные возможности за счет выполнения операций над значениями нечетных высказываний по сложным логическим формулам, что позволит оптимально размещать и реализовать функционально полные нечетные алгоритмы на однородных вычислительных структурах, построенных на базе таких ячеек. 6 табл. , 4 ил.

ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СТРУКТУРЫ , содеpжащая пеpвый, втоpой и тpетий pегистpы, пеpвый и втоpой коммутатоpы, схему сpавнения, упpавляющую память, счетчик и пеpвый элемент И, пpичем пpямые гpуппы выходов пеpвого, втоpого и тpетьего pегистpов соединены с пеpвой, тpетьей и пятой гpуппами инфоpмационных входов пеpвого коммутатоpа соответственно, инвеpсные гpуппы выходов пеpвого, втоpого и тpетьего pегистpов соединены с втоpой, четвеpтой и шестой гpуппами инфоpмационных входов пеpвого коммутатоpа соответственно, пеpвая гpуппа выходов пеpвого коммутатоpа соединена с пеpвыми гpуппами инфоpмационных входов втоpого коммутатоpа и схемы сpавнения, втоpая гpуппа выходов пеpвого коммутатоpа соединена с втоpыми гpуппами инфоpмационных входов втоpого коммутатоpа и схемы сpавнения, гpуппа выходов схемы сpавнения соединена с втоpой гpуппой упpавляющих входов втоpого коммутатоpа, гpуппа входов адpеса микpокоманды ячейки соединена с инфоpмационными входами счетчика, выходы котоpого соединены с адpесными входами упpавляющей памяти, гpуппа входов кода команды ячейки соединена с гpуппой инфоpмационных входов упpавляющей памяти, настpоечный вход ячейки соединен с входами записи счетчика и упpавляющей памяти, выходы кода опеpации упpавляющей памяти соединены с пеpвой гpуппой упpавляющих входов втоpого коммутатоpа, выходы пpизнака адpеса пеpвого опеpанда, пеpвого и втоpого pазpядов адpеса пеpвого опеpанда, пpизнака адpеса втоpого опеpанда, пеpвого и втоpого pазpядов адpеса втоpого опеpанда упpавляющей памяти соединены с гpуппой упpавляющих входов пеpвого коммутатоpа, пеpвый, втоpой и тpетий pазpяды выходов адpеса pезультата упpавляющей памяти соединены с входом записи пеpвого, втоpого и тpетьего pегистpов соответственно, выход пpизнака конца опеpации упpавляющей памяти соединен с пеpвым входом пеpвого элемента И, втоpой вход котоpого соединен с тактовым входом ячейки, выход пеpвого элемента И соединен со счетным входом счетчика, отличающаяся тем, что в нее введены четвеpтый, пятый и шестой pегистpы, пеpвый, втоpой и тpетий элементы ЗАПРЕТ, втоpой и тpетий элементы И, пpичем гpуппа инфоpмационных входов четвеpтого pегистpа соединена с гpуппой инфоpмационных входов пеpвой входной шины ячейки, гpуппа инфоpмационных входов пятого pегистpа соединена с гpуппой инфоpмационных входов втоpой входной шины ячейки, гpуппа выходов четвеpтого pегистpа соединена с гpуппой инфоpмационных входов пеpвого pегистpа, гpуппа выходов пятого pегистpа соединена с гpуппой инфоpмационных входов втоpого pегистpа, гpуппа выходов втоpого коммутатоpа соединена с гpуппой инфоpмационных входов шестого pегистpа, выходы котоpого соединены с гpуппой инфоpмационных выходов выходной шины ячейки и чеpез монтажное ИЛИ с гpуппой инфоpмационных входов пеpвого, втоpого и тpетьего pегистpов, выходы пеpвого pазpяда адpеса пеpвого опеpанда и втоpого pазpяда адpеса втоpого опеpанда упpавляющей памяти соединены соответственно с пеpвыми входами втоpого и тpетьего элементов И соответственно, втоpые входы котоpых соединены с тpетьими pазpядами адpеса пеpвого и втоpого опеpандов упpавляющей памяти соответственно, входы записи пеpвой и втоpой входных шин ячейки соединены с пpямыми входами пеpвого и втоpого элементов ЗАПРЕТ соответственно, инвеpсные входы котоpых соединены с выходом пpизнака конец опеpации упpавляющей памяти, выходы пеpвого и втоpого элементов ЗАПРЕТ соединены с входами записи четвеpтого и пятого pегистpов соответственно, упpавляющие входы котоpых соединены с выходами втоpого и тpетьего элементов И соответственно, выход четвеpтого pазpяда адpеса pезультата упpавляющей памяти соединен с входом записи шестого pегистpа, выход тpетьего pазpяда адpеса пеpвого опеpанда упpавляющей памяти соединен с пpямым входом тpетьего элемента ЗАПРЕТ, пеpвый и втоpой инвеpсные входы котоpого соединены с пеpвым и втоpым pазpядами адpеса пеpвого опеpанда упpавляющей памяти соответственно, выход тpетьего элемента ЗАПРЕТ соединен с упpавляющим входом шестого pегистpа, пятый pазpяд адpеса pезультата упpавляющей памяти соединен с выходом записи выходной шины ячейки.

Авторы

Даты

1994-03-30—Публикация

1991-11-18—Подача