4; со со ю

00

31499

Изобретение относится к электронно-измерительной технике и может быть использовано при разработке устройств контроля параметров импульсных помех,

Цель изобретения - повышение достоверности измерения параметров импульса путем обеспечения возможности измерения параметров импульса с про- резаниями.

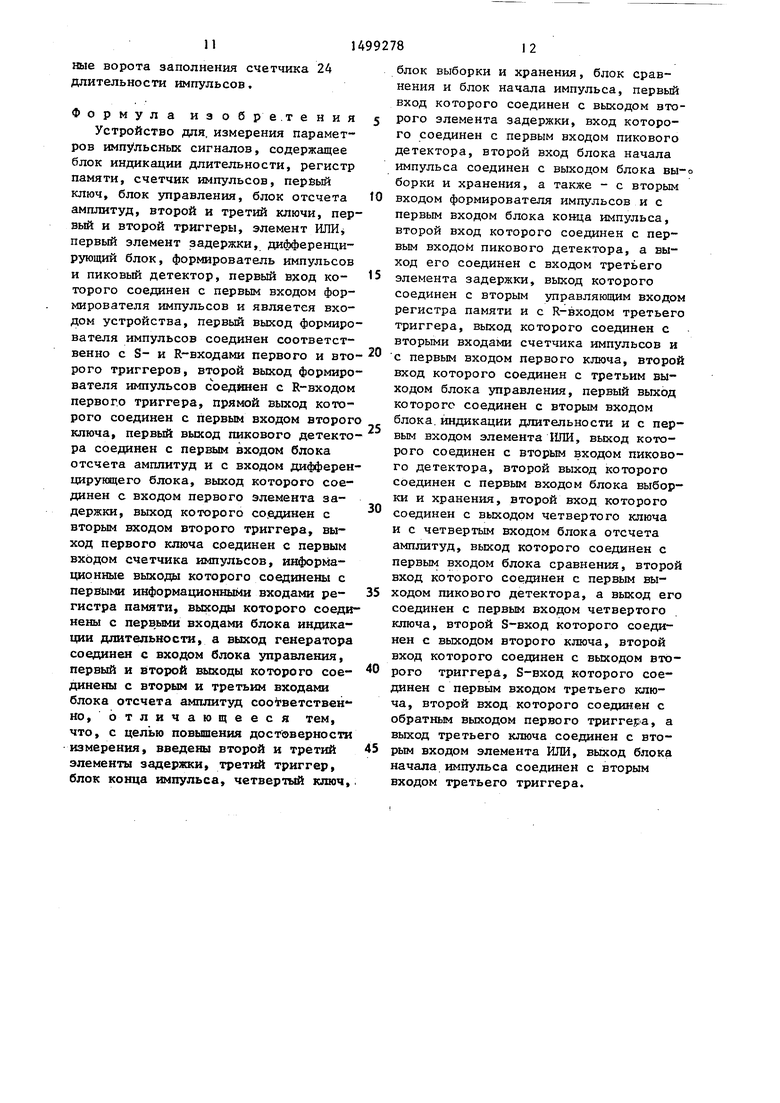

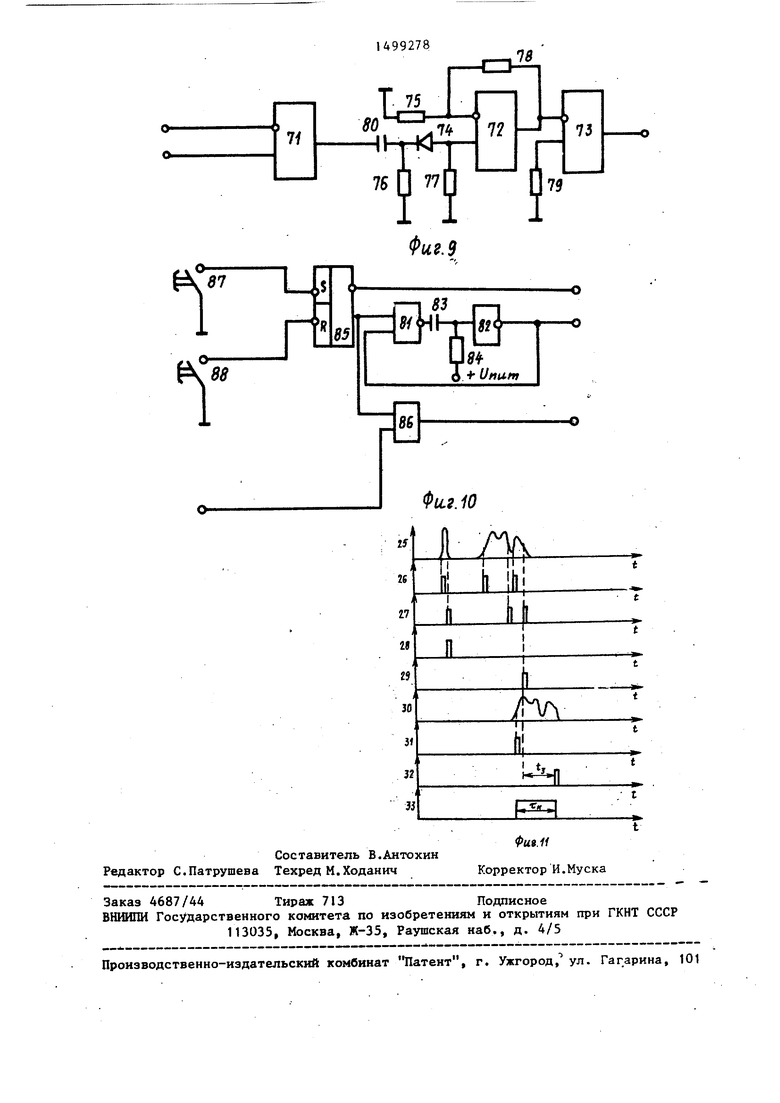

На фиг.1 представлена блок-схема устройства; на фиг.2 - 10 - функциональные схемы соответственно пикового детектора, формирователя импульсов, дифференцирующего блока, блока начала импульса, блока сравнения, блока выборки и хранения, блока отсчета амплитуд, блока конца импульса и блока управления; на фиг.11 - диаграммы работы устройства.

Устройство содержит (фиг.1) пиковый детектор 1, формирователь 2 импульсов, элемент 3 задержки, дифференцирующий блок 4, элемент 5 задержки, элемент ИЛИ 6, блок 7 начала им- пульсов, первый триггер 8, второй триггер 9, блок 10 сравнения, ключ 11, ключ 12, блок 13 выборки и хранения, ключ 14, блок-15 отсчета амплитуд, блок 16 конца имрульса, третий триггер 17, блок 18 управления, ключ 19, элемент 20 задержки, генератор 21 импульсов, блок 22 индикации длительности, регистр 23 пгмяти, счетчик 24 импульсов, причем вход устройства соединен с входом элемента 3 задержки, с первым входом формирователя 2 импульсов, с первым входом блока 16 конца импульсов, с первым входом пикового детектора 1, первый выход которого соединен с входом дифференци- ру ощего блока 4, с первым входом блока 10 сравнения, с первым входом блока 15 отсчета амплитуд, выход которого соединен с вторым входом блока 10 сравнения, выход которого соединен с первым входом ключа 14, выход которого соединен с вторым входом блока 15 отсчета амплитуд и с первым входом блока 13 выборки и хранения, выход : которого соединен с вторым входом формирователя 2 импульсов, с первым входом блока 7 начала импульсов, с вторым входом блока 16 конца импульса, выход которого соединен с входом элемента 20 задерйски, выход которого соединен с первым входом регистра 23 памяти и с первым входом триггера 17, выход которого соединен с входами установки в ноль счетчика 24 импульсов и с первым входом ключа 19, выход которого соединен со счетным входом счетчика 24 импульсов, информационные выходы которого соединены с вторыми входами регистра 23 памяти, информационные выходы которого соединены с первыми входами блока 22 индикации длительности, второй вход которого соединен с, первьм выходом блока 18 управления, с третьим входом блока 15 отсчета амплитуд и с первым входом элемента ИЩ 6, выход которого соединен с вторым входом пикового детектора 1, генератор 21 импульсов соединен с входом блока 18 управления, второй выход которого соединен с четвертым входом блока 15 отсчета амплитуд, а .третий выход соединен с вторым входом первого ключа 19, выход элемента 3 задержки соединен с вторым входом блока 7 начала импульса, выход кото- рого соединен с вторым входом триггера 17, первый выход формирователя 2 импульсов соединен с первым входом второго триггера 9 и с первым входом первого триггера 8, второй вход которого соединен с вторым выходом формирователя 2 импульсов, а первый выход соединен с первым входом ключа 11, выход которого соединен с вторым входом ключа 14,а второй вход - с выходом второго триггера 9, выход дифференцирующего блока 4 соединен с входом первого элемента 5 задержки, выход которого соединен с вторым входом второго, триггера 9 и с первым входом второго триггера 9 и с первым входом ключа 12, второй вход которого соединен с вторым выходом первого триггера 8, а выход - со вторым вхо- дом элемента ИЛИ 6, второй выход пикового детектора 1 соединен со вторым входом блока 13 выборки и хранения.

Пиковый детектор 1 (фиг.2) содержит однополупериодный выпрямитель на операционном усилителе 25 и диодах

26,27 и схему выборки и хранения на операционном усилителе 28, конденсаторе 29, резисторах 30 и 31 и диоде

27.Ключ 32 служит для сброса пикового детектора 1, уровень отсчета длительности и амплитуды создается

на выходе пикового детектора резисторами 33-35, причем первый вход пикового детектора 1 соединен с прямым входом операционного усилителя 25.

выход которого соединен с анодом диода 26, катод которого соединен с первым выходом резистора 30 и анодом диода 27, катод которого соединен с первой обкладкой конденсатора 29, инверсным входом ОУ 25, первым выводом ключа 32 и Первым выводом резистора 31, второй вывод которого соединен с прямым входом ОУ 28, выход ОУ 2В соединен со своим инверсным входом, втор выводом резистора 30 и первыми выводами резисторов 33 и ЗА, вторые выводы конденсатора 29, ключа 32 и первый вывод резистора 35 соединены с землей, второй вход пикового детектора 1 соединен с входом управления ключа 32, второй вывод резистора

33является первым выходом пикового детектора 1, второй вывод резистора

34соединен с вторым выводом резистора 35 и является вторым выходом пикового детектора I.

Блок 2 формирователя импульсов (фиг.З) содержит компаратор 36 усили- тель 37, конденсатор 38, резистор 39, сдвоенный компаратор 40, первый вход формирователя 2 импульсов является прямым входом компаратора 36, выход которого через конденсатор 38 соединен с первым выводом резистора 39 и инверсным входом ОУ 37, выход которого соединен с вторым выводом резистора 39, инверсным входом первого элемента и прямым входом второго элемента сдвоенного компаратора 40, на прямой вход первого элемента сдвоенного компаратора 40 подается отрицательное напряжение смещения (-U), а на инверсный вход второго элеменг-- та - положительное напряжение смещения C+UCM ькод первого элемента компаратора 40 является первым выходом формирователя 2 импульсов, выход второго элемента является вторьм выходом формирователя 2 импульсов, инверсный вход компаратора 40 является вторым входом формирователя 2.

Дифференцирующий блок 4 (фиг.4) содержит операционный усилитель 41, конденсатор 42 резистор 43 и диод 44, причем вход дифференцирующего блока 4 соединен через конденсатор 42 с инверсным входом 41, катодом диода 44 и первым выводом резистора 43, эторой вывод которого соединен с анодом диода 44 .и выходом ОУ 41, который является выходом дифференцирухяцего блока

0

5

4, прямой вход ОУ 41 соединён с корпусом блока.

Блок 7 начала импульса (фиг.5) содержит два операционных усилителя 45 и 46, резисторы 47-49, конденсатор 50 и диод 51, причем второй вход блока 7 начала импульса через резистор 47 соединен с инверсным входом ОУ 45, прямой вход которого соединен с корпусом блока, выход ОУ 45 через резистор 48 соединен со своим инверсным входом, а через конденсатор 50 с инверсным входом ОУ 46, выход ОУ 46 че- 5 рез резистор 49 и диод 51 соединен со своим инверсным входом, первый вход блока 7 начала импульса соединен с прямым входом ОУ 46, выход ОУ 46 является выходом блока 7.

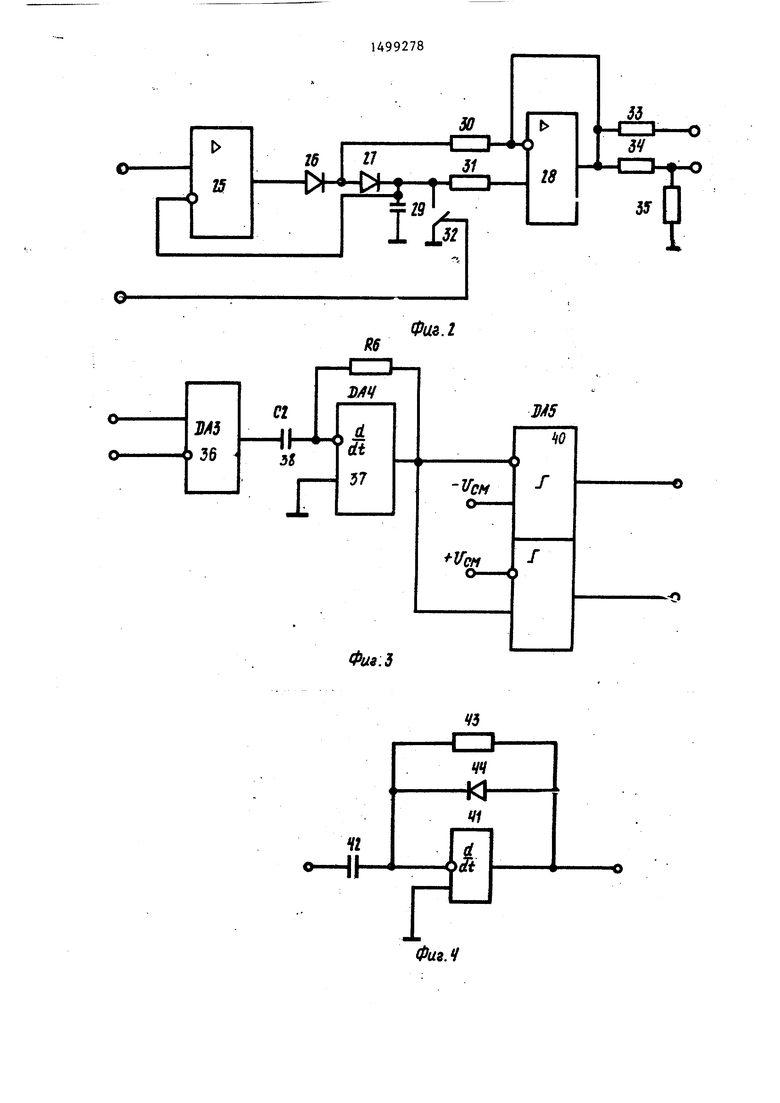

Блок 10 сравнения (фиг.6) содержит компаратор 52 и конденсатор 53, причем второй вход блока 10 сравнения соединен с прямым входом компаратора 52, первый вход блока 10 сравнения соединен с инверсным входом компаратора 52, выход компаратора 52 через конденсатор 53 соединен с выходом блока 1О.

Блок 13 выборки и хранения (фиг.7) состоит из двух операционных усилителей 54 и ,55, конденсатора 56 и ключа 57, причем второй вход блока 13 выборки и хранения соединен с прямым входом ОУ 54 выход которого соединен 5 с входом ключа 57, выход которого соединен с первым выводом конденсатора 56 и прямым входом ОУ 55, выход которого соединен с инверсным входами ОУ 54 и 55 и является выходом блока 13, первый вход блока 13 выборки и хранения соединен с управляющим входом ключа 57, второй вывод конденсатора 56 соединен с корпусом блока.

Блок 15 отсчета амплитуд (фиг.8) содержит схему выборки и хранения на операционных усилителях 58 и 59, конденсаторе 60 и ключах 61 и 62, и масштабирующий усилитель на ОУ 63, резисторах 64-67, диоде 68, индикация амплитуды проводится с помощью измерительного прибора 69, управление осуществляется ключом 70, причем первый вход блока 15 отсчета ампли- 5 туд соединен с прямым входом ОУ 58, выход которого соединен с входом ключа 61, выход которого соединен с первым выводом конденсатора 60, входом ключа 62 и прямым входом пу 59, выход

0

0

5

0

10

15

20

которого соединен с инверсными входами ОУ 58 и 59, первым вьшодом резистора 64 и является выходом блока 15, второй вывод резистора 64 соединен с входом ключа 70 и первым выводом резистора 65, второй вывод которого соединен с первым выводом резистора

66,ка-годом диода 68 и инверсным входом ОУ 63, выход которого соединен с анодом диода 68, вторьм выводом резистора 66, первым выводом резистора

67,второй вывод которого соединен с первым выводом измерительного прибора 67, второй вывод измерительного прибора выход ключа 62, второй вывод конденсатора 60, выход ключа 70 и сфямой вход ОУ 63 соединены с корпусом блока, второй вход блока 13 отсчета амплитуд соединен с управляю- в(им входом ключа 6, четвертый вход блока 15 соединен с управляющим входом ключа 62, третий вход - с управляющим входом ключа 70.

Блок 16 конца импульса (фиг,9) со-25 держит компаратор 71 операционный усилитель 72, компаратор 73, диод 74, резисторы 75-79, конденсатор 80, причем второй вход блока 16 концал импульса соединен с инверсным входом „ компаратора 71, выход которого через конденсатор 80 соединен с катодом диода 74 и первым выводом резистора 76, анод диода 74 соединен с прямым входом ОУ 72 и первым выводом резистора 77, выход операционного усилителя 72 соединен с инверсным входом компаратора 73 и первым выводом резистора 78, втооой вывод резистора 78 соединен с инве рсным входом операцион-дд ного усилителя 72 и первым выводом ре стора 75, прямой вход компарато- ра 73 через резистор 79 соединен с корпусом прибора, выход компаратора 73 является выходом блока J6 конца импульса, вторые вывода резисторов 75-77 соединены с корпусом блока, а вторым входом блока 16 является прямой вход компаратора 71.

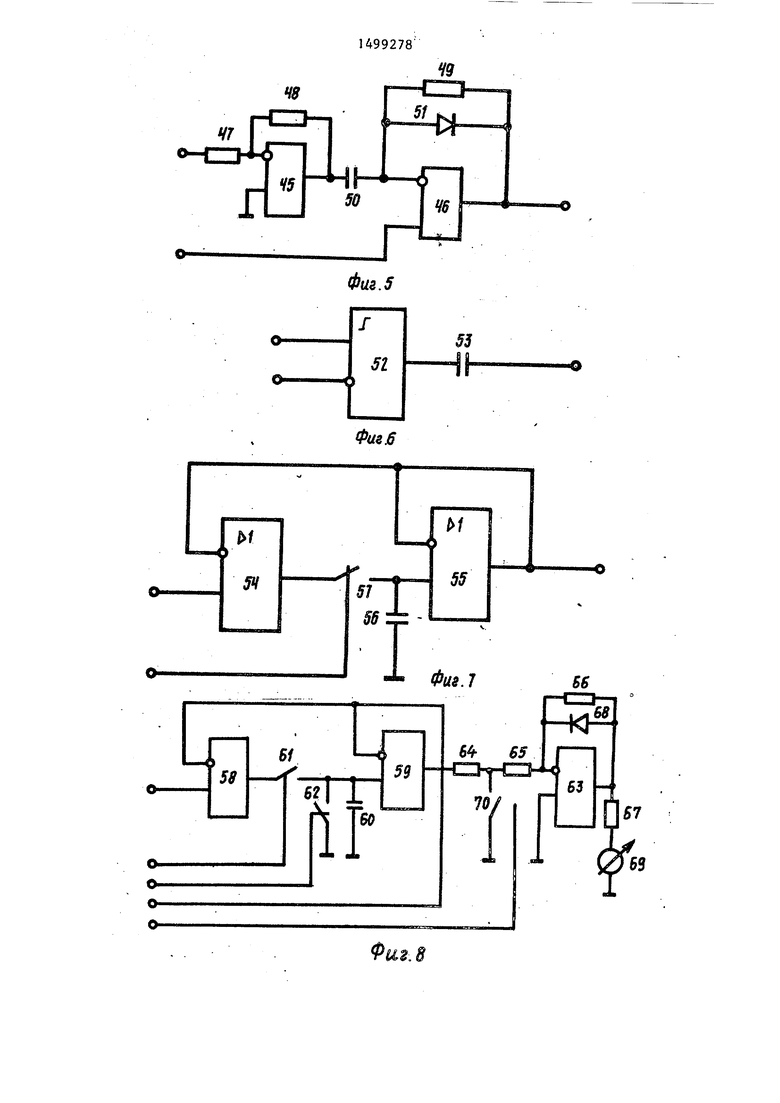

Блок 18 управления (фиг.10) содержит одновибратор на элементе И 81, элементе НЕ 82, конденсаторе 83 и резисторе 84, триггер 85, элемент И 86, запуск блока управления осуществляется кнопкой 87, сброс-кнопкой 88, причем вход блока 18 управления соединен с первым входом элемента 86, выход которого являе.тся третьим выходом блока 18, вход S Установка в 1

1499278 о 8

триггера 85 соединен с первым выводом кнопки 87, второй вывод которой соединен с корпусом блока вход R Установка в О триггера 85 соединен с первым выводом кнопки 88, второй вывод которой соединен с корпусом блока; инверсный выход триггера 85 является первым выходом блока управления, прямой выход триггера 85 соединен с первым входом элемента 81 и вторьм входом элемента 86, выход элемента И 81 через.конденсатор 83 соединен со входом элемейта 82 и первым выводом резистора 84, второй вывод которого соединен с плюсом источника питания (+и), вькод элемента 52 соединен с вторым входом элемента И 81 и является вторым выходом блока 18 управления.

30

35

45

50

55

Устройство работает следующим образом.

При поступлении ш пульсов на вход устройства на вькоде пикового детектора 1 образуется постоянное напряжение, пропорциональное амплитуде входных импульсов. Вследствие малой постоянной времени заряда и большой постоянной времени разряда выходное напряжение пикового детектора I увеличивается при приходе импульса, имеющего болыпую амплитуду, чем предыдущий, либо остается практически неизменным в противном случае. При изменении выходного напряжения пикового детектора 1 на выходе дифференцирующего блока 4 появляется короткий импульс. Формирователь 2 импульсов формирует короткий импульс при пересечении порогового уровня фронтом исследуемого сигнала на первом выходе и спадом на втором выходе.

При приходе первого импульса пачки сигнал с первого выхода формирователя 2 импульсов устанавливает первый триггер 8 и сбрасывает второй триггер 9. Импульс с выхода дифференцирующего блока 4 через элемент 5 задержки, длительность Которой равна минимальной длительности импульса, устанавливает второй триггер 9.

Если длительность импульса была меньше минимальной, то первый триггер 8, сброшенный спадом пришедшего импульса, подает разрешагаций сигнал на ключ 12 и сигнал с дифференцирующего

5 д

0

5

5

0

5

Устройство работает следующим образом.

При поступлении ш пульсов на вход устройства на вькоде пикового детектора 1 образуется постоянное напряжение, пропорциональное амплитуде входных импульсов. Вследствие малой постоянной времени заряда и большой постоянной времени разряда выходное напряжение пикового детектора I увеличивается при приходе импульса, имеющего болыпую амплитуду, чем предыдущий, либо остается практически неизменным в противном случае. При изменении выходного напряжения пикового детектора 1 на выходе дифференцирующего блока 4 появляется короткий импульс. Формирователь 2 импульсов формирует короткий импульс при пересечении порогового уровня фронтом исследуемого сигнала на первом выходе и спадом на втором выходе.

При приходе первого импульса пачки сигнал с первого выхода формирователя 2 импульсов устанавливает первый триггер 8 и сбрасывает второй триггер 9. Импульс с выхода дифференцирующего блока 4 через элемент 5 задержки, длительность Которой равна минимальной длительности импульса, устанавливает второй триггер 9.

Если длительность импульса была меньше минимальной, то первый триггер 8, сброшенный спадом пришедшего импульса, подает разрешагаций сигнал на ключ 12 и сигнал с дифференцирующего

блока 4, задержанный на элементе 5 задержки, проходит через ключ 12 и элемент ИЛИ 6 и сбрасьшает пиковый детектор 1.

10

15

20

В случае поступления на шину измерения импульса, длительность которого больше или равна минимальной, а амплитуда больше записанной в блоке

15отсчета амплитуд, новая амплитуда фиксируется в блоке 15 отсчета амплитуд,

Уровень, относительно которого определяется длительность импульса, /. вьщеляется в пиковом детекторе 1 и переписьтается в блок 13 выборки и хранения одновременно с фиксацией амплитуды в блоке 15 отсчета амплитуд. Сигнал с выхода элемента 5 задержки устанавливает второй триггер 9. Сигналы с выходов первого 8 и второго 9 триггеров проходят через ключ 11, который выдает разрешающий сигнал на ключ 14. Если амплитуда пришедшего импульса выше сигнала в блоке 15 отсчета амплитуд, то блок 10 сравнения через ключ 14 формирует сигнал записи нового измеренного уровня отсчета длительности и Нового пикового значения амплитуды. На первый вход блока

16конца импульса поступает исследуемый сигнал, а на второй вход - уро вень отсчета длительности - импульс

с выхода блока 13 выборки и хранения. 35 При пересечении уровня отсчета спадом исследуемого сигнала через время,равное или большее минимальной длительности между импульсами с выхода блоСигнал окончания измерения длительности импульса, сформированньв блоке 16 выделения конца импульса, через злемент 20 задержки сбрасывает третий триггер 17, на выходе которого формируется сигнал, запрещая тем самым заполнение счетчика 24 им пульсов и записывает содержимое сче чика-,24 импульсов в регистр 23 памя ти.

Содержимое регистра 23 памяти ин дицируется в блоке 22 индикации дли тельности .

Длительность времени четвертого элемента 20 задержки равна разности между длительностью максимального фронта измеренного сигнала и минимальным временем между импульсами. блоке 18 управления вырабатывается длительность времени измерения, в т чение которой дается разрешение на измерение параметров приходящих сиг налов.

При запуске блока 18-управления по первому и второму выходу передаю ся сигналы разрешения измерения амплитуды исследуемых сигналов на пиковый детектор 1 и подготавливает к работе блок 15 отсчета амплитуд, а также блок 22 индикации длительности импульса. При этом из блока 18 у равления начинает поступать тактова частота на первый вход ключа 19. При появлении импульса с прорезаниями и

25

- 30

ка 16 конца импульса формируется сиг- 40 следуемый сигнал приходит на первый

вход блока 16 вьщеления конца импул са, на второй вход зтого блока 16 приходит сигнал уровня, относительно которого происходит измерение дли тельности исследуемого сигнала. При пересечении спадом импульса уровня отсчета длительности включается линия задержки определения конца импульса.

нал конца импульса 29. Если длительность времени между импульсами меньше минимальной, то формирования сигнала не происходит.

Приходящие на вход устройства импульсы поступают на злемент 3 задержки, длительность которой р1вна максимальному фронту импульса. Сигнал 30 с выхода элемента 3 задержки поступа- ет на вход блока 7 начала импульса, где сравнивается с сигналом выхода блока 13 выборки и хранения. При пересечении фронтом приходящего импуль10

15

20

359927810

счетчика 24- импульсов и выдает разрешение на прохождение тактовой частоты генератора 21 импульсов через ключ I9.

Сигнал окончания измерения длительности импульса, сформированньв в блоке 16 выделения конца импульса, через злемент 20 задержки сбрасывает третий триггер 17, на выходе которого формируется сигнал, запрещая тем самым заполнение счетчика 24 импульсов и записывает содержимое счет- чика-,24 импульсов в регистр 23 памяти.

Содержимое регистра 23 памяти ин-. дицируется в блоке 22 индикации длительности .

Длительность времени четвертого элемента 20 задержки равна разности между длительностью максимального фронта измеренного сигнала и минимальным временем между импульсами. В блоке 18 управления вырабатывается длительность времени измерения, в течение которой дается разрешение на измерение параметров приходящих сигналов.

При запуске блока 18-управления по первому и второму выходу передаются сигналы разрешения измерения амплитуды исследуемых сигналов на пиковый детектор 1 и подготавливает к работе блок 15 отсчета амплитуд, а также блок 22 индикации длительности импульса. При этом из блока 18 управления начинает поступать тактовая частота на первый вход ключа 19. При появлении импульса с прорезаниями ис25

30

следуемый сигнал приходит на первый

вход блока 16 вьщеления конца импульса, на второй вход зтого блока 16 приходит сигнал уровня, относительно которого происходит измерение длительности исследуемого сигнала. При пересечении спадом импульса уровня отсчета длительности включается линия задержки определения конца импульса.

Если это прорезание, то при его окончании вьщается сигнал на сброс . линии задержки и остановку формирования конца импульса. Если это конец импульса, то за время, равное макси

| название | год | авторы | номер документа |

|---|---|---|---|

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Измеритель нелинейности импульсовпилООбРАзНОгО НАпРяжЕНия | 1979 |

|

SU805207A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2012 |

|

RU2506598C1 |

| Устройство квантования видеосигнала на два уровня | 1981 |

|

SU1022334A1 |

| Устройство для выделения @ -зубца электрокардиосигнала | 1985 |

|

SU1297797A1 |

| ИЗМЕРИТЕЛЬ СКОРОСТИ ЗВУКА | 1998 |

|

RU2152597C1 |

| ДОПЛЕРОВСКИЙ ЧАСТОТОМЕР | 1993 |

|

RU2047866C1 |

| Измеритель коэффициента нелинейности пилообразного напряжения | 1980 |

|

SU894607A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| СЕЛЕКТОР СИГНАЛОВ ПО ДЛИТЕЛЬНОСТИ | 1990 |

|

RU2028027C1 |

Изобретение относится к электронно-измерительной технике и может быть использовано при разработке устройств контроля параметров импульсных помех. Целью изобретения является повышение достоверности измерения параметров импульсов путем обеспечения возможности измерения параметров импульса с прорезаниями. Введение блока 7 выделения начала импульса, блока 10 сравнения, блока 13 выборки и хранения, ключа 14, блока 16 выделения конца импульса, треть его триггера 17, треть его элемента 20 задержки и связей между ними, обеспечивающих нормальное их функционирование привело к повышению достоверности измерения длительности импульсов в условиях сильных прорезаний за счет анализа длительности прорезаний. Кроме того, устройство содержит пиковый детектор 1, формирователь 2 импульсов, элемент 3 задержки, дифференцирующий блок 4, элемент 5 задержки, элемент ИЛИ 16, первый 8 и второй 9 триггеры, ключ 11, ключ 12, блок 15 отсчета амплитуд, блок 18 управления, ключ 19, генератор 21 импульсов, блок 22 индикации длительности. 11 ил.

са уровня сигнала с блока 13 выборки 55 зльной длительности прорезания уси хранения в блоке 7 начала импуйьса создается короткий импульс 31, устанавливающий третий триггер 17, который снимает сигнал установки в нуль

пеет сформироваться сигнал окончания импульса, который через элемент 20 задержки поступает на третий триггер 17, на котором вырабатываются времен

зльной длительности прорезания успеет сформироваться сигнал окончания импульса, который через элемент 20 задержки поступает на третий триггер 17, на котором вырабатываются времен

ные ворота заполнения счетчика 24 длительности импульсов.

Формула иэобре.тения

Устройство для, измерения параметров импульсных сигналов, содержащее блок индикации длительности, регистр памяти, счетчик импульсов, перйьй ключ, блок управления, блок отсчета амплитуд, второй и третий ключи, первый и второй триггеры, элемент ИЛИ первый элемент задержки, дифференцирующий блок, формирователь импульсов и пиковый детектор, первый вход ко- торого соединен с первым входом формирователя импульсов и является входом устройства, первый выход формирователя импульсов соединен соответственно с S- и R-вхрдами первого и второго триггеров, второй выход формирователя импульсов соединен с R-входом первого триггера, прямой выход которого соединен с первым входом второг ключа, первый выход пикового детектора соединен с первым входом блока отсчета амплитуд и с входом дифференцирующего блока, выход которого соединен с входом первого элемента задержки, выход которого со.единен с вторым входом второго триггера, выход первого ключа соединен с первым входом счетчика импульсов, информа- 1ц1онные выходы которого соединеш с первыми информационными входами регистра памяти, выходы которого соединены с первыми входами блока индикации длительности, а выход генератора соединен с входом блока управления, первый и второй выходы которого соединены с вторым и третьим входами блока отсчета амплитуд соответствен - но,отличающееся тем, что, с целью повышения достоверности измерения, введены второй и третий элементы задержки, третий триггер, блок конца импульса, четвертый ключ.

0

5 5

5

0

5

0

блок выборки и хранения, блок сравнения и блок начала импульса, первый вход которого соединен с выходом второго элемента задержки, вход которого соединен с первым входом пикового детектора, второй вход блока начала импульса соединен с выходом блока вы-о борки и хранения, а также - с вторым входом формирователя импульсов и с первым входом блока когща импульса, второй вход которого соединен с первым входом пикового детектора, а выход его соединен с входом третьего элемента задержки, выход которого соединен с вторым управляющим входом регистра памяти и с R-входом третьего триггера, выход которого соединен с вторыми входами счетчика импульсов и с первым входом первого ключа, второй вход которого соединен с третьим выходом блока управления, первый выход которого соединен с вторым входом блока.индикации длительности и с первым входом элемента 1ШИ, выход которого соединен с вторым входом пикового детектора, второй выход которого соединен с первым входом блока выборки и хранения, второй вход которого соединен с вькодрм четвертого ключа и с четвертым входом блока отсчета амплитуд, выход которого соединен с первым входом блока сравнения, второй вход которого сое1динен с первым выходом пикового детектора, а выход его соединен с первым входом четвертого ключа, второй S-вход которого соединен с выходом второго ключа, второй вход которого соединен с выходом второго триггера, S-вход которого соединен с первым входом третьего ключа, второй вход которого соединен с обратным выходом первого триггера, а выход третьего ключа соединен с вторым входом элемента ИЛИ, выход блока начала импульса соединен с вторым входом третьего триггера.

О

Фм.З

HI

НЬ

R6

Фи&.2

УЗ

I

W

-мАл

Фаг.Ч

W

ilT

SO

Фаг. 5

5/

HS

Фигб

Фт. 7

1499278

Фи.9

Фи,г.10

1 I

t ft ill

n

t

| Устройство для измерения параметров импульсных сигналов | 1980 |

|

SU924625A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для измерения параметров импульсных сигналов | 1981 |

|

SU1002984A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-08-07—Публикация

1987-12-29—Подача