Изобретение относится к средствам измерения частоты путем преобразования частоты в напряжение и может быть использовано в области медицины в ультразвуковых допплеровских измерителях скорости кровотока.

Наиболее близким по технической сущности к предлагаемому является частотомер из состава ультразвукового допплеровского измерителя скорости кровотока, который содержит нуль-компаратор 11, детектор 13, первый фильтр 14 нижних частот, пороговый компаратор 15, мультиплексор 16, второй фильтр 17 нижних частот, формирователь (21, 23-25) стандартных импульсов, источник 26 опорного напряжения, и который предназначен для получения напряжения, пропорционального частоте допплеровского сигнала.

Сигналы Х1(t) и Х2(t) имеют одинаковую частоту и амплитуду и отличаются только по фазе, что несущественно, если оставить в стороне вопрос о знаке допплеровской частоты и ограничиться однополярным выходным напряжением Uвых, как это принято для предлагаемого допплеровского частотомера; поэтому сигналы Х1(t) и Х2(t) равнозначны в отношении работы нуль-компаратора 11 и детектора 13.

Прототип несовершенен с точки зрения чувствительности измерений частоты, поскольку не обеспечивает требуемой точности измерений при малом отношении сигнал/шум, а также достоверности измерений.

Хотя прототип имеет высокую чувствительность преобразования двухполярного сигнала в импульсный, благодаря применению нуль-компаратора, но именно это обусловливает его недостатки.

Импульсные помехи, возникающие под действием шума внешнего и внутреннего происхождения приводят к потере точности.

Частота импульсного сигнала в отсутствие полезного сигнала на входе частотомера под действием шума стремится принять значения, близкие к верхнему пределу рабочего диапазона частот, и, вместо нулевого показания, частотомер дает ложные показания, чем нарушается достоверность измерений. В прототипе для обеспечения достоверности измерений формируется сигнал Кр, управляющий работой второго фильтра нижних частот; однако нет гарантии от появления выброса выходного напряжения частотомера при пропадании полезного сигнала на его входе из-за задержки выключения сигнала Кр.

Цель изобретения повышение чувствительности измерений частоты допплеровского сигнала в широком диапазоне частот.

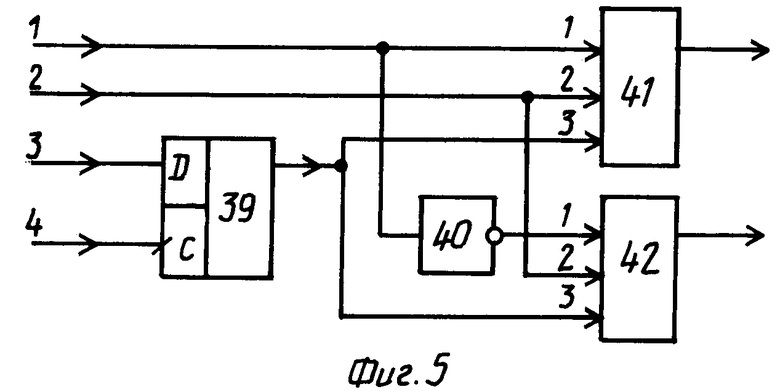

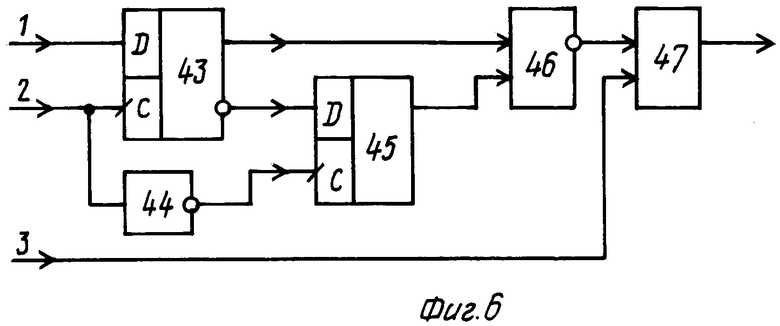

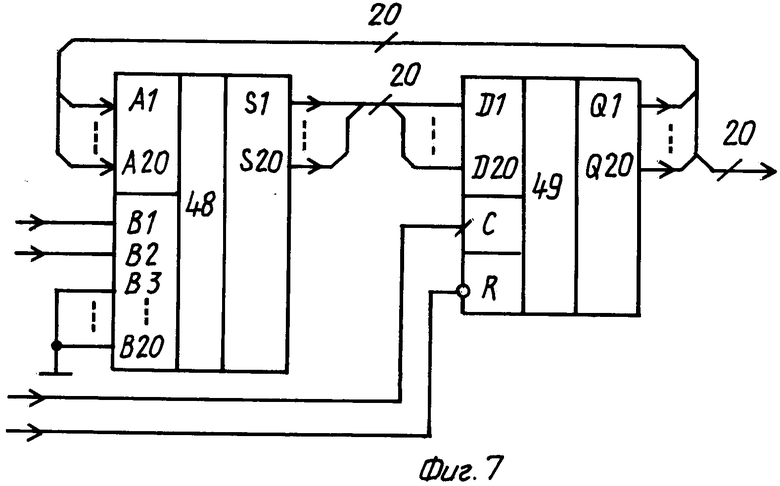

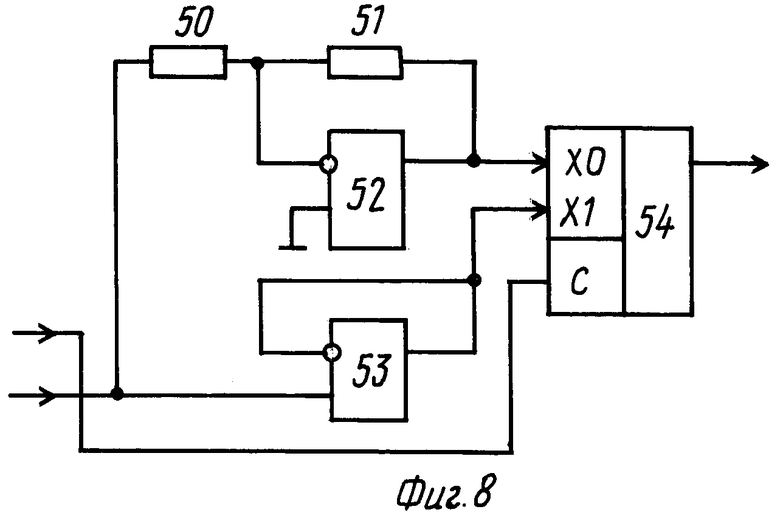

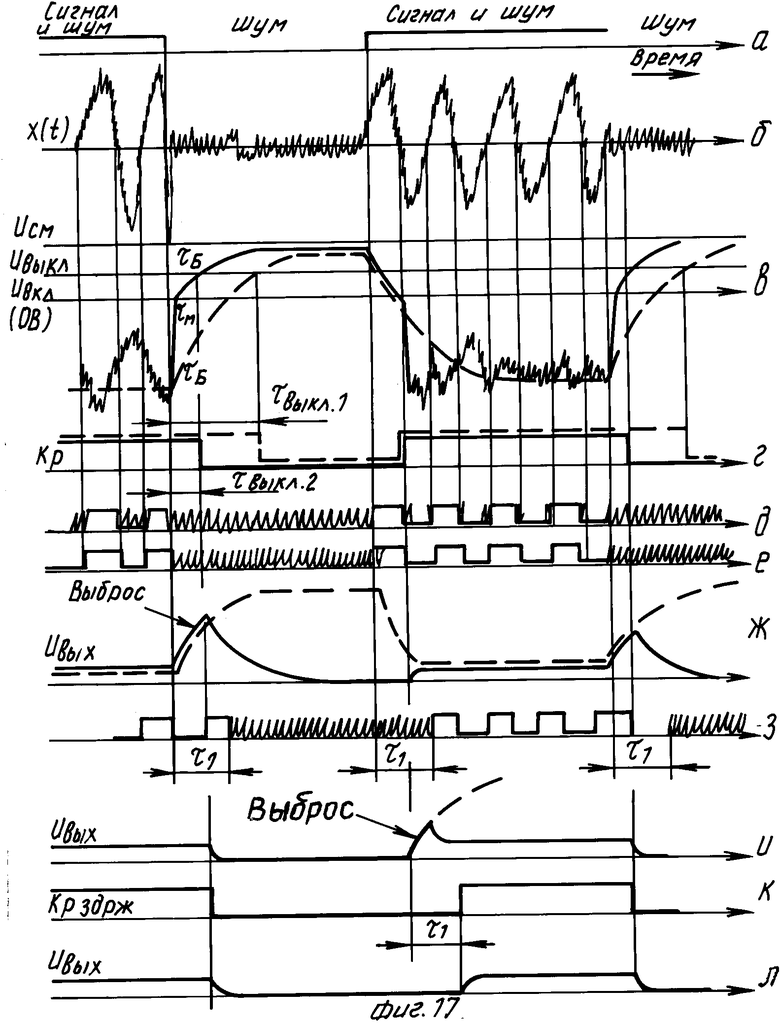

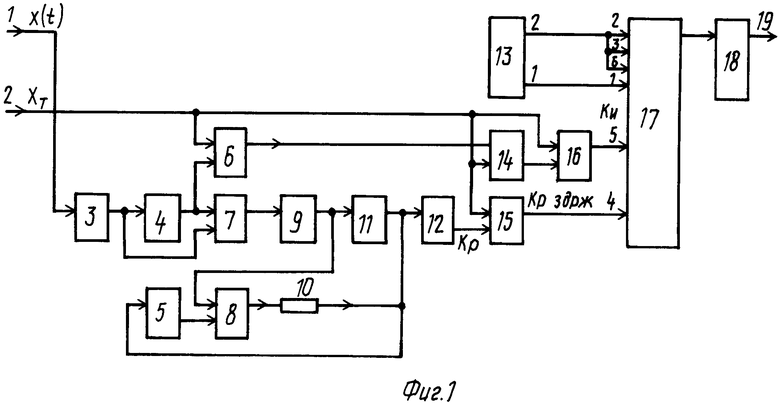

На фиг.1-15 представлены структурные схемы частотомера и его частей; на фиг. 1 частотомера; на фиг.2 усилителя; на фиг.3 нуль-компаратора; на фиг.4 селектора скважности; на фиг.5 формирователя кода; на фиг.6 формирователя сброса; на фиг.7 счетчика; на фиг.8 детектора; на фиг.9 инвертора; на фиг.10 первого фильтра нижних частот; на фиг.11 порогового компаратора; на фиг.12 элемента задержки сигнала; на фиг.13 элемента задержки фронта; на фиг.14 формирователя длительности; на фиг.15 второго фильтра нижних частот; на фиг. 16 временные диаграммы работы элемента задержки сигнала; на фиг.17 временные диаграммы, связанные с устранением выброса напряжения на выходе частотомера.

Частотомер содержит две входные шины 1 и 2, усилитель 3, два нуль-компаратора 4 и 5, селектор 6 скважности, детектор 7, ключ 8, инвертор 9, резистор 10, фильтр 11 нижних частот, пороговый компаратор 12, источник 13 опорного напряжения, элемент 14 задержки сигнала, элемент 15 задержки фронта, формирователь 16 длительности, мультиплексор 17, фильтр 18 нижних частот и выходную шину 19.

Входная шина 1 частотомера соединена с входом усилителя 3, выход которого соединен с сигнальным входом детектора 7 и входом нуль-компаратора 4, выход которого соединен с сигнальным входом селектора 6 скважности и управляющим входом детектора 7, выход которого соединен с входом инвертора 9, выход которого соединен с входом фильтра 11 нижних частот и сигнальным входом ключа 8, управляющий вход которого соединен с выходом нуль-компаратора 5, а выход с выводом резистора 10, другой вывод которого соединен с выходом фильтра 11 нижних частот, входом нуль-компаратора 5 и входом порогового компаратора 12, выход которого соединен с сигнальным входом элемента 15 задержки фронта, тактовый вход которого соединен с входной шиной 2 частотомера и тактовыми входами элемента 14 задержки сигнала, формирователя 16 длительности и селектора 6 скважности, выход которого соединен с сигнальным входом элемента 14 задержки сигнала, выход которого соединен с сигнальным входом формирователя 16 длительности, выход которого соединен с пятым входом мультиплексора 17, четвертый вход которого соединен с выходом элемента 15 задержки фронта, первый вход c первым выходом источника 13 опорного напряжения, второй, третий и шестой входы со вторым выходом источника 13 опорного напряжения, а выход с входом фильтра 18 нижних частот, выход которого соединен с выходной шиной 19 частотомера.

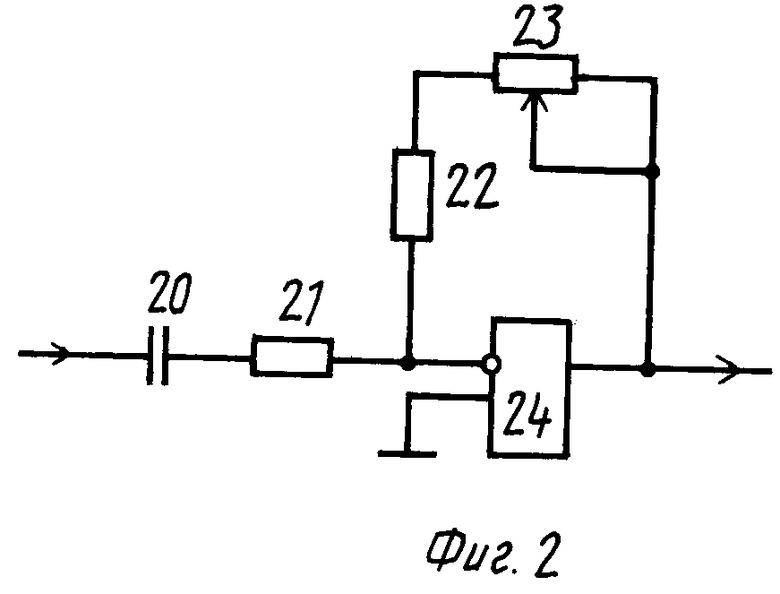

Усилитель 3 (фиг. 2) содержит конденсатор 20, резисторы 21-23 и операционный усилитель 24. Вход усилителя 3 соединен с выводом конденсатора 20, другой вывод которого соединен с выводом резистора 21, другой вывод которого соединен с первым выводом резистора 22 и инверсным входом операционного усилителя 24, прямой вход которого соединен с общим проводом, а выход с выходом усилителя 3 и первым и вторым выводами резистора 23, третий вывод которого соединен с вторым выводом резистора 22.

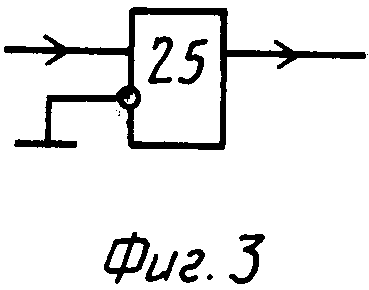

Нуль-компаратор 4 (5) (фиг.3) содержит компаратор 25. Вход нуль-компаратора 4 соединен с прямым входом компаратора 25, инверсный вход которого соединен с общим проводом, а выход с выходом нуль-компаратора 4.

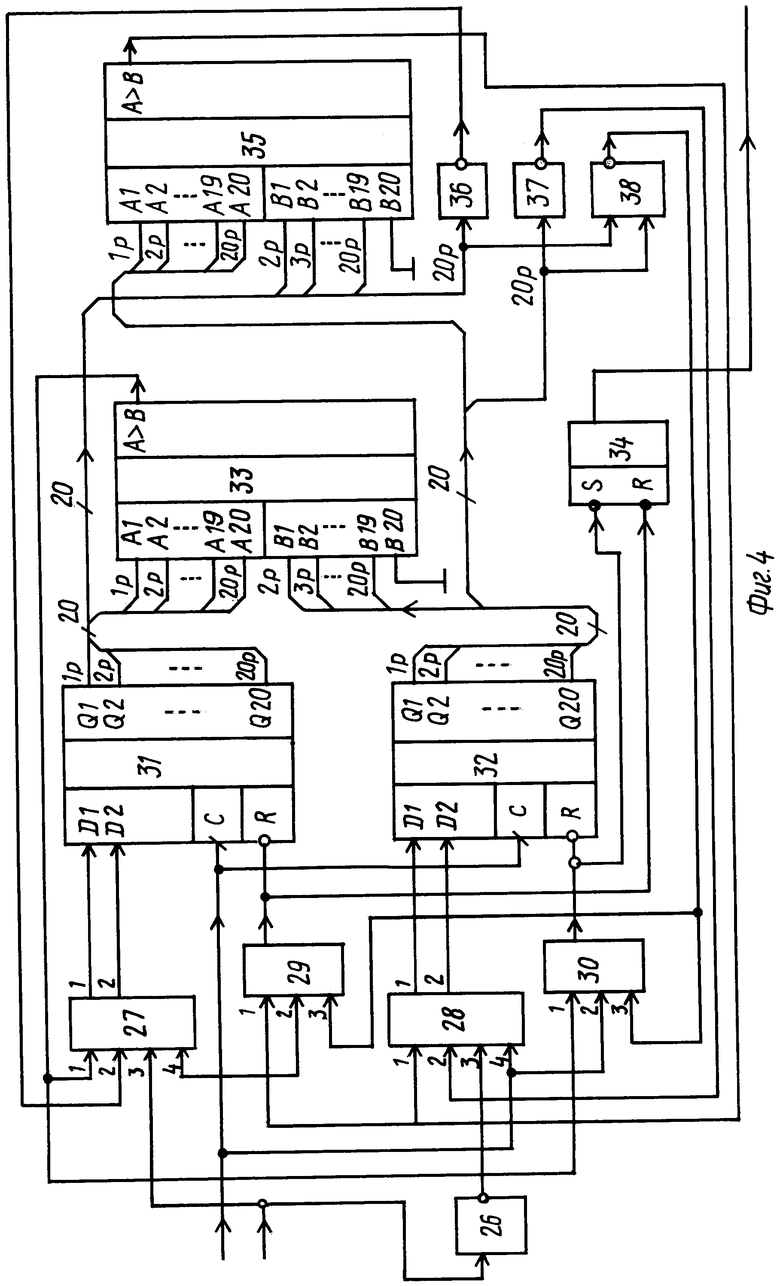

Селектор 6 скважности (фиг.4) содержит инвертор 26, два формирователя 27 и 28 кода, два формирователя 29 и 30 сброса, два счетчика 31 и 32, компаратор 33, RS-триггер 34, компаратор 35, два инвертора 36 и 37 и элемент 38 2И-НЕ. Сигнальный вход селектора 6 скважности соединен с третьим входом формирователя 27 кода и входом инвертора 26, выход которого соединен с третьим входом формирователя 28 кода, первый вход которого соединен с первым входом формирователя 29 сброса и выходом компаратора 35, второй вход с выходом инвертора 37, а четвертый вход с тактовым входом селектора 6 скважности, вторыми входами формирователей 29 и 30 сброса, входами С счетчиков 31 и 32 и четвертым входом формирователя 27 кода, первый вход которого соединен с первым входом формирователя 30 сброса и выходом компаратора 33, второй вход с выходом инвертора 36, первый и второй выходы соответственно с входами D 1 и D 2 счетчика 31, вход R которого соединен с входом R RS-триггера 34 и выходом формирователя 29 сброса, а выходы (Q 2 Q 20) соединены соответственно с входами (А 2 -А 20) компаратора 33 и входами (В1-В19) компаратора 35, выход Q 20 с входом инвертора 36 и первым входом элемента 38 2И-НЕ, выход Q 1 с входом А1 компаратора 33, вход В20 которого соединен с общим проводом, а входы (В1 В19) с выходами (Q 2 Q 20) cчетчика 32, входами (А2 А20) компаратора 35, вход В20 которого соединен с общим проводом, а вход А1 с выходом Q1 cчетчика 32, входы D1 и D2 которого соединены соответственно с первым и вторым выходами формирователя 28 кода, а выход Q20 c входом инвертора 37 и вторым входом элемента 38 2И-НЕ, выход которого соединен с третьими входами формирователя 29 сброса и формирователя 30 сброса, выход которого соединен с входом R счетчика 32 и входом S RS-триггера 34, выход которого соединен с выходом селектора 6 скважности.

Формирователь 27 (28) кода (фиг.5) содержит D-триггер 39, инвертор 40 и два элемента 41 и 42 3И. Первый вход формирователя 27 кода соединен с первым входом элемента 41 3И и входом инвеpтора 40, второй вход с вторыми входами элементов 41 и 42 3И, третий и четвертый входы соответственно с входом D и входом С D-триггера 39, выход которого соединен с третьими входами элементов 41 и 42 3И, выходы которых соединены соответственно с первым и вторым выходами формирователя 27 кода, а первый вход элемента 42 3И соединен с выходом инвертора 40.

Формирователь 29 (30) сброса (фиг.6) содержит D-триггер 43, инвертор 44, D-триггер 45, элемент 46 2И-НЕ и элемент 47 2И. Первый вход формирователя 29 сброса соединен с входом D D-триггера 43, второй вход с входом С D-триггера 43 и входом инвертора 44, третий вход с вторым входом элемента 47 2И, выход которого соединен с выходом формирователя 29 сброса, а первый вход с выходом элемента 46 2И-НЕ, первый вход которого соединен с прямым выходом D-триггера 43, инверсный выход которого соединен с входом D D-триггера 45, выход которого соединен с вторым входом элемента 46 2И-НЕ, а вход С с выходом инвертора 44.

Счетчик 31 (32) (фиг.7) содержит сумматор 48 и регистр 49. Входы D1 и D2 счетчика 31 соединены соответственно с входами В1, В2 сумматора 48, входы С и R соответственно с входами С и R регистра 49, входы (D1 D20) которого соединены соответственно с выходами (S1 S20) cумматора 48, а выходы (Q1 Q20) с выходами (Q1 Q20) cчетчика 31 и входами (А1 А20) сумматора 48, входы (В3-В20) которого соединены с общим проводом.

Детектор 7 (фиг. 8) содержит два резистора 50 и 51, два операционных усилителя 52 и 53 и мультиплексор 54. Сигнальный вход детектора 7 соединен с прямым входом операционного усилителя 53 и выводом резистора 50, другой вывод которого соединен с первым выводом резистора 51 и инверсным входом операционного усилителя 52, прямой вход которого соединен с общим проводом, а выход с вторым выводом резистора 51 и входом ХО мультиплексора 54, вход Х1 которого соединен с инверсным входом и выходом операционного усилителя 53, вход С и выход соответственно с управляющим входом и выходом детектора 7.

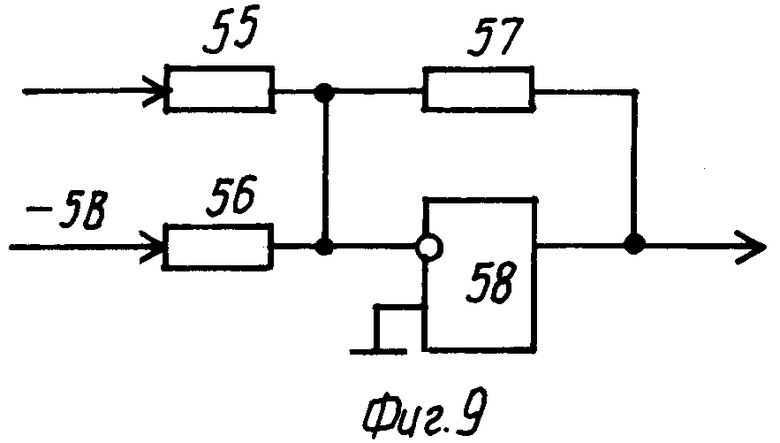

Инвертор 9 (фиг.9) содержит три резистора 55-57 и операционный усилитель 58. Вход инвертора 9 соединен с выводом резистора 55, другой вывод которого соединен с первыми выводами резисторов 56 и 57 и инверсным входом операционного усилителя 58, прямой вход которого соединен с общим проводом, а выход с вторым выводом резистора 57 и выходом инвертора 9; при этом второй вывод резистора 56 соединен с проводом отрицательного напряжения питания.

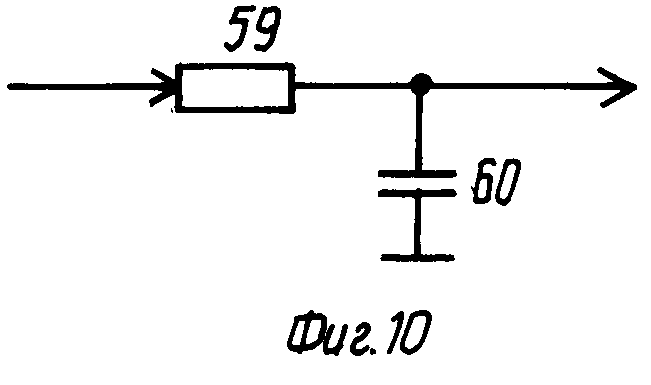

Фильтр 11 нижних частот (фиг.10) содержит резистор 59 и конденсатор 60. Вход фильтра 11 нижних частот соединен с выводом резистора 59, а выход с другим выводом резистора 59 и выводом конденсатора 60, другой вывод которого соединен с общим проводом.

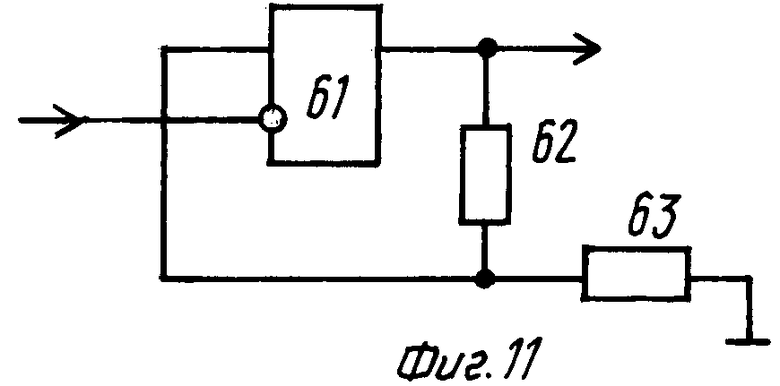

Пороговый компаратор 12 (фиг.11) содержит компаратор 61 и два резистора 62 и 63. Вход порогового компаратора 12 соединен с инверсным входом компаратора 61, а выход с выходом компаратора 61 и выводом резистора 62, другой вывод которого соединен с прямым входом компаратора 61 и выводом резистора 63, другой вывод которого соединен с общим проводом.

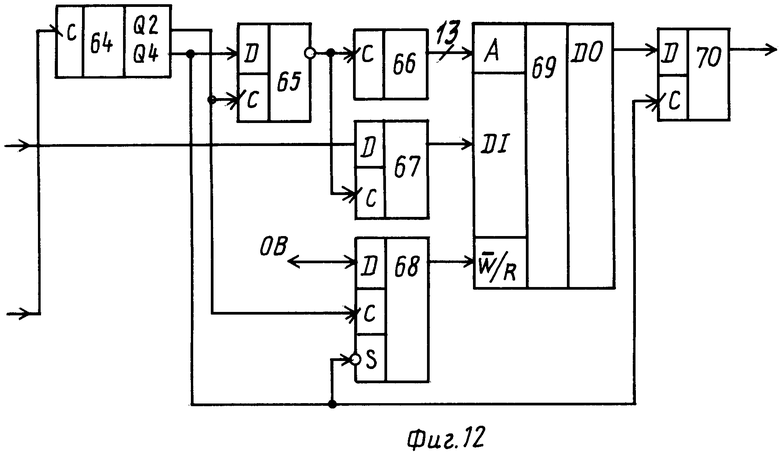

Элемент 14 задержки сигнала (фиг.12) содержит счетчик 64, D-триггер 65, счетчик 66, D-триггер 67, D-триггер 68, оперативное запоминающее устройство (ОЗУ) 69 и D-триггер 70.

Тактовый вход элемента 14 задержки сигнала соединен с входом С счетчика 64, а сигнальный вход с входом D D-триггера 67, вход С которого соединен с входом С счетчика 66 и инверсным выходом D-триггера 65, вход С которого соединен с выходом Q 2 cчетчика 64 и входом С D-триггера 68, а вход D с выходом Q4 cчетчика 64, входом С D-триггера 70 и входом S D-триггера 68, вход D которого соединен с общим проводом, а выход с входом  /R ОЗУ 69, вход D1 которого соединен с выходом D-триггера 67, адресная шина А с выходной шиной счетчика 66, а выход D0 с входом D D-триггера 70, выход которого соединен с выходом элемента 14 задержки сигнала.

/R ОЗУ 69, вход D1 которого соединен с выходом D-триггера 67, адресная шина А с выходной шиной счетчика 66, а выход D0 с входом D D-триггера 70, выход которого соединен с выходом элемента 14 задержки сигнала.

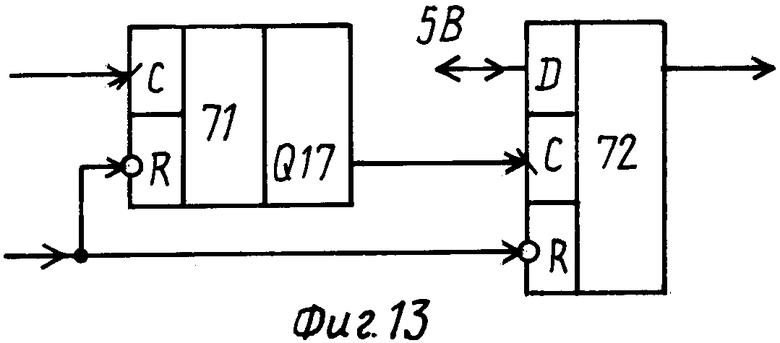

Элемент 15 задержки фронта (фиг.13) содержит счетчик 71 и D-триггер 72. Тактовый вход элемента 15 задержки фронта соединен с входом С счетчика 71, а сигнальный вход с входом R счетчика 71 и входом R D-триггера 72, вход С которого соединен с выходом Q17 cчетчика 71, вход D с проводом положительного напряжения питания, а выход с выходом элемента 15 задержки фронта.

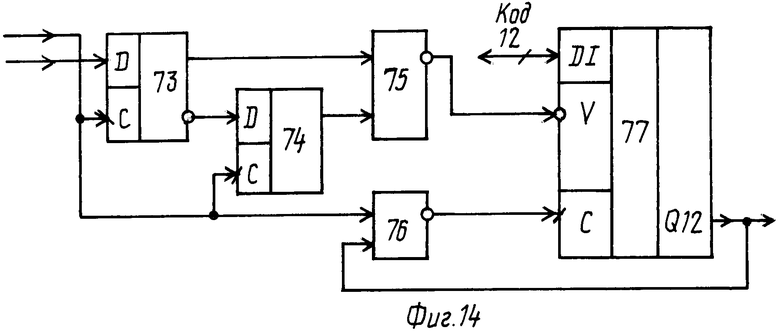

Формирователь 16 длительности (фиг.14) содержит два D-триггера 73 и 74, два элемента 75 и 76 2И-НЕ и счетчик 77. Сигнальный вход формирователя 16 длительности соединен с входом D D-триггера 73, а тактовый вход с первым входом элемента 76 2И-НЕ, входами С D-триггера 74 и D-триггера 73, инверсный выход которого соединен с входом D D-триггера 74, а прямой выход с первым входом элемента 75 2И-НЕ, второй вход которого соединен с прямым выходом D-триггера 74, а выход с входом V счетчика 77, входная шина D1 которого соединена поразрядно с общим проводом или проводом положительного напряжения питания согласно установленному коду, вход С с выходом элемента 76 2И-НЕ, а выход Q12 с вторым входом элемента 76 2И-НЕ и выходом формирователя 16 длительности.

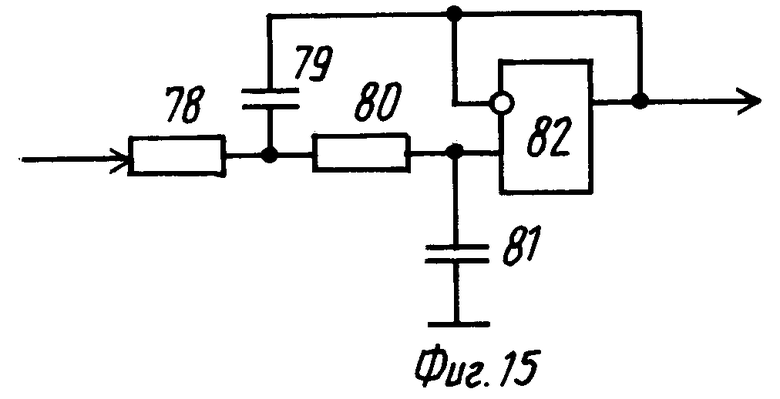

Фильтр 18 нижних частот (фиг.15) содержит резистор 78, конденсатор 79, резистор 80, конденсатор 81 и операционный усилитель 82. Вход фильтра 18 нижних частот соединен с выводом резистора 78, другой вывод которого соединен с первым выводом резистора 80 и выводом конденсатора 79, другой вывод которого соединен с выходом фильтра 18 нижних частот и с инверсным входом и выходом операционного усилителя 82, прямой вход которого соединен с вторым выводом резистора 80 и выводом конденсатора 81, другой вывод которого соединен с общим проводом.

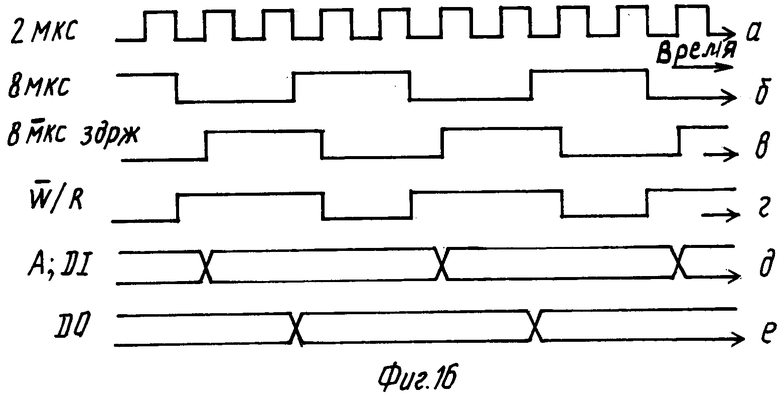

Частотомер работает следующим образом. Допплеровский сигнал Х(t) (фиг. 17, б), который представляет собой чередование шума и смеси шума с полезным синусоидальным сигналом допплеровской частоты, поступает на первый вход частотомера в промежутки времени, обозначенные на фиг.17, а. Усиленный до необходимой величины усилителя 3 сигнал Х(t) поступает на вход нуль-компаратора 4, на выходе которого образуется импульсный сигнал (фиг.17,д) с импульсными помехами, вызванными действием шума. Импульсный сигнал поступает на сигнальный вход селектора 6 скважности, который работает в качестве подавителя помех в импульсном сигнале. Введение селектора 6 скважности в структурную схему частотомера сделано с целью повышения чувствительности измерений частоты допплеровского сигнала в широком диапазоне частот. Импульсный сигнал допплеровской частоты, очищенный от помех (фиг.17,е), или же с частотой, достигающей верхнего предела рабочего диапазона частот, в случае действия только шума (фиг. 17,е), поступает на сигнальный вход элемента 14 задержки сигнала, который задерживает импульсный сигнал на необходимое время τ1 (фиг. 17,з). Для понимания работы элемента 14 задержки сигнала (фиг.12) служат временные диаграммы (фиг.16); при этом на фиг.16, а изображен сигнал "2 мкс" с периодом 2 мкс на выходе Q2 cчетчика 64, на фиг. 16, б cигнал "8 мкс" с периодом 8 мкс на выходе Q4 счетчика 64, на фиг.16, в выходной сигнал D триггера 65 "8 мкс здрж" с периодом 8 мкс, на фиг.16, г сигнал  /R управления режимами записи и чтения ОЗУ 69, на фиг.16, д моменты смены адреса и данных на входе ОЗУ 69, на фиг.16, е моменты обновления выходных данных.

/R управления режимами записи и чтения ОЗУ 69, на фиг.16, д моменты смены адреса и данных на входе ОЗУ 69, на фиг.16, е моменты обновления выходных данных.

Задержанный импульсный сигнал поступает на сигнальный вход формирователя 16 длительности, который заменяет положительные неопределенные по длительности импульсы входного сигнала на положительные импульсы установленной и неизменной длительности выходного сигнала Kи. Сигнал Kи поступает на вход 5 мультиплексора 17.

Детектор 7 осуществляет двухполупериодное детектирование сигнала, поступающего на его сигнальный вход с выхода усилителя 3, с помощью импульсного сигнала, поступающего на его управляющий вход с выхода нуль-компаратора 4. Полученный сигнал инвертируется и смещается по уровню на величину Uсм инвертором 9. Выпрямленный фильтром 11 нижних частот сигнал изменяется, как показано на фиг. 17, в; пунктирной линией обозначено изменение сигнала для случая большого по величине времени усреднения τБ фильтра 11 нижних частот. Пороговый компаратор 12 гистерезисного типа формирует сигнал Кр (фиг.17,г); пунктирной линией обозначено изменение сигнала Кр для случая большого по величине времени усреднения τБ фильтра 11 нижних частот. Зона гистерезиса, определяемая напряжениями Uвыкл, Uвкл, устраняет произвольное переключение сигнала Kрпри постоянной амплитуде допплеровского сигнала на входе частотомера, которое может быть вызвано недостаточной степенью фильтрации. Для уменьшения времени выключения τвыкл.1 и достижения его независимости от амплитуды сигнала Х(t) (фиг.17,б), время усреднения фильтра 11 нижних частот снижается до величины τм (фиг.17, в) в (30-100) раз по сравнению с величиной τБ за счет шунтирования резистора 59 (фиг.10) фильтра 11 нижних частот резистором 10, когда выходное напряжение фильтра 11 нижних частот становится меньше ОВ; сравнение производит нуль-компаратор 5, который управляет переключением ключа 8.

Элемент 15 задержки фронта задерживает момент включения сигнала Крздрж по сравнению с сигналом Кр на время τ1 (фиг.17,к). Тактовый сигнал Хт, необходимый для работы селектора 6 скважности, элемента 14 задержки сигнала, элемента 15 задержки фронта и формирователя 16 длительности, поступает на второй вход частотомера.

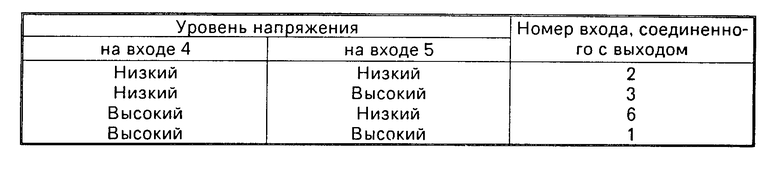

Работа мультиплексора 17 поясняется с помощью таблицы.

На сигнальные входы 2,3,6 мультиплексора 17 поступает напряжение ОВ, а на сигнальный вход 1 стабилизированное постоянное положительное напряжение от источника 13 опорного напряжения. При высоком уровне напряжения сигнала Крздрж сигнал Kи допплеровской частоты создает на выходе мультиплексора 17 импульсный сигнал допплеровской частоты, стабилизированный по амплитуде и длительности.

Фильтр 18 нижних частот выделяет постоянную составляющую Uвыхимпульсного сигнала (фиг. 17, л), которая поступает на выходную шину 19 частотомера. Напряжение Uвых пропорционально допплеровской частоте.

В случае, если сигнал Kрздрж постоянно имеет высокий уровень напряжения и отсутствует задержка импульсного сигнала (фиг. 17, е), выходное напряжение частотомера изменяется, как показано пунктирной линией на фиг.17, ж, достигая максимального значения во время действия только шума на входе частотомера (фиг.17, б), что вызвано высокой частотой импульсного сигнала (фиг. 17, е).

В случае, если отсутствуют задержка импульсного сигнала и задержка фронта сигнала Кр, т.е. на вход формирователя 16 длительности поступает импульсный сигнал (фиг. 17, е), а на вход 4 мультиплексора 17 сигнал Кр (сплошная линия на фиг. 17, г), то выходное напряжение частотомера изменяется, как показано сплошной линией на фиг.17, ж. Выброс (фиг.17, ж) возникает при условии, что время выключения τвыкл2, определяемое временем усреднения фильтра 11 нижних частот, сопоставимо или превышает время усреднения фильтра 18 нижних частот.

В случае, если отсутствует задержка фронта сигнала Кр, т.е. на вход 4 мультиплексора 17 поступает сигнал Кр (сплошная линия на фиг.17, г), выходное напряжение частотомера изменяется, как показано на фиг.17, и; выброс возникает при включении сигнала Кр (фиг.17, г, 17, з, 17, и).

Из изложенного следует, что для повышения чувствительности частотомера приняты следующие меры:

1) c целью повышения точности измерений частоты на пороге чувствительности в широком диапазоне частот используется селекция импульсного сигнала по скважности;

2) с целью получения однозначного показания частотомера при постоянной частоте и амплитуде входного допплеровского сигнала в условиях действия шума и остатков фильтрации, для формирования сигнала Кр применен двухпороговый гистерезисный режим сравнения (фиг.17,в) напряжения Uвыкл, Uвкл;

3) с целью получения независимости разности напряжений Uвыкл, Uвклот величины напряжения шума на входе частотомера, установлена ручным регулированием коэффициента усиления усилителя заданная величина напряжения шума на входе детектора, а также постоянный порог включения (выключения) Uсм (фиг.17,в) для заданного отношения сигнал/шум;

4) с целью устранения выбросов выходного сигнала частотомера, обеспечена практическая независимость времени выключения τвыкл2 (фиг.1,7 г) от напряжения входного допплеровского сигнала путем применения двух автоматически переключаемых при напряжении Uвкл (ОВ) значений времени усреднения τм и τБ (фиг. 17, в) первого фильтра нижних частот, а также введена задержка импульсного сигнала допплеровской частоты и фронта сигнала Кр на время τ1 (фиг. 17, з, 17, к).

Для исключения выброса выходного напряжения частотомера необходимо, чтобы время задержки τ1 превышало наибольшее значение времени выключения τвыкл2.

Исследование макета частотомера, работающего с тактовой частотой 2 МГц, в диапазоне частот допплеровского сигнала от 100 Гц до 10 кГц при отношении сигнал/шум не более 2 подтвердило достижение цели изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1982 |

|

SU1119050A1 |

| Аналого-цифровой частотомер | 1988 |

|

SU1712894A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| Устройство для отображения телетекста на экране телевизионного приемника | 1980 |

|

SU1181568A3 |

| СПОСОБ КОНТРОЛЯ КОНТАКТИРОВАНИЯ КМОП-БИС И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2009518C1 |

| Дуплексная система телемеханики по проводам электрической сети | 1988 |

|

SU1540015A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ С АВТОНОМНЫМ ИНДУКТОРОМ | 2005 |

|

RU2291548C1 |

| Устройство для передачи и приема двух сигналов по одному проводу | 1989 |

|

SU1741281A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

Использование: для измерения частоты доплеровского сигнала со свойственным ему непрерывным изменением в широких пределах по частоте и амплитуде в условиях действия шума с представлением результатов в виде напряжения, пропорционального частоте. Сущность изобретения: частотомер содержит две выходные шины 1 и 2, усилитель 3, два нуль-компаратора 4 и 5, селектор скважности 6, детектор 7, ключ 8, инвертор 9, резистор 10, фильтр нижних частот 11, пороговый компаратор 12, источник опорного напряжения 13, элемент задержки сигнала 14, элемент задержки фронта 15, формирователь длительности 16, мультиплексор 17, фильтр нижних частот 18 и выходную шину 19. 17 ил. 1 табл.

ДОППЛЕРОВСКИЙ ЧАСТОТОМЕР, содержащий две входные шины, детектор, нуль-компаратор, вход которого соединен с сигнальным входом детектора, первый фильтр нижних частот, пороговый компаратор, вход которого соединен с выходом первого фильтра нижних частот, формирователь длительности, тактовый вход которого соединен с второй входной шиной, источник опорного напряжения, мультиплексор, первый и второй входы которого соединены соответственно с первым и вторым выходами источника опорного напряжения, а пятый вход с выходом формирователя длительности, второй фильтр нижних частот, выход которого является выходом частотомера, а вход соединен с выходом мультиплексора, отличающийся тем, что, с целью повышения чувствительности измерений частоты допплеровского сигнала в широком диапазоне частот, в него введены усилитель, второй нуль-компаратор, селектор скважности, ключ, инвертор, резистор, элемент задержки сигнала и элемент задержки фронта, при этом первая входная шина соединена с входом усилителя, выход которого соединен с входом первого нуль-компаратора, выход которого соединен с сигнальным входом селектора скважности и управляющим входом детектора, выход которого соединен с входом инвертора, выход которого соединен с входом первого фильтра нижних частот и с сигнальным входом ключа, управляющий вход которого соединен с выходом второго нуль-компаратора, а выход с выводом резистора, другой вывод которого соединен с входом второго нуль-компаратора и с входом порогового компаратора, выход которого соединен с сигнальным входом элемента задержки фронта, выход которого соединен с четвертым входом мультиплексора, а тактовый вход с тактовыми входами селектора скважности, элемента задержки сигнала и формирователя длительности, сигнальный вход которого соединен с выходом элемента задержки сигнала, сигнальный вход которого соединен с выходом селектора скважности, а третий и шестой входы мультиплексора соединены с вторым входом мультиплексора.

| Ультразвуковой допплеровский измеритель скорости кровотока | 1984 |

|

SU1215659A1 |

| Устройство для сортировки каменного угля | 1921 |

|

SU61A1 |

Авторы

Даты

1995-11-10—Публикация

1993-06-16—Подача