ND

СЛ СП

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсно-фазовый детектор | 1986 |

|

SU1437963A1 |

| Импульсно-фазовый детектор | 1988 |

|

SU1518872A2 |

| Измеритель нелинейности импульсовпилООбРАзНОгО НАпРяжЕНия | 1979 |

|

SU805207A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU841057A1 |

| Импульсно-фазовый детектор | 1982 |

|

SU1113874A1 |

| Аппаратура акустического каротажа нефтяных и газовых скважин | 1976 |

|

SU652517A1 |

| Синтезатор частот | 1987 |

|

SU1555862A1 |

| Фазовый детектор | 1988 |

|

SU1688377A1 |

| УСТРОЙСТВО ТЕПЛОВОЙ ЗАЩИТЫ ЭЛЕКТРОДВИГАТЕЛЯ | 2012 |

|

RU2498472C1 |

| Устройство для задержки выключения ламп освещения | 1982 |

|

SU1088156A1 |

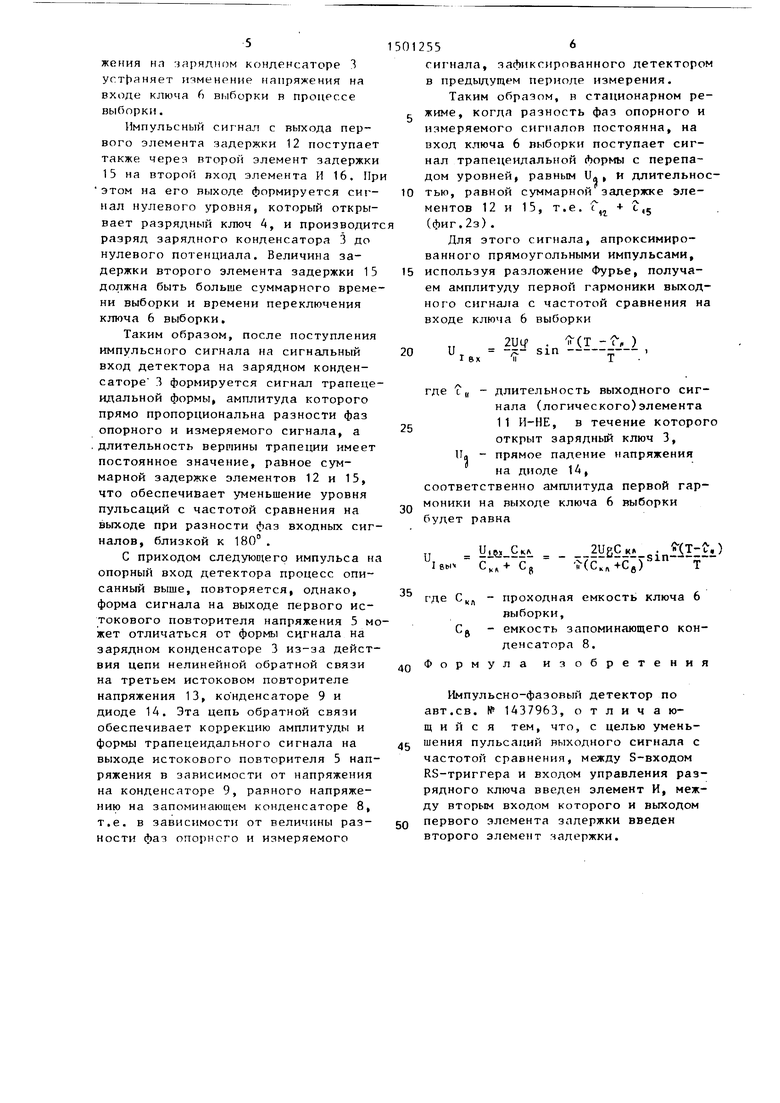

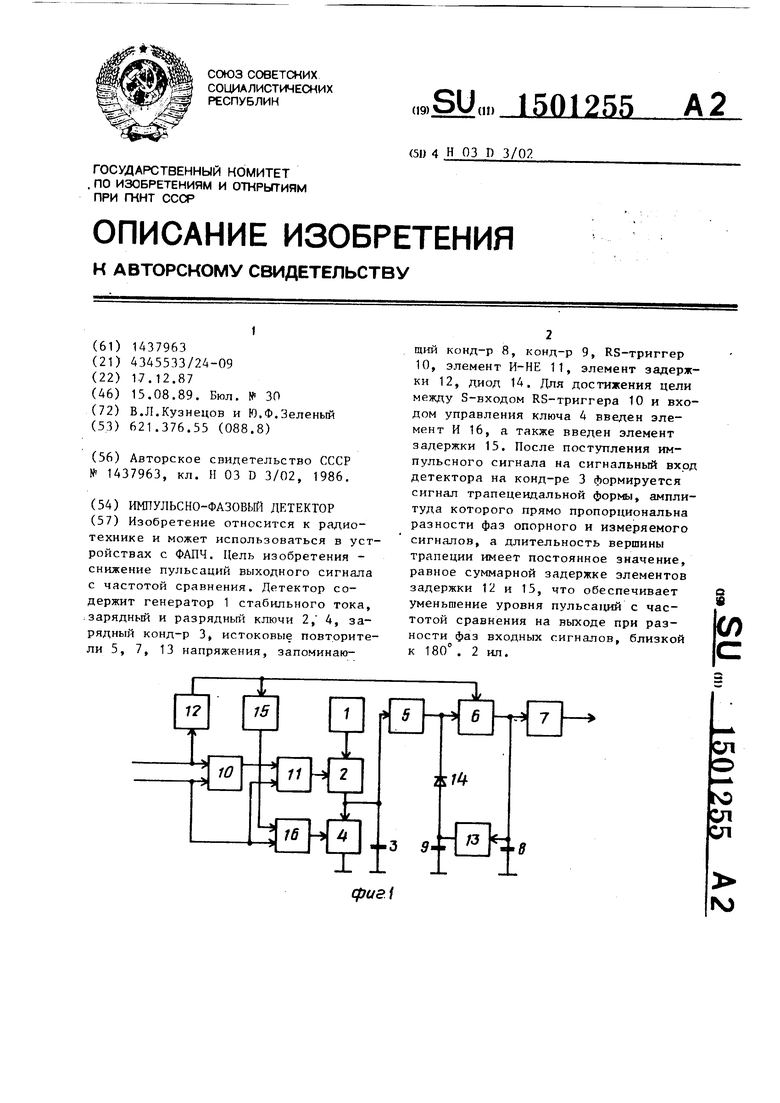

Изобретение относится к радиотехнике и может использоваться в устройствах с ФАПЧ. Цель изобретения - снижение пульсаций выходного сигнала с частотой сравнения. Детектор содержит генератор 1 стабильного тока, зарядный и разрядный ключи 2, 4 зарядный конд-р 3, истоковые повторители 5, 7, 13 напряжения, запоминающий конд-р 8, конд-9, RS-триггер 10, элемент И-НЕ 11, элемент задержки 12, диод 14. Для достижения цели между входом триггера 10 и входом управления ключа 4 введен элемент И 16, а также введен элемент задержки 15. После поступления импульсного сигнала на сигнальный вход детектора на конд-ре 3 формируется сигнал трапецеидальной формы, амплитуда которого прямо пропорциональна разности фаз опорного и измеряемого сигналов, а длительность вершины трапеции имеет постоянное значение, равное суммарной задержке элементов задержки 12 и 15, что обеспечивает уменьшение уровня пульсаций с частотой сравнения на выходе при разности фаз входных сигналов, близкой к 180°. 2 ил.

сриг

N)

3130

Изобретение относится к радиотехнике и может использоваться в устройствах с фпзовой автоподстрой- кой частоты.

Цель изобретения - снижение пульсаций выходного сигнала с частотой сравнения.

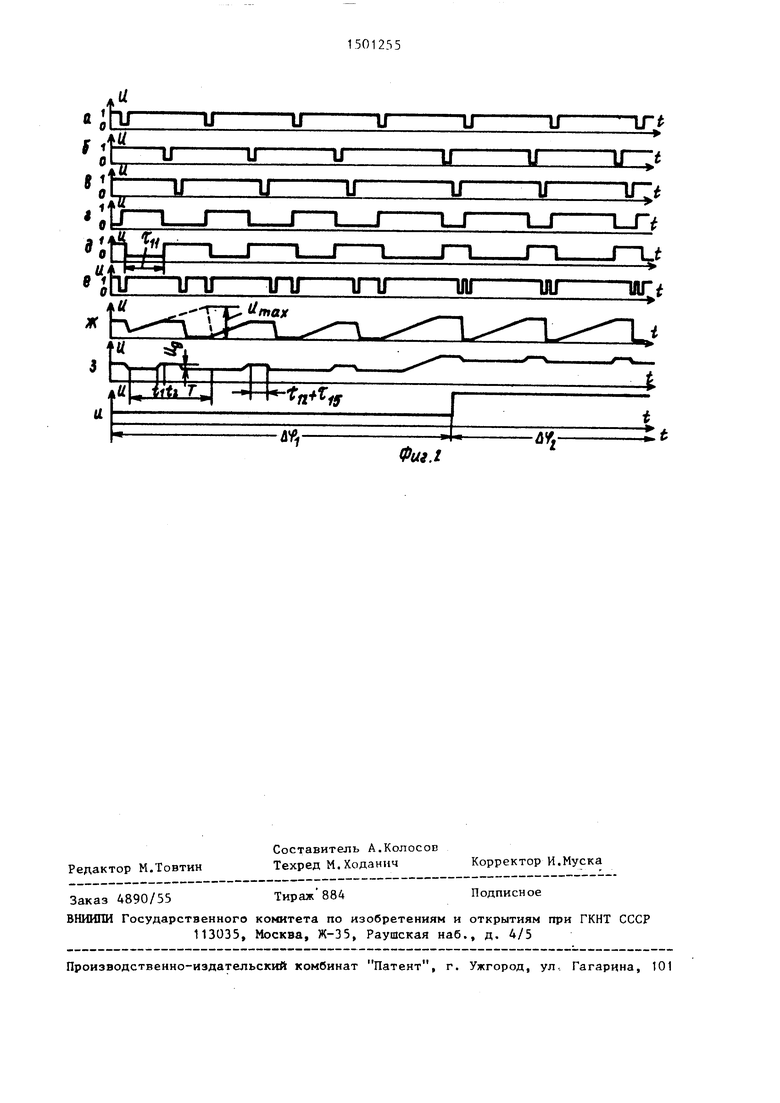

На Лиг.1 приведена структурная электрическая схема импульсно-фазо- вого детектора; на Лиг.2 - временные диаграммы его работы,

Импульсно-фазовый детектор содержит генератор 1 стабильного тока, зарядный ключ 2, зарядный конденса- тор 3, разрядный ключ 4, первый ис- токовый повторитель напряжения 5, ключ 6 выборки, второй истоковый повторитель напряжения 7, запоминающий конденсатор 8, конденсатор 9, RS-триггер 10, элемент И-НЕ 11, первый элемент задержки 12, третий истоковый повторитель напряжения 13, диод 14, второй элемент задержки 15, элемент И 16.

Импульсно-фазовый детектор работает следующим образом.

При поступлении импульсного сигнала })иг.2а, с уровнем логического нуля на опорный вход детектора RS- триггер 10 устанавливается в единичное состояние фиг.2г, а разрядный ключ 4 открывается, обеспечивая разряд зарядного конденсатора 3 до нулевого потенциала фиг,2ж. В течение времени действия импульса на опорном входе детектора на выходе элемента И-НЕ 11 формируется сигнал единичного уровня (})иг.2д, который поступает на вход управления зарядного ключа 2 и закрывает его. После окончания действия входного импульса опорного сигнала на выходе элемента И-НЕ 11 формируется сигнал логическо го нуля, который открывает зарядный ключ 2, одновременно с этим на выходе элемента И 16 формируется сигнал фиг.2е.логической единицы, который закрывает разрядный ключ 4. Чере открытый зарядньш ключ 2 зарядный конденсатор 3 заряжается от генератора 1 стабильного тока, В результате заряда стабильным током на зарядном конденсаторе 3 формируется на- растающее линейное пилообразное напряжение фиг.2ж, максимальное значени которого соответствует разности фаз входных сигналов, равной bcf 360.

5

0 с О 5

0

При поступлении импульса фиг.2б с уровнем логического нуля на сигнальный вход импульсно-фазового детектора RS-триггер 10 устанавливается в нулевое состояние, на выходе элемента И-М1 1 1 формируется сигн.ял с уровнем логической единицы, который закрывает зарядный ключ 2. При этом разрядный ключ А также находится в закрытом состоянии. Закрытое состояние обоих ключей обеспечивает фиксацию на зарядном конденсаторе 3 постоянного напряжения фиг.2ж, равного по величине пилообразному сигналу в момент прихода импульса на сигнальный вход импульсно-Лазового детектора.

Таким образом, при поступлении импульсного сигнала на сигнальный вход детектора, на зарядном конденсаторе 3 вместо пилообразного формируется сигнал трапецеидальной формы, амплитуда которого прямо пропорциональна разности фаз опорного и измеряемого сигналов.

Постоянное напряжение, зафиксированное на зарядном конденсаторе 3, через первый истоковый повторитель напряжения 5 фиг.2в поступает на вход ключа 6 выборки. На вход управления ключа 6 выборки через первый элемент 12 задержки подается импульсный сигнал фиг.2в, поступивший на сигнальный вход детектора. Этот сигнал открывает ключ 6 выборки и через первый истоковый повторитель напряжения 5 происходит заряд запоминающего конденсатора 8 до напряжения фиксации зарядного конденсатора 3. Сигнал в виде постоянного напряжения фиг,2и на запоминающем конденсаторе 8 через второй истоковьш повторитель напряжения 7 поступает, на выход устройства. Одновременно с зарядом запоминающего конденсатора 8 через третий истоковый повторитель 13 напряжения происходит заряд конденсатора 9 также до напряжения фиксации зарядного конденсатора 3. Первый элемент задержки 12 обеспечивает открытие ключа 6 выборки после окончания изменения напряжения на зарядном конденсаторе 3, Величина задержки первого элемента задержки 12 должна быть больше суммарного времени переключения RS-триггера 10 и зарядного ключа 2. Введение задержки выборки совместно с фиксацией напря5

жения нл зарядном конленсаторе 3 угт 1аняет изменение напряжения на входе ключа (ч В1,1борки в процессе выборки.

Импульсный сигнал с выхода первого элемента задержки 12 поступает также через второй элемент задержки 15 на второй вход элемента И 16, Пр этом на его выходе формируется сиг- нал нулевого уровня, который открывает разрядный ключ А, и производит разряд зарядного конденсатора 3 до нулевого потенциала. Величина задержки второго элемента задержки 15 должна быть больше суммарного времени выборки и времени переключения ключа 6 выборки.

Таким образом, после поступления импульсного сигнала на сигнальный вход детектора на зарядном конденсаторе 3 формируется сигнал трапецеидальной формы, амплитуда которого прямо пропорциональна разности фаз опорного и измеряемого сигнала, а длительность верпины трапеции имеет постоянное значение, равное суммарной задержке элементов 12 и 15, что обеспечивает уменьшение уровня пульсаций с частотой сравнения на выходе при разности фаз входных сигналов, близкой к 180° .

С приходом следуюп1его импульса н опорный вход детектора процесс описанный выше, повторяется, однако, форма сигнала на выходе первого ис- токового повторителя напряжения 5 может отличаться от формы сигнала на зарядном конденсаторе 3 из-за действия цепи нелинейной обратной связи на третьем истоковом повторителе напряжения 13, ко нденсаторе 9 и диоде 14. Эта цепь обратной связи обеспечивает коррекцию амплитуды и формы трапецеидального сигнала на выходе истокового повторителя 5 напряжения в зависимости от напряжения на конденсаторе 9, равного напряжению на запоминающем конденсаторе 8, т.е. в зависимости от величины раз- ности фаз опорного и измеряемого

556

сигнала, зафиксированного детектором в предыдущем периоде измерения.

Таким образом, в стационарном реиме, когда разность фаз опорного и измеряемого сигналов постоянна, на вход ключа 6 выборки поступает сигнал трапецеидальной Формы с перепаом уровней, равным U, н длительностью, равной суммарной задержке элементов 12 и 15, т.е. Г, (фиг.2з),

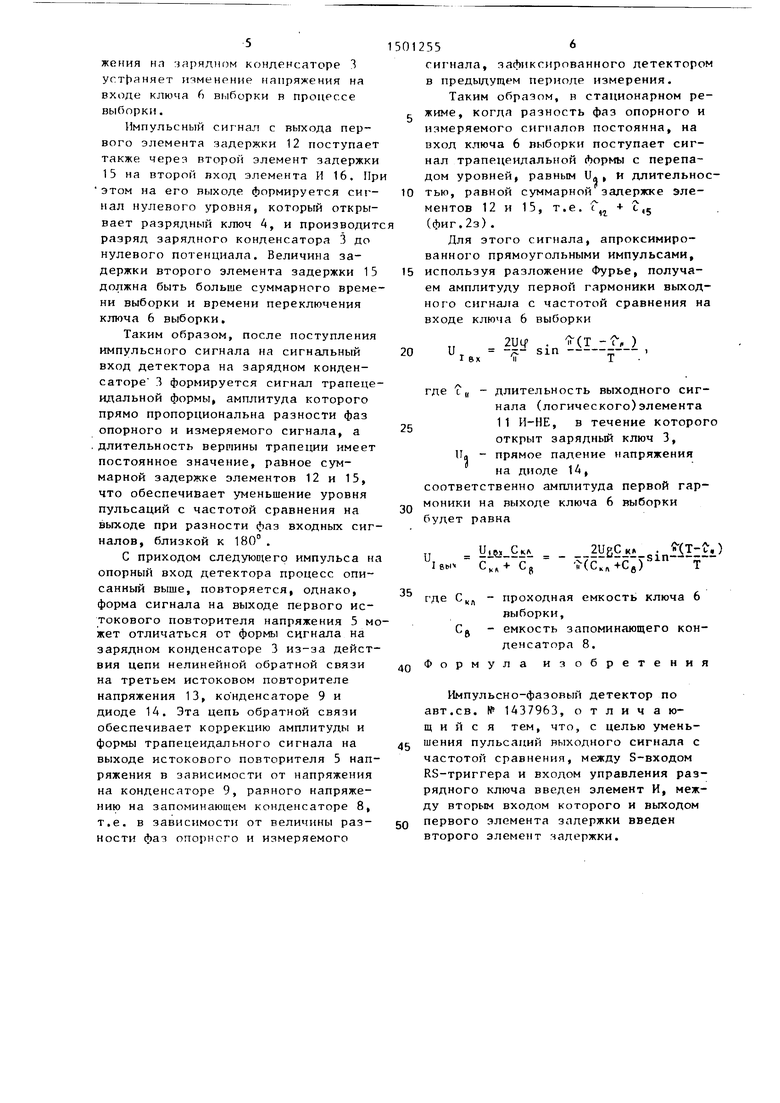

Для этого сигнала, апроксимиро- ванного прямоугольными импульсами, используя разложение Фурье, получаем амплитуду первой гармоники выходного сигнала с частотой сравнения на входе ключа 6 выборки

2U4 . (Т -1, )

и -я- sin.

I ex IIт

где с,, - длительность выходного сигнала (логического)элемента 11 И-НЕ, в течение которого открыт зарядный ключ 3, Но - прямое падение напряжения

на диоде 1А,

соответственно амплитуда первой гароники на выходе ключа 6 выборки удет равна

- Уш С 12ysC K« . f(T;2i)

Ск.-ь

(c.л+c.)

sinгде - проходная емкость ключа 6

выборки,

Cg - емкость запоминающего конденсатора 8. Формула изобретения

Импульсно-фазовый детектор по авт.св. № 1А37963, отличающийся тем, что, с целью уменьшения пульсаций выходного сигнала с частотой сравнения, между S-входом RS-триггера и входом управления разрядного ключа введен элемент И, между вторым входом которого и выходом первого элемента задержки введен второго элемент задержки.

и

ainr

u

u

f t

tu

и

.ЛГ

«:

JL

u

J

Tf/

Jl

u

IT

IL

IT

ЗТГЧ

ic;

ЗЦ

T-Tl

o,

Фаг.1

Авторы

Даты

1989-08-15—Публикация

1987-12-17—Подача