(54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1979 |

|

SU847374A1 |

| Аналоговое запоминающее устройство | 1975 |

|

SU543983A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| Усилитель заряда | 1983 |

|

SU1148003A1 |

| АМПЛИТУДНЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ПОСТОЯННОЕ | 2001 |

|

RU2190230C1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1042036A1 |

| Аналоговое запоминающее устройство | 1983 |

|

SU1104586A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД | 2001 |

|

RU2190229C1 |

| Аналоговое запоминающее устройство | 1983 |

|

SU1191943A1 |

| Логарифмический аналого-цифровой преобразователь | 1990 |

|

SU1725397A1 |

I

Изобретение относится к информационно-измерительной технике и может быть использовано для запоминания максимального значения импульсного сигнала с большим временем хранения.

Известно аналоговое запоминающее устройство (АЗУ), позволяющее запоминать максимальное значение импульсного сигнала и содержащее усилитель, диод, конденсатор 1.

Однако АЗУ имеет -недостаточную точность при работе в щироком динамическом диапазоне входных сигналов.

Наиболее близким по технической сущности к предлагаемому является АЗУ, которое содержит усилитель, ключи, истоковый повторитель, конденсаторы и компараторы, операционный усилитель, элемент И и RS-триггер 2.

Однако это устройство хорошо работает в широком динамическом диапазоне, но время хранения мало, за счет того, что после запоминания максимального значения сигнала падение напряжения на ключе велико и происходит большая утечка заряда с конденсатора во время хранения.

Цель изобретения - увеличение времени хранения устройства.

Поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее первый и второй накопительные элементы, конденсаторы, одни из обкладок которых соединены с шиной нулевого потенциала, другая обкладка первого конденсатора соединена с управляющим входом генератора тока и через первый ключ с выходом операционного усилителя, неинвертирующий вход которого подключен к одному из входов первого компаратора, к выходу устройства, к выходу истокового повторителя,к неиНВертирующему входу операционного усилителя, и через последовательно соединенные второй и третий ключи с вы.ходом

ycилитev я, вход усилителя соединен с другим входом первого компаратора и через элемент задержки со входом устройства, второй компаратор, один из входов которого соединен со входом устройства, а другой вход - с щиной ну,девого потенциала, RSтриггер, S-вход которого подключен к выходу второго компаратора. R-вход RS-триггера соединен с разрядной шиной, выход усилителя соединен со входом истокозого повторителя и с другой обкладкой второго конденсатора через последовательно соединенные третий и четвертый ключи, введены пятый ключ, элемент И, элемент ИЛИ и инвертор, выход которого соединен с управляющим входом второго ключа, вход инвертора подключен к выходу элемента ИЛИ и управляющему входу первого ключа, выход элемента И соединен с управляюiJiHM входом третьего ключа, первые входы элементов И и ИЛИ соединены с выходом первого компаратора, а вторые входы - с прямым и инверсным выходами RS-триггера, соответственно, инвертирующий вход операционного усилителя соединен с шиной нулевого потенциала через пятый ключ, управляющие входы первого и пятого ключей соединены с инверсным выходом RS-триггера, выход усилителя через третий соединен с инвертирующим входом операционного уси,жителя.

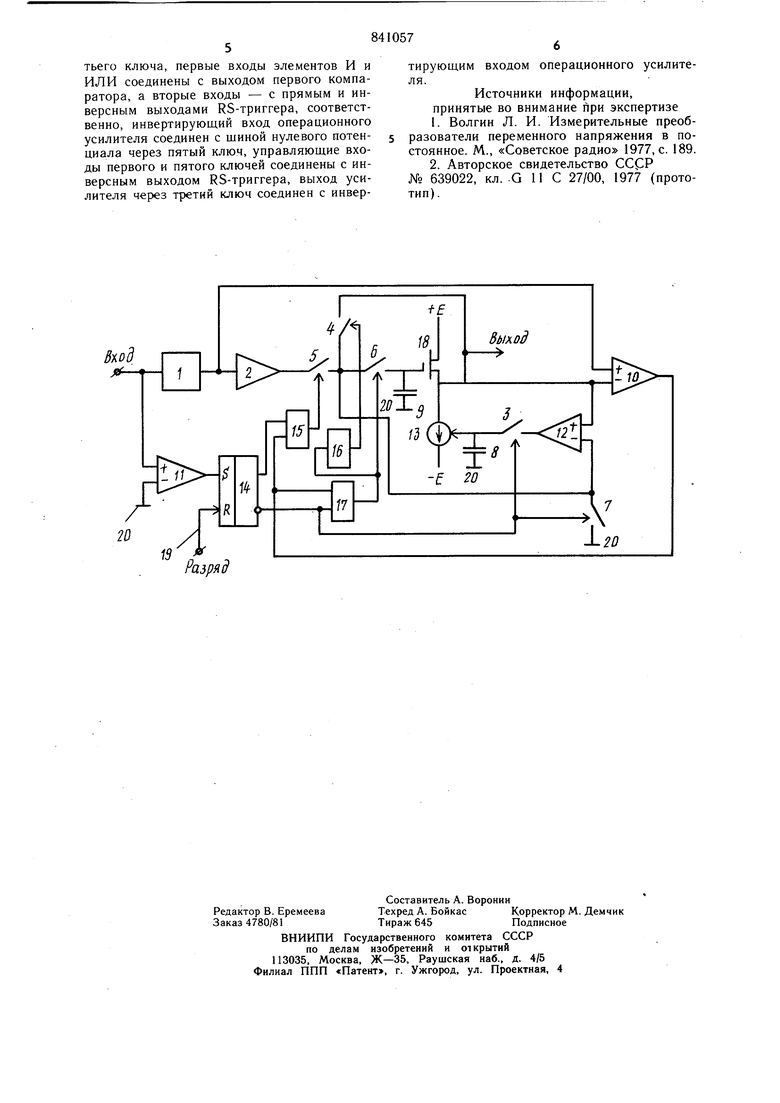

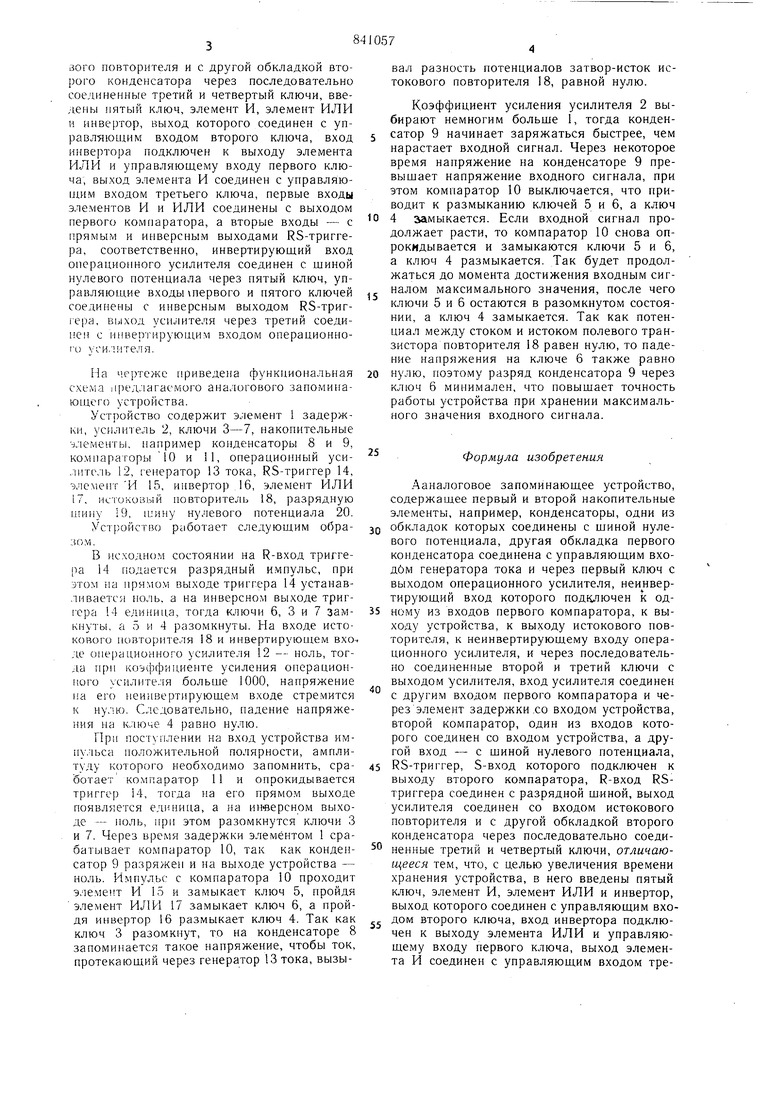

На чертеже приведена функциональная схема 1)ед-1агаемого аналогового запоминающего устройства.

Устройство содержит элемент 1 задержки, усилипель 2, ключи 3-7, накопительные элементы, например конденсаторы 8 и 9, компарагоры 10 и 11, операционный усилитель 12, генератор 13 тока, RS-триггер 14, элеме1гг И 15, инвертор 16, элемент ИЛИ 17. иссоковый повторитель 18, разрядную тину 19, нулевого потенциала 20.

Уст)ойство рг1ботает следующим образом.

В исходно.м состоянии на R-вход тригге ia 14 подается разрядный импульс, при этом на прямом выходе триггера 14 устанавливается ноль, а на инверсном выходе триггера 14 единица, тогда ключи 6, 3 и 7 замкнуты, а 5 и 4 разомкнуты. На входе истокового повторителя 18 и инвертируюп,ем вхо-, де онерационного усилителя 12 -- ноль, тогда при коэффициенте усиления онерационiioro усилителя больше 1000, напряжение па его неилвертирующе.м входе стремится к нулю. Следовательно, падение напряжения на к.пюче 4 равно нулю.

При поступлении на вход устройства импульса положительной полярности, амплитуду которого необходимо запомнить, сработает компаратор 11 и опрокидывается триггер 14, тогда на его прямом выходе появляется едшцща, а на ин-версном выходе - ноль, 1ри этом разомкнутся ключи 3 и 7. Через время задержки элементом 1 срабатывает компаратор 10, так как конденсатор 9 разряжен и на выходе устройства - ноль. Импульс с компаратора 10 проходит элемент И 15 и замыкает ключ 5, пройдя элемент ИЛИ 17 замыкает ключ 6, а пройдя инвертор 16 размыкает ключ 4. Так как ключ 3 разомкнут, то на конденсаторе 8 запоминается такое напряжение, чтобы ток, протекающий через генератор 13 тока, вызывал разность потенциалов затвор-исток истокового повторителя 18, равной нулю.

Коэффициент усиления усилителя 2 выбирают немногим больше 1, тогда конденсатор 9 начинает заряжаться быстрее, чем нарастает входной сигнал. Через некоторое время напряжение на конденсаторе 9 превыщает напряжение входного сигнала, при этом компаратор 10 выключается, что приводит к размыканию ключей 5 и 6, а ключ

0 4 замыкается. Если входной сигнал продолжает расти, то компаратор 10 снова опрокидывается и замыкаются ключи 5 и 6, а ключ 4 размыкается. Так будет продолжаться до момента достижения входным сигналом максимального значения, после чего ключи 5 и 6 остаются в разомкнутом состоянии, а ключ 4 замыкается. Так как потенциал между стоком и истоком полевого транзистора повторителя 18 равен нулю, то падение напряжения на ключе 6 также равно

нулю, поэтому разряд конденсатора 9 через ключ 6 минимален, что повышает точность работы устройства при хранении максимального значения входного сигнала.

Формула изобретения

Ааналоговое запоминающее устройство, содержащее первый и второй накопительные элементы, например, конденсаторы, одни из

обкладок которых соединены с шиной нулевого потенциала, другая обкладка первого коиденсатора соединена с управляющим входОм генератора тока и через первый ключ с выходом операционного усилителя, неинвертирующий вход которого подключен к одному из входов первого компаратора, к выходу устройства, к выходу истокового повторителя, к неинвертирующему входу операционного усилителя, и через последовательно соединенные второй и третий ключи с выходом усилителя, вход усилителя соединен с другим входом первого компаратора и через элемент задержки .со входом устройства, второй компаратор, один из входов которого соединен со входом устройства, а другой вход - с щиной нулевого потенциала,

5 RS-триггер, S-вход которого подключен к выходу второго компаратора, R-вход RSтриггера соединен с разрядной щиной, выход усилителя соединен со входом истокового повторителя и с другой обкладкой второго конденсатора через последовательно соединенные третий и четвертый ключи, отличающееся тем, что, с целью увеличения времени хранения устройства, в него введены пятый ключ, элемент И, элемент ИЛИ и инвертор, выход которого соединен с управляющим вхоJ дом второго ключа, вход инвертора подключен к выходу элемента ИЛИ и управляющему входу первого ключа, выход элемента И соединен с управляющим входом третьего ключа, первые входы элементов И и ИЛИ соединены с выходом первого компаратора, а вторые входы - с прямым и инверсным выходами RS-триггера, соответственно, инвертирующий вход операционного усилителя соединен с шиной нулевого потенциала через пятый ключ, управляющие входы первого и пятого ключей соединены с инверсным выходом RS-триггера, выход усилителя через третий ключ соединен с инверРазряд

тирующим входом операционного усилителя.

Источники информации, принятые во внимание при экспертизе

№ 639022, кл. .G 11 С 27/00, 1977 (прототип).

Авторы

Даты

1981-06-23—Публикация

1979-09-28—Подача