ел ел ел

00

о

ГС

л1

Изобретение относится к радиотехнике и может быть использовано в радиоприемниках и радиопередающих устройствах и в измерительной технике,

Целью изобретения является расширение диапазона формируемых частот и повышения спектральной чистоты.

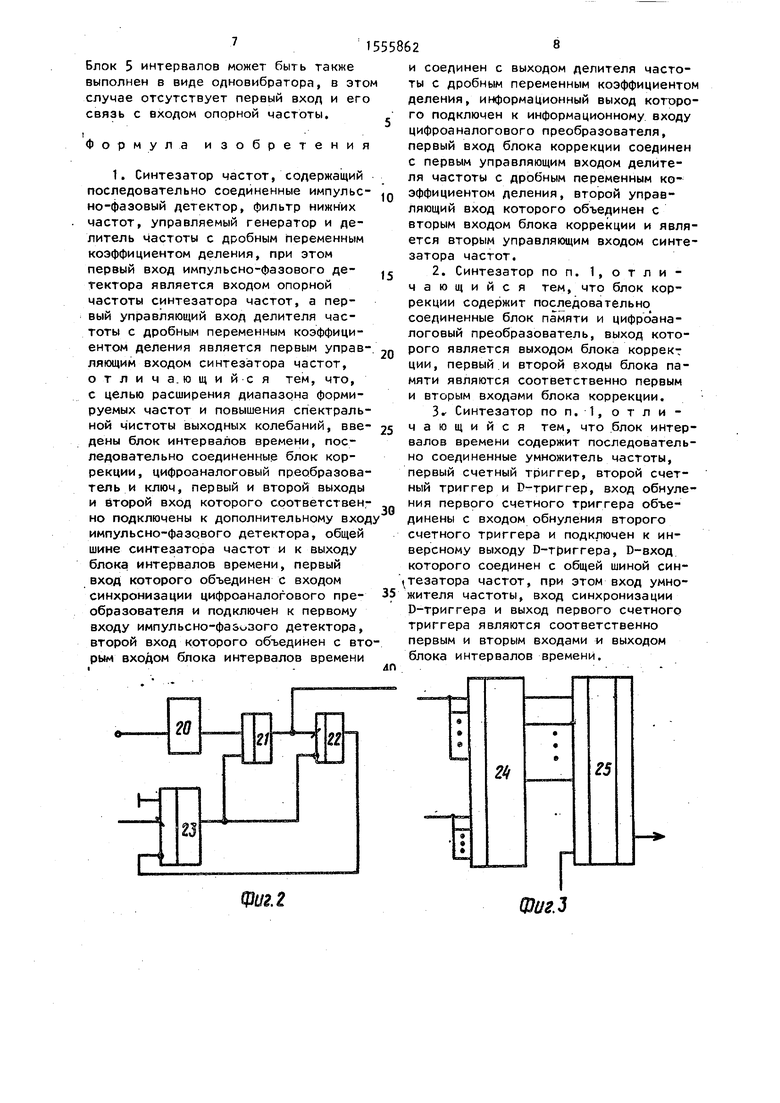

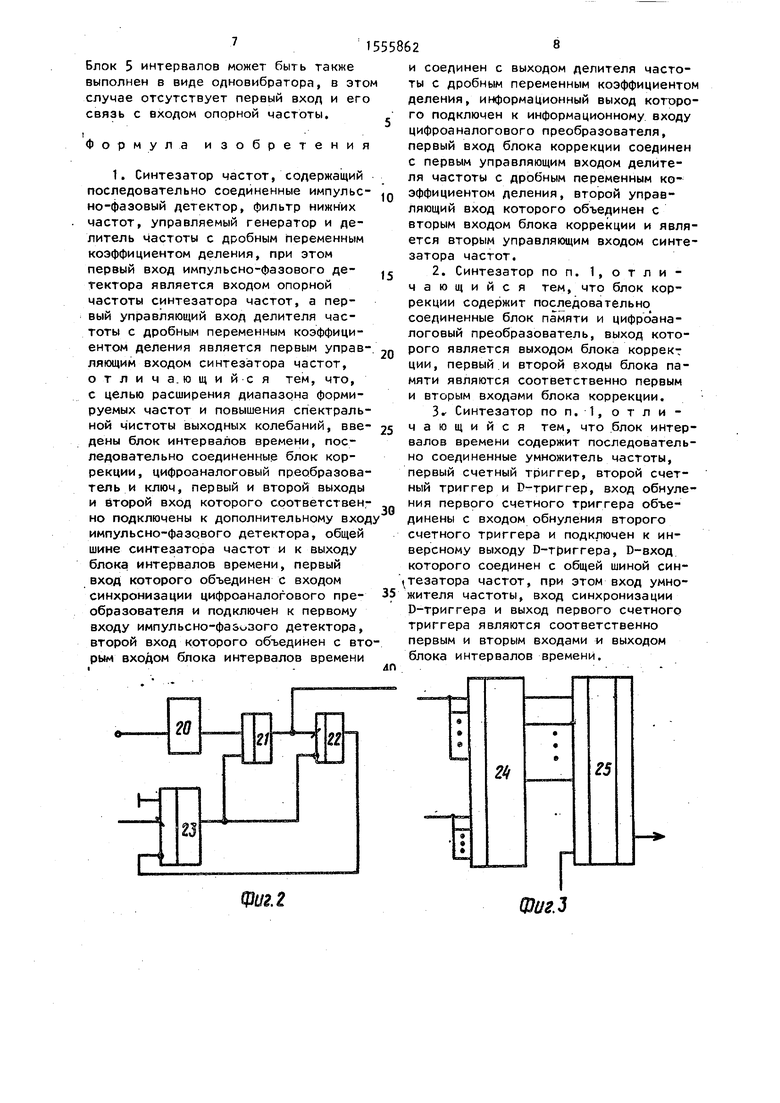

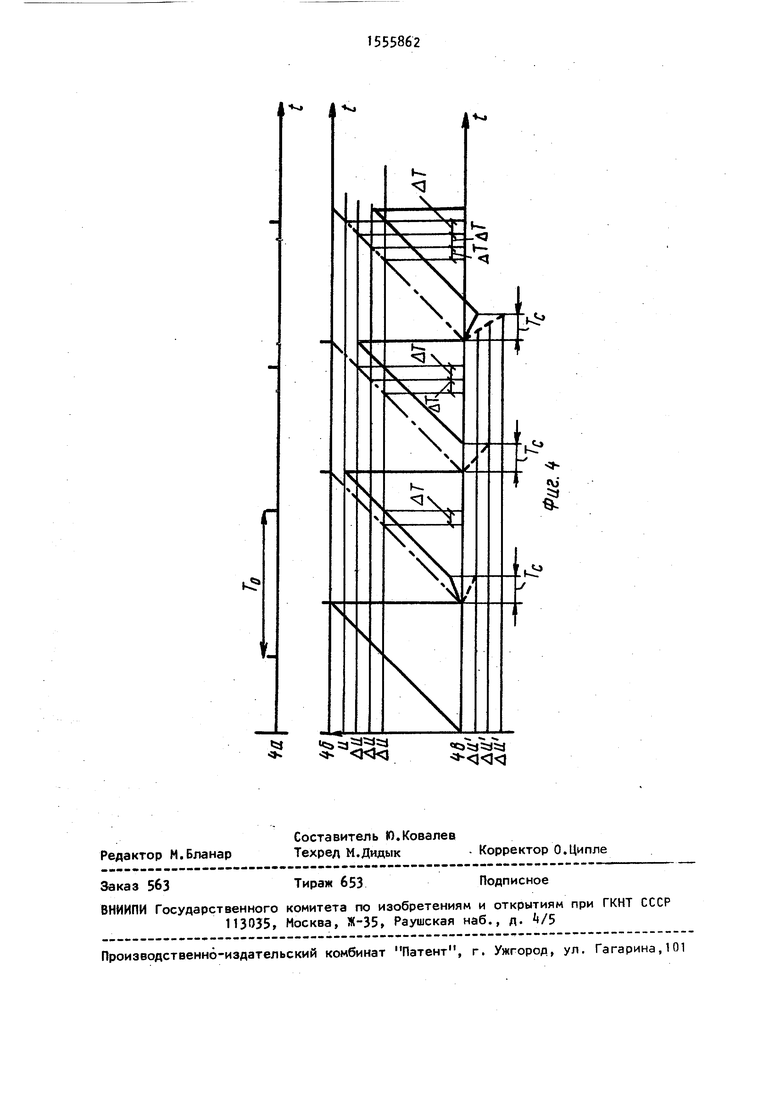

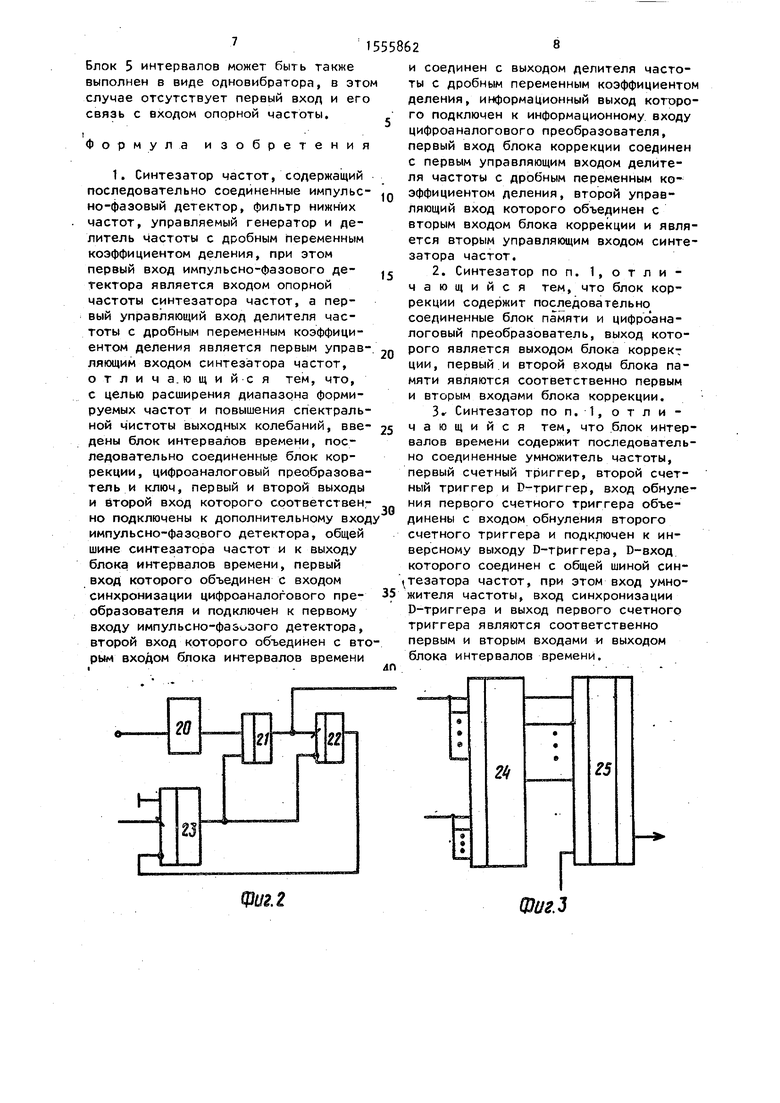

На фиг. 1 представлена структурна электрическая схема синтезатора час- тот; на фиг. 2 - блок интервалов времени; на фиг. 3 - блок коррекции; на фиг. k - временные диаграммы работы импульсно-фазового детектора.

Синтезатор частот содержит им- пульсно-фазовый детектор (ИФД) 1 фильтр 2 нижних частот, управляемый генератор 3, делитель 4 частоты с дробным переменным коэффициентом деления (ДДПКД), блок 5 интервалов времени, ключ 6, блок 7 коррекции, цифроаналоговый преобразователь (ЦАП 8. При этом ДДПКД k состоит из блока 9 исключения импульса, делителя 10 частоты, сумматора 11 кодов и регист ра 12 памяти. ИФД 1 содержит первый ключ 13, источник 14 тока, зарядный конденсатор 15, первый повторитель 16, второй ключ 17, запоминающий конденсатор 18, второй повторитель 19. Блок интервалов времени содержит умножитель 20 частоты, первый счетны триггер 21, второй счетный триггер 22, D-триггер 23. Блок коррекции содержит блок 24 памяти, ЦАП 25.

Синтезатор частот работает следующим образом.

В установившемся режиме на первом управляющем входе ДДПКД 4 присутствует S-разрядный код, где S - число разрядов сумматора 11, регистра 12, ЦАП 8; М - информационная емкость первого управляющего входа синтезатора частот.

Числовое значение кода равно X - дробной части сдвига частоты управляемого генератора 3. На втором управляющем входе ДДПКД k присутствует Н-разрядный код коэффициента деле

ния делителя 10, причем Н logjZ, где Z - максимальный коэффициент деления делителя 10. Числовое значение кода на втором управляющем входе ДДПКД 4 равно N. На фиг. 4а показаны импульсы на входе опорной частоты ИФД 1, на фиг. 4б показаны импульсы на выходе делителя 10, на фиг. 4в напряжение на зарядном конденсаторе 15. При этом сплошной линией (фиг. 4в

fпоказано суммарное напряжение на зарядном конденсаторе 15, создаваемо ЦАП 8 и источником 14 тока, штриховой линией - напряжение на зарядном конденсаторе 15,создаваемое ЦАП 8, штрихпунктирной линией напряжение на зарядном конденсаторе 15 от источника 14 тока. Таким образом, токи от источника 14 тока и ЦАП 8 имеют противоположную полярность. Сплошными горизонтальными линиями (фиг. 4в) показано напряжение на запоминающем конденсаторе 18.

Блок 5 интервалов формирует на выходе импульс длительностью Тс, разность AT между периодом опорного сигнала Т0 и периодом сигнала на выходе ДДПКД 4 (NT)

AT - Тп - NT; 1 X

AT (N+1)T - Т„

M/2J (1) М-1, (2)

МТ0 (MN+X)T,

XT jjjj-|1 X

(3)

М/2 , (4)

,т (М-Х)Тв

М/2 ± X М-1. (5)

Разность периодов сигналов на входе ИЛД 1 не постоянна и зависит от коэффициента деления делителя 10 и числового значения кода X на первом входе управления при фиксированной емкости М ЦАП 8 и других элементов.

Приращение напряжения UU за цикл за счет тока I источника 14 тока равно

ATT IUT

ли ---,

где С - емкость зарядного конденсатора 15. , Приращение напряжения A.U за счет тока ЦАП 8 равно

AU

А1«. Тс С

где Т - длительность импульса на выходе блока 5 интервала, на которую отпирается ключ 6; AI - шаг квантования ЦАП 8.

Учитывая, что напряжение AU и AU должны компенсировать друг друга, получают

(6)

и с

получают

(7)

где Х( равен либо X при 1 Ј X М/2, либо М-Х при М/2 Ј Х М-1. Полный ток ЦАП 8 1Ц равен

N.uT

и х1

Ец/R,

(8)

где

ЕЦнапряжение на входе опорного напряжения ЦАП 8 с выхода блока 7 коррекции; R - сопротивление резисторной матрицы R - 2R в составе ЦАП 8.

Из (7) и (8) с учетом того, что Т0 КТС, где К - коэффициент умножения умножителя 20, и, задавая ток

тока I Eft/R, где Е.

источника 14 напряжение на шине опорного напряжения в источнике 14 тока, получают

Е ц - МЕ0К N.M (9) Таким образом, для полной компенсации напряжения на зарядном конденсаторе 15 ИФД 1 необходимо напряжени на выходе блока 7 коррекции изменять в соответствии с (9).

Это можно сделать при выполнении блока 7 коррекции в виде блока 2k памяти и ЦАП 25. В блоке 2k памяти, в котором значениям X и N на первом и втором входах ставится в соответм-к

ствие значения

N-M + X

на выходе,

а ЦАП 25 с числом разрядов Р, определяемых допустимым уровнем подобных составляющих в спектре выходного сигнала управляемого генератора 3. В некоторых случаях напряжение на входе опорного напряжения ЦАП 25 может быть кратно Е0.

Пусть перед приходом импульса на

40 В этот момент времени блок 9 исключения импульса ДДПКД 4 вырезает один импульс из последовательности импульсов с выхода.управляемого генератора 3. Любые изменения значения

45 дробной части сдвига частоты управляемого генератора 3, т.е. изменения X либо изменения N поступают на вход блока 7 коррекции, который корректи(9)

руют в соответствии с формулой вход ИФД 1 с выхода делителя 10 теку- 50 напряжение на входе опорного напря- щее значение общего опережения сиг- жения ЦАП 8, что приводит к изменению уровня побочных составляющих в спектре выходного сигнала. Диапазон перестройки (количество частот) опре- 55 делается разрядностью ЦАП 8 и делитеналом управляемого генератора 3 частоты его выходного сигнала сто фазе на выходе регистра 12 равно Y. Выход- |ной ток ЦАП 8 соответствует этому значению Y.

Цикл начинается при появлении импульса на выходе делителя 10, который открывает первый ключ 13 ИФД 1

ля 10.

Использование ИФД 1 типа выборка- запоминание также существенно уменьшает уровень побочных составляющих.

5

10

55«62б

и разряжает через него зарядный конденсатор 15. По спаду этого импульса на выходе регистра 12 появляется число, равное сумме чисел на первом и втором входах сумматора 11, т.е. X + Y. Первый ключ 13 запирается и начинается разряд зарядного конденсатора 15 током источника 14 тока. На инверсном выходе D-триггера 23 блока 5 интервалов устанавливается логическая 1, разрешая работу первого и второго счетных триггеров 21 и 22. На выходе первого счетнсго

5 триггера 21 формируется из опорной частоты, умноженной умножителем 20 в К раз, сигнал длительностью Тс Т0/К, после чего первый 21 и второй 22 счетные триггеры и D-триггер

20 23 обнуляются. На время Те открывается ключ 6, корректируя напряжение на зарядном конденсаторе 15, который продолжает заряжаться до появления импульса на входе опорной частоты

25 ИФД 1. За время этого короткого импульса происходит перезапись напряжения на зарядном конденсаторе 15 через первый повторитель 16 и второй ключ 17 на запоминающий конденсатор

18и далее через второй повторитель

19и фильтр 2 это напряжение поступает на вход управления управляемого генератора 3. Кроме того, по спаду этого импульса на выходе ЦАП 8 устанавливается ток, соответствующий

30

35 значению X + Y. Затем циклы повторяются, пока значения X + Y не превышают М и на выходе переполнения сумматора 11 появляется сигнал.

40 В этот момент времени блок 9 исключения импульса ДДПКД 4 вырезает один импульс из последовательности импульсов с выхода.управляемого генератора 3. Любые изменения значения

45 дробной части сдвига частоты управляемого генератора 3, т.е. изменения X либо изменения N поступают на вход блока 7 коррекции, который корректи(9)

руют в соответствии с формулой 50 напряжение на входе опорного напря- жения ЦАП 8, что приводит к изменению уровня побочных составляющих в спектре выходного сигнала. Диапазон перестройки (количество частот) опре- 55 делается разрядностью ЦАП 8 и делителя 10.

Использование ИФД 1 типа выборка- запоминание также существенно уменьшает уровень побочных составляющих.

Блок 5 интервалов может быть также выполнен в виде одновибратора, в этом

случае отсутствует первый вход и связь с входом опорной частоты.

его

i

Формула изобретения

1. Синтезатор частот, содержащий последовательно соединенные импульс- но-фазовый детектор, фильтр нижних частот, управляемый генератор и делитель частоты с дробным переменным коэффициентом деления, при этом первый вход импульсно-фазового детектора является входом опорной частоты синтезатора частот, а первый управляющий вход делителя частоты с дробным переменным коэффициентом деления является первым управляющим входом синтезатора частот, отличающийся тем, что, с целью расширения диапазона формируемых частот и повышения спектральной чистоты выходных колебаний, введены блок интервалов времени, последовательно соединенные блок коррекции, цифроаналоговый преобразователь и ключ, первый и второй выходы и второй вход которого соответственно подключены к дополнительному вход импульсно-фазового детектора, общей шине синтезатора частот и к выходу блока интервалов времени, первый вход которого объединен с входом синхронизации цифроаналогового преобразователя и подключен к первому входу импульсно-фазозого детектора, второй вход которого объединен с вторым входом блока интервалов времени

м

у

10

15

20

25

30

35

лп

и соединен с выходом делителя частоты с дробным переменным коэффициентом деления, информационный выход которого подключен к информационному входу цифроаналогового преобразователя, первый вход блока коррекции соединен с первым управляющим входом делителя частоты с дробным переменным коэффициентом деления, второй управляющий вход которого объединен с вторым входом блока коррекции и является вторым управляющим входом синтезатора частот.

2. Синтезатор по п. 1, о т л и - чающийся тем, что блок коррекции содержит последовательно соединенные блок памяти и цифро ана- логовый преобразователь, выход которого является выходом блока коррекции, первый и второй входы блока памяти являются соответственно первым и вторым входами блока коррекции.

3.- Синтезатор по п. 1, о т л и - чающийся тем, что блок интервалов времени содержит последовательно соединенные умножитель частоты, первый счетный триггер, второй счетный триггер и D-триггер, вход обнуления первого счетного триггера объединены с входом обнуления второго счетного триггера и подключен к инверсному выходу D-триггера, D-вход которого соединен с общей шиной син- тезатора частот, при этом вход умножителя частоты, вход синхронизации D-триггера и выход первого счетного триггера являются соответственно первым и вторым входами и выходом блока интервалов времени.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1988 |

|

SU1698988A1 |

| Синтезатор частот | 1988 |

|

SU1628203A1 |

| Синтезатор частот | 1988 |

|

SU1698989A1 |

| Синтезатор частот | 1987 |

|

SU1631720A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Цифровой формирователь частотно-модулированных сигналов с низким уровнем искажений | 2021 |

|

RU2765273C1 |

| Синтезатор частот | 1985 |

|

SU1312732A1 |

| Синтезатор частот | 1989 |

|

SU1646053A1 |

| Синтезатор с коммутируемой полосой пропускания кольца фазовой автоподстройки частоты | 2023 |

|

RU2812098C1 |

| Цифровой синтезатор изменяющейся частоты | 1988 |

|

SU1525861A1 |

Изобретение относится к радиотехнике. Цель изобретения - расширение диапазона формируемых частот и повышение спектральной чистоты выходных колебаний. Синтезатор частот содержит импульсно-фазовый детектор 1, фильтр 2 нижних частот, управляемый генератор 3, делитель 4 частоты с дробным переменным коэффициентом деления. Цель достигается введением блока 5 интервалов времени, ключа 6, блока 7 коррекции и ЦАП 8, с помощью которых осуществляется изменение уровня побочных составляющих в спектре выходного сигнала. Синтезатор по пп. 2 и 3 ф-лы отличается выполнением блока 7 коррекции и блока 5 интервалов времени. 2 з.п. ф-лы, 4 ил.

г

г

5

г

Фиг.З

ta s

U5,5,

S

«C55J a5J

| Тиббс, Темпл | |||

| Анализатор спектра на базе синтезатора частоты с контуром (ЬАПЧ | |||

| - Электроника, 1978, К 9, с | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Синтезатор частот | 1985 |

|

SU1312732A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ( СИНТЕЗАТОР ЧАСТОТ | |||

Авторы

Даты

1990-04-07—Публикация

1987-10-05—Подача