Изобретение относится к электроизмерительной технике и может быть использовано для построения высокоточных средств измерений.

Цель изобретения - повышение точности измерения и расширение области применения посредством обеспечения измерения постоянного напряжения произвольной полярности.

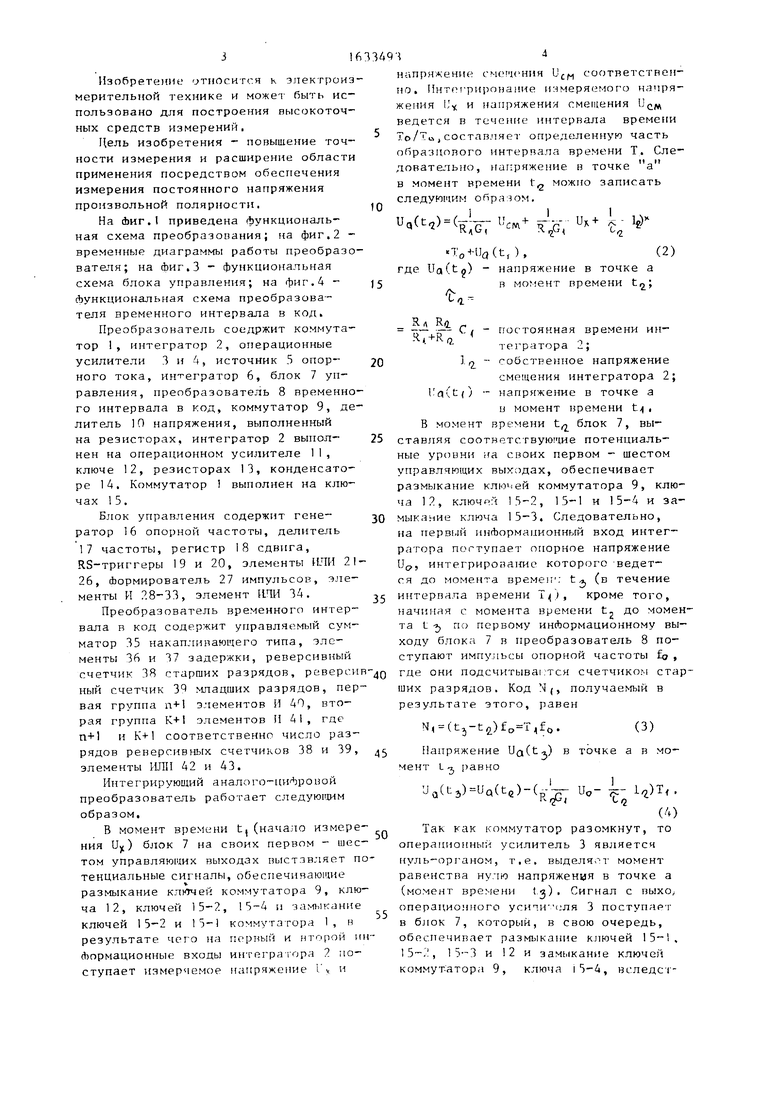

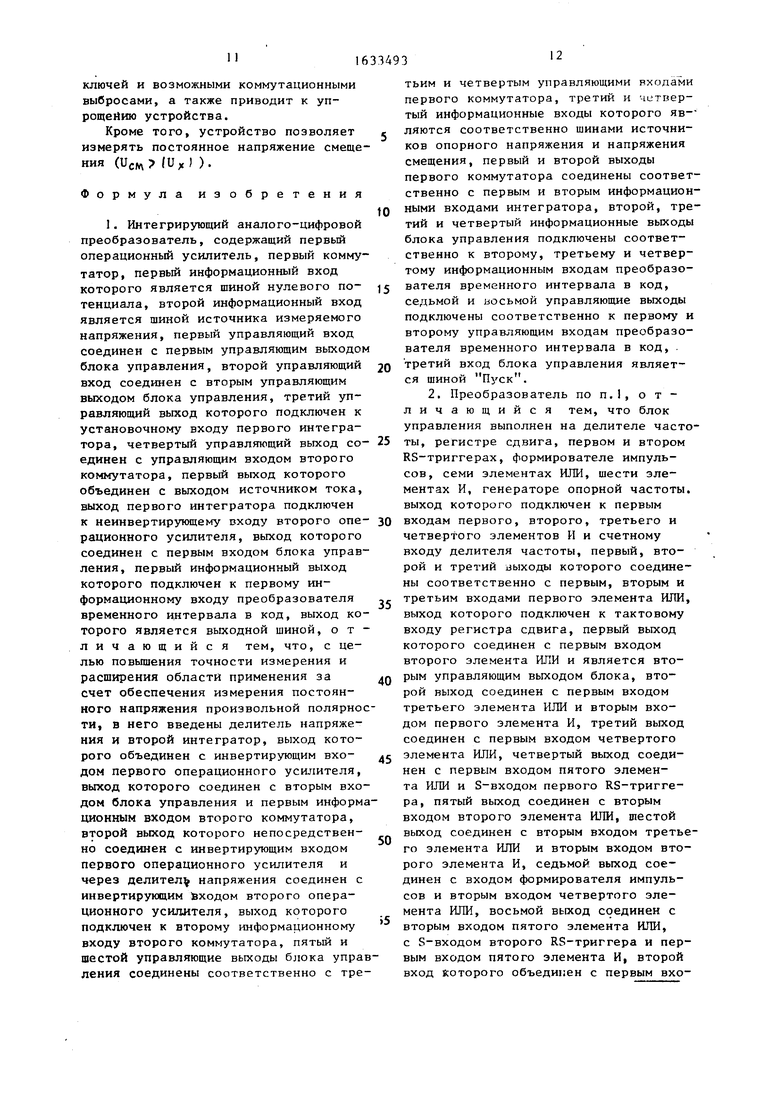

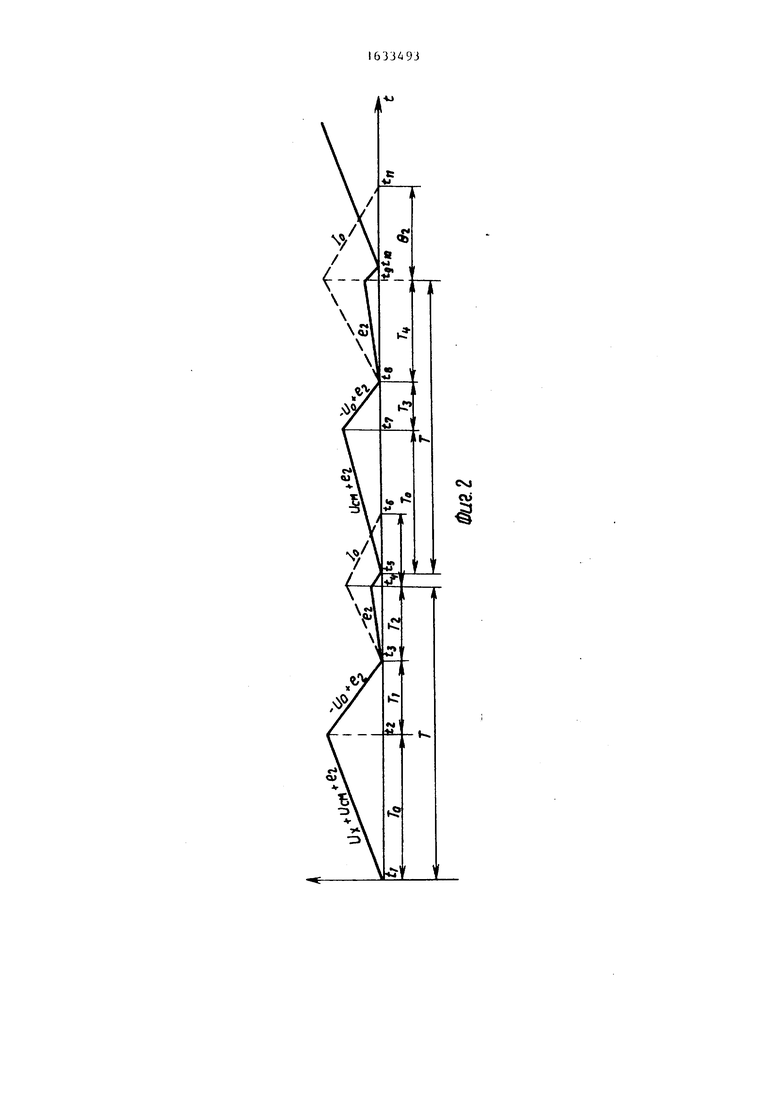

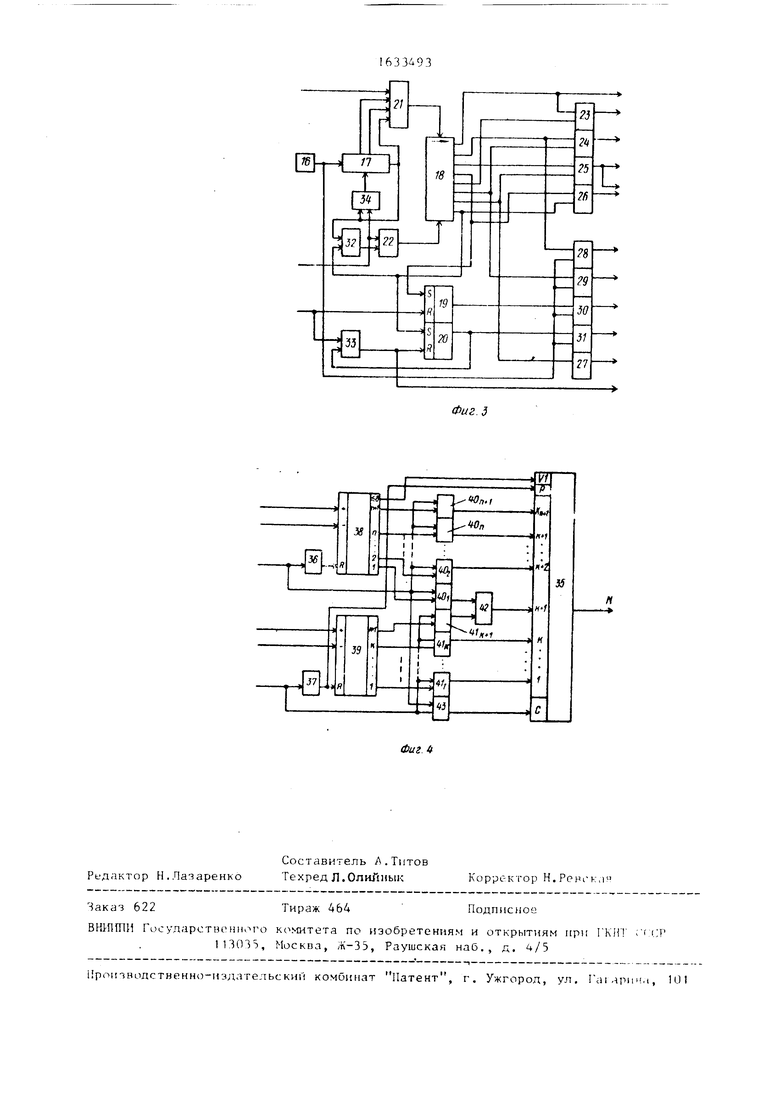

На Лиг. приведена функциональная схема преобразования; на фиг.2 - временные диаграммы работы преобразователя; на Фиг.З - функциональная схема блока управления; на фиг.4 - сЪункциональная схема преобразователя временного интервала в код.

Преобразователь соедржит коммутатор 1, интегратор 2, операционные усилители 3 и 4, источник 5 опорного тока, интегратор 6, блок 7 управления, преобразователь 8 временного интервала в код, коммутатор 9, делитель 10 напряжения, выполненный на резисторах, интегратор 2 выполнен на операционном усилителе 11, ключе 12, резисторах 13, конденсаторе 14. Коммутатор 1 выполнен на ключах 1 5.

Блок управления содержит генератор 16 опорной частоты, делитель 17 частоты, регистр 18 сдвига, RS-триггеры 19 и 20, элементы ИЛИ 21 26, (Ьормирователь 27 импульсов, элементы И 7.8-33, элемент ИЛИ 34.

Преобразователь временного интервала в код содержит управляемый сумматор 35 накапливающего типа, элементы 36 и 37 задержки, реверсивный

16334934

напряжение смешения UCM соответственно. Интегрирование измеряемого напряжения Ь и напряжения смешения UCM ведется в течение интервала времени То/То,составляет определенную часть образцового интервала времени Т. Следовательно, напряжение в точке а в момент времени t можно записать

следующим образом.

Мч) (

,

и

cm

я К U +

X Јц

V

T0+lJQ(t, ),(2)

где Ua(trt) - напряжение в точке а

Ъьв момент времени

0

5

R Ид.

«-,n C постоянная времени ин1 теграгора 2;

J Ј - собственное напряжение смещения интегратора 2; l q(,t() - напряжение в точке а о момент времени t, В момент времени t блок 7, выставляя соответствующие потенциальные уровни на своих первом - шестом управляющих выходах, обеспечивает размыкание ключей коммутатора 9, ключа 12, КЛЮЧРЙ 15-2, 15-1 и 15-4 и за- 0 мыкание ключа 15-3. Следовательно, на первый информационный вход интегратора поступает опорное напряжение UG,, интегрирогзание которого ведется до момента времен ; t (в течение 5 интерната времени I , кроме того,

начиная с момента времени t- до момента L , по первому информационному выходу блока 7 в преобразователь 8 поступают импульсы опорной частоты fo ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Интегрирующий преобразователь напряжения в код | 1986 |

|

SU1410275A1 |

| Устройство для измерения отклонения сопротивления от заданного значения | 1986 |

|

SU1536322A1 |

| Устройство для логарифмирования отношения сигналов | 1982 |

|

SU1112375A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Генератор сигналов для формирования управляющих токов доменной памяти | 1989 |

|

SU1725255A1 |

| Способ измерения рассогласования между углами поворота,один из которых задан кодом | 1985 |

|

SU1285595A1 |

| Измерительный преобразователь для тензорезисторных весоизмерительных устройств | 1990 |

|

SU1830463A1 |

| Преобразователь угол-код | 1974 |

|

SU496580A1 |

| Многоканальный цифроаналоговый преобразователь | 1984 |

|

SU1269269A1 |

Изобретение относится к электро - иэмерительной технике и предназначено для построения высокоточных средств измерения. Изобретение позволяет повысить точность измерения и расширить область применение посредством обеспечения измерения постоянного напряжения произвольной полярности. Поставленная цель достигается тем, что в интегрирующий аналого-цифровой преобразователь, содержащий операционные усилители 3 и 4, коммутаторы 1 и 9, интегратор 2, блок 7 управления, преобразователь 8 временного интервала в код, источник 5 опорного тока, введены интегратор 6 и делитель 10 напряжения, 2 з.п. ф-лы, 4 илS (Л

счетчик 38 старших разрядов, реверсив- о где они подсчитыва: тся счетчиком старный счетчик 3е младших разрядов, первая группа п+1 элементов И 40, вторая группа К+1 элементов И 41, где п+1 и К+1 соответственно число разрядов реверсивных счетчиков 38 и 39, Напряжение Ua(t.,) в точке а в моэлементы ИЛИ 42 и 43.

Интегрирующий аналого-цифровой преобразователь работает следующим образом.

В момент времени t((начало измерения U) блок 7 на своих первом - шестом управляющих выходах выставляет потенциальные сигналы, обеспечивающие размыкание клнтчей коммутатора 9, ключа 12, ключей 15-2, 15-4 и замыкание ключей 15-2 и 15-1 коммутатора 1, в результате чего на первый и нтпрой ин сЬормационные входы интегра юра 2 поступает измеряемое напряжение и

мент I о, равно

Ja(4)Mte)-(

U0- тс- Ц)Т,.

(/О

Так как коммутатор разомкнут, то операционный усилитель 3 является нуль-органом, т.е. выделяет момент равенства нучю напряжения в точке а (момент времени игнал с выхо,, операционного усити сля 3 поступает в блок 7, который, в свою очередь, обеспечивает размыкание ключей 15-1, 15-., 15-3 и 12 и замыкание ключей коммутатора 9, ключа |5-4, вследс1 ших разрядов. Код N(, получаемый в результате этого, равен

(3)

N,(t5-tu).

мент I о, равно

Ja(4)Mte)-(

U0- тс- Ц)Т,.

(/О

Так как коммутатор разомкнут, то операционный усилитель 3 является нуль-органом, т.е. выделяет момент равенства нучю напряжения в точке а (момент времени игнал с выхо,, операционного усити сля 3 поступает в блок 7, который, в свою очередь, обеспечивает размыкание ключей 15-1, 15-., 15-3 и 12 и замыкание ключей коммутатора 9, ключа |5-4, вследс1 вне чего интегрируется собственное напряжение смещения 1,, интегратора т.е. можно записать

Ua(t4)uq(u)+ i- 15T2.

(, Я.

Подставляя в выражение (5) зн l q(tj) из выражения (4), а зате Ufl(t) из выражения (2), можно писать

То 7, . То ,, Т(

Ua(t4), . „, „„ iv

+ L- le(T0-t-T,-t-T2)-HJq(t,)

Напряжение в точке г равно

ua(t4)uQ(t4)+i,

где Ij, - собственное напряжение смещения буферного операционного усилителя 3. Тогда, напряжение в точке в равно

U6((t4) Mt4)(l+ |±) + Ъ Э

1,1+{|.

Следовательно, напряжение в точке б равно

U5(t4)Ue(t4)(t4)(l-1- |i) +

+ ЧО+1Г -14.(9

кз

где 1ф - собственное напряжение смешения операционного усилителя 4

Напряжение I jCt) запоминается на емкости интегратора 6. В момент времени Ц заканчивается образцовый интервал времени Т. В этот же момент времени блок 7 обеспечивает размыкание ключей коммутатора 9 и замыкание ключа 12, что приводит к тому, что интегратор 2 сбрасывается, т.е. происходит разряд конденсатора 14, Кроме того, происходит интегрирование вспомогательной опорной величины (тока 1О) интегратором 6, которое заканчивается в момент времени t6, т.е. момент времени достижения напряжением Ur(t) порогового уровня (в данном случае нулевого). В этот у:е интервал времени из блока 7 по третьему информацией- ному выходу в преобразователь 3 поступают импульсы опорной частоты fo, где они подсчитываются счетчиком 39. Код NЈ, получаемый в результате этого, равен

(t6-t4)fcA(Ю)

е

6334936

Момент времени tfc, т.е. оконча ние интервала времени 0, выделяется операционным усилителе:: 4, который в течение этого интервала времени работает как нуль-орган. Сигнал с выхода операционного усилителя 4 поступает на второй вход блока 7.

Согласно временной диаграмме мож- ном записать

10

35

40

45

55

jЈ 0/ Ge

Uj(t4)

В момент времени t,

(П)

начинается

Uq(t7)-lla(ts) + (i исй+

В момент времени t7 блок

второй цикл преобразования, по дли- 15 тельности равный первому (Т), В момент времени I. g блок 7 обеспечивает замыкание ключа 15-1, а все остальные ключи находятся в разомкнутом сое- тоянии. Таким образом, на второй ин- 20 (Ьормационный вход интегратора 2 поступает напряжение смещения UCM ко торое интегрируется в течение интервала времени. Следовательно, можно записать

tT / - IT /ж- 1 / IT . Ч rrt

(12)

7 обеспечивает замыкание ключа 15-3 к размы- 30 кание ключа 15-1. На червый информационный вход интегратора 2 поступает опорное напряжение -Uo, интегрирование которого продолжается до момента времени tg, (в течение интервала времени t), кроме того, начиная с момента времени с7 до момента времени tg по второму информационному входу блока 7 в преобразователь 8 поступают импульсы опорной частоты fo, где они вычитаются в реверсивном счетчике 38. В результате на выходе данного счетчика с учетом (3) Формируется код разности т интервалов времени Т и Т-j, т.е.

Мт-(Т4-Тз)1:в,(13)

Напряжение UQ(te) в точке а в момент времени t« равно

50 Ua(te)UQ(t7)-(J-Ј- U0- 14)T3. (14)

Работа устройства на интервале времени Тд. аналогична работе устройства на интервале времени Т., поэтому можно записать

V4 ҐTЈ:uc«-

R,G,

Я«Г„

+.- lcCTe+Tft+T4)(t5);

(15)

Uj(t9)Uq(tg)(l+ ЈVl3(l+ f)-l4.(16)

R3

Кроме того, согласно временной диаграмме можно записать

«( .

(17)

Подставляя (15) в (16) и (6) в (9), а также принимая ( - , получим соответственно

Hl -+Ua(ts)(-l4;(18)

«W-ldb-11 я

ReG,

R.G.

ьсм

г Uo 4 2

1 2У Лд Х

+ Д- 4+Uq(t)o/+%o(U(19)

ОЈ

Вычитая (19) из (18) и принимая Uq(t )Ud|(tu) ,получаем

Mt -Urfttf-C U,- U0 +

+ tUo).(20)

Начиная с момента времени t g до момента времени (интервал времени по четвертому информационному выходу блока 7 в- преобразователь 8 пступает опорная частота f0. В резултате в реверсивном счетчике 34 с учтом (10) Лормируется код (М@) разности интервалов времени (У$, т.е

V(0,-0e)Јo.

(21)

Вычитая (17) из (11), получав;

1о

Urf(t)-U(J(tq) ()

(22)

Решая совместно уравнения (20) и (22), получаем

.-V

Uo

(23) Выбирая

- U0Gi(R4+R3)

где га - основание принятой системы счисления; К - количество дополнительных младших разрядов, можно записать

()+m-fc(0,-64 TD. (2.4

Блок 7 работает следующим образом,

В момент времени t , по тине Пуск импульс через элемент 34 сбр

0

5

O

5

0

5

0

5

сывает делитель 17 в нулевое состояние, а через -элемент 22 устанаичнпа- ет регистр 18 в состояние, соответствующее уровню логической 1 на первом его выходе, что, в свою очередь, обеспечивает появление высокого потенциального уровня на втором и шестом управляющих выходах блока 7, по окончании временного интервала Т о (заданная часть образцового интервала Т) в момент времени tg на первом выходе делителя 17 появлется импульс, который через элемент 21 поступает на тактовый вход регистра 18. Вследствие это: г, на первом выходе регистра 18 сдвига появляется низкий потенциальный уровень, а на второй выход - высокий потенциальный уровень, вследствие чего на пятом управляющем выходе блока 7 устанавливается высокий потенциальный уровень, и, кроме того, открывается элемент И 28 и опорная частота поступает на первый информационный выход блока 7. В момент времени t сигнал с первого входа блока 7 обеспечивает сдвиг логической I в третий разряд регистра 18, в результате чего на первом и четвертом чыходах блока 7 формируется высокий потенциальный уровень, а элемент И 28 закрывается. В момент времени t4 (окончание образцового интервала времени Т) на втором выходе делителя 17 формируется сигнал, двигающий логическую 1 в четвертый разряд регистра 18. Вследствие этого на третьем управляющем выходе блока 7 Формируется высокий потенциальный уровень и, кроме того, взводится RS- триггер 19, высокий потенциальный уровень с выхода которого открывается элемент И 30 и опорная частота 10 поступает на третий информационный вь(ход блока 7. Через интервал вре/ч

мени ijq, необходимый для полного разряда интегратора ., импульс, Нормируемый на третьем выходе делителя 17, обеспечивает сброс через элемент 34 делителя 17 и через элемент 21 сдвиг логической 1 в пятый разряд регистра 18, тем самым обеспечивается высокий потенциальный уровень на шестом управляющем выходе блока 7 (момент времени tg, Лиг. 2). В момент времени tfc (Лиг.2) сигнал с второго входа блока 7 сбрасывает триггер 19, В момент времени t7 (Лиг.2) импульс с первого выхода я лителя 17 через эле

16

мент 21 поступает на тактовый вход регистра 18, сдвигает логическую 1 в шестой его разряд. Это приводит к тому, что на пятом управляющем выходе блока 7 формируется высокий потенциальный уровень и, кроме того, открывается элемент И 29, через который опорная частота f0 с генератора 16 поступает на второй информационный выход блока 7. В момент времени tg сигнал с первого входа блока 7 через элемент 21 обеспечивает сдвиг логической 1 в седьмой разряд регистра 18, что, в свою очередь, приводит к тому, что на первом и четвертом управляющих выходах блока 7 формируется высокий потенциальный уровень. В момент времени t) импульс с второго выхода делителя 17 через элемент 21 поступает на тактовый вход регистра 18 и сдвигает логическую 1 в 8-й разряд, это обеспечивает формирование высокого потенциального уровня

на третьем управляющем выходе блока 1 открытие элемента И 32 - взведение RS-триггера 20, высокий потенциальный уровень с выхода которого открывает элемент 31, через который опорная частота fo с генератора 16 поступает на четвертый информационный выход блока 7. В момент времени tg на выходе формирователя 27 формируется импульс, поступающий на седьмой управляющий выход блока 7. В момент времени t(о(фиг.2) на третьем выходе делителя 17 формируется импульс, обеспечивающий обнуление регистра 18, делителя 17. Кроме того, этот же импульс через открытый элемент 32 и элемент 22 поступает на установочный вход регистра 18, т.е. начинается новый цикл измерения. В момент времени t сигнал с второго входа блока 7 проходит через открытый элемент 33, сбрасывает RS-триггер 20 и одновременно поступает на восьмой управляющий выход блока 7, Преобразователь 8 временного интервала в код работает следующим образом. Опорная частота ffl поступает на суммирующий вход реверсивного счетчика 38 в течение интервала времени Т(. В течение интервала времени То, опорная частота fQ поступает на вычитающий вход этого же счетчика. В счетчике формируется код NT пропорциональный разности интервалов времени (Tj-Tj) .

NT (Т,- T5)f,

(25)

10

5

0

о

В момент времени t (фиг.2) сигнал с первого управляющего входа преобразователя 8 открывает элементы АО и, проходя через элемент 43, обеспе чивает запись кода NT в сумматор 35, если Т, в прямом коде, если TjtTj, то сигнал с управляющего выхода счетчика 38 обеспечивает перепись кода NT в сумматор 35 в виде (NT+ 1).

На вычитающий вход реверсивного счетчика 39 опорная частота fo поступает в течение интервала времени 8 , на суммирующий вход - в те- чениг интервала времени 6/. В данном счетчике формируется код Ng, пропорциональный разности интервалов времени (6 f QJ .

N0 (9a- G,)f о (26)

В момент времени (фиг.2) сигнал с второго управляющего входа преобразователя 8 открывает элементы И 41 и через элемент 43 обеспечива- ,. ет запись кода NQ в сумматор 35. Причем состояние управляющего выхода реверсивного счетчика 38 определяет режим сложения кодов NT и Ng.

Если, 8 - 0,j, то соответственно T,7TV тогда

Ng NT - (27)

Если , то соответственно , тогда

N5. (NT-H) + (Ne+O

(28)

Таким образом, в момент времени t

(I

(фиг.2) на выходе сумматора 35 формируется код NJ-, пропорциональный изменяемому напряжению и содержащий информацию о знаке этого напряжения в слоем К+(п+1) разряде.

Сброс счетчиков 38 и 39 производится сигналом с выходов элементов 36 и 37 в моменты времени (t + Ј3) и (t(1 + ) соответственно.

Анализируя функцию преобразования (24), можно отметить, что исключена погрешность, обусловленная напряжением смещения блока сравнения известного преобразователя. того, использование источника опорного напряжения позволяет исключить муль типлекативную погрешность,.возникающую в результате использования источника опорного тока в известном устройстве. Исключение из цепей интегрирующего конденсатора коммутирующих ключей позволяет ликвидировать погрешность преобразования, обусловленную оЪтаточными параметрами этих

ключей и возможными коммутационными выбросами, а также приводит к упрощению устройства.

Кроме того, устройство позволяет измерять постоянное напряжение смещения (UCM |UXJ ).

Формула изобретения

5

0

5

0

5

0

5

0

тьим и четвертым управляющими входами первого коммутатора, третий и четвертый информационные входы которого яв-- ляются соответственно шинами источников опорного напряжения и напряжения смещения, первый и второй выходы первого коммутатора соединены соответственно с первым и вторым информационными входами интегратора, второй, третий и четвертый информационные выходы блока управления подключены соответственно к второму, третьему и четвертому информационным входам преобразователя временного интервала в код, седьмой и восьмой управляющие выходы подключены соответственно к первому и второму управляющим входам преобразователя временного интервала в код, третий вход блока управления является шиной Пуск.

5

0

5

0

5

0

5

0

ным входом является вычитающий вход первого реверсивного счетчика, третьим информационным входом является вычитающий вход второго реверсивного счетчика, четвертым информационным входом является суммируюший вход второго реверсивного счетчика, первым управляющим входом является вход первого элемента задержки, который соединен с первыми входами чпементоя И первой группы п+1 элементов И и первым входом первого элемента ИЛИ, вторым ; правляюгаим входом преобразователя является вход второго элемента задержки, который соединен с первыми входами элементов второй группы К+1 элементов И ирторым входом второго элемента ПЛИ, ьыход которого подключен к входу еннхрогизации управляемого сумматора накапливающего типа, информационные входь г первого по К-й которого подключены к выходам соответствующих элементов II второй группы К+1 элементов И, (К+1)-й информационный вход 1 правляемогч сумматора, накапливающего типа соединен с выходом второго элемента ИЛИ, первый и второй входы которого cot/и-Ч.-НЫ соответственно с выходом СК+Р. -го элемента И второй группы К+ 1 элс-MriHTOi: И и выходом первого элемента И первой группы п+1 .1чементов И, информационные входы с (К+2)-го по (К+п+1)-й управляемого сумматора накапливающего типа соединены соответственно с выходами элементов И с второго по (п+1)-и первой группы п+1 элементов И, управляющий вход соединен с управляющим выходом первого реверсивного счетчика, информационные выходы с первого по (п+1)-й которого соединены соответственно с вторыми входами элементов И первой группы п+1 элементов И, вторые входы элементов И второй группы К+1 элементов И соединены с соответствующими выходами второго реверсивного счетчика, установочный вход которого объединен с установочным входом управляемого сумматора на капливакячего типа и подключен к выходу второго элемента задержки, выход первого элемента задержки соединен с установочным входом первого рет версивного счетчика.

у1

I

tf

Редактор Н.Патаренко

Составитель А.Титов Техред Л.Олийнык

-Заказ 622

Тираж 464

ВНШШИ Государственного комитета по изобретениям и открытиям при I КН ci1 113035, Москва, Ж-35, Раушская наб., д. 4/5

Корректор Н.,

Подписное

| Мартяшин А.И | |||

| Преобразователи электрических параметров для систем контроля и измерения | |||

| - М.: Энергия, 1976, с | |||

| Переносный ветряный двигатель | 1922 |

|

SU384A1 |

| Ростстимулирующая добавка для цыплят-бройлеров | 1986 |

|

SU1417236A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-03-07—Публикация

1989-03-09—Подача