тора, выход второго переключателя подключен к входу второго реверсивного счетчика, выход которого соединен с первым входом четвертого сумматора, второй вход которого является вторым входом формирователя, а выход подключен к второму входу второго коммутатора.

3.Устройство по п. 1, отличающееся тем, что формирователь импульсов содержит задатчик кода и узел сравнения кодов, первый вход которого является входом формирователя, а выходы являются первым и вторым выходами формирователя соответственно, выход задатчика кодов подключен к второму входу узла сравнения кодов.

4.Устройство по п. 1, отличающееся тем, что блок управления содержит ключ, с первого по третий триггеры, элемент И, четвертый и пятый реверсивные счетчики, третий и четвертый переключатели, третий коммутатор, второй счетчик и управляемый делитель частоты, первый вход которого соединен с первым входом третьего коммутатора и является первым входом блока, а выход является первым выходом блока, выход третьего коммутатора соединен с первым входом второго счетчика, первый выход которого является четвертым выходом блока, а второй выход соединен с первым входом первого триггера, выход которого является вторым выходом блока и подключен к второму входу третьего коммутатора, входы третьего и четвертого переключателей являются пятым входом блока, выходы третьего переключателя соединены с входами четвертого реверсивного счетчика, выход которого соединен с вторым входом управляемого делителя частоты, выходы четвертого переключателя подключены к входу пятого реверсивного счетчика, выход которого подключен к второму входу второго счетчика, третий вход третьего коммутатора является шестым входом блока, первый вход второго триггера является третьим входом блока, первый выход - третьим выходом блока, а второй выход соединен с первым входом элемента И, выход которого подключен к второму входу первого триггера, к третьему входу второго счетчика и к первому входу третьего триггера, выход которого соединен с вторым вхо дом элемента И, третий вход которого является четвертым входом блока, выход ключа соединен с вторыми входами второго и третьего триггеров, четвертый вход второго счетчика является вторым входом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения однократных электрических сигналов | 1983 |

|

SU1141445A1 |

| Устройство для регистрации однократных сигналов | 1980 |

|

SU983741A1 |

| Устройство для сглаживания периодических случайных сигналов | 1981 |

|

SU982012A1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ, ОТОБРАЖЕНИЯ И ОБРАБОТКИ ПЕРЕХОДНЫХ ПРОЦЕССОВ В КОНТАКТНОЙ ЦЕПИ МАГНИТОУПРАВЛЯЕМЫХ ПРИБОРОВ | 1990 |

|

RU2060552C1 |

| Спироанализатор | 1986 |

|

SU1391621A1 |

| Устройство для индикации информации | 1977 |

|

SU708375A1 |

| Преобразователь величины мощности и действующего значения напряжения в цифровой код | 1986 |

|

SU1404952A1 |

| Устройство для вычисления массы нефти и нефтепродуктов в резервуарах | 1983 |

|

SU1117653A1 |

| Устройство для регистрации однократных сигналов | 1980 |

|

SU983742A1 |

| Цифровой измеритель температуры | 1985 |

|

SU1303849A1 |

1. УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ИНФОРМАЦИИ, содержащее формирователь, выходы которого подключены к соответствующи.м информационным входам коммутатора, выход которого через последовательно соединенные усилитель и аналого-цифровой преобразователь подключен к первому входу первого блока памяти, выход которого подключен к перво.му входу формирователя кодов, второй вход которого соединен с выходом второго блока памяти, а третий вход - с первым выходом генератора тактовых импульсов, второй выход которого подключен к первому входу блока управления, первый выход которого соединен с первым входом счетчика, выход которого соединен с первым входом блока отображения, второй выход блока управления соединен с первым входом второго и вторым входом первого блоков памяти, вход формирователя через блок согласования подключен к первому входу блока компараторов, выход которого подключен к управляющему входу коммутатора и к входу щифратора, выход которого соединен с вторым входом второго блока памяти, отличающееся тем, что, с целью повышения точности устройства, в него введены первый и второй сумматоры, цифроаналоговый преобразователь, реверсивный счетчик, ждущий генератор и формирователь импульсов, причем второй выход счетчика подключен к второму входу блока управления, третий выход которого соединен с входом ждущего генератора, выход которого подключен к первому входу реверсивного счетчика, выход которого соединен с первым входом второго сумматора и с входом цифроаналогового преобразователя, выход которого соединен с первым входом первого сумматора, второй вход которого является информационным входом устройства, а выход подключен к входу формирователя, второй вход второго сумматора соединен с выходом формирователя кодов, а выход второго сумматора подключен к второму входу блока отображения, четвертый выход блока управления соединен с третьим входом первого и третьим входом (Л второго блоков памяти, выход аналого-цифрового преобразователя подключен к входу формирователя импульсов, первый выход которого соединен с вторым входом реверсивного счетчика, а второй выход - с третьим входом блока управления, четвертый вход которого является входом синхронизации устройства, а пятый вход соединен с перО) вым выходом генератора тактовых импуль сов, третий выход которого подключен к второ.му входу блока компараторов и щестому 05 входу блока управления. со сд 2. Устройство по п. 1, отличающееся тем, что формирователь кодов содержит третий и четвертый сумматоры, второй и третий реверсивные счетчики, первый и второй переключатели и второй коммутатор, первый вход которого является первым входом формирователя, выход подключен к первому вхоjiy третьего сумматора, выход которого является выходом формирователя, входы первого и второго переключателей являются третьим входом формирователя, выход первого переключателя подключен к входу третьего реверсивного счетчика, выход которого соединен с вторым входом третьего сумма

1

Изобретение относится к автоматике и вычислительной технике, и может быть использовано для регистрации формы однократных электрических сигналов.

Известно устройство, содержащее три коммутатора, аналого-цифровой преобразователь, блок памяти, реверсивный счетчик, матричную индикаторную панель, блок управления, счетчик, цифровой нуль-орган, элемент И, регистры, переключатель и кнопки, соединенные определенным образом 1.

Недостатком данного устройства является низкая точность регистрации, обусловленная отсутствием возможности автоматического выбора чувствительности вертикального отклонения, а также отсутствием автоматического смещения входного сигнала перед регистрацией.

Наиболее близким по технической сущности к предлагаемому является устройство для регистрации информации, содержащее первый и второй формирователи напряжения, коммутатор, усилитель, преобразователь аналог-код, два блока памяти, блоки регулирования чувствительности по координатам, матричную индикаторную панель, блок управления перемещением изображения по одной координате, блок синхронизации, блок компараторов, щифратор и блок задания масштаба по другой координате с их связями 2.

Недостатком данного устройства является низкая точность из-за отсутствия автоматического смещения входного сигнала к нулевому уровню перед регистрацией, а также больщая динамическая погрещность, возникающая при взятии отсчетов, совпадающих

по времени с процессом автоматического переключения поддиапазонов чувствительности.

Цель изобретения - повышение точности устройства.

Указанная цель достигается тем, что в

устройство для регистрации информации, содержащее формирователь, выходы которого подключены к соответствующим информационным входам коммутатора, выход которого через последовательно соединенные

усилитель и аналого-цифровой преобразователь подключен к первому входу первого блока памяти, выход которого подключен к первому входу формирователя кодов, второй вход которого соединен с выходом второго блока памяти, а третий вход - с первым выходом генератора тактовых импульсов, второй выход которого подключен к

первому входу блока управления, первый выход которого соединен с первым входом счетчика, выход которого соединен с первым входом блока отображения, второй выход блока управления соединен с первым входом второго и вторым входом первого блоков памяти, вход формирователя через блок согласования подключен к первому входу блока компараторов, выход которого подключен к управляющему входу коммутатора и к входу шифратора, выход которого соединен с вторым входом второго блока памяти, введены первый и второй сумматоры, цифроаналоговый преобразователь, реверсивный счетчик, ждущий генератор и формирователь импульсов, причем второй выход счетчика подключен к второму входу блока управления, третий выход которого соединен с входом ждущего генератора, выход которого подключен к первому входу реверсивного счетчика, выход которого соединен с первым входом второго сумматора и с входом цифроаналогового преобразователя, выход которого соединен с первым входом первого сумматора, второй вход которого является информационным входом устройства, а выход подключен к входу формирователя, второй вход второго сумматора соединен с выходом формирователя кодов, а выход второго сумматора подключен к второму входу блока отображения, четвертый выход блока управления соединен с третьим входом первого и третьим входом второго блоков памяти, выход аналого-цифрового преобразователя подключен к входу формирователя импульсов, первый выход которого соединен с вторым входом реверсивного счетчика, а второй выход - с третьим входом блока управления, четвертый вход которого является входом синхронизации устройства, а пятый вход соединен с первым выходом генератора тактовых импульсов, третий выход которого подключен к второму входу блока компараторов и шестому входу блока управления.

Формирователь кодов содержит третий и четвертый сумматоры, второй и третий реверсивные счетчики, первый и второй переключатели и второй коммутатор, первый вход которого является первым входом формирователя, выход подключен к первому входу третьего сумматора, выход которого является выходом формирователя. Входы первого и второго переключателей являются третьим входом формирователя, выход первого переключателя подключен к входу третьего реверсивного счетчика, выход которого соединен с вторым входом третьего сумматора, выход второго переключателя подклю-чен к входу второго реверсивного счетчика, выход которого соединен с первым входом четвертого сумматора, второй вход которого является вторым входом формирователя, а

выход подключен к второму входу второго коммутатора.

Формирователь импульсов содержит задатчик кода и узел сравнения кодов, первый вход которого является входом формирователя, а выходы являются первым и вторым выходами формирователя соответственно, выход задатчика кодов подключен к второму входу узла сравнения кодов.

Q Блок управления содержит ключ, с первого по третий триггеры, элемент И, четвертый и пятый реверсивные счетчики, третий и четвертый переключатели, третий коммутатор, второй счетчик и управляемый делитель частоты, первый вход которого соединен с первым входом третьего коммутатора и является первым входом блока, а выход является первым выходом блока, выход третьего коммутатора соединен с первым входом второго счетчика, первый выход

Q которого является четверты.м выходом блока, а второй выход соединен с первым входом первого триггера, выход которого является вторым выходом блока и подключен к второму входу третьего коммутатора, входы третьего и четвертого переключателей

5 являются пятым входом блока, выходы третьего переключателя соединены с входами четвертого реверсивного счетчика, выход которого соединен с вторым входом управляемого делителя частоты, выходы четвертого пеQ реключателя подключены к входу пятого реверсивного счетчика, выход которого подключен к второму входу второго счетчика, третий вход третьего коммутатора является шестым входом блока, первый вход второго триггера является третьим входом блока,

первый выход - третьим выходом блока, а второй выход соединен с первым входом элемента И, выход которого подключен к вто-. рому входу первого триггера, к третьему входу второго счетчика и к первому входу третьего триггера, выход которого соединен с вторым входом элемента И, третий вход которого является четвертым входом блока, выход ключа соединен с вторыми входами второго и третьего триггеров, четвертый вход второго счетчика является вторым входом блока.

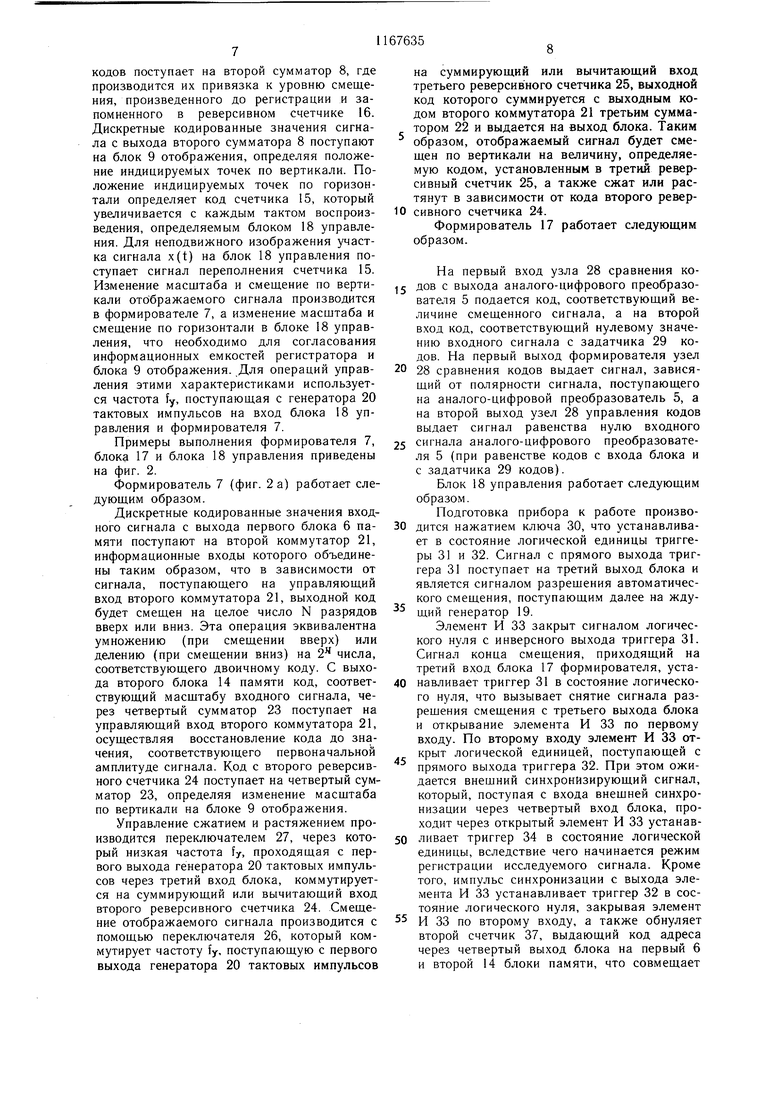

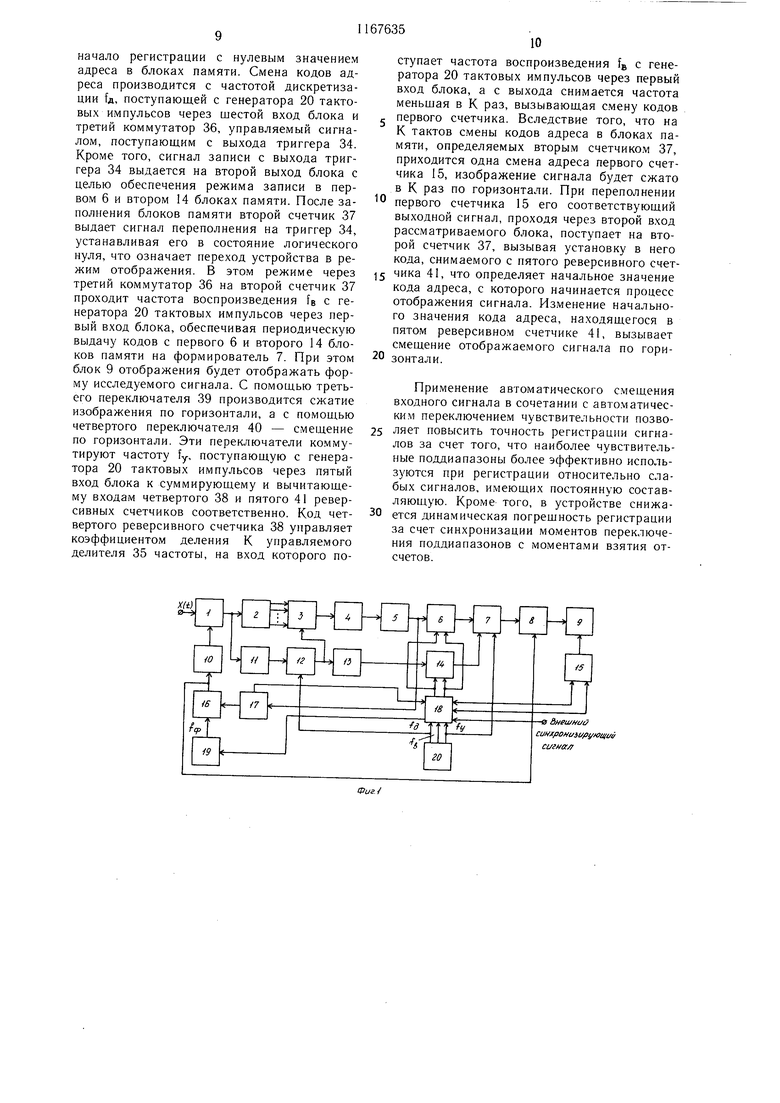

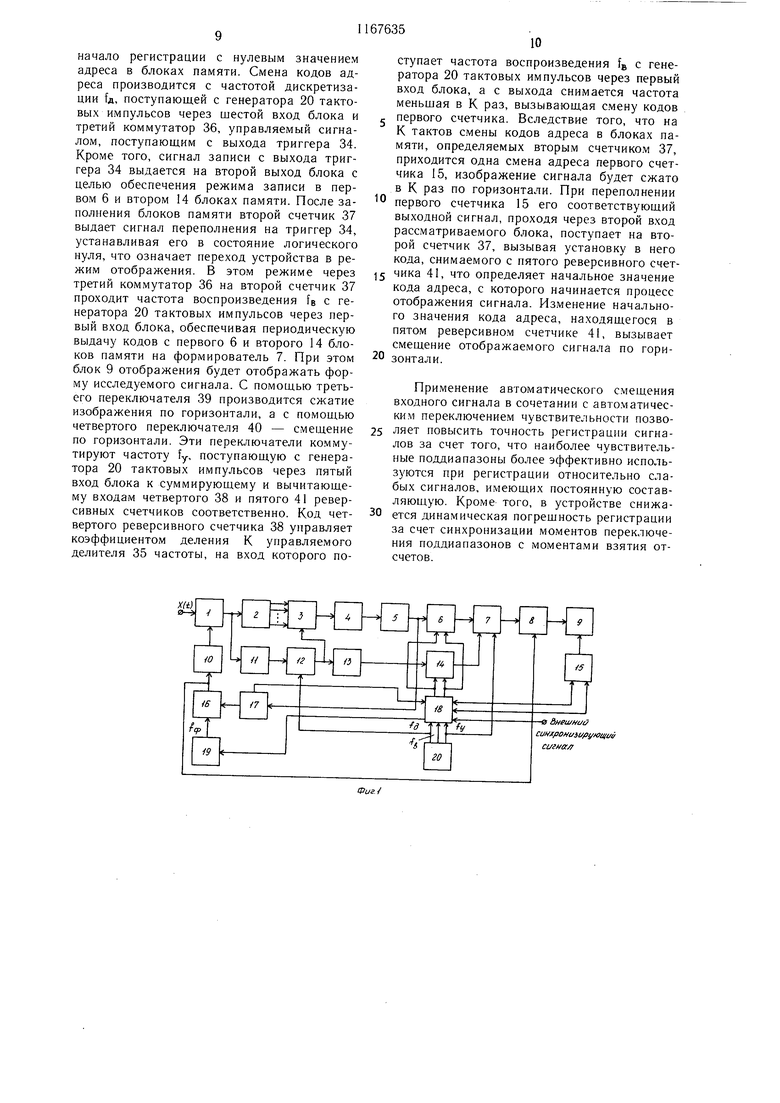

5 На фиг. 1 представлена структурная схема устройства; на фиг. 2 а, б, в - схемы формирователя кодов, блока управления реверсивным счетчико.м и блока управления соответственно.

Устройство содержит первый сумматор 1, формирователь 2, коммутатор 3, усилитель 4, аналого-цифровой преобразователь 5, первый блок 6 памяти, формирователь 7 кодов, второй сумматор 8, блок 9 отображения,

5 цифроаналоговый преобразователь 10, блок 11 согласования, блок 12 компараторов, гпифратор 13, второй блок 14 памяти, счетчик 15, реверсивный счетчик 16, формирователь 17 импульсов, блок 18 управления.

ждущий генератор 19, генератор 20 актовых импульсов, второй коммутатор 21; третий 22 и четвертый 23 сумматоры, второй 24 и третий 25 реверсивные счетчики, первый 26 и второй 27 переключатели, узел 28 сравнения кодов и задатчик 29 кода, ключ 30, второй 31 и третий 32 триггеры, элемент И 33, первый триггер 34, управляемый делитель 35 частоты, третий коммутатор 36, второй счетчик 37, четвертый реверсивный счетчик 38, третий 39 и четвертый 40 переключатели, пятый реверсивный счетчик 41.

Устройство работает следующим образом. .

Входной сигнал {i) поступает на первый сумматор 1 и складывается с выходным сигналом цифроаналогового преобразователя 10. Смещенный сигнал с выхода сумматора 1 поступает на формирователь 2, представляющий собой устройство с несколькими выходами, с которых снимается сигнал, промасщтабированный с различными коэффициентами.

Кроме того, сигнал с выхода сумматора 1 поступает через блок И на вход блока 12 компараторов. В зависимости от уровня входного сигнала управляющий сигнал с выхода блока 12 компараторов разрешает прохождение промасщтабированного сигнала с одного из выходов формирователя 2 через коммутатор 3 на вход усилителя 4, имеющего постоянный коэффициент усиления. Далее усиленный сигнал преобразуется аналого-цифровым преобразователем 5 в код, который поступает на первый блок 6 памяти и на блок 17.

Перед началом регистрации производится автоматическое смещение входного сигнала к нулевому уровню. При этом ждущий генератор 19 начинает вырабатывать импульсы с тактовой частотой под действием разрешающего сигнала, приходящего с блока 18 управления. Импульсы с выхода ждущего генератора 19 считаются реверсивным счетчиком 16, направление счета определяется управляющим сигналом с формирователя 17 и соответствует полярности напряжения, поступающего на вход аналого-цифрового преобразователя 5. Код с выхода реверсивного счетчика 16 преобразуется цифроаналоговым преобразователем 10 в аналоговый сигнал и подается на первый сумматор 1. Полярность выходного сигнала цифроаналогового преобразователя 10 выбирается так, что при отрицательном смещении напряжения с выхода первого сумматора 1 (и соответственно на входе аналого-цифрового преобразователя 5) реверсивный счетчик 16 и цифроаналоговый преобразователь 10, управляемые блоком 17, отрабатывают эту величину в сторону увеличения, а при положительном смещении - в сторону уменьшения. Таким образом, действует замкнутая петля отрицательной обратной связи:

первый сумматор 1 - формирователь 2 - коммутатор 3 - усилитель 4 - аналогоцифровой преобразователь 5 - блок 17 - реверсивный счетчик 16 - цифроаналоговый преобразователь 10 - первый сумматор 1, с помощью которой величина смещения сигнала на выходе сумматора 1 (и соответственно на входе аналого-цифрового преобразователя 5) отрабатывается к нулю.

- Этот процесс заканчивается тогда, когда код на выходе аналого-цифрового преобразователя 5 будет соответствовать нулевому значению аналогового сигнала. При этом формирователь 17 вырабатывает сигнал конца смещения, поступающий на блок 18 управления, который, в свою очередь, запрещает выработку импульсов ждущим генератором 19 и останавливает реверсивный счетчик 16. Код с реверсивного счетчика 16 будет использоваться в режиме отображения для восстановления исходного уровня смещения отображаемого сигнала.

После завершения процесса автоматического смещения сигнала к нулевому уровню производится его регистрация, которая начинается с приходом внешнего синхронизирующего сигнала на блок 18 управления, который, в свою очередь, выдает сигналы записи на первый 6 и второй 14 блоки памяти соответственно. При этом коды с аналого-цифрового преобразователя 5, соответствующие мгновенным значениям входного сигнала, смещенного перед регистрацией и промасщтабированного в зависимости от его величины, записываются в блок 6 памяти с частотой дискретизации f , определяемой

5 генератором 20 тактовых импульсов. Частота дискретизации f также подается на блок 12 компараторов, синхронизируя процесс переключения поддиапазонов чувствительности, что исключает регистрацию ложных отсчетов, совпадающих по времени с переходными процессами, возникающими при переключении поддиапазонов чувствительности. Одновременно с запоминанием в первый блок 6 памяти кодов, соответствующих амплитуде исследуемого сигнала в дискретные моменты времени, во второй блок 14 памяти записывается код масштаба каждой ординаты, снимаемый с выхода шифратора 13, переключенного к блоку 12 компараторов. Регистрация сигнала заканчивается с заполнением первого 6 и второго 14 блоков

памяти (которое происходит одновременно). В режиме отображения дискретные кодированные значения сигнала и масштаба каждой ординаты периодически выбираются из блоков 6 и 14 памяти с частотой воспроизведения fg и поступают на формирователь 7, в котором производится их преобразование в двоичный код, соответствующий ординатам исследуемого сигнала с учетом их масштаба. Далее эта последовательность

кодов поступает на второй сумматор 8, где производится их привязка к уровню смещения, произведенного до регистрации и запомненного в реверсивном счетчике 16. Дискретные кодированные значения сигнала с выхода второго сумматора 8 поступают на блок 9 отображения, определяя положение индицируемых точек по вертикали. Положение индицируемых точек по горизонтали определяет код счетчика 15, который увеличивается с каждым тактом воспроизведения, определяемым блоком 18 управления. Для неподвижного изображения участка сигнала x(t) на блок 18 управления поступает сигнал переполнения счетчика 15. Изменение масштаба и смещение по вертикали отображаемого сигнала производится в формирователе 7, а изменение масштаба и смешение по горизонтали в блоке 18 управления, что необходимо для согласования информационных емкостей регистратора и блока 9 отображения. Для операций управления этими характеристиками используется частота fy, поступающая с генератора 20 тактовых импульсов на вход блока 18 управления и формирователя 7.

Примеры выполнения формирователя 7, блока 17 и блока 18 управления приведены на фиг. 2.

Формирователь 7 (фиг. 2 а) работает следующим образом.

Дискретные кодированные значения входного сигнала с выхода первого блока 6 памяти поступают на второй коммутатор 21, информационные входы которого объединены таким образом, что в зависимости от сигнала, поступающего на управляющий вход второго коммутатора 21, выходной код будет смещен на целое число N разрядов вверх или вниз. Эта операция эквивалентна умножению (при смещении вверх) или делению (при смещении вниз) на 2 числа, соответствующего двоичному коду. С выхода второго блока 14 памяти код, соответствующий масштабу входного сигнала, через четвертый сумматор 23 поступает на управляющий вход второго коммутатора 21, осуществляя восстановление кода до значения, соответствующего первоначальной амплитуде сигнала. Код с второго реверсивного счетчика 24 поступает на четвертый сумматор 23, определяя изменение масштаба по вертикали на блоке 9 отображения.

Управление сжатием и растяжением производится переключателем 27, через который низкая частота fy, проходящая с первого выхода генератора 20 тактовых импульсов через третий вход блока, коммутируется на суммирующий или вычитающий вход второго реверсивного счетчика 24. Смещение отображаемого сигнала производится с помощью переключателя 26, который коммутирует частоту fy, поступающую с первого выхода генератора 20 тактовых импульсов

на суммирующий или вычитающий вход третьего реверсивного счетчика 25, выходной код которого суммируется с выходным кодом второго коммутатора 21 третьим сумматором 22 и выдается на выход блока. Таким образом, отображаемый сигнал будет смещен по вертикали на величину, определяемую кодом, установленным в третий реверсивный счетчик 25, а также сжат или растянут в зависимости от кода второго реверсивного счетчика 24.

Формирователь 17 работает следующим образом.

На первый вход узла 28 сравнения кодов с выхода аналого-цифрового преобразователя 5 подается код, соответствующий величине смещенного сигнала, а на второй вход код, соответствующий нулевому значению входного сигнала с задатчика 29 кодов. На первый выход формирователя узел

0 28 сравнения кодов выдает сигнал, зависящий от полярности сигнала, поступающего на аналого-цифровой преобразователь 5, а на второй выход узел 28 управления кодов выдает сигнал равенства нулю входного

5 сигнала аналого-цифрового преобразователя 5 (при равенстве кодов с входа блока и с задатчика 29 кодов).

Блок 18 управления работает следующим образом.

Подготовка прибора к работе производится нажатием ключа 30, что устанавливает в состояние логической единицы триггеры 31 и 32. Сигнал с прямого выхода триггера 31 поступает на третий выход блока и является сигналом разрешения автоматического смещения, поступающим далее на жду щий генератор 19.

Элемент И 33 закрыт сигналом логического нуля с инверсного выхода триггера 31. Сигнал конца смещения, приходящий на третий вход блока 17 формирователя, устанавливает триггер 31 в состояние логического нуля, что вызывает снятие сигнала разрешения смещения с третьего выхода блока и открывание элемента И 33 по первому входу. По второму входу элемент И 33 открыт логической единицей, поступающей с прямого выхода триггера 32. При этом ожидается внешний синхронизирующий сигнал, который, поступая с входа внещней синхронизации через четвертый вход блока, проходит через открытый элемент И 33 устанавливает триггер 34 в состояние логической единицы, вследствие чего начинается режим регистрации исследуемого сигнала. Кроме того, импульс синхронизации с выхода элемента И 33 устанавливает триггер 32 в состояние логического нуля, закрывая элемент

5 И 33 по второму входу, а также обнуляет второй счетчик 37, выдающий код адреса через четвертый выход блока на первый 6 и второй 14 блоки памяти, что совмещает

начало регистрации с нулевым значением адреса в блоках памяти. Смена кодов адреса производится с частотой дискретизации (д, поступающей с генератора 20 тактовых импульсов через шестой вход блока и третий коммутатор 36, управляемый сигналом, поступающим с выхода триггера 34. Кроме того, сигнал записи с выхода триггера 34 выдается на второй выход блока с целью обеспечения режима записи в первом 6 и втором 14 блоках памяти. После заполнения блоков памяти второй счетчик 37 выдает сигнал переполнения на триггер 34, устанавливая его в состояние логического нуля, что означает переход устройства в режим отображения. В этом режиме через третий коммутатор 36 на второй счетчик 37 проходит частота воспроизведения fe с генератора 20 тактовых импульсов через первый вход блока, обеспечивая периодическую выдачу кодов с первого 6 и второго 14 блоков памяти на формирователь 7. При этом блок 9 отображения будет отображать форму исследуемого сигнала. С помощью третьего переключателя 39 производится сжатие изображения по горизонтали, а с помощью четвертого переключателя 40 - смещение по горизонтали. Эти переключатели коммутируют частоту fy, поступающую с генератора 20 тактовых импульсов через пятый вход блока к суммирующему и вычитающему входам четвертого 38 и пятого 41 реверсивных счетчиков соответственно. Код четвертого реверсивного счетчика 38 управляет коэффициентом деления К управляемого делителя 35 частоты, на вход которого поступает частота воспроизведения fg с генератора 20 тактовых импульсов через первый вход блока, а с выхода снимается частота меньшая в К раз, вызывающая смену кодов первого счетчика. Вследствие того, что на К тактов с.мены кодов адреса в блоках памяти, определяемых вторы.м счетчико.м 37, приходится одна смена адреса первого счетчика 15, изображение сигнала будет сжато в К раз по горизонтали. При переполнении

первого счетчика 15 его соответствующий выходной сигнал, проходя через второй вход рассматриваемого блока, поступает на второй счетчик 37, вызывая установку в него кода, снимаемого с пятого реверсивного счетчика 41, что определяет начальное значение кода адреса, с которого начинается процесс отображения сигнала. Изменение начального значения кода адреса, находящегося в пятом реверсивном счетчике 41, вызывает смещение отображаемого сигнала по горизонтали.

Применение автоматического смещения входного сигнала в сочетании с автоматическим переключением чувствительности позволяет повысить точность регистрации сигналов за счет того, что наиболее чувствительные поддиапазоны более эффективно используются при регистрации относительно слабых сигналов, имеющих постоянную составляющую. Кроме того, в устройстве снижается динамическая погрещность регистрации за счет синхронизации моментов переключения поддиапазонов с моментами взятия отсчетов.

. 20 6л.

На 9S/j. 5нешн1/ц синхро6}

В)

иг.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для индикации информации | 1977 |

|

SU708375A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для индикации | 1978 |

|

SU734756A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-15—Публикация

1982-03-24—Подача