u,ti)

-С

tfe/A.

Фиг. г

31509

Изобретение относится к электроизмерительной технике и может быть использовано для измерения фазового сдвига электрических сигналов, в фа- .эочувствительных вольтметрах, измерителях мгновенной мощности, в анализаторах амплитудно- и фазочастотного спектров и т.д.

Цель изобретения - повьппение точности измерения.

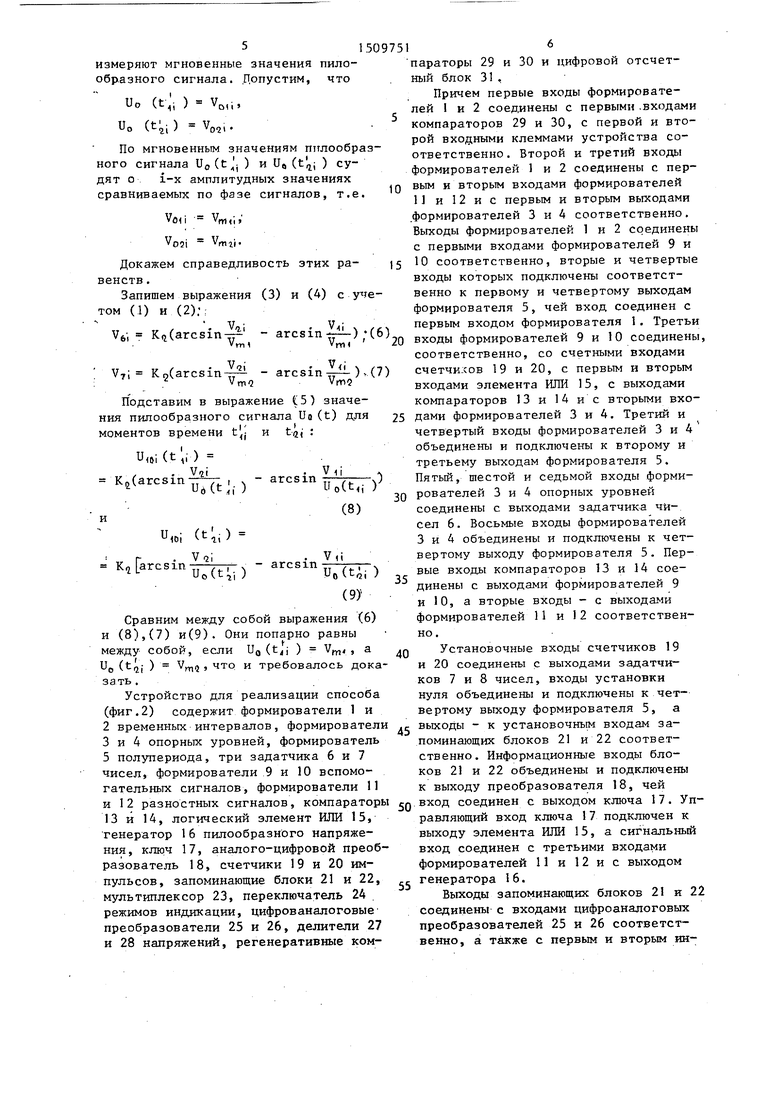

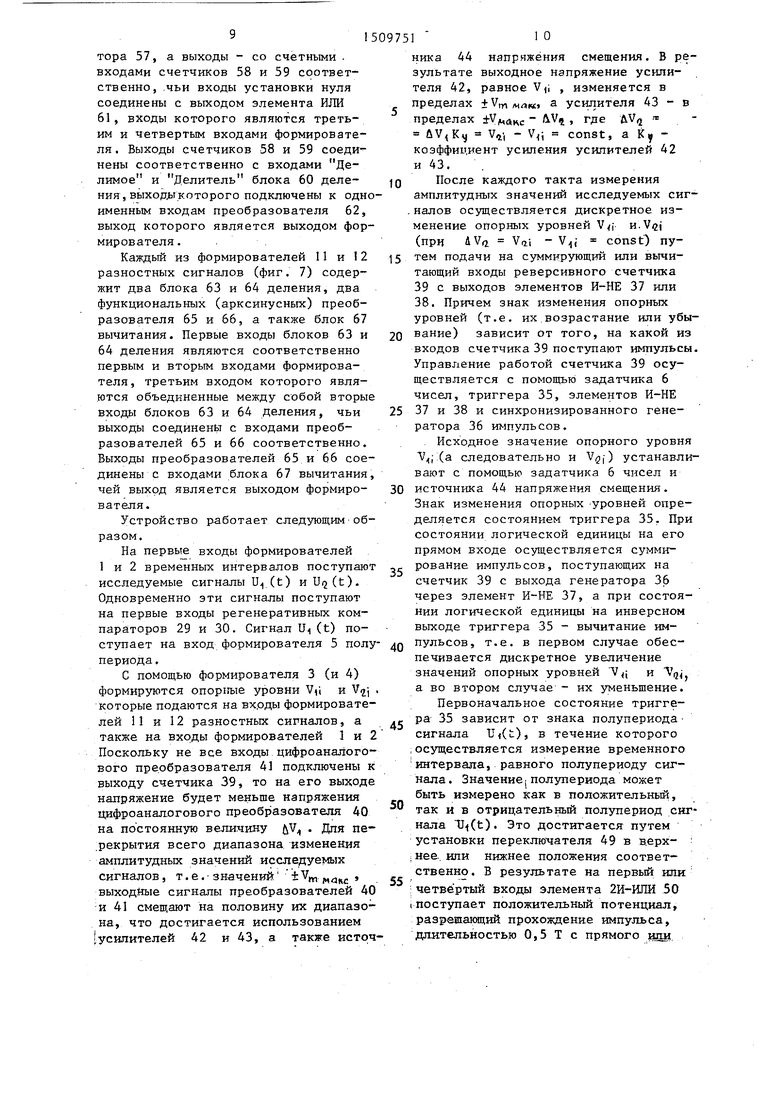

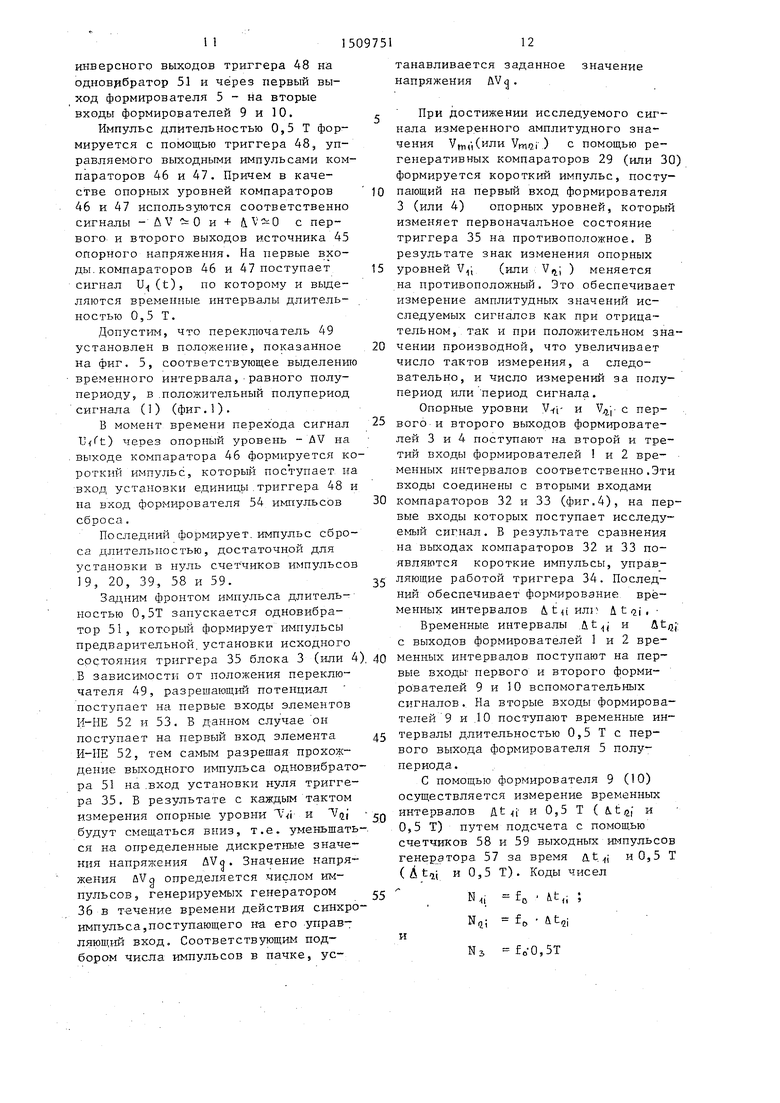

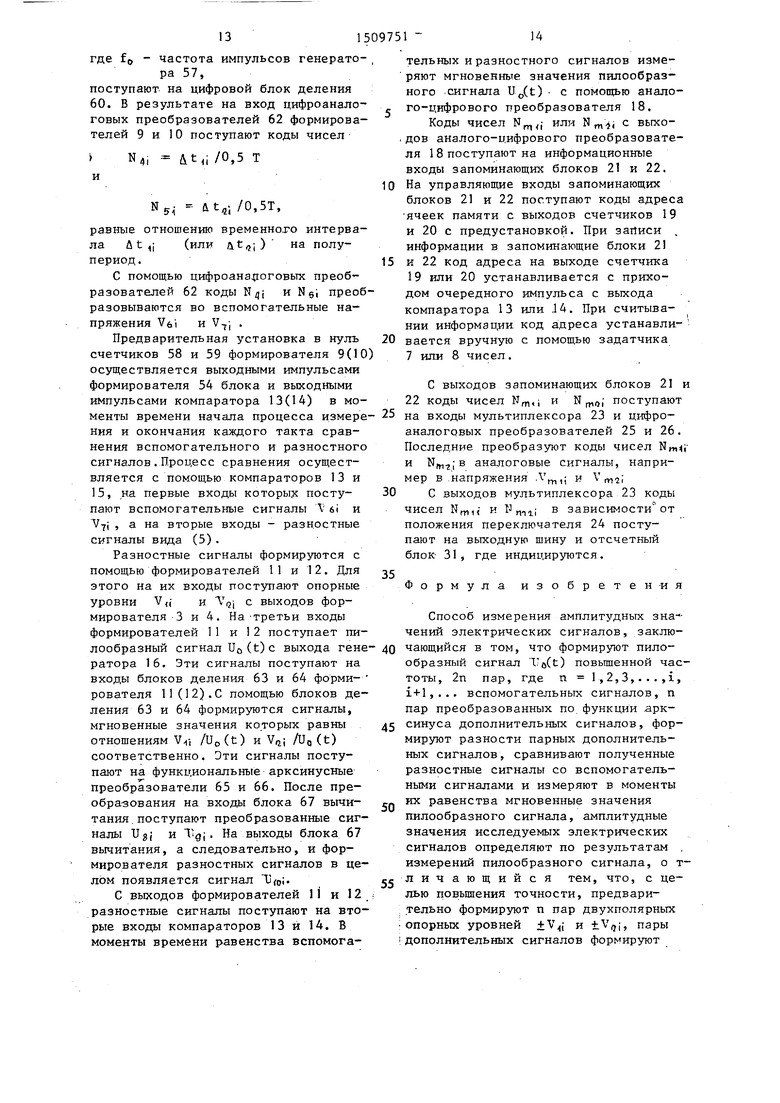

На фиг. I приведены временные диаграммы, поясняющие предлагаемый способ; на фиг. 2 блок-схема устрой- ства для его реализации, на фиг.3-7 - формирователь временных интервалов, формирователь опорных уровней, формирователь полупериода, формирователь вспомогательных сигналов и формирователь разностных сигналов устройст- ва соответственно.

Необходимо .измерить амплитудные значения Vm и V сравниваемых по фазе сигналов

. U4 (t) V, sinSlt

U-jCt ) .sin(Jlt-4),

2Я

где SI -- - .круговая частота,..

-период,

-фазовый сдвиг сигналов.

Для этого формируют опорные уров- .ни ,- и , где i 1,2,3,..., п и пилообразный сигнал Uo(t ) повышенной частрты.

Измеряют значение полупериода исследуемых сигналов, например, путем .измерения временного интервала, ограниченного моментами перехода сигнала U){ (t) или U-KgCt) через уровни - AV и + &V в положительном и отрицательном направлениях. По ре- зультату измерения формируют сигнал

П iT

V - Tf - ъ J

где К, - коэффициент пропорциональности.

Затем сравнивают исследуемые сигналы с опорными уровнями V«j и Vfti Равенства этих сигналов

V,«,sinAt,i V,j ; . Vn дsinЛt,u, V,i,- ; ( -%) V,i , Vff,tsin(Jl.

Vei

ступают в моменты времени t и t(, i и tui), определяемые выражениями

aJ csinCV, /V,);

i (Vui/Vmi); t,i -j-arcsin (V,; /У г+M x)i

t i+A - arcsin (V,ii /Vms + ). Измеряют временные интервалы

t,f44.-

..

0,5T ., . V7t . Vii .

V (arcsin-rr- - arcsj-n-rp-) ITУт Vrvi4

.. 0) .

ut i - t/Ji+1 - t (ji - .

0,5T , . l . . - (arcsin- - arcsLn---)v

I V,nnVi-MO

(2)

Результаты измерений запоминают. По результатам измерений формируют сигналы

v,i К,. flt,i;

Vgi K -utai,

. Далее формируют вспомогательные сигналы

Vsi K(V,i /V, ); (3). Vyi K,(V5i/V3 ), (4) .

где Kft - коэффициент пропорциональности, и дополнительные сигналы

Ugj (t) K,i arcsin v,i ) и

Ugi(t) K arcsinB/zi /U«,(t)L

.

Определяют разность дополнительных сигналов каждой L-Й пары:

U(oi(t) Ugi (t) -Uji (t)

К ar.csin

T

. - j./ v,i

UoCt)

- arcsjn

)

V(5)

55

Полученные разностные сигналы сравнивают с вспомогательными сигналами .

В момент времени t ,, и их равенства, т.е. при Uioi (t ,; ) Veii .

U,oi (t ,i) Vi,51509751

измеряют мгновенные значения пилообразного сигнала. Допустим, что

Uo (t,i ) V,,, Uo () Vo,,.. 5

По мгновенным значениям птшообраз- ного сигнала U ( ) и U ( ) судят о i-x амплитудных значениях сравниваемых по фазе сигналов, т.е.

Voii Vfv,,i,

Vo2i mif

Докажем справедливость этих ра- 15 венств.

Запишем выражения (3) и (4) с учетом (1) и (2);:

V,

- - arcsin:-- , , vmiVmt 20

61

М Vrt| 4i / f

arcsin fp- -arcsin-j;;-):(6).

VQJ.

. Q(,cii:uB J-ll-r;- - arCSln- T

,T 2Vm

VT Kn(arcsin-rr - arcsin

Подставим в выражение t5) значения пилообразного сигнала Uo (t) для 25

и tiit :

U,6l(t,i)

- arcsin

11

Uo(t,i ) (8)

- arcsin

Uo( ) (9

Сравним между собой выражения (6) и (8),(7) и(9). Они попарно равны между собой, если UQ (tj j ) V, , а Ug ( ) , что и требовалось доказать .

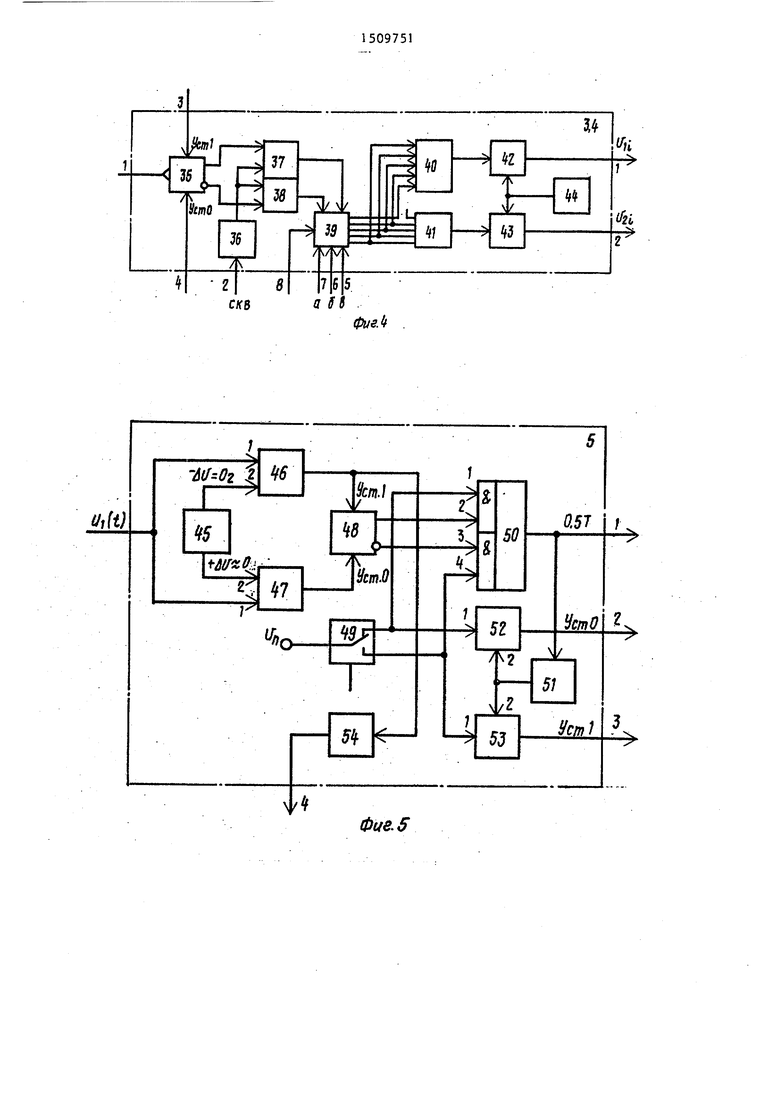

Устройство для реализации способа (фиг.2) содержит формирователи 1 и

2временных интервалов, формирователи

3и 4 опорных уровней, формирователь 5 полупериода, три задатчика 6 и 7 чисел, формирователи 9 и 10 вспомогательных сигналов, формирователи 11

и 12 разностных сигналов, компараторы 13 и 14, логический элемент ИЛИ 15, генератор 16 пилообразного напряжения, ключ 17, аналого-цифровой преобразователь 18, счетчики 19 и 20 импульсов, запоминающие блоки 21 и 22, мультиплексор 23, переключатель 24 режимов индикации, цифрованалоговые преобразователи 25 и 26, делители 27 и 28 напряжений, регенеративные ком5

15

20

).

)

25

30

35

Q

.

CQ параторы 29 и 30 и цифровой отсчет- ный блок 31 ,

Причем первые входы формирователей I и 2 соединены с первыми .входами компараторов 29 и 30, с первой и второй входными клеммами устройства соответственно . Второй и третий входы формирователей 1 и 2 соединены с первым и вторым входами формирователей 1 и 12 и с первым и вторым выходами формирователей 3 и 4 соответственно. Выходы формирователей 1 и 2 соединены с первыми входами формирователей 9 и 10 соответственно, вторые и четвертые входы которых подключены соответственно к первому и четвертому выходам формирователя 5, чей вход соединен с первым входом формирователя 1. Третьи входы формирователей 9 и 10 соединены, соответственно, со счетными входами счетчихов 19 и 20, с первым и вторым входами элемента HlHi 15, с выходами компараторов 13 и 14 и с вторыми входами формирователей 3 и 4, Третий и четвертый входы формирователей 3 и 4 объединены и подключены к второму и третьему выходам формирователя 5. Пятый, шестой и седьмой входы формирователей 3 и 4 опорных уровней соединены с выходами задатчика чисел 6. Восьмые входы формирователей 3 и 4 объединены и подключены к четвертому выходу формирователя 5. Первые входы компараторов 13 и 14 соединены с выходами формирователей 9 и 10, а вторые входы - с выходами формирователей 11 и 2 соответственно.

Установочные входы счетчиков 19 и 20 соединены с выходами задатчи- ков 7 и 8 чисел, входы установки нуля объединены и подключены к четвертому выходу формирователя 5, а выходы - к установочньгм входам запоминающих блоков 21 и 22 соответственно. Информационные входы блоков 21 и 22 объединены и подключены к выходу преобразователя 18, чей вход соединен с выходом ключа 17. Управляющий вход ключа 17 подключен к выходу элемента ИЛИ 15, а сигнальный вход соединен с третьими входами формирователей 11 и 12 и с выходом генератора 16.

Выходы запоминающих блоков 21 и 22 соединены с входами цифроаналоговых преобразователей 25 и 26 соответственно, а также с первым и вторым информационными входами мультиплексора 23, выходы которого соединены с входами блока 31 и выходной шиной, а управляющие входы подключены к выходам переключателя 24 . Вход последнего соединен с клеммой напряжения питания.

Выходы цифроаналоговых преобразователей 25 и 26 являются аналоговыми выходами устройства и соединены через делители 25 и 28 напряжений с вторыми входами компараторов 29 и 30 соответственно, выходы которых подключены к первым входам формирователей 3 и 4 соответственно.

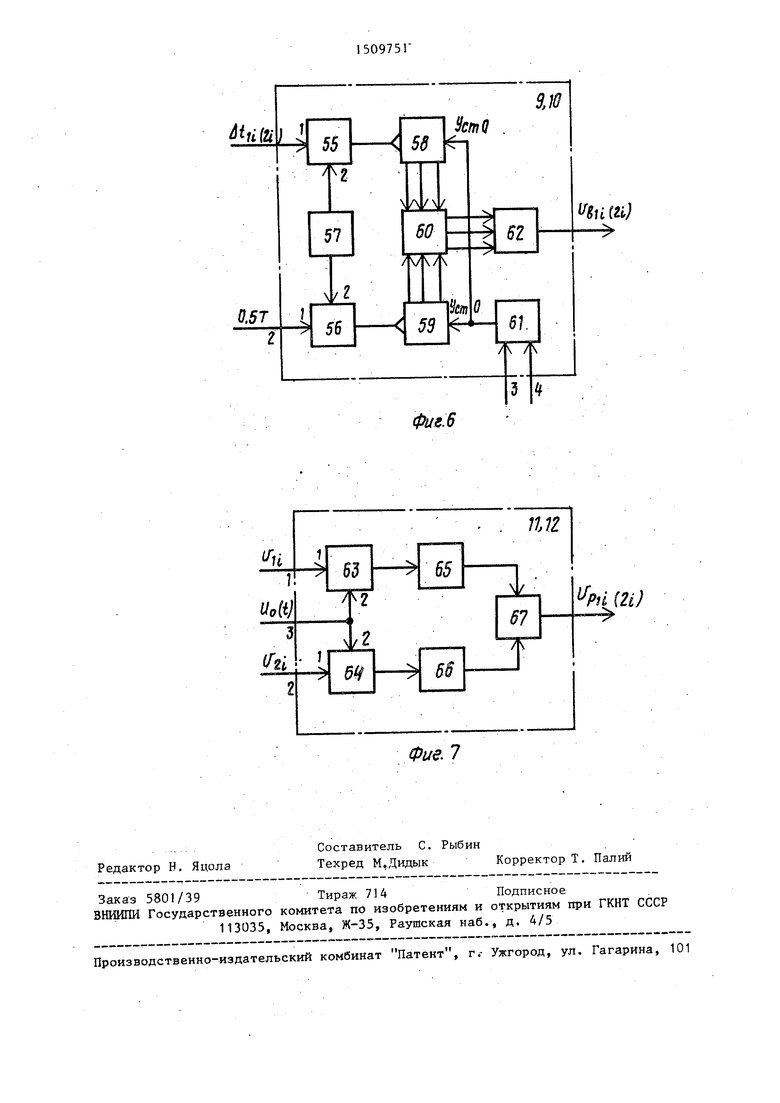

Причем каждый из формирователей временных интервалов 1 и 2 (фиг.З) включает в себя два компаратора 32 и 33 и триггер 34. Первые входы компараторов 32 и 33 объединены и являются первым входом формирователя, вторым и третьим входами которого являются вторые входы компараторов 32 и 33 соответственно. Выходы компараторов 32 и 33 соединены соответственно с входом установки единицы и входом установки нуля триггера 34, чей выход является выходом формирователя

вателей 40 и 41 подключены соответс венно к прямым входам усилителей 4 43, инверсные входы которых объедин ны и соединены с выходом источника Выходы первого и второго усилителей 42 и 43 являются первым и вторым вы ходами формирователя.

Формирователь 5 полупериода (фи

IQ содержит источник 45 опорного напря жения, два компаратора 46 и 47, три гер 48, переключатель 49, логически элемент 2И-ИЛИ 50, одновибратор 51 два логических элемента И-НЕ 52 и 5

15 и формирователь 54 импульсов сброса Первые входы компараторов 46 и 4 объединены и являются входом формирователя. Вторые входы компараторов 46 и 47 соединены соответственно с

20 первым и вторым выходами источника Выходы компараторов 46 и 47 подключ ны соответственно к входам установк единицы и нуля триггера 48, прямой выход которого соединен с вторым вх

25 дом элемента 2И-ИЛИ 50, чей третий вход подключен к инверсному выходу триггера 48. Первый вход логическог элемента 2И-ИПИ 50 соединен с первы входом элемента- И-НЕ 52 и подключен

Каэгдый из формирователей 3 и 4 опор- 30 к первому выходу переключателя 49,

вателей 40 и 41 подключены соответственно к прямым входам усилителей 42 и 43, инверсные входы которых объединены и соединены с выходом источника 44. Выходы первого и второго усилителей 42 и 43 являются первым и вторым выходами формирователя.

Формирователь 5 полупериода (фиг.5)

содержит источник 45 опорного напряжения, два компаратора 46 и 47, триггер 48, переключатель 49, логический элемент 2И-ИЛИ 50, одновибратор 51, два логических элемента И-НЕ 52 и 53

и формирователь 54 импульсов сброса. Первые входы компараторов 46 и 47 объединены и являются входом формирователя. Вторые входы компараторов 46 и 47 соединены соответственно с

первым и вторым выходами источника 45 Выходы компараторов 46 и 47 подключе- ны соответственно к входам установки единицы и нуля триггера 48, прямой выход которого соединен с вторым входом элемента 2И-ИЛИ 50, чей третий вход подключен к инверсному выходу триггера 48. Первый вход логического элемента 2И-ИПИ 50 соединен с первым входом элемента- И-НЕ 52 и подключен

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения интенсивности линии в оптическом спектре | 1987 |

|

SU1509625A1 |

| Цифровой измеритель составляющих комплексных сопротивлений | 1987 |

|

SU1456907A1 |

| Способ измерения мгновенных значений фазового сдвига электрических сигналов | 1986 |

|

SU1386940A1 |

| Цифровой интегрирующий вольтметр | 1983 |

|

SU1093984A2 |

| Фотоэлектрическая следящая система гидирования телескопа | 1984 |

|

SU1228068A1 |

| Стабилизатор переменного напряжения | 1988 |

|

SU1534434A1 |

| Устройство для сравнения фаз | 1987 |

|

SU1494102A1 |

| Ультразвуковой измеритель скорости потока | 1985 |

|

SU1500836A1 |

| Способ измерения амплитудного значения электрического сигнала | 1986 |

|

SU1441321A1 |

| Многоканальное устройство для управления вентильным преобразователем | 1982 |

|

SU1073875A1 |

Изобретение может быть использовано для измерения фазового сдвига электрических сигналов и позволяет повысить точность измерения. Устройство, реализующее способ, содержит формирователи (Ф) 1 и 2 временных интервалов, Ф 3 и 4 опорных уровней, Ф 5 полупериода, Ф 9 и 10 вспомогательных сигналов, задатчики 6...8 чисел, Ф 11 и 12 разностных сигналов, компараторы 13 и 14, элемент ИЛИ 15, генератор 16 пилообразного напряжения, ключ 17, аналого-цифровой преобразователь 18, счетчики 19 и 20 импульсов, запоминающие блоки 21 и 22, мультиплексор 23, переключатель 24 режимов индикации, цифроаналоговые преобразователи 25 и 26, делители 27 и 28 напряжения, регенеративные компараторы 29 и 30 и цифровой отсчетный блок 31. Согласно способу формируют N пар двухполярных опорных уровней ± V1I и ± V2I. Пары дополнительных сигналов формируют по функциям ARCSIN V1I/U0(T) и ARCSIN V2I/U0(T). Вспомогательные сигналы формируют путем сравнения исследуемых сигналов с опорными уровнями. Временные интервалы ΔТ1I и ΔТ2I измеряют между моментами перехода первого и второго исследуемых сигналов и измеряют полупериод исследуемых сигналов. После этого определяют отношение результатов измерения временных интервалов к результату измерения полупериода. 7 ил.

ных уровней (фиг.4) состоит из триггера 35, синхронизированного генератора 36 импульсов, двух логических элементов И-НЕ 37 и 38, реверсивного 39 импульсов с предустановкой, двух цифоанапоговых преобразователей 40 и 41 двух усилителей 42 и 43 и источника 44 напряжения смещения. Счетный вход триггера 35 является первым входом формирователя, вторым входом которого является З т равляющий вход .генератора 36, выход- которого соединен с яер- выми входами элементов И-НЕ 37 и 38, чьи вторые входы подключены к пара35

40

вход которого соединен с клеммой питания, а второй выход подключен .к четвертому входу элемента 2И-ИЛИ 50 и к первому входу элемента И-НЕ 53, второй вход которого соединен с вторым входом элемента И-НЕ 52 и ключен к прямому выходу одновибрато- ра 51, чей вход соединен с выходом логического элемента 2И-ИЛИ 50 и является первым выходом формирователя, вторым и третьим выходами которо го являются выходы логических элементов И-НЕ 52 и 53 соответственно. Четвертым выходом формирователя явфазным выходам триггера 35, входы ус- 45 ляется выход формирователя 54, вход

тановки нуля и единицы которого являются соответственно третьим и чет- .вертым входами формирователя. Выходы элементов И-НЕ37 и 38 соединены соответственно с суммирующим и вычитающим входами счетчика 39, установочные входы которого являются пятым, шестым и седьмым входами формирователя, восьмым входом которого является

50

которого подключен к выходу первого компаратора 46.

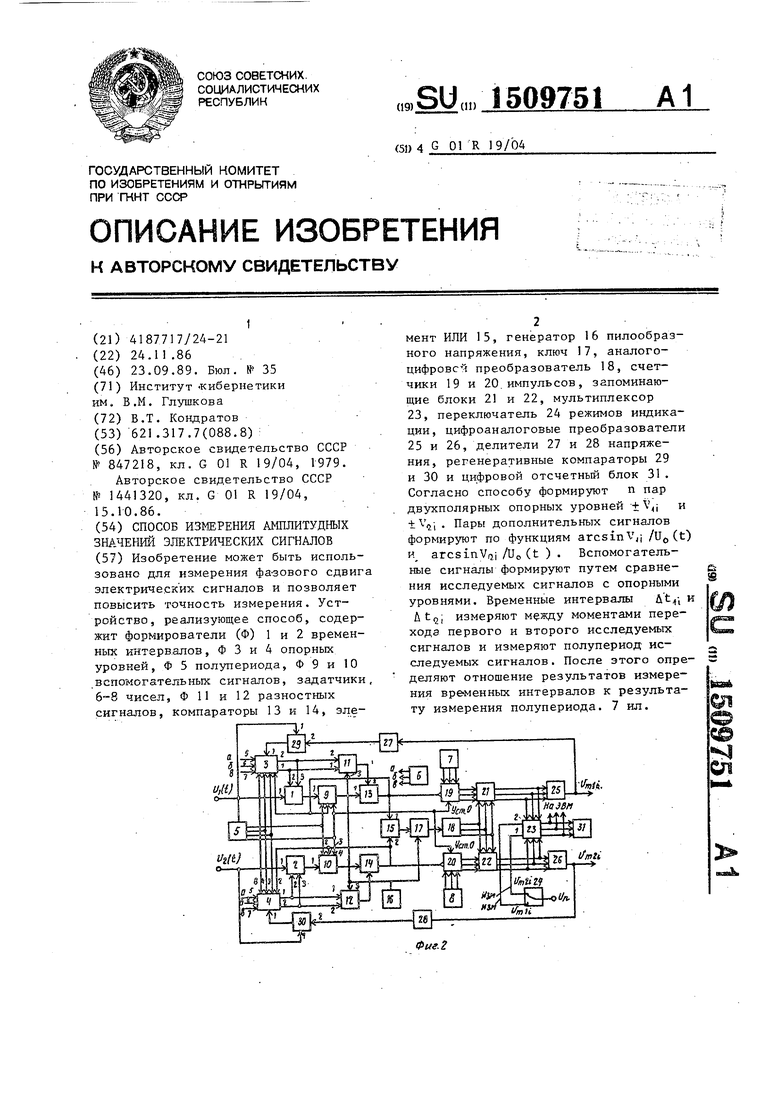

Каждый из формирователей 9 и 10 вспомогательных сигналов (фиг.6) включает в себя два логических элемента И-НЕ 55 и 56, генератор 57 импульсов, два счетчика 58 и 59 импульсов, цифровой блок 60 деления, логический элемент ИЛИ 61 и цифровход установки нуля счетчика 39. п вы-сг аналоговый преобразователь 62. Перходов счетчика 39 соединены с одноименными входами преобразователя 40, а п-1 выход - с одноименными входами преобразователя 41. Выходы преобразовые входы элементов И-НЕ 55 и 56 являются соответственно первым и вторым входами формирователя. Вторые входы соединены с выходами генера5

0

вход которого соединен с клеммой питания, а второй выход подключен .к четвертому входу элемента 2И-ИЛИ 50 и к первому входу элемента И-НЕ 53, второй вход которого соединен с вторым входом элемента И-НЕ 52 и ключен к прямому выходу одновибрато- ра 51, чей вход соединен с выходом логического элемента 2И-ИЛИ 50 и является первым выходом формирователя, вторым и третьим выходами которого являются выходы логических элементов И-НЕ 52 и 53 соответственно. Четвертым выходом формирователя яв0

которого подключен к выходу первого компаратора 46.

Каждый из формирователей 9 и 10 вспомогательных сигналов (фиг.6) включает в себя два логических элемента И-НЕ 55 и 56, генератор 57 импульсов, два счетчика 58 и 59 импульсов, цифровой блок 60 деления, логический элемент ИЛИ 61 и цифровые входы элементов И-НЕ 55 и 56 являются соответственно первым и вторым входами формирователя. Вторые входы соединены с выходами генератора 57, а выходы - со счетными . входами счетчиков 58 и 59 соответственно, .чьи входы установки нуля соединены с выходом элемента ИЛИ 61, входы которого являются третьим и четвертым входами формирователя . Выходы счетчиков 58 и 59 соединены соответственно с входами Делимое и Делитель блока 60 деления, выходы которого подключены к одноименным входам преобразователя 62, выход которого является выходом формирователя ...

Каждый из формирователей 11 и 12 разностных сигналов (фиг. 7) содержит два блока 63 и 64 деления, два функциональных (арксинусных) преобразователя 65 и 66, а также блок 67 вычитания. Первые входы блоков 63 и 64 деления являются соответственно первым и вторым входами формиро.ва- теля, третьим входом которого являются объединенные между собой вторые входы блоков 63 и 64 деления, чьи выходы соединены с входами преобразователей 65 и 66 соответственно. Выходы преобразователей 65 и 66 соединены с входами блока 67 вычитания, чей выход является выходом формирователя.

Устройство работает следующимобразом.

На первьте входы формирователей 1 и 2 временных интервалов поступают исследуемые сигналы U., (t) и ). Одновременно эти сигналы поступают на первые входы регенеративных компараторов 29 и 30. Сигнал U (t) поступает на вход формирователя 5 полупериода .

С помощью формирователя 3 (и 4) формируются опорные уровни V,i и , которые подаются на вх.оды формирователей 11 и 12 разностных сигналов, а также на входы формирователей 1 и 2 Поскольку не все входы цифроаналого- вого преобразователя 41 подключены к выходу счетчика 39, то на его выходе напряжение будет меньше напряжения 1 фроанал.огового преобразователя 40 на постоянную величину . Для пе- ;рекрытия всего диапазона изменения амплитудных значений исследуемых сигналов, т.е.-значений ±V jj, , выходйые сигналы преобразователей АО и 41 смещают на половину их диапазона, что достигается использованием усилителей 42 и 43, а также источ0

5

0

5

5

0

5

0

5

теля пределах

0

ника 44 напряжения смещения. В результате выходное напряжение усили- 42, равное V(i , изменяется в

т /члк а усилителя 43 - в пределах ±V/i, где uV - V.,i const, а Ку - коэффициент усиления усилителей 42 и 43. ,

После каждого такта измерения амплитудных значений исследуемых сигналов осуществляется дискретное изменение опорных уровней V/f и.Уо (при 4V,2. V(ii - const) путем подачи на суммирующий или вычитающий входы реверсивного счетчика 39 с выходов элементов И-НЕ 37 или 38. Причем знак изменения опорных уровней (т.е. их возрастание или убывание) зависит от того, на какой из входов счетчика 39 поступают импульсы. Управление работой счетчика 39 осуществляется с помощью задатчика 6 чисел, триггера 35, элементов И-НЕ 37 и 38 и синхронизированного генератора 36 импульсов.

Исходное значение опорного уровня (а следовательно и ) устанавливают с помощью задатчика 6 чисел и источника 44 напряжения смещения. Знак изменения опорных -уровней определяется состоянием триггера 35. При состоянии логической единицы на его прямом входе осуществляется суммирование импульсов, поступающих на счетчик 39 с выхода генератора 36 через элемент И-НЕ 37, а при состоянии логической единицы на инверсном вьпсоде триггера 35 - вычитание импульсов, т.е. в первом случае обеспечивается дискретное увеличение значений опорных уровней и Vrj, а во втором случае - их уменьщение.

Первоначальное состояние триггера 35 зависит от знака полупериода- сигнала и(), в течение которого ;осуществляется измерение временного интервала, равного полупериоду сигнала. Значение полупериода может быть измерено как в положительный, так и в отрицательный полупериод сигнала ). Это достигается путем установки переключателя 49 в в.ерх- : ;Нее.. ипи нижнее положения соответственно. В результате на первый или :четвёртый входы элемента 2И-ИПИ 50 (Поступает положительный потенциал, разрешакщий прохождение импульса, длительностью 0,5 Т с прямого шш.

1 1

инверсного выходов триггера 48 на одноврбратор 51 и через первый выход формирователя 5 - на вторые входы формирователей 9 и 10. Импульс длительностью 0,5 Т формируется с помощью триггера 48, управляемого выходными импульсами компараторов 46 и 47. Причем в качестве опорных уровней компараторов 46 и 47 используются соответственно сигналы -AV OH+&V O с первого и второго выходов источника 45 опорного напряжения. На первые входы, компараторов 46 и 47 поступает сигнал и (t), по которому и вьще- ляются временные интервалы длительностью 0,5 Т.

Допустим, что переключатель 49 установлен в положение, показанпое на фиг. 5, соответствующее выделению временного интервала,равного полупериоду, в .положительный полупериод сигнала (1) (фиг.1).

В момент времени перехода сигнал ) через опорный уровень - AV на выходе компаратора 46 формируетс51 короткий импульс, который поступает иа вход установки единицы .триггера 48 и на вход формирователя 54 импульсов сброса.

Последний формирует, импульс сброса длительностью, достаточной для установки в нуль счетчиков импульсов 19, 20, 39, 58 и 59.

Задним фронтом импульса длительностью 0,5Т запускается одновибра- тор 51, который формирует импульсы предварительной, установки исходного состояния триггера 35 блока 3 (или 4 .Б зависимости от положения переключателя 49, разрешающ1Й потендиал поступает на первые входы элементов И-НЕ 52 и 53. В данном случае он поступает на первый вход элемента И-НЕ 52, тем самым разрешая прохождение выходного импульса одновибрато ра 51 на .вход установки нуля триггера 35. В результате с каждым тактом измерения опорные уровни I .fi и Vijj будут смещаться вниз, т.е. уменьшаться на определенные дискретные значения напрялсения uVq. Значение напряжения flVg определяется числом импульсов, генерируемых генератором 36 в течение времени действия синхроимпульса,поступающего на его управляющий вход. Соответствующим подбором числа импульсов в пачке, ус 150975112

танавливается заданное напряжения UV.

При достижении исследуемого сигнала измеренного амплитудного значения Vf,i,|(HHH Vm(2i .) с помощью регенеративных компараторов 29 (или 30 формируется короткий импульс, поступающий на первый вход формирователя 3 (или 4) опорных уровней, который изменяет первоначальное состояние триггера 35 на противоположное. В результате знак изменения опорных уровней V (или : ) меняется на противоположный. Это обеспечивает измерение амплитудных значений исследуемых сигналов как при отрицательном, так и при положительном значении производной, что увеличивает число тактов измерения, а следовательно, и число измерений за полупериод или период сигнала.

Опорные уровни У-,- и с первого и второго выходов формирователей 3 и 4 поступают на второй и третий входы формирователей и 2 вре- менных интервалов соответственно.Эти входы соединены с вторыми входами компараторов 32 и 33 (фиг.4), на первые входы которых поступает исследуемый сигнал. В результате сравнения на выходах компараторов 32 и 33 появляются короткие импульсы, управляющие работой триггера 34. Последний обеспечивает формирование временных интервалов ДЬ илп Л t rjj ,

Временные интервалы . и с выходов формирователей 1 и 2 временных интервалов поступают на первые входы- первого и второго формирователей 9 и 10 вспомогательных сигналов. На вторые входы формирователей 9 и .10 поступают временные интервалы длительностью 0,5 Т с первого выхода формирователя 5 полупериода.

С помощью формирователя 9 (Ю) осуществляется измерение временных интервалов At i и 0,5 Т ( &.t;2i и 0,5 Т) путем подсчета с помощ,ью счетчиков 58 и 59 выходных импульсов генератора 57 за время и 0,5 Т ( А t-j,; и 0,5 Т). Коды чисел

-fc f.

it,i ;

utoi

и

NS foO,5T

13

1509751 генерато-,

14

где fo - частота импульсов

ра 57,

поступают на цифровой блок деления 60. В результате на вход цифроанало- говых преобразователей 62 формирователей 9 и 10 поступают коды чисел

N

4i

- /0,5 Т

N

Si

- &t.j /0,5Т,

тельных и разностного сигналов изме- ряют мгновенньте значения пилообразного .сигнала Uo(t) с помощью анало- - го-цифрового преобразователя 18.

Коды чисел N(j или с выхо- ,дов аналого-цифрового преобразователя 18 поступают на информационные входы запоминающих блоков 21 и 22.

10 На управляющие входы запоминающих блоков 21 и 22 поступают коды адреса ячеек памяти с выходов счетчиков 19 и 20 с предустановкой. При записи . информации в запоминающие блоки 21

15 и 22 код адреса на выходе счетчика 19 или 20 устанавливается с приходом очередного импульса с выхода компаратора 13 или J4. При считывании информации код адреса устанавли20 вается вручную с помощью задатчика 7 или В чисел.

С выходов запоминающих блоков 21 и 22 коды чисел N,j и N поступают

времени начапа процесса измере- 25 на входы мультиплексора 23 и цифро- аналоговых преобразователей 25 и 26. Последние преобразуют коды чисел

равные отношению временното интервала Л t 1 (или at,;) на полу- период.

С помощью цифроана юговых преобразователей 62 коды Niji и Ngi преобразовываются во вспомогательные напряжения Vei и .

Предварительная установка в нуль счетчиков 58 и 59 формирователя 9(10) осуществляется выходными импульсами формирователя 54 блока и выходными импульсами компаратора 13(14) в моменты

ния и окончания каждого такта сравнения вспомогательного и разностного сигналов.Процесс сравнения осуществляется с помощью компараторов 13 и 15, на первые входы которых поступают вспомогательные сигналы 6i и

30

и N,;B аналоговые сигналы, например в .напряжения и rrti i

С выходов мультиплексора 23 коды чисел Nf,- и Угмг в зависимости от положения переключателя 24 поступают на вьтходную шину и отсчетный блок- 31, где индицируются.

V

71

а на вторые входы - разностные

сигналы вида (5).

Разностные сигналы формируются с помощью формирователей 11 и 12. Для этого на их входы поступают опорные уровни V(i и TQJ с выходов формирователя 3 и 4. На Третьи входы формирователей 11 и 12 поступает пи45

лообразный сигнал Uo(t)c выхода гене- 40 чающийся в том, что формируют пило- ратора 16. Эти сигналы поступают на входы блоков деления 63 и 64 форми- рователя 11(12).С помощью блоков деления 63 и 64 формируются сигналы, мгновенные значения которых равны отнощениям /Uc,(t) и У.; AJo (t) соответственно. Эти сигналы поступают на функциональные арксинусные преобразователи 65 и 66. После преобразования на входы блока 67 вычитания, поступают преобразованные сигналы TJgi и ligj . На выходы блока 67 вычитания, а следовательно, и формирователя разностных сигналов в целом появляется сигнал TifoiС выходов формирователей П к 12.; разностные сигналы поступают на вторые входы компараторов 13 и 14. В моменты времени равенства вспомога50

55

образный сигнал To(t) повьшенной час тоты, 2п пар, где п 1,2,3,...,, 1+1,... вспомогательных сигналов, п пар преобразованных по функции арксинуса дополнительных сигналов, формируют разности парных дополнительных сигналов, сравнивают полученные разностные сигналы со вспомогательными сигналами и измеряют в моменты их равенства мгновенные значения пилообразного сигнала, амплитудные значения исследуемых электрических сигналов определяют по результатам измерений пилообразного сигнала, о т личающийся тем, что, с целью повьшгения точности, предварительно формируют п пар двухполярных опорньк уровней ( и , пары дополнительных сигналов формируют

14

и N,;B аналоговые сигналы, например в .напряжения и rrti i

С выходов мультиплексора 23 коды чисел Nf,- и Угмг в зависимости от положения переключателя 24 поступают на вьтходную шину и отсчетный блок- 31, где индицируются.

Формула изобретения

Способ измерения амплитудных зна-- чений электрических сигналов, заклю

чающийся в том, что формируют пило-

образный сигнал To(t) повьшенной частоты, 2п пар, где п 1,2,3,...,, 1+1,... вспомогательных сигналов, п пар преобразованных по функции арксинуса дополнительных сигналов, формируют разности парных дополнительных сигналов, сравнивают полученные разностные сигналы со вспомогательными сигналами и измеряют в моменты их равенства мгновенные значения пилообразного сигнала, амплитудные значения исследуемых электрических сигналов определяют по результатам . измерений пилообразного сигнала, о т- личающийся тем, что, с целью повьшгения точности, предварительно формируют п пар двухполярных опорньк уровней ( и , пары дополнительных сигналов формируют

15

arcsin

Vif

UZt) a вспомогательные сигпо функциям

.

налы формируют путем сравнения ис- следуемых временных интервалов ,&t,| и fitд-, между моментами перекода первого и второго исследуемых сигналов

./ .- ;

и, Ц

5

751 16

через i-ю пару опорных уровней, измере. Т ния полупериода исследуемых сигналов и

определения отношения результатов измерения временных интервалов &tf и к результату измерения полу Т периода -у.

Uilt}

Фиг

Фиг. З

6(1-01

4

ЦВ

5 fwig

2

47

j/

Й

/

V

5

0US.lt .

Ь./

g

5(

0.57

52

/F

УстО

/

/

5J

Jbl

фце.

Фиг.6

Фие. 7

| Способ измерения амплитудного значенияэлЕКТРичЕСКОгО СигНАлА | 1979 |

|

SU847218A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ измерения амплитудного значения электрического сигнала | 1986 |

|

SU1441320A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-09-23—Публикация

1986-11-24—Подача